Mostra el registre d'ítem simple

Breaking master-slave model between host and FPGAs

| dc.contributor.author | Bosch Pons, Jaume |

| dc.contributor.author | Vidal, Miquel |

| dc.contributor.author | Filgueras Izquierdo, Antonio |

| dc.contributor.author | Álvarez Martínez, Carlos |

| dc.contributor.author | Jiménez González, Daniel |

| dc.contributor.author | Martorell Bofill, Xavier |

| dc.contributor.author | Ayguadé Parra, Eduard |

| dc.contributor.other | Universitat Politècnica de Catalunya. Doctorat en Arquitectura de Computadors |

| dc.contributor.other | Universitat Politècnica de Catalunya. Departament d'Arquitectura de Computadors |

| dc.contributor.other | Barcelona Supercomputing Center |

| dc.date.accessioned | 2020-09-29T13:40:36Z |

| dc.date.issued | 2020 |

| dc.identifier.citation | Bosch, J. [et al.]. Breaking master-slave model between host and FPGAs. A: ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming. "PPoPP'20: Proceedings of the 2020 25th ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming: San Diego, CA, USA: 22-26 February 2020". New York: Association for Computing Machinery (ACM), 2020, p. 419-420. ISBN 978-1-4503-6818-6. DOI 10.1145/3332466.3374545. |

| dc.identifier.isbn | 978-1-4503-6818-6 |

| dc.identifier.uri | http://hdl.handle.net/2117/329410 |

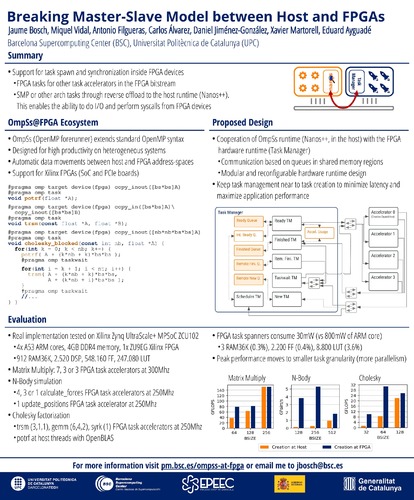

| dc.description.abstract | This paper proposes to enhance current task-based programming models by breaking their current master-slave approach between the main processor and its hardware accelerators. As a proof-of-concept, it presents an extension of the OmpSs@FPGA toolchain that allows the tasks offloaded into the FPGA to create and synchronize nested tasks on their own without involving the host. Those FPGA spawned tasks may target the host to execute code not suitable for the FPGA, like system calls or I/O operations; or target other kernel accelerators inside the same FPGA. In addition to the programmability benefits of this new feature, the proposed system presents significant performance improvements and a better productivity over the classical master-slave approach. |

| dc.description.sponsorship | This work has received funding from EPEEC project (Euro-pean Union’s Horizon 2020 Research and Innovation Pro-gramme, under grant agreement No 801051), from SpanishGovernment (projects SEV-2015-0493 and TIN2015-65316-P,grant BES-2016-078046), and from Generalitat de Catalunya(contracts 2017-SGR-1414 and 2017-SGR-1328). |

| dc.format.extent | 2 p. |

| dc.language.iso | eng |

| dc.publisher | Association for Computing Machinery (ACM) |

| dc.subject | Àrees temàtiques de la UPC::Informàtica::Arquitectura de computadors::Arquitectures paral·leles |

| dc.subject.lcsh | Parallel programming (Computer science) |

| dc.subject.other | Heterogeneous (hybrid) systems |

| dc.subject.other | Parallel programming languages |

| dc.title | Breaking master-slave model between host and FPGAs |

| dc.type | Conference lecture |

| dc.subject.lemac | Programació en paral·lel (Informàtica) |

| dc.contributor.group | Universitat Politècnica de Catalunya. CAP - Grup de Computació d'Altes Prestacions |

| dc.identifier.doi | 10.1145/3332466.3374545 |

| dc.description.peerreviewed | Peer Reviewed |

| dc.relation.publisherversion | https://dl.acm.org/doi/10.1145/3332466.3374545 |

| dc.rights.access | Open Access |

| local.identifier.drac | 28979543 |

| dc.description.version | Postprint (published version) |

| dc.relation.projectid | info:eu-repo/grantAgreement/EC/H2020/801051/EU/European joint Effort toward a Highly Productive Programming Environment for Heterogeneous Exascale Computing (EPEEC)/EPEEC |

| dc.relation.projectid | info:eu-repo/grantAgreement/MINECO//TIN2015-65316-P/ES/COMPUTACION DE ALTAS PRESTACIONES VII/ |

| local.citation.author | Bosch, J.; Vidal, M.; Filgueras, A.; Álvarez, C.; Jiménez, D.; Martorell, X.; Ayguadé, E. |

| local.citation.contributor | ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming |

| local.citation.pubplace | New York |

| local.citation.publicationName | PPoPP'20: Proceedings of the 2020 25th ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming: San Diego, CA, USA: 22-26 February 2020 |

| local.citation.startingPage | 419 |

| local.citation.endingPage | 420 |