Exploració per autor "Casas, Marc"

Ara es mostren els items 21-40 de 96

-

Convolutional neural network training with dynamic epoch ordering

Plana Rius, Ferran; Angulo Bahón, Cecilio; Casas, Marc; Mirats Tur, Josep Maria (IOS Press, 2019)

Plana Rius, Ferran; Angulo Bahón, Cecilio; Casas, Marc; Mirats Tur, Josep Maria (IOS Press, 2019)

Comunicació de congrés

Accés restringit per política de l'editorialThe paper presented exposes a novel approach to feed data to a Convolutional Neural Network (CNN) while training. Normally, neural networks are fed with shuffled data without any control of what type of examples contains ... -

Cost-aware prediction of uncorrected DRAM errors in the field

Boixaderas Coderch, Isaac; Živanovič, Darko; Moré Codina, Sergi; Bartolomé Rodríguez, Javier; Vicente Dorca, David; Casas, Marc; Carpenter, Paul Matthew; Radojković, Petar; Ayguadé Parra, Eduard (Institute of Electrical and Electronics Engineers (IEEE), 2020)

Boixaderas Coderch, Isaac; Živanovič, Darko; Moré Codina, Sergi; Bartolomé Rodríguez, Javier; Vicente Dorca, David; Casas, Marc; Carpenter, Paul Matthew; Radojković, Petar; Ayguadé Parra, Eduard (Institute of Electrical and Electronics Engineers (IEEE), 2020)

Text en actes de congrés

Accés obertThis paper presents and evaluates a method to predict DRAM uncorrected errors, a leading cause of hardware failures in large-scale HPC clusters. The method uses a random forest classifier, which was trained and evaluated ... -

Data prefetching on in-order processors

Ortega Carrasco, Cristobal; García Flores, Víctor; Moretó Planas, Miquel; Casas, Marc; Rositoru, Roxana (Institute of Electrical and Electronics Engineers (IEEE), 2018)

Ortega Carrasco, Cristobal; García Flores, Víctor; Moretó Planas, Miquel; Casas, Marc; Rositoru, Roxana (Institute of Electrical and Electronics Engineers (IEEE), 2018)

Text en actes de congrés

Accés obertLow-power processors have attracted attention due to their energy-efficiency. A large market, such as the mobile one, relies on these processors for this very reason. Even High Performance Computing (HPC) systems are ... -

Design Space Exploration of Next-Generation HPC Machines

Gómez, Constantino; Martínez, Francesc; Armejach, Adrià; Moretó, Miquel; Mantovani, Filippo; Casas, Marc (2019)

Gómez, Constantino; Martínez, Francesc; Armejach, Adrià; Moretó, Miquel; Mantovani, Filippo; Casas, Marc (2019)

Report de recerca

Accés obertThe landscape of High Performance Computing (HPC) system architectures keeps expanding with new technologies and increased complexity. With the goal of improving the efficiency of next-generation large HPC systems, ... -

Design space exploration of next-generation HPC machines

Gómez Crespo, Constantino; Martínez Palau, Francesc; Armejach Sanosa, Adrià; Moretó Planas, Miquel; Mantovani, Filippo; Casas, Marc (Institute of Electrical and Electronics Engineers (IEEE), 2019)

Gómez Crespo, Constantino; Martínez Palau, Francesc; Armejach Sanosa, Adrià; Moretó Planas, Miquel; Mantovani, Filippo; Casas, Marc (Institute of Electrical and Electronics Engineers (IEEE), 2019)

Text en actes de congrés

Accés restringit per acord de confidencialitatThe landscape of High Performance Computing (HPC) system architectures keeps expanding with new technologies and increased complexity. With the goal of improving the efficiency of next-generation large HPC systems, designers ... -

Design trade-offs for emerging HPC processors based on mobile market technology

Armejach Sanosa, Adrià; Casas, Marc; Moretó Planas, Miquel (2019-09-01)

Armejach Sanosa, Adrià; Casas, Marc; Moretó Planas, Miquel (2019-09-01)

Article

Accés obertHigh-performance computing (HPC) is at the crossroads of a potential transition toward mobile market processor technology. Unlike in prior transitions, numerous hardware vendors and integrators will have access to ... -

Dynamically adapting floating-point precision to accelerate deep neural network training

Osorio Ríos, John Haiber; Armejach Sanosa, Adrià; Petit, Eric; Henry, Greg; Casas, Marc (Institute of Electrical and Electronics Engineers (IEEE), 2021)

Osorio Ríos, John Haiber; Armejach Sanosa, Adrià; Petit, Eric; Henry, Greg; Casas, Marc (Institute of Electrical and Electronics Engineers (IEEE), 2021)

Text en actes de congrés

Accés obertMixed-precision (MP) arithmetic combining both single- and half-precision operands has been successfully applied to train deep neural networks. Despite its advantages in terms of reducing the need for key resources like ... -

Efficiency analysis of modern vector architectures: vector ALU sizes, core counts and clock frequencies

Barredo Ferreira, Adrián; Cebrián González, Juan Manuel; Valero Cortés, Mateo; Casas, Marc; Moretó Planas, Miquel (2020-03)

Barredo Ferreira, Adrián; Cebrián González, Juan Manuel; Valero Cortés, Mateo; Casas, Marc; Moretó Planas, Miquel (2020-03)

Article

Accés obertMoore’s Law predicted that the number of transistors on a chip would double approximately every 2 years. However, this trend is arriving at an impasse. Optimizing the usage of the available transistors within the thermal ... -

Efficient direct convolution using long SIMD instructions

Limas Santana, Alexandre de; Armejach Sanosa, Adrià; Casas, Marc (Association for Computing Machinery (ACM), 2023)

Limas Santana, Alexandre de; Armejach Sanosa, Adrià; Casas, Marc (Association for Computing Machinery (ACM), 2023)

Text en actes de congrés

Accés obertThis paper demonstrates that state-of-the-art proposals to compute convolutions on architectures with CPUs supporting SIMD instructions deliver poor performance for long SIMD lengths due to frequent cache conflict misses. ... -

Efficiently running SpMV on long vector architectures

Gómez Crespo, Constantino; Mantovani, Filippo; Focht, Erich; Casas, Marc (Association for Computing Machinery (ACM), 2021)

Gómez Crespo, Constantino; Mantovani, Filippo; Focht, Erich; Casas, Marc (Association for Computing Machinery (ACM), 2021)

Text en actes de congrés

Accés restringit per política de l'editorialSparse Matrix-Vector multiplication (SpMV) is an essential kernel for parallel numerical applications. SpMV displays sparse and irregular data accesses, which complicate its vectorization. Such difficulties make SpMV to ... -

ETP4HPC’s SRA 5 strategic research agenda for High-Performance Computing in Europe 2022: European HPC research priorities 2023-2027

Carpenter, Paul Matthew; Casas, Marc; Unsal, Osman Sabri; Radojkovic, Petar; Martorell Bofill, Xavier; Miranda, Alberto; Guitart Fernández, Jordi; Corbalán González, Julita; Peña Monferrer, Antonio José; Bautista Gomez, Leonardo Arturo; Vázquez García, Miguel; Beltran Querol, Vicenç; Queralt Calafat, Anna; Nou Castell, Ramon; Borrell Pol, Ricard; Houzeaux, Guillaume; Serradell Maronda, Kim; Carrera Pérez, David; García Sáez, Artur; Puchol García, Carlos (2022-09)

Carpenter, Paul Matthew; Casas, Marc; Unsal, Osman Sabri; Radojkovic, Petar; Martorell Bofill, Xavier; Miranda, Alberto; Guitart Fernández, Jordi; Corbalán González, Julita; Peña Monferrer, Antonio José; Bautista Gomez, Leonardo Arturo; Vázquez García, Miguel; Beltran Querol, Vicenç; Queralt Calafat, Anna; Nou Castell, Ramon; Borrell Pol, Ricard; Houzeaux, Guillaume; Serradell Maronda, Kim; Carrera Pérez, David; García Sáez, Artur; Puchol García, Carlos (2022-09)

Report de recerca

Accés obertThis document feeds research and development priorities devel-oped by the European HPC ecosystem into EuroHPC’s Research and Innovation Advisory Group with an aim to define the HPC Technology research Work Programme and ... -

Evaluating execution time predictability of task-based programs on multi-core processors

Grass, Thomas Dieter; Rico Carro, Alejandro; Casas, Marc; Moretó Planas, Miquel; Ramírez Bellido, Alejandro (Springer, 2015)

Grass, Thomas Dieter; Rico Carro, Alejandro; Casas, Marc; Moretó Planas, Miquel; Ramírez Bellido, Alejandro (Springer, 2015)

Text en actes de congrés

Accés restringit per política de l'editorialTask-based programming models are becoming increasingly important, as they can reduce the synchronization costs of parallel programs on multi-cores. Instances of the same task type in task-based programs consist of the ... -

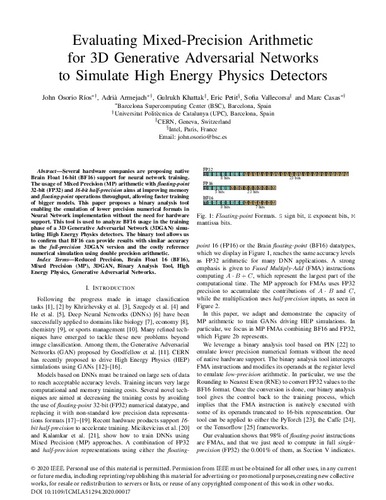

Evaluating mixed-precision arithmetic for 3D generative adversarial networks to simulate high energy physics detectors

Osorio Ríos, John Haiber; Armejach Sanosa, Adrià; Khattak, Gulrukh; Petit, Eric; Vallecorsa, Sofia; Casas, Marc (Institute of Electrical and Electronics Engineers (IEEE), 2020)

Osorio Ríos, John Haiber; Armejach Sanosa, Adrià; Khattak, Gulrukh; Petit, Eric; Vallecorsa, Sofia; Casas, Marc (Institute of Electrical and Electronics Engineers (IEEE), 2020)

Text en actes de congrés

Accés obertSeveral hardware companies are proposing native Brain Float 16-bit (BF16) support for neural network training. The usage of Mixed Precision (MP) arithmetic with floating-point 32-bit (FP32) and 16-bit half-precision aims ... -

Evaluating scientific workflow execution on an asymmetric multicore processor

Pietri, Ilia; Zhuang, Sicong; Casas, Marc; Moretó Planas, Miquel; Sakellariou, Rizos (Springer, 2018-02)

Pietri, Ilia; Zhuang, Sicong; Casas, Marc; Moretó Planas, Miquel; Sakellariou, Rizos (Springer, 2018-02)

Comunicació de congrés

Accés obertAsymmetric multicore architectures that integrate different types of cores are emerging as a potential solution for good performance and power efficiency. Although scheduling can be improved by utilizing an appropriate set ... -

Evaluating the impact of OpenMP 4.0 extensions on relevant parallel workloads

Vidal Ortiz, Raul; Casas, Marc; Moretó Planas, Miquel; Chasapis, Dimitrios; Ferrer Ibáñez, Roger; Martorell Bofill, Xavier; Ayguadé Parra, Eduard; Labarta Mancho, Jesús José; Valero Cortés, Mateo (Springer, 2015)

Vidal Ortiz, Raul; Casas, Marc; Moretó Planas, Miquel; Chasapis, Dimitrios; Ferrer Ibáñez, Roger; Martorell Bofill, Xavier; Ayguadé Parra, Eduard; Labarta Mancho, Jesús José; Valero Cortés, Mateo (Springer, 2015)

Text en actes de congrés

Accés obertOpenMP has been for many years the most widely used programming model for shared memory architectures. Periodically, new features are proposed and some of them are finally selected for inclusion in the OpenMP standard. The ... -

Evaluation of HPC applications’ Memory Resource Consumption via Active Measurement

Casas, Marc; Bronevetsky, Greg (IEE, 2016)

Casas, Marc; Bronevetsky, Greg (IEE, 2016)

Article

Accés obertAs the number of compute cores per chip continues to rise faster than the total amount of available memory, applications will become increasingly starved for memory storage capacity and bandwidth, making the problem of ... -

Exploiting asynchrony from exact forward recovery for DUE in iterative solvers

Jaulmes, Luc; Casas, Marc; Moretó Planas, Miquel; Ayguadé Parra, Eduard; Labarta Mancho, Jesús José; Valero Cortés, Mateo (2015)

Jaulmes, Luc; Casas, Marc; Moretó Planas, Miquel; Ayguadé Parra, Eduard; Labarta Mancho, Jesús José; Valero Cortés, Mateo (2015)

Report de recerca

Accés obertThis paper presents a method to protect iterative solvers from Detected and Uncorrected Errors (DUE) relying on error detection techniques already available in commodity hardware. Detection operates at the memory page ... -

Exploiting asynchrony from exact forward recovery for DUE in iterative solvers

Jaulmes, Luc; Casas, Marc; Moretó Planas, Miquel; Ayguadé Parra, Eduard; Labarta Mancho, Jesús José; Valero Cortés, Mateo (Association for Computing Machinery (ACM), 2015)

Jaulmes, Luc; Casas, Marc; Moretó Planas, Miquel; Ayguadé Parra, Eduard; Labarta Mancho, Jesús José; Valero Cortés, Mateo (Association for Computing Machinery (ACM), 2015)

Text en actes de congrés

Accés obertThis paper presents a method to protect iterative solvers from Detected and Uncorrected Errors (DUE) relying on error detection techniques already available in commodity hardware. Detection operates at the memory page ... -

Exploiting page table locality for Agile TLB Prefetching

Vavouliotis, Georgios; Alvarez Martí, Lluc; Karakostas, Vasileios; Nikas, Konstantinos; Koziris, Nectarios; Jiménez, Daniel A.; Casas, Marc (Institute of Electrical and Electronics Engineers (IEEE), 2021)

Vavouliotis, Georgios; Alvarez Martí, Lluc; Karakostas, Vasileios; Nikas, Konstantinos; Koziris, Nectarios; Jiménez, Daniel A.; Casas, Marc (Institute of Electrical and Electronics Engineers (IEEE), 2021)

Text en actes de congrés

Accés obertFrequent Translation Lookaside Buffer (TLB) misses incur high performance and energy costs due to page walks required for fetching the corresponding address translations. Prefetching page table entries (PTEs) ahead of ... -

Exploration of architectural parameters for future HPC systems

Gómez, Constantino; Martínez, Francesc; Armejach Sanosa, Adrià; Casas, Marc; Mantovani, Filippo; Moretó Planas, Miquel (Barcelona Supercomputing Center, 2019-05-07)

Gómez, Constantino; Martínez, Francesc; Armejach Sanosa, Adrià; Casas, Marc; Mantovani, Filippo; Moretó Planas, Miquel (Barcelona Supercomputing Center, 2019-05-07)

Text en actes de congrés

Accés obert