Universiteit Gent Faculteit Ingenieurswetenschappen en Architectuur Vakgroep Elektronica en Informatiesystemen

# Automated Design of Domain-Specific Custom Instructions

Geautomatiseerd ontwerp van domeinspecifieke gespecialiseerde instructies

# Cecilia González-Álvarez

Promotoren: Prof. Dr. Ir. Lieven Eeckhout

Prof. Dr. Daniel Jiménez-González

Prof. Dr. Carlos Álvarez

Proefschrift tot het behalen van de graad van Doctor in de Ingenieurswetenschappen: Computerwetenschappen Academiejaar 2015-2016

# Automated Design of Domain-Specific Custom Instructions

Diseño automatizado de instrucciones especializadas para un dominio específico

# Cecilia González-Álvarez

Directores: Prof. Dr. Lieven Eeckhout

Prof. Dr. Daniel Jiménez-González

Prof. Dr. Carlos Álvarez

Tesis presentada para obtener el título de Doctora por la Universitat Politècnica de Catalunya Programa de Doctorado: Arquitectura de Computadores Año académico 2015-2016

# Acknowledgements

I would like to express my sincere gratitude to my advisors: Daniel Jiménez-González and Carlos Álvarez at UPC, and Lieven Eeckhout at UGent. They have guided me with expertise and understanding, and without their support this thesis would have never been possible.

I would also like to thank people I met at each step of my PhD journey. First, I thank my supervisor at BSC, Xavier Martorell for his guidance and support, and my colleagues at BSC and UPC for all the great moments shared. Also, a very special thanks goes to Hironori Kasahara, professor at Waseda University, for all the encouragement during the year and a half that I spent in Japan. At last, I also would like to thank my colleagues at UGent, with special thanks to Jennifer Sartor for her help and support.

Of course, I would like to thank my family and friends for all the best moments shared that lighted up the darkest times. Special thanks go to my parents and Klaas for their loving encouragement.

Finally, this research would not have been possible without the financial assistance of the Severo Ochoa program (SEV-2011-00067), the Spanish Ministry of Science and Technology (TIN2012-34557), the Generalitat de Catalunya (MPEXPAR, 2009-SGR-980), HiPEAC3 Network of Excellence (FP7/ICT 287759), the European Research Council under the European Community's Seventh Framework Programme (FP7/2007-2013) / ERC Grant agreement no. 259295, the Xilinx University Program, and the Japanese Ministry of Education. I express my gratitude to those agencies.

Ghent, 24/09/2015 Cecilia González Álvarez

# Summary

In the last years, hardware specialization has received renewed attention as chips approach a utilization wall. Specialized accelerators can take advantage of underutilized transistors implementing custom hardware that complements the main processor. However, specialization adds complexity to the design process and limits reutilization. Application-Specific Instruction Processors (ASIPs) balance performance and reusability, extending a general-purpose processor with custom instructions (CIs) specific for an application, implemented in Specialized Functional Units (SFUs). Still, timeto-market is a major issue with application-specific designs because, if CIs are not frequently executed, the acceleration benefits will not compensate for the overall design cost. Domain-specific acceleration increases the applicability of ASIPs, as it targets several applications that run on the same hardware. Also, reconfigurable SFUs and the automation of the CIs design can solve the aforementioned problems. In this dissertation, we explore different automated approaches to the design of CIs that extend a baseline processor for domain-specific acceleration to improve both performance and energy efficiency.

First, we develop automated techniques to identify code sequences within a domain to create CI candidates. Due to the disparity among coding styles of different programs, it is difficult to find patterns that are represented by a unique CI across applications. Therefore, we propose an analysis at the basic block level that identifies equivalent CIs within and across different programs. We use the Taylor Expansion Diagram (TED) canonical representation to find not only structurally equivalent CIs, but also functionally similar ones, as opposed to the commonly applied directed acyclic graph (DAG) isomorphism detection. We combine both methods into a new Hybrid DAG/TED technique to identify more patterns across applications that map to the same CI. Then, we select a subset of the CI candidates that fits in the available SFU area. Because of the complexity of the problem, we propose four scoring heuristics to reduce the design space and smooth the potential performance speedup across applications. We include these me-

IV Summary

thods in the FuSInG framework, and we estimate performance with hardware models on a set of media benchmarks. Results show that, when limiting core area devoted to specialization, the SFU customization with the largest speedups includes a mix of application and domain-specific custom instructions.

If we target larger CIs to obtain higher speedups, reusability across applications becomes critical; without enough equivalences, CIs cannot be generalized for a domain. We aim to share partially common operations among CIs to accelerate more code, especially across basic blocks, and to reduce the hardware area needed for specialization. Hence, we create a new canonical representation across basic blocks, the Merging Diagram, to facilitate similarity detection and improve code coverage. We also introduce clustering-based partial matching to identify partially-similar domainspecific CIs, which generally leads to better performance than applicationspecific ones. Yet, at small areas, merging two CIs induces a high additional overhead that might penalize energy-efficiency. Thus, we also detect fragments of CIs and we join them with the existing merged clusters resulting in minimal extra overhead. Also, using speedup as the deciding factor for CI selection may not be optimal for devices with limited power budgets. For that reason, we propose a linear programming-based selection that balances performance and energy consumption. We implement these techniques in the MInGLE framework and evaluate them with media benchmarks. The selected CIs significantly improve the energy-delay product and performance, demonstrating that we can accelerate a domain covering more code while reducing the needed area for the CI implementation.

# Resumen

La especialización de hardware ha recibido renovado interés debido al utilization wall, ya que transistores infrautilizados pueden implementar hardware a medida que complemente el procesador principal. Sin embargo, el proceso de diseño se complica y se limita la reutilización. Procesadores de instrucciones para aplicaciones específicas (ASIPs) equilibran rendimiento y reuso, extendiendo un procesador con instruciones especializadas (custom instructions - CIs) para una aplicación, implementadas en unidades funcionales especializadas (SFUs). No obstante, los plazos de comercialización suponen un obstáculo en diseños específicos ya que, si las CIs no se ejecutan con frecuencia, los beneficios de la aceleración no compensan los costes de diseño. La aceleración de un dominio específico incrementa la aplicabilidad de los ASIPs, acelerando diferentes aplicaciones en el mismo hardware, mientras que una SFU reconfigurable y un diseño automatizado pueden resolver los problemas mencionados. En esta tesis, exploramos diferentes alternativas al diseño de CIs que extienden un procesador para acelerar un dominio, mejorando el rendimiento y la eficiencia energética.

Proponemos primero técnicas automatizadas para identificar código acelerable en un dominio. Sin embargo, la identificación se ve dificultada por la diversidad de estilos entre diferentes programas. Por tanto, proponemos identificar en el bloque básico CIs equivalentes utilizando la representación canónica Taylor Expansion Diagram (TED). Con TEDs encontramos no sólo código estructuralmente equivalente, sino también con similitud funcional, en contraposición a la detección isomórfica de grafos acíclicos dirigidos (DAG). Combinamos ambos métodos en una nueva técnica híbrida DAG/TED, que identifica en varias aplicaciones más secuencias representadas por la misma CI. Tras esto, seleccionamos un subconjunto de CIs que puede ser contenido en el área de la SFU. Por la complejidad del problema, proponemos cuatro heurísticas de selección para reducir el espacio de búsqueda y homogeneizar el rendimiento de las aplicaciones. Incluimos estas técnicas en la infraestructura FuSInG y estimamos el rendimiento para un conjunto de benchmarks multimedia. Los resultados muestran que, al

vi Resumen

limitar el área de especialización, la configuración de la SFU con las mayores ganancias incluye una mezcla de CIs específicas tanto para una aplicación como para todo el dominio.

Si nos centramos en CIs más grandes para obtener mayores ganancias, la reutilización se vuelve crítica; sin suficientes equivalencias las CIs no pueden ser generalizadas. Nuestro objetivo es que las CIs compartan parcialmente operaciones, especialmente a través de bloques básicos, y reducir el área de especialización. Por ello, creamos una representación canónica de CIs que cubre varios bloques básicos, Merging Diagram, para mejorar el alcance de la aceleración y facilitar la detección de similitud. Además, proponemos una búsqueda de coincidencias parciales basadas en clustering para identificar CIs de dominio específico parcialmente similares, las cuales derivan generalmente mejor rendimiento. Pero en áreas reducidas, la fusión de CIs induce un coste adicional que penalizaría la eficiencia energética. Así, detectamos fragmentos de CIs y los unimos con grupos de CIs previamente fusionadas con un coste extra mínimo. Usar el rendimiento como el factor decisivo en la selección puede no ser óptimo para disposivos con consumo de energía limitado. Por eso, proponemos un mecanismo de selección basado en programación lineal que equilibra rendimiento y consumo energético. Implementamos estas técnicas en la infraestructura MInGLE y las evaluamos con benchmarks multimedia. Las CIs seleccionadas mejoran notablemente la eficiencia energética y el rendimiento, demostrando que podemos acelerar un dominio cubriendo más código a la vez que reducimos el área de implementación.

# Samenvatting

In de afgelopen jaren heeft hardwarespecialisatie opnieuw aandacht gekregen omdat chips de utilization wall naderen, door de vertraging van het schalen van de voedingsspanning. Gespecialiseerde acceleratoren kunnen profiteren van onderbenutte energiezuinige transistors door de implementatie van aangepaste hardware die de hoofdprocessor aanvullen. Echter, specialisatie verhoogt de complexiteit van het ontwerpproces en beperkt de flexibiliteit wat betreft circuit hergebruik. Applicatie-Specifieke Instructieset Processors (ASIPs) houden rekening met zowel prestaties als flexibiliteit. Ze breiden een "general-purpose processor" uit met aangepaste instructies voor specifieke toepassingen, geïmplementeerd in Specialized Functional Units (SFUs). Het ontwerpproces kan vereenvoudigd worden met geautomatiseerde technieken die gespecialiseerde instructies (Eng: Custom Instructions - CIs) identificeren, selecteren en implementeren. De "timeto-market" is echter een groot probleem bij applicatie-specifieke ontwerpen. Indien CIs niet vaak worden uitgevoerd wegen de voordelen van versnelling niet op tegen de totale ontwerpkosten. Domeinspecifieke versnelling verhoogt de toepasbaarheid van ASIPs, als ze zich kunnen richten op verscheidene toepassingen die op dezelfde hardware in dezelfde tijdsperiode uitgevoerd worden. In dit proefschrift onderzoeken we verschillende benaderingen wat betreft het ontwerp van de CIs die een baseline processor voor domeinspecifieke acceleratie uitbreiden om de herbruikbaarheid te verhogen en om zowel de prestatie als energie-efficiëntie te verbeteren.

Allereerst ontwikkelen we geautomatiseerde technieken om codesequenties die versneld kunnen worden tussen verschillende toepassingen binnen een domein te identificeren. Iedere onafhankelijke sequentie is en nieuwe CI kandidaat die op een SFU kan uitgevoerd worden. CIs die zich richten op een volledig domein zijn een veelbelovende optie. Het verschil in codeerstijlen van verschillende programma's maakt het echter moeilijk om patronen in code te identificeren die door een unieke CI kunnen worden vervangen. Bijgevolg stellen we een analyse op het basisblok voor die gelijkwaardige CIs binnen hetzelfde programma en over de verschillende programma's

VIII SAMENVATTING

heen herkent. We gebruiken hiervoor het Taylor Expansion Diagram (TED) om niet alleen structureel maar ook functioneel gelijkwaardige stukken code te vinden, in tegenstelling tot de vaak toegepaste direct acyclische grafiek (DAG) isomorfisme detectie. We combineren ook beide methodes in een nieuwe hybride DAG/TED-techniek. Dit helpt ons meer sequenties te identificeren uit meerdere toepassingen die op dezelfde CI gemapt kunnen worden. Hierdoor kunnen hogere versnellingen bereikt worden in een kleinere chip area.

Vervolgens, om grotere versnellingen te verkrijgen, richten we ons op CIs die grotere codesequenties dan een basisblok versnellen. Maar als de beschikbare oppervlakte voor de implementatie beperkt is, wordt herbruikbaarheid van de hardware een kritieke factor. Echter, als we niet genoeg overeenkomsten over toepassingen vinden, kunnen CIs niet gegeneraliseerd worden voor een domein. Wij streven ernaar, specifiek tussen basisblokken, om gedeeltelijk gemeenschappelijke operaties te delen tussen CIs om de code die versneld kan worden uit te breiden en om de hardware ruimte die nodig is voor specialisatie te verminderen. Daarom creëren we een nieuwe canonieke representatie van CIs doorheen basisblokken: het Merging Diagram. Deze nieuwe representatie verbetert gelijkheidsdetectie en codedekking ten opzichte van eerdere methoden. Ook introduceren we clustering-based matching die gecombineerd word in samengevoegde CIs om oppervlakte voor implementatie te besparen. Deels samengevoegde domein-specifieke CIs leiden over het algemeen tot betere prestaties dan applicatie-specifieke CIs. Toch zorgt op kleine oppervlaktes het samenvoegen van twee extra CIs voor hoge overheadkosten die energie-efficiëntie kunnen verminderen. Zodus sporen we ook fragmenten van CIs op die slechts gedeelten van eerder gegenereerde en/of samengevoegde CIs bevatten. Wij verbinden de fragmenten van CIs met de bestaande samengevoegde clusters, wat resulteert in minder oppervlakte overhead dan volledige CI samenvoegen. Deze technieken zorgen voor het uitbreiden van de versnellingsmogelijkheden van CIs, omdat er meer code wordt versneld terwijl de ruimte die nodig is voor de CI-implementatie verkleind wordt.

Bij de laatste stap van het CI-ontwerp, wordt een selectie gemaakt van subsets van CIs die passen in de beschikbare SFU-ruimte. De complexiteit van het probleem en de grote CI ontwerpruimte voor een volledig toepassingsdomein maakt de selectie rekenkundig uitdagend. Wij stellen vier score heuristieken voor om snel en efficiënt de ontwerpruimte van CI kandidaten te doorzoeken. De heuristieken rekenen het verwacht gezamenlijk gebruik van CIs binnen en over verschillende programma's uit, met als doel de po-

SUMMARY IN DUTCH IX

tentiële speedup doorheen applicaties te bereiken, waardoor ze geschikt zijn voor domeinspecifieke versnelling. Het gebruiken van de versnelling als de beslissende factor voor CI selectie kan echter niet optimaal zijn voor toestellen met een beperkte vermogensvoorraad. Daarom introduceren we ook energie-efficiëntie tot een nieuwe parameter om rekening mee te houden. We stellen een op geheeltallig programmering gebaseerd selectie mechanisme voor dat streeft naar een evenwicht tussen versnelling en energieverbruik om een hoog-performante en energiezuinige CI-configuratie te selecteren.

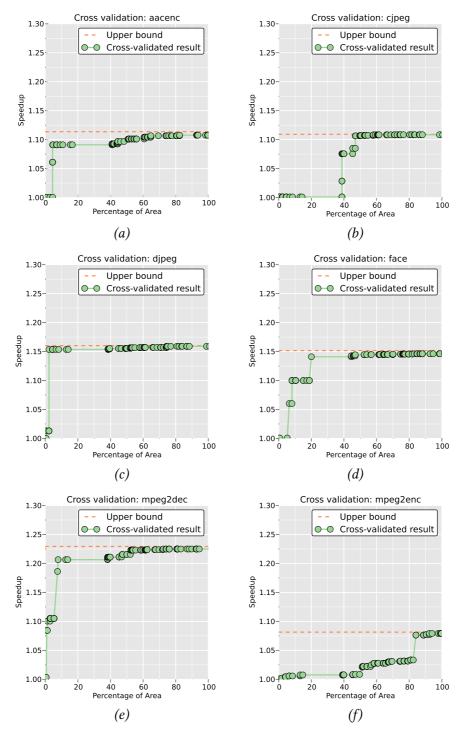

Wij bouwen het exploratie raamwerk FuSInG om codesequenties te extraheren en te analyseren met DAG, TED en Hybrid identificatiemethoden, en om hen te ordenen met score heuristieken. De algemene prestatie wordt geschat op basis van hardware-modellen doorheen het gehele spectrum van applicatie-specifieke en domein-specifieke versnelling in hardware, gebruik makend van een aantal multimedia benchmarks. We evalueren onze canonieke representaties voor het ontwerp van domein-specifieke CIs, en we tonen dat zij essentieel zijn om meer gelijkstellingen dan structurele voorstellingen zoals DAGs over toepassingen te vinden. We onderzoeken ook de tradeoffs van verschillende SFU configuraties om de prestatie van het volledige systeem met beperkt oppervlakte over toepassingen te optimaliseren. Resultaten tonen aan dat, wanneer de beschikbare chip oppervlakte voor specialisatie beperkt is, de SFU aanpassing met de grootste speedups een mix bevat van applicatie- en domeinspecifieke instructies. Daarnaast hebben we de resultaten cross-valideerd om te tonen dat de geïdentificeerde CIs effectief zijn voor ongeziene toepassingen binnen hetzelfde domein, waarmee specialisatie meer algemeen toepasbaar maakt.

Ook creëren we MInGLE, een geautomatiseerd raamwerk dat voorlopige CIs herkent, en deze tot *Merging Diagrams* transformeert. Dit framework voegt, afhankelijk van hun gelijkaardigheidsscore, CIs samen. Het framework selecteert, op basis van de geheeltallig programmering techniek, CI configuraties die efficiënt de beschikbare ruimte voor specialisatie benutten. Experimentele resultaten met een set van media benchmarks tonen aan dat, gemiddeld, versnelling over basisblokken betere speedup en *energie-delay product* (EDP) verbetering bereikt dan over een enkele basisblok (speedup van 1.98× versus 1.48×, EDP verbetering van 3.35× versus 1.67×). Ook over basisblokken, gedeeltelijke *matching* bereikt betere speedup en EDP verbetering in vergelijking met exacte matching, gegeven dezelfde oppervlakte (bijv., voor 1.8% van de oppervlakte, speedup van 1.88× versus 1.73× en EDP verbetering van 3.04× versus 2.53×). Bovendien, het uit-

X Samenvatting

gebreide MInGLE+ raamwerk identificeert, extraheert en selecteert fragmenten van CIs. Matching met fragmenten gebruikt oppervlakte effectiever dan de gedeeltelijke matching (bijv. voor 1% van de oppervlakte, 2× versus 1.63× en EDP verbetering van 3.65× versus 2.35×). De geselecteerde CIs verbeteren de prestatie en energie-efficiëntie van toepassingen uit het multimedia domein aanzienlijk. Dit toont aan dat we een applicatiedomein efficiënt kunnen versnellen met gedeeltelijk gekoppelde CIs.

# **Table of Contents**

| En | glish  | Summary                                 | III |

|----|--------|-----------------------------------------|-----|

| Re | sume   | en en Español                           | v   |

| Ne | ederla | andse Samenvatting                      | VII |

| 1. | Intr   | oduction                                | 1   |

|    | 1.1.   | Motivation and Context                  | 1   |

|    | 1.2.   | Custom Instruction Design               | 3   |

|    | 1.3.   | Key Challenges                          | 4   |

|    | 1.4.   | Key Contributions                       | 6   |

|    | 1.5.   | Key Results                             | 9   |

|    | 1.6.   | Publications                            | 11  |

|    |        | 1.6.1. Other research activities        | 11  |

|    | 1.7.   | Overview                                | 12  |

| 2. | Bacl   | kground                                 | 13  |

|    | 2.1.   | Introduction                            | 13  |

|    | 2.2.   | Custom Instruction Design               | 14  |

|    | 2.3.   | Datapath Accelerators                   | 15  |

|    |        | 2.3.1. The Case for Domain Acceleration | 18  |

|    |        | 2.3.1.1. DSFU Design                    | 19  |

|    |        | 2.3.1.2. Base Processor Integration     | 20  |

|    | 2.4.   | Intermediate Code Representations       | 25  |

|    |        | 2.4.1. Structural Representations       | 25  |

|    |        | 2.4.1.1. IR and SelectionDAG in LLVM    | 25  |

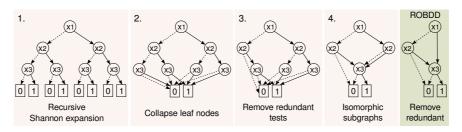

|    |        | 2.4.2. Canonical Diagrams               | 26  |

|    |        | 2.4.2.1. Binary Decision Diagrams       | 26  |

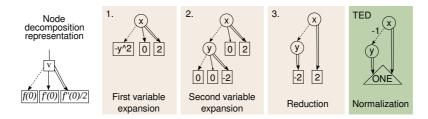

|    |        | 2.4.2.2. Taylor Expansion Diagrams      | 28  |

| 3. | Func  | tionally | / Similar I  | Domain-Specific Instructions               | 33 |

|----|-------|----------|--------------|--------------------------------------------|----|

|    | 3.1.  | Introdu  | iction       |                                            | 33 |

|    | 3.2.  | Contex   | t            |                                            | 34 |

|    | 3.3.  | FuSInC   | 3 Automat    | ic Framework                               | 35 |

|    | 3.4.  | Identifi | cation of (  | CI Candidates with DFG Exploration         | 37 |

|    | 3.5.  | Instruc  | tion Clust   | ering to Discover Equivalences             | 38 |

|    |       | 3.5.1.   | Clusterin    | g with DAG Isomorphism                     | 38 |

|    |       | 3.5.2.   | Clusterin    | g with TED isomorphism                     | 40 |

|    |       | 3.5.3.   | Hybrid T     | ED-DAG clustering                          | 41 |

|    | 3.6.  | Heurist  | tic Selectio | on                                         | 42 |

|    |       | 3.6.1.   |              | on-Specific Scoring                        | 42 |

|    |       | 3.6.2.   | Domain-      | Specific Scoring                           | 43 |

|    |       |          | 3.6.2.1.     | Scoring 1: Normalized Application-Specific | 43 |

|    |       |          | 3.6.2.2.     | Scoring 2: Scaled by Sharing               | 43 |

|    |       |          | 3.6.2.3.     | Scoring 3: Geometric Mean of Sharing       | 44 |

|    |       |          | 3.6.2.4.     | Scoring 4: Random-Scaled Sharing           | 44 |

|    | 3.7.  | Estima   | ting Perfo   | rmance and Area                            | 45 |

|    | 3.8.  | Experi   | mental Set   | up                                         | 46 |

|    | 3.9.  | Results  |              |                                            | 49 |

|    |       | 3.9.1.   | DAG vs 7     | ГЕD vs Hybrid                              | 49 |

|    |       | 3.9.2.   | Domain-      | Specific Scoring                           | 53 |

|    |       | 3.9.3.   | Applicati    | on-Specific vs Domain-Specific Configu-    |    |

|    |       |          | rations .    |                                            | 56 |

|    |       | 3.9.4.   | Custom I     | nstruction Analysis                        | 59 |

|    |       | 3.9.5.   | Cross-Va     | lidation                                   | 61 |

|    | 3.10. | Summa    | ary          |                                            | 64 |

|    |       |          |              |                                            |    |

| 4. |       | -        |              | ain-Specific Instructions                  | 65 |

|    | 4.1.  |          |              |                                            | 65 |

|    | 4.2.  |          |              | ivation                                    | 66 |

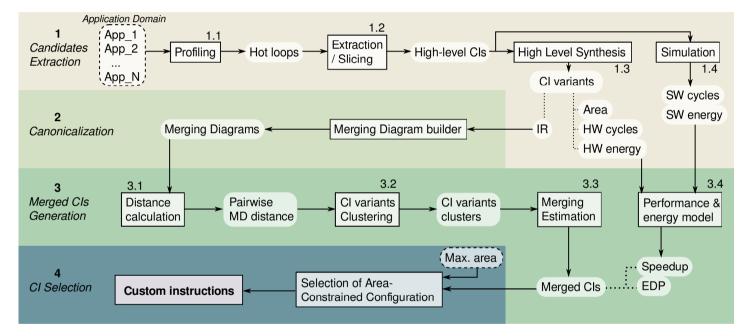

|    | 4.3.  |          |              | rork                                       | 68 |

|    | 4.4.  |          |              | action: From Application Code to Hard-     |    |

|    |       |          |              | n                                          | 68 |

|    | 4.5.  | Canoni   | icalization  | of Custom Instructions using Merging Di-   |    |

|    |       | agrams   |              |                                            | 70 |

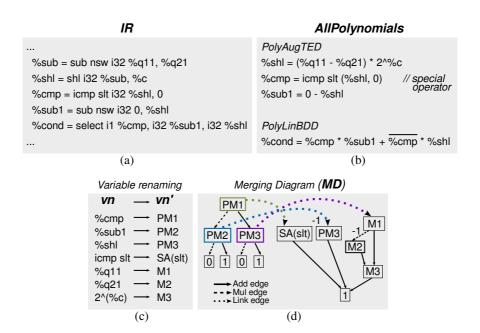

|    |       | 4.5.1.   | 0 0          | Diagram Construction                       | 71 |

|    |       | 4.5.2.   |              | agram of variants                          | 74 |

|    | 4.6.  |          |              | erged Custom Instructions                  | 74 |

|    |       | 4.6.1.   | Distance     | Calculation                                | 74 |

Table of Contents XIII

|    |       | 4.6.2. Clustering Custom Instruction Variants             | 74  |

|----|-------|-----------------------------------------------------------|-----|

|    |       | 4.6.3. Merging Estimation and Modeling                    | 76  |

|    | 4.7.  | Custom Instruction Selection for an Area Constrained Con- |     |

|    |       | figuration                                                | 77  |

|    | 4.8.  | Complexity                                                | 79  |

|    | 4.9.  | Evaluation                                                | 79  |

|    |       | 4.9.1. Experimental Setup                                 | 79  |

|    |       | 4.9.2. Results and Discussion                             | 81  |

|    | 4.10. | Summary                                                   | 84  |

| 5. | Frag  | ments of Domain-Specific Instructions                     | 87  |

|    | 5.1.  | Introduction                                              | 87  |

|    | 5.2.  | Motivation                                                | 88  |

|    | 5.3.  | MInGLE+ Automatic Framework                               | 90  |

|    | 5.4.  | Generation of Custom Instruction Fragments                | 92  |

|    | 5.5.  | Distance and Matching Calculation                         | 94  |

|    | 5.6.  | Custom Instruction Selection with Fragments               | 95  |

|    | 5.7.  | Evaluation                                                | 96  |

|    |       | 5.7.1. Experimental Setup                                 | 96  |

|    |       | 5.7.2. Results                                            | 97  |

|    |       | 5.7.2.1. Speedup and EDP Improvement                      | 97  |

|    |       | 5.7.2.2. Threshold Analysis                               | 101 |

|    |       | 5.7.2.3. Sharing Characterization                         | 103 |

|    | 5.8.  | Summary                                                   | 105 |

| 6. | Cond  | clusion                                                   | 107 |

|    | 6.1.  | Overview                                                  | 107 |

|    | 6.2.  | Future work                                               | 110 |

# List of Figures

| 1.1. | Automated process for CI generation and key contributions.     | 6  |

|------|----------------------------------------------------------------|----|

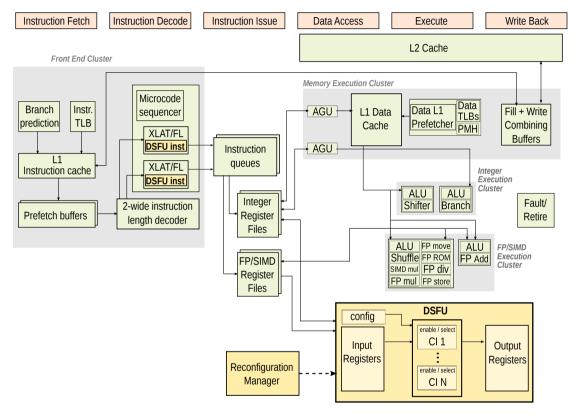

| 2.1. | Generic target architecture with SFU                           | 16 |

| 2.2. | Implementation of a merged CI that executes on a DSFU          | 19 |

| 2.3. | DSFU with a configuration manager to reprogram CIs             | 20 |

| 2.4. | Intel Atom processor pipeline with a tightly-coupled DSFU .    | 21 |

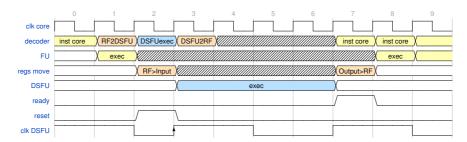

| 2.5. | Chronogram of instructions on a pipeline with a tightly-       |    |

|      | coupled DSFU                                                   | 24 |

| 2.6. | Example of a reduced and ordered BDD construction              | 27 |

| 2.7. | Example of a canonical TED construction                        | 29 |

| 3.1. | Schematic overview of the CI selection and evaluation frame-   |    |

|      | work FuSInG                                                    | 36 |

| 3.2. | Examples of the usage of TEDs for instruction clustering       | 39 |

| 3.3. | Results of benchmark speedup versus CI area for DAG, TED       |    |

|      | and Hybrid methods with domain-specific CIs (part 1/2) $$      | 50 |

| 3.4. | Results of benchmark speedup versus CI area for DAG, TED       |    |

|      | and Hybrid methods with domain-specific CIs (part $2/2$ )      | 51 |

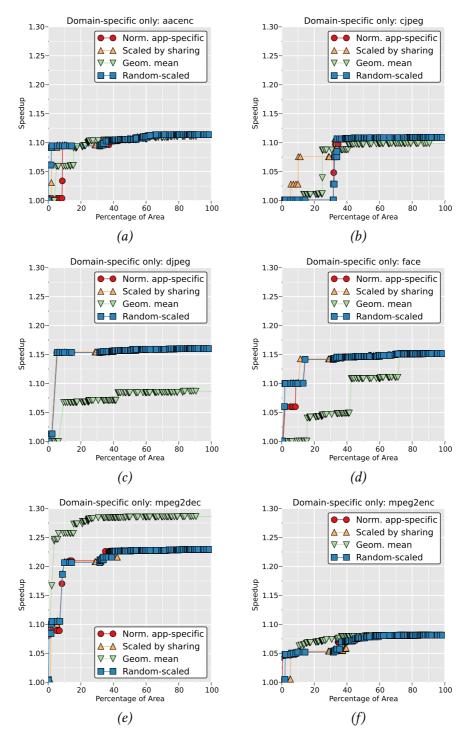

| 3.5. | Results of benchmark speedup versus SFU area for scoring       |    |

|      | techniques with domain-specific CIs (part 1/2)                 | 54 |

| 3.6. | Results of benchmark speedup versus SFU area for scoring       |    |

|      | techniques with domain-specific CIs (part 2/2)                 | 55 |

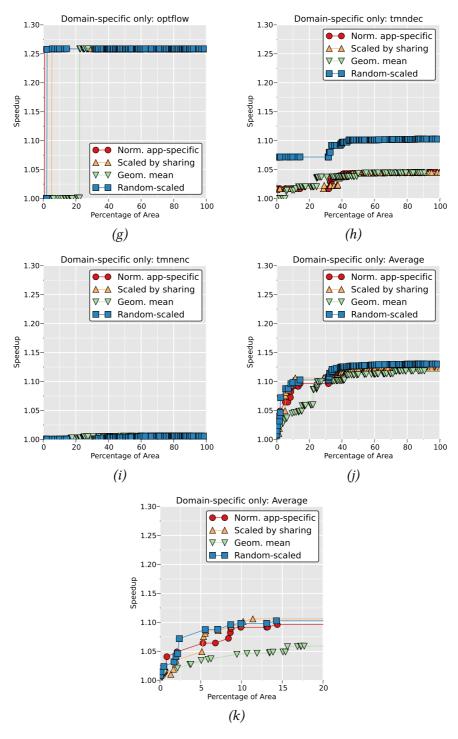

| 3.7. | Results of benchmark speedup versus SFU area using only        |    |

|      | application-specific, application and domain-specific, or only |    |

|      | domain-specific CIs (part 1/2)                                 | 57 |

| 3.8. | Results of benchmark speedup versus SFU area using only        |    |

|      | application-specific, application and domain-specific, or only |    |

|      | domain-specific CIs (part 2/2)                                 | 58 |

| 3.9. | Results of benchmark speedup versus SFU area for cross-        |    |

|      | validation per application using domain-specific CIs (part     |    |

|      | 1/2)                                                           | 62 |

|      |                                                                |    |

XVI LIST OF FIGURES

| 3.10. | Results of benchmark speedup versus SFU area for cross-validation per application using domain-specific CIs (part |     |

|-------|-------------------------------------------------------------------------------------------------------------------|-----|

|       | 2/2)                                                                                                              | 63  |

| 4.1.  | MInGLE framework for the implementation and generation                                                            |     |

|       | of partially-merged CIs                                                                                           | 69  |

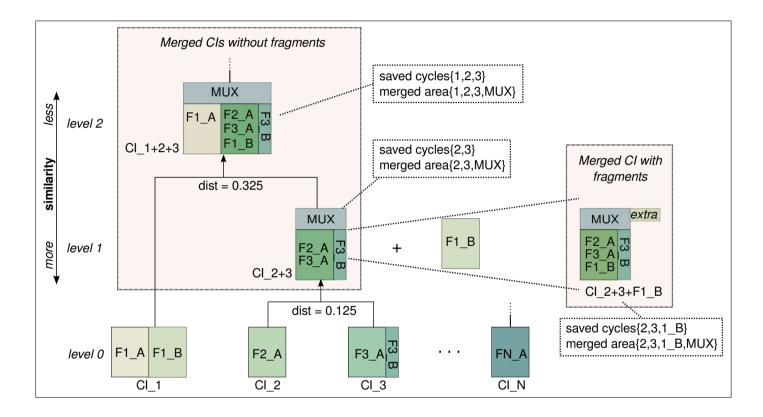

| 4.2.  | Example of Merging Diagram construction                                                                           | 72  |

| 4.3.  | Hierarchical clustering of CIs                                                                                    | 75  |

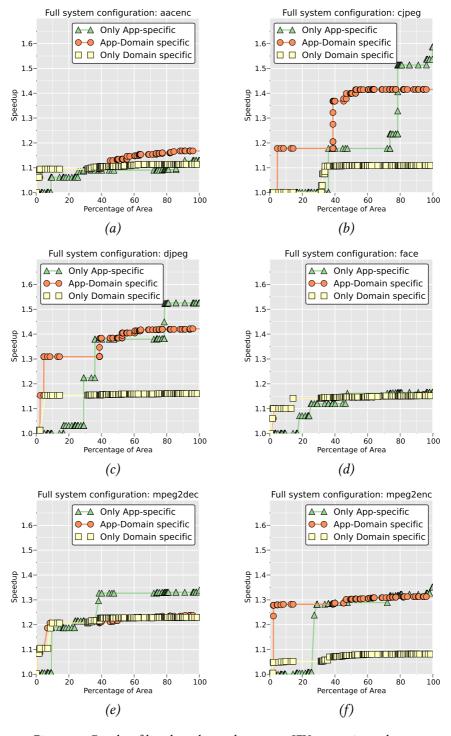

| 4.4.  | Average speedup versus percentage of area occupancy of                                                            |     |

|       | the DSFU for exact and partial matching methods                                                                   | 82  |

| 4.5.  | Average EDP improvement versus percentage of area occu-                                                           |     |

|       | pancy of the DSFU for exact and partial matching methods .                                                        | 82  |

| 4.6.  | Speedup for each benchmark at a limited implementation area                                                       | 83  |

| 4.7.  | EDP improvement for each benchmark at a limited imple-                                                            |     |

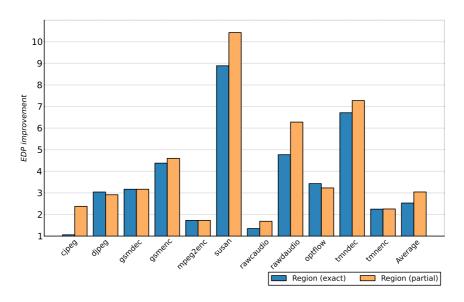

|       | mentation area                                                                                                    | 84  |

| 5.1.  | Example of partial merging without and with CI fragments .                                                        | 89  |

| 5.2.  | MInGLE+ automated framework for the generation of CIs                                                             |     |

|       | with fragments                                                                                                    | 91  |

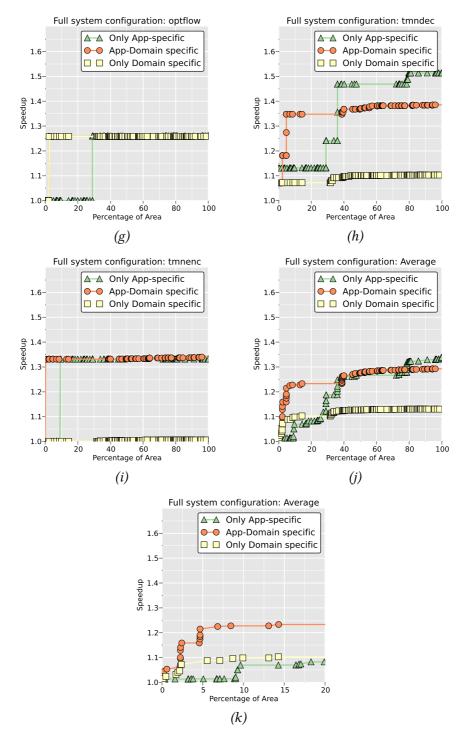

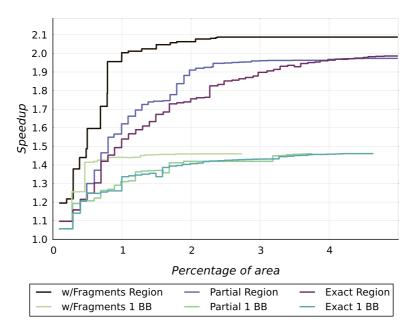

| 5.3.  | Average speedups against increasing area percentages for exact and partial matching and matching with fragments   | 98  |

| 5.4.  | Average EDP improvements against increasing area percen-                                                          | , 0 |

| 0.1.  | tages for exact and partial matching and matching with                                                            |     |

|       | fragments                                                                                                         | 99  |

| 5.5.  | EDP improvement for each benchmark with CIs selected                                                              |     |

|       | across basic blocks with fragments, partial matching and                                                          |     |

|       |                                                                                                                   | 100 |

| 5.6.  | Percentage of area versus average EDP improvement for the                                                         | 100 |

| 0.0.  | -                                                                                                                 | 101 |

| 5.7.  | Characterization of shared FPGA hardware for different area                                                       |     |

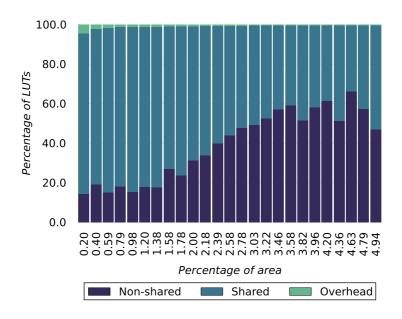

|       |                                                                                                                   | 104 |

| 5.8.  | Characterization of shared FPGA hardware for different area                                                       |     |

|       |                                                                                                                   | 104 |

# List of Tables

| 2.1. | Extensions to the base ISA to operate the DSFU                                                               | 23       |

|------|--------------------------------------------------------------------------------------------------------------|----------|

| 3.1. | Description of the evaluated application benchmarks and their input files                                    | 47       |

| 3.2. | Number of code sequences and CIs found in each application with DAG, TED and Hybrid methods, and the percen- |          |

|      | tage of dynamic instructions covered by them                                                                 | 48       |

| 3.3. | Classification of CIs in a full-system configuration of 5%,                                                  | <b>.</b> |

|      | 10% and 15% of the SPARC area                                                                                | 60       |

| 4.1. | Percentages of area occupancy and EDP improvement for                                                        |          |

|      | different CI implementations                                                                                 | 67       |

| 4.2. | List of the evaluated applications and benchmarks suites                                                     | 80       |

| 5.1. | For each application, number of CIs and CI variants con-                                                     |          |

|      | sidered, the percentage of dynamic instructions covered by                                                   |          |

|      | them, and the number of candidates found                                                                     | 96       |

| 5.2. | Number of candidates in the selection step and time to solve                                                 |          |

|      | the selection problem for different thresholds using mat-                                                    |          |

|      | ching with fragments                                                                                         | 102      |

# List of Acronyms

ARM Advanced RISC Machines

ASIP Application-Specific Instruction Processor

ASIC Application-Specific Integrated Circuit

BDD Binary Decision Diagram

CFG Control Flow Graph

CI Custom Instruction

CMOS Complementary Metal-Oxide-Semiconductor

DAG Directed Acyclic Graph

DFG Data Flow Graph

DMA Direct Memory Access

DSFU Domain-Specific Functional Unit

EDP Energy-Delay Product

FPGA Field Programmable Gate Array

GPU Graphics Processing Unit

HLS High Level Synthesis

INF If-then-else Normal Form

IR Intermediate Representation

ISA Instruction Set Architecture

XX ACRONYMS

ISEF Instruction Set Extension Fabric

ITE If Then Else (operator)

MILP Mixed Integer Linear Programming

MISO Multiple Input Single Output

MIMO Multiple Input Multiple Output

RISC Reduced Instruction Set Computing

ROBDD Reduced Ordered Binary Decision Diagram

SFU Specialized Functional Unit

SMT Simultaneous Multithreading

SRAM Static Random-Access Memory

SSA Static Single Assignment

TED Taylor Expansion Diagram

VLIW Very Long Instruction Word

## 1.1. Motivation and Context

The steady increase of processor speed that Moore's law had been dictating since 1965 [1] was jeopardized when the limits of dimensional scaling started to raise concern among chip makers. The doubling in number of transistors per chip every one and a half to two years that Moore forecasted, and that yields to higher performing circuits, was conceptualized by Dennard [2]. His scaling law establishes that, keeping the electrical field constant, if the chip dimensions scale down, the integration density of transistors on a chip increases, causing circuits to be faster and to reduce power consumption. The constant field scaling paradigm governed the microelectronics industry due to its continuous delivery of higher performance with lower power consumption at lower costs in each semiconductor process generation. However, since the beginning of this century, there has been a slowdown of the energy per transistor switch scaling due to technology limitations. This has been marked as the end of Dennard scaling: voltage scaling cannot keep up with transistor scaling. Now, at each new process generation, integration density increases, but so does the static power leakage. All the transistors on a chip are not powered at the same time to avoid thermal runaway, resulting in an under-utilization of the chip [3–5], also known as dark silicon. Seeing that the times of Dennard scaling are over, we cannot count anymore on power improvements based on traditional technology

advances.

Meanwhile, nowadays market trends demand, more than ever, low-power processors that do not sacrifice performance. Societal needs shape a technological future with energy-efficient intelligent systems integrated in any conceivable gadget. Devices will become increasingly sophisticated, with richer functionalities compared to existing ones, and demanding more optimized solutions. By way of example, smartphone production overtook that of client PCs in 2011; in that year, there were 73 million more smartphones shipped than PCs and tablets together. Also, in May 2015 Google announced that searches on mobile devices surpassed PCs in the US for the first time, and in the UK, mobile handsets now account for 56% of time spent on the Internet. In view of this unstoppable takeover of size-constrained machines, we ask whether the market can keep up with the demand of high functionality with low-power budgets in the advent of *dark silicon*.

Ultimately, we should look for a down-scaled technology that can be efficiently used in modern application domains. The benefits of Moore's shrinking rates could continue without Dennard's rules; with equivalent scaling [6] we use other means than dimensional scaling to maintain improvements in speed and energy. For instance, we can propose new architectures that provide special-purpose functionalities and that are heterogeneously integrated with current processors. Specialized or custom computers are not novel; since the first specialized computer, over 50 years ago [7], the implementation of specific computing units has been extensively studied. But it is now when their benefits over traditional, general-purpose architectures, are becoming more popular. Specialization is seen as a way to cope with the *dark silicon* problem, by increasing the energy efficiency that a low-power budget imposes.

Consequently, custom computing as off-core accelerators, GPUs or incore functional units is a hot topic. Current generation of mobile processors already integrate heterogeneous chips combined with accelerators, which are also becoming more common in server and desktops. Even supercomputer engineers pay now attention to accelerator-based systems; the first three supercomputers in the June 2015 Green500 list<sup>1</sup> rely on special-purpose acceleration with their PEZY-SC cores to provide high energy efficiency. Also, customized computing is in the spotlight of European public funds for research and innovation. The European Commission, under the Horizon 2020 program<sup>2</sup> and the Joint Technology Initiative on Electronic Compo-

<sup>1</sup>http://www.green500.org/lists/green201506

<sup>2</sup>http://ec.europa.eu/research/participants/portal/desktop/en/ opportunities/h2020/topics/9080-ict-04-2015.html

nents and Systems<sup>3</sup>, has granted more than €100 million in 2015 for the development of the next generation of CPUs together with customized and low-power computing. New custom architectures across several application domains are key targets for the European Commission to reinforce Europe's technological competitiveness.

Approaches to custom computing are diverse, therefore accelerating systems may vary depending on the target application domain. Focusing on mobile devices, we still find a plethora of different types of applications that demand performance within constrained power budgets, from common multimedia tasks to voice or facial recognition. Embedded systems equipped with specialized hardware can increase performance and reduce energy consumption, but the implementation details of the customized section are nonetheless a hard choice. For instance, we can obtain high performance accelerating critical parts of an application with Application-Specific Integrated Circuits (ASICs); however, their design cost is expensive, as they lack the flexibility of being programmable. Options that allow hardware reutilization, such as reconfigurable technologies, still need a considerable effort from the designer, which may compromise the total cost and time-to-market of the final product.

Ideally, specialization in embedded systems should yield performance and energy gains close to those of an ASIC, while being flexible and reusable with minimum overhead. New micro-architectural approaches that use prebuilt building blocks are our proposal: extensible processors, also known as Application-Specific Instruction Processors (ASIPs) [8], balance performance and flexibility, and yet maintain the energy efficiency gains of specialization. As they reuse a pre-verified and pre-optimized base processor, the design process is less complex and time-to-market is shorter. The classical ASIP design process augments a general-purpose processor with specialized functional units (SFUs) that execute instructions customized for a particular application. This design process can be automated to identify, select and implement those **custom instructions (CIs)**, and the focus of this dissertation lays, precisely, in those automated methods for CI design.

## 1.2. Custom Instruction Design

Extending processors with SFUs not only reduces the design costs of acceleration. Other benefits of using CIs include the minimization of the cycles spent in the prediction, fetch, decode, scheduling and commit stages of a processor. For each data and instruction fetch, they can perform from

<sup>3</sup>http://www.ecsel-ju.eu/web/index.php

tens to hundreds of operations, cutting down the processor's energy waste. Also, the deployment of CIs is more effective than specializing a complete processor as they are easier to program than bigger off-core accelerators.

SFU customization is the process of discovering new CIs that accelerate the target applications. Within a small and controlled application domain, CIs can be manually detected by studying limited benchmark code, combining frequently executed bundles of operations into one CI. However, with real applications, manual exploration is not an option; the benefits of CIs would not compensate time and effort in design. Therefore, SFU customization is normally an automated process integrated as an alternative path of an application's compilation flow. Automatic CI discovery has attracted extensive attention as research topic since it is far from being a trivial process.

The design of CIs can be broken down into three different phases: the discovery or generation of CIs, the implementation of CIs, and the substitution of generic code by CIs. Out of those three, CI generation is the most important and difficult phase and hence it is our focus here; it is the focus as well for most of the related work. CI generation examines the application code's data-flow graph (DFG) and identifies subgraphs of operations as special instructions. Typically within a single basic block, these subgraphs join tens of operations into a single CI to maximize the overall speedup. Their reusability is commonly very limited; a CI is found at a concrete point of a single application, making them essentially application-specific. CI generation is done in two steps: candidate identification and final selection. First, during candidate identification, subgraphs are identified under architectural constraints. This exploration can take exponential time complexity, thus algorithms to convey this problem are a recurring topic in the literature. Then, the final selection finds the best set of CIs that maximizes the performance in a limited area. How this problem is attacked is also relevant, since it is NP-complete. Therefore, the complete CI design process has substantial research interest, as the acceleration benefits of SFUs can be hard to obtain.

# 1.3. Key Challenges

To accelerate a processor with SFUs, we are compelled to provide simple and fast design methods of CIs that improve performance. However, the general adoption of such a customizing technology depends on a variety of factors: how applicable is the CI generation in a broad context, how energy side-effects are taken into consideration, or how an efficient use of the area is ensured. These points challenge the CI design process and must be adequately addressed.

First, note that the increasing market demand in consumer electronics

imposes strict time-to-market constraints. Also, systems with accelerators are in constant change, since the software that runs on them is regularly modified; therefore, users may want to accelerate applications that were not considered at design time. ASIPs allow programmability to a certain extent to amortize chip design costs, but the common trend is to design CIs for an individual application. As application-specific CIs are not highly reusable, they are sentenced to a short life span at the expense of high investments. In addition, if CIs are not frequently executed, the acceleration benefits will not compensate for the overall energy consumption. Thus, extending the CIs usage to a whole domain of applications can increase the suitability of ASIPs for acceleration. We can then find similar CIs in different programs that can be implemented as only one instruction, improving reusability and economizing hardware resources. But although applications within the same domain often perform similar computations that require the same hardware, we are confronted with two issues: first, exploring several applications at once results in a design space explosion, and second, non-uniform programming styles of different codes may hide their underneath similarities.

Over the past few years, advances in automatic high-level synthesis (HLS) have enabled rapid prototyping of accelerators, which results into another important issue: varying the optimization options, we can obtain many configurations of the same CI. We can have again a design space explosion. Exploration of the different architectural configurations then becomes a sensible task, and automated ways for curbing the design space are key to be able to find a configuration solution that delivers good performance.

While performance speedup is the key metric that traditionally drives CI design, if we only look at performance we may downplay other equally important aspects. Embedded processors have a constrained power budget to watch; therefore, CI design should attempt to balance performance gains with energy efficiency. Furthermore, albeit the SFU hardware area is limited, the expected speedup partially depends on the code coverage of the CI; bigger CIs may deliver better speedups, but all may not fit in the available area. Thus, when several applications are competing for the same resources, we need to be able to prioritize CIs without penalizing overall efficiency. Also, code coverage is subject to the kind of operations executed on the SFU; if branch or predication instructions are left out, as is commonly the case, CIs can only span within a basic block. Small CIs can be counter-productive for performance, but they also have a strong advantage over bigger ones: their reusing degree across applications may be higher and, on average, they yield a more balanced global improvement. All these

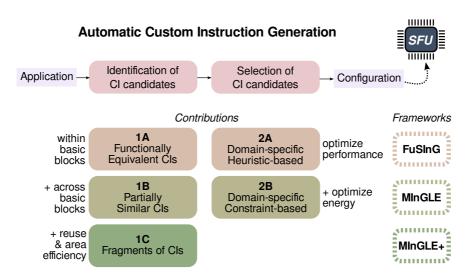

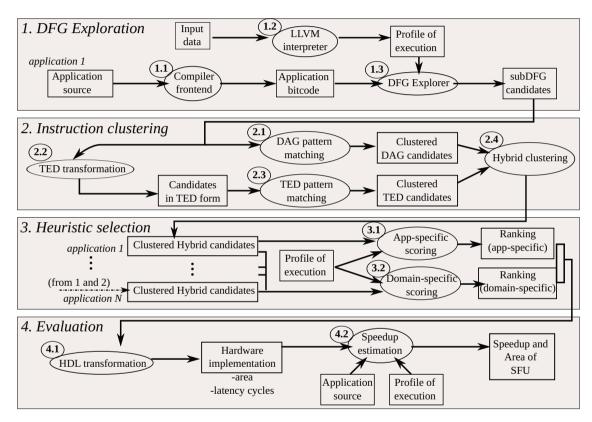

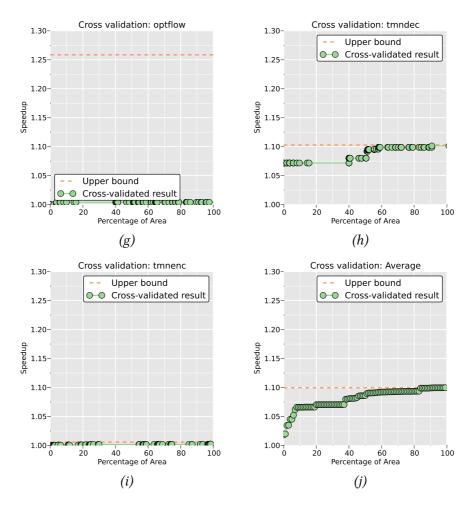

Figure 1.1: The automated process for CI generation and the key contributions of this dissertation.

trade-offs have to be carefully weighed to achieve full efficiency in every sense of the word.

## 1.4. Key Contributions

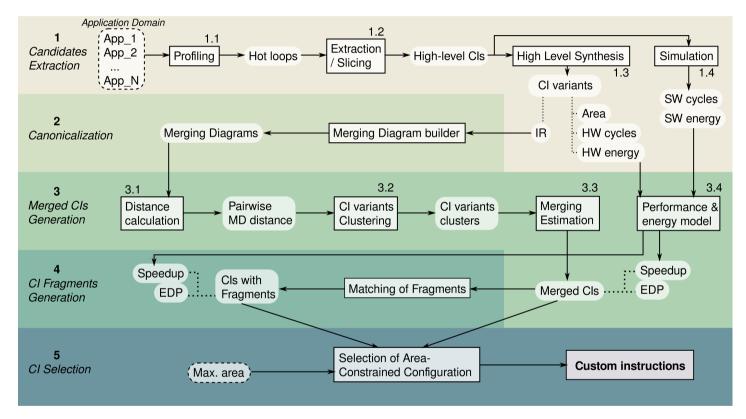

In this dissertation, we explore different approaches for CI generation, focusing on domain-specific acceleration. Figure 1.1 shows, on the top, a high-level schema of the CI generation process; an application is analyzed to identify CI candidates, and a subset of the best candidates is selected to configure the SFU. The figure also shows, on the bottom, our key contributions; we expand and improve the identification in contributions 1-A, B and C, and we provide alternatives to the candidate selection problem in contributions 2-A and B. The contributions are implemented within these frameworks: FuSInG (Functionally Similar Instructions Generator), which implements 1-A and 2-A; MInGLE (Merged Instructions Generator for Large Efficiency), which implements 1-B and 2-B, and MInGLE+, expanded with 1-C.

#### Contribution 1-A:

## Identification of functionally equivalent custom instructions

Limiting ASIPs to application-specific acceleration makes them feasible for only big-volume markets with high returns. Therefore, creating CIs that target a whole domain is an economically viable solution. However, the disparity among coding styles of different programs makes it difficult to identify code patterns that can be represented by a unique CI across applications.

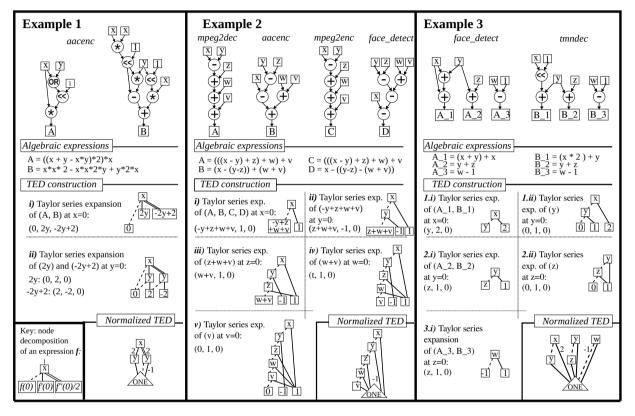

We therefore propose an analysis at the basic block level, complementary to CI candidate identification, that identifies equivalent CIs within the same program and across different programs. We use the Taylor Expansion Diagram (TED) canonical representation to identify common sections of code that can be accelerated by specialized hardware. As TEDs are canonical, we can find not only structurally equivalent pieces of code, but also functionally similar ones. Functional equivalence reveals if CIs perform the same mathematical function, which cannot be guessed with a DFGbased representation. We compare them to a straightforward technique of directed acyclic graph (DAG) isomorphism detection, which essentially reveals whether graphs are similar in shape. We also introduce a new Hybrid DAG/TED technique that combines the best of the traditional graph isomorphism with TEDs. With any of the three techniques, we can identify CI candidates that are specific for either an application or a domain. We find that, with the canonical representation, we can identify more sequences across applications that are mapped to the same CI, thus achieving higher speedups for smaller chip area than the traditionally used DAGs.

# Contribution 1-B: Identification of partially similar custom instructions

Hardware reusability across applications is a critical factor to achieve high and balanced speedups with CIs, yet if there are not enough equivalences, CIs cannot be generalized for a domain. This issue arises more frequently when we target larger code sections to obtain higher performance.

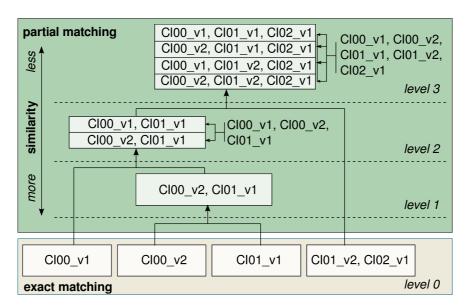

Consequently, we introduce a new canonical representation of CIs across basic blocks, the Merging Diagram, to facilitate similarity detection and improve the code coverage of our CIs. It builds upon the previous Hybrid DAG/TEG representation to provide a more compact representation with predication, spanning CIs across basic blocks. We also propose clustering-based partial matching of code sequences to identify not only those CIs that are functionally equivalent, but also those with partial similarities. Clustered CIs are merged and we quantify their potential improvement of cove-

ring more code while reducing the needed area for the CI implementation. These techniques expand the opportunity for CIs with a limited area budget inside simple processors to accelerate numerous applications from a domain, improving the system's energy efficiency.

# Contribution 1-C: Identification of custom instruction fragments

We have observed that partially-similar domain-specific CIs outperform application-specific ones when the area for implementation is over a given threshold. However, at small areas, we have to rely on application-specific CIs, since the potential gains of merging two CIs do not compensate for the involved overhead.

To solve this, we extend CI merging with an analysis step that detects parts of CIs that can use the existing merged clusters with minimal extra overhead. We call CI fragments to those parts of CIs, since they do not include the full original CI as in the partially similar CIs, but only sections of it. With CI fragments we can improve reutilization of hardware at the most limited areas, because we partially reuse an already merged CI cluster, with minimum additional overhead.

### **Contribution 2-A:**

## Domain-specific heuristic-based selection

At the last step of any CI generation process, the final selection tries to choose a subset of CIs that fits within the available area. The objective of getting an optimal CI group is an NP-complete problem, and thus there exists no known fast solution for it. Also, the CI design space of a whole application domain is big enough to make the task computationally challenging. Typically, approximate algorithms or heuristics are used to solve the selection fast. The main drawback of existing methods is that they target speedup for individual applications. Therefore, their suitability for a whole domain is rather limited, since the gains must be balanced to be fair across applications.

To bridge this gap, we propose four scoring heuristics to quickly and effectively cull the huge CI design space. These heuristics rank potential CIs under the premise that we aim to smoothen the obtained gains across applications. We evaluate them and give insight about their suitability for domain-specific acceleration.

#### **Contribution 2-B:**

## Domain-specific energy-efficient selection

Having proved that the CI selection is appropriate for a domain of applications, we go a step further by introducing energy efficiency into the equation. Speedup is an excellent metric to select a set of CIs that accelerate the applications, hence it has been extensively used in the literature. However, for devices with limited power budgets, focusing only on performance can be detrimental for the design, since we may be introducing power-hungry CIs as well.

This last contribution proposes a constraint-based selection mechanism that, with a novel objective function, balances speedup and energy consumption to fulfill the goal of a energy-efficient design with good performance. We then solve the problem of choosing an energy-efficient set of CIs to fit in limited area while accelerating a domain harmoniously.

## 1.5. Key Results

We summarize here the key results obtained with the frameworks that implement the contributions: FuSInG, MInGLE and MInGLE+.

#### **FuSInG**

We combine the techniques for functional equivalence identification and the scoring heuristics in our automated framework FuSInG, which also estimates performance and area of new acceleration designs. With the framework, we explore the trade-offs between application-specific and domain-specific hardware specialization. Results expose the following insights:

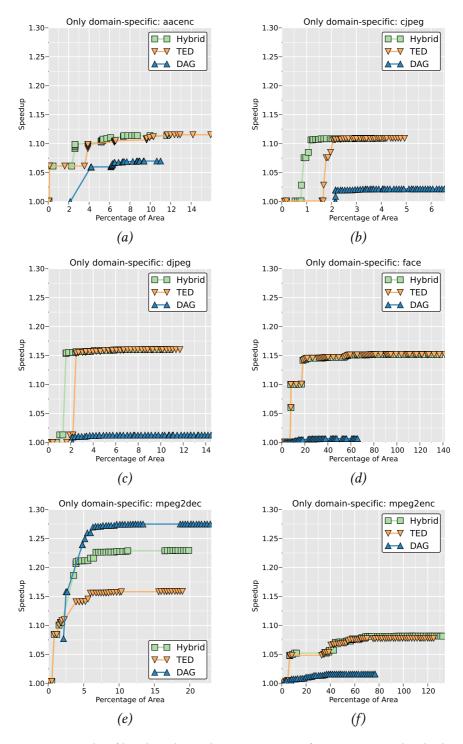

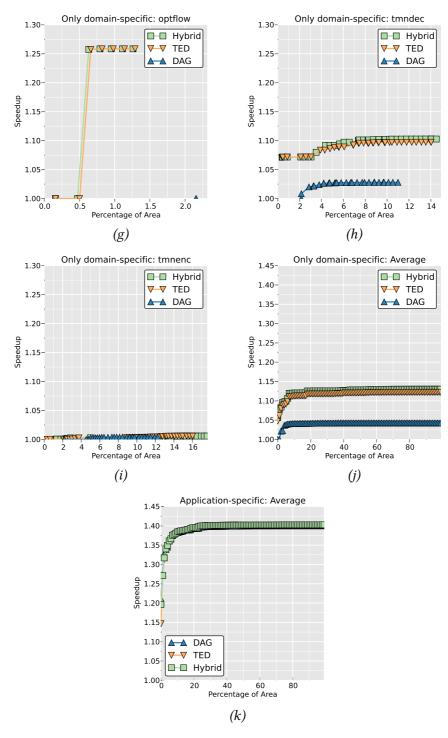

- TED and Hybrid DAG/TED representations identify more hardware acceleration opportunities across applications that are mapped to the same CI, which results in higher speedups for lower area than the traditionally used DAGs.

- While using only application-specific CIs results in the highest possible speedups at unbounded core areas, it is ineffective at small areas. Instead, including domain-specific CIs in the configuration produces the highest possible speedup at small, more realistic core areas, which underlines the importance of identifying CIs that can be shared across applications.

New applications inside a domain can also benefit from CIs already designed for that domain. This suggests that processors with domainspecific functional units can extend their lifetime, making specialization more generally applicable.

#### **MInGLE**

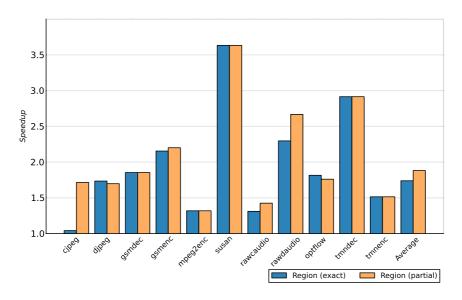

Partial matching of Merging Diagrams expands the acceleration opportunities for domain-specific CIs with a limited area budget, improving the system's energy efficiency. We implement these techniques in our automated framework MInGLE, and we evaluate them with applications from the media domain. We obtain the following key results:

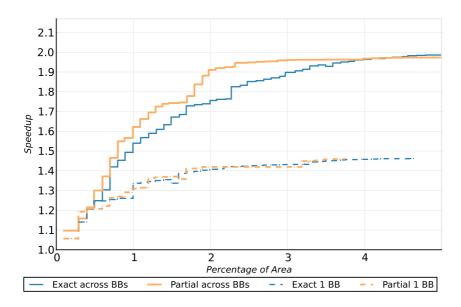

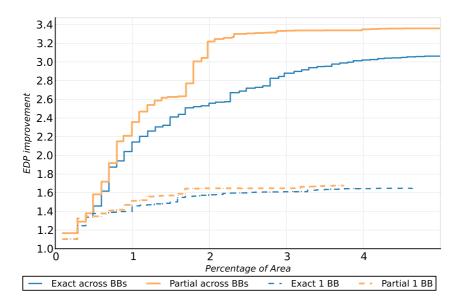

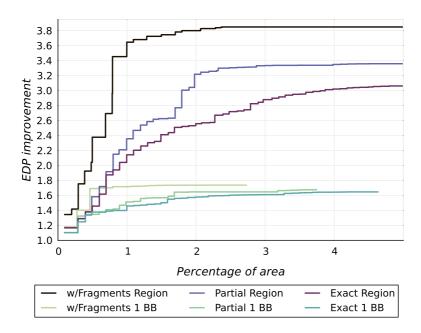

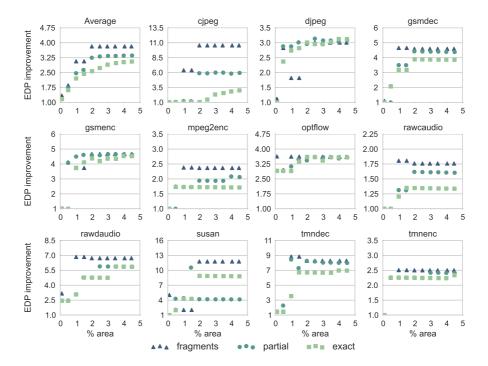

- CIs that cover code beyond the basic block level expand the acceleration opportunities, achieving a maximum average speedup of 1.98× and an energy-delay product (EDP) improvement of 3.35×, a significant gain over CIs within a single basic block (speedup of 1.48× and EDP improvement of 1.67×).

- Partial matching and merging of CIs is crucial for achieving larger speedup and EDP improvement for a limited hardware area. For instance, for 1.8% of the area, the EDP improvement of partial matching reaches 3.04×, higher than a exact matching CI configuration (2.53×).

#### MInGLE+

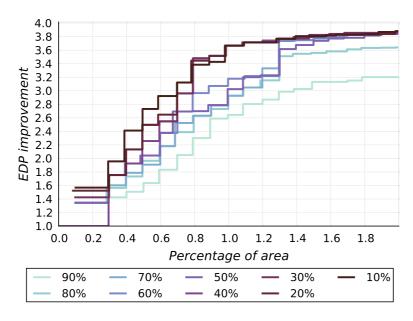

We extend the analysis in MInGLE+ to detect fragments of CIs that can use the existing merged clusters with minimal area overhead. These are the outcomes of this extension:

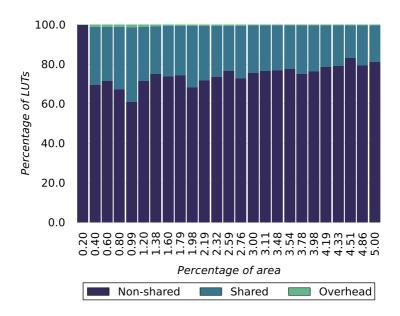

- CI fragments increase the share-out of the circuit components on an SFU at better rate than partial matching, which results in more implementation area available. This means that we achieve a particular energy efficiency at greatly reduced hardware area.

- CI fragments are key to get high performance and energy efficiency at the smallest areas. For example, for 1% of the area, CIs with fragments achieve, on average, a speedup of 2× and an EDP improvement of 3.6×, significantly higher than results for partially matched CIs (speedup of 1.6× and EDP improvement of 3.6×)

Introduction 11

## 1.6. Publications

The above contributions and results are gathered in several international journals and conference proceedings.

Contributions 1-A and 2-A, with focus on the identification and selection of functionally equivalent CIs for an application domain, were published in:

C. González-Álvarez, J. B. Sartor, C. Álvarez, D. Jiménez-González, and L. Eeckhout. "Accelerating an application domain with specialized functional units". *ACM Transactions on Architecture and Code Optimization (TACO)*, Vol 10, No 4, January 2014.

Contributions 1-B and 2-B, that go a step further identifying and selecting domain-specific partially-similar energy-efficient CIs, were published in:

C. González-Álvarez, J. B. Sartor, C. Álvarez, D. Jiménez-González, and L. Eeckhout. "Automatic Design of Domain-Specific Instructions for Low-Power Processors". *Proceedings of the 26th IEEE International Conference on Application-specific Systems, Architectures and Processors (ASAP)*, 2015. Best student paper award.

Contribution 1-C, that extends previous contributions to allow maximum efficiency at small hardware areas, will be published in:

C. González-Álvarez, J. B. Sartor, C. Álvarez, D. Jiménez-González, and L. Eeckhout. "MInGLE: An Efficient Framework for Domain Acceleration using Low-Power Specialized Functional Units". *ACM Transactions on Architecture and Code Optimization (TACO)*, 2015. Under review.

## 1.6.1. Other research activities

In addition to the publications above, we list here other research activities that are not included in this dissertation. These include studies of automatic parallelization for heterogeneous multicores, as well as automatically generated accelerators integration in multicore systems, using the OSCAR source-to-source compiler and runtime. We refer to the original articles for more information:

C. González-Álvarez, Y. Kanehagi, K. Takemoto, Y. Kishimoto, K. Muto, H. Mikami, A. Hayashi, K. Kimura, H. Kasahara. "Automatic

12 Introduction

parallelization with OSCAR API Analyzer: a cross-platform performance evaluation". *IPSJ SIG Notes*, Dec 2012. Information Processing Society of Japan (IPSJ).

C. González-Álvarez, H. Ishikawa, A. Hayashi, D. Jiménez-González, C. Álvarez, K. Kimura and H. Kasahara. "Automatic design exploration framework for multicores with reconfigurable accelerators". 7th HiPEAC Workshop on Reconfigurable Computing (WRC 2013).

K. Kimura, C. González-Álvarez, A. Hayashi, H. Mikami, M. Shimaoka, J. Shirako, H. Kasahara, "OSCAR API v2.1: Extensions for an advanced accelerator control scheme to a low-power multicore API", 17th Workshop on Compilers for Parallel Computing (CPC2013), Lyon, France, Jul. 2013.

## 1.7. Overview

This dissertation is organized as follows.

In Chapter 2, we present the necessary background information on hard-ware acceleration. We give an overview of relevant design techniques and accelerator architectures found in the literature, narrowing the research focus to processors with specialized functional units that execute CIs. We provide the design details of an extended processor that we use in our experiments, and we close the chapter with additional background information on code representations.

We present two key contributions in Chapter 3. First, we introduce the techniques to identify equivalent CIs that can be clustered together. Then, we explain a set of heuristics developed for domain-specific selection. Lastly, we evaluate the presented methodologies for a concrete application domain and present insights on the trade-off of application-specific and domain-specific acceleration.

In Chapter 4, we introduce two more key contributions. We firstly describe the methodology behind the identification of partially-similar CIs, and secondly, the selection mechanism to choose the most efficient configuration of CIs.

We introduce in Chapter 5 our last contribution. We explain the concept of fragments of CIs, presenting the techniques to extract and implement them, and we demonstrate their effectiveness comparing the results against previously proposed methods.

Finally, we present the conclusions of this dissertation in Chapter 6 and we discuss possible future research directions.

## 2.1. Introduction

Hardware acceleration, in its many forms, has emerged as a solution to the demands of high performance and low power in the embedded market. A cost-effective approach is to extend a baseline processor with specialized hardware and its ISA with new custom instructions. The hardware is augmented as functional units, tightly-coupled to the processor's datapath, or coprocessors, intra or outer-core, working as a slave of the main processor.

Datapath specialization can be approached from different perspectives, depending on the focus of the problem. First, from the top-down point of view of creating hardware starting from a set of target applications, we can consider automated design CIs, also known as instruction set extensions. Generally, methods explore the target applications' critical code and translate them to hardware under some constraints. We review those exploration techniques in Section 2.2. From another angle, a bottom-up process involves creating the configurable accelerator design based on architectural expertise. The focus is on creating specialized hardware, possibly configurable, in a less automated way, and then map applications on the hardware to accelerate them. Those architectural proposals are surveyed in Section 2.3, with a specific focus on tightly-coupled accelerators.

Independently from the perspective, hardware acceleration is a complex process that involves more than exploration and architectural design. Once

the design is ready, the actual circuit implementation is a step necessary to prove the suitability of the accelerator. In the latest years, high level synthesis (HLS) programs, such as Vivado HLS [9], have contributed to speed up the implementation step. Different compilation phases are also involved, such as instruction selection once the hardware is created. We do not cover that step in this dissertation, assuming that we can annotate code to substitute lines of code by the accelerating CI. However, Section 2.4 includes background information on compilers' intermediate representations (IRs) and other coding models that are relevant for the upcoming chapters.

## 2.2. Custom Instruction Design

There are many techniques for CI design from the ISA extension perspective that target different objectives and architectures. We provide here a comprehensive survey of evolution of the field through the most important works found in the literature.

The first work on the topic [10] proposes to partition the main problem of instruction generation into *regularity extraction* and *template matching*, which we have previously introduced as generation of CIs, and the substitution of generic code by CIs. They do not provide any implementation of their ideas neither in hardware nor in simulation, but estimate quantitatively the gains depending on the instruction types. In the first description [11] of CI operations types MISO (Multiple Input Single Output) and MIMO (Multiple Input Multiple Output), the authors discuss architectural constraints, such as register ports, in their identification of new instructions within the VLIW compiler Trimaran. Later work [12, 13] formally establish the analysis using Data Flow Graphs (DFG), and the importance of preserving graph convexity. The research focus shifts to the design process problem and clearly separates **identification** and **selection** phases.

Reducing the algorithmic complexity of the design methods is a priority to make the program tractable. Some works rely on heuristics [14] to predict a CI's gain as a function of the instruction's frequency of execution and latency, and on dynamic programming to optimize area usage. Pipelining techniques [15] allow CIs with more inputs and outputs than ports in the register file. A later work by the same authors [16] couple the identification and selection phases, which results in relaxing the constraints and opens up the possibility of approximate techniques and genetic algorithms that are computationally less expensive. Their CIs have any number of outputs, and are evaluated with a software latency model using the hardware measurements of CMOS operators. Others [17] assume that the core processor must be a RISC, which also relaxes constraints. This implies a limited number

of inputs and outputs, which prunes the results, in order to minimize the number of registers used.

A different work for the application-specific embedded market [18] assumes additional storage inside an ARM-based ASIP that allows DMA for some vectors. They select CIs with a merit function based on a latency estimation of memory accesses as a model of SRAM. In their experiments with decoder, filter and encryption applications the CIs are simulated in Simplescalar.

Breaking with the application-specific CI design trends, the generation of domain-specific CIs [19] involves a pattern-matching approach on the data-flow graph using heuristics. They define guide functions for a greedy search that prune the exploration space, using the criticality of the datapath, latency and area as metrics. Most notably, they combine instruction candidates to generalize the accelerators for a simulated VLIW architecture within Trimaran. Also integrated in Trimaran, ASIP extensions for multimedia and cryptography applications based on identification of maximal convex subgraphs within a basic block [20], could be adapted for domainspecific acceleration, since they group graphs that can be implemented with the same hardware and estimate their gain to choose the most promising one. The concept of maximal convex subgraph, or the maximum code coverage that we can get in a basic block without violating any constraint, is further studied [21]. They propose a fast CI identification algorithm [21] based on binary search, that we adapt in our domain-specific framework described in Chapter 3.

Other approaches to solve the CI design problem include applying integer linear programming [22, 23] or constraint programming [24] at only the CI identification, or at any of the CI design steps. Alternatively, other authors [25] apply a predefined set of rules, in a specific order, to obtain a DAG representation of code functionality instead of focusing on the structure of CI subgraphs, which is related to the techniques we see in this dissertation.

## 2.3. Datapath Accelerators

A common accelerator classification [26] categorizes architectures according to their size and proximity to the CPU. On one hand, **loosely-coupled systems**, or **coprocessors**, accelerate coarse-grained tasks with low interaction with the rest of the program, and imply a manual approach to hardware/software partitioning. An example of such a loosely-coupled system is GARP [27], in which a MIPS processor invokes special instructions that run on a custom coprocessor, outside the main core. On the other hand, **tightly-coupled systems**, or **specialized functional units** (SFUs),

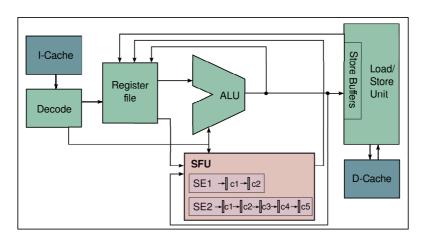

Figure 2.1: Target architecture. The specialized functional unit (SFU) is part of the execution pipeline of an in-order processor core.

accelerate finer-grained tasks and interact directly with the processor flow. Their programming approach is more automated and target a wider range of applications. Our generic architecture falls in the latter category, as it executes the CIs on an SFU that is tightly integrated in the datapath of an in-order general-purpose processor (see Figure 2.1). Our target architecture is a single-issue in-order processor with a configurable pipeline to execute CIs. Each CI runs inside one specialized execution (SE) pipeline of the SFU and takes a variable number of cycles (c). The SFU is multi-cycle and reads and writes data from and to the register file of the core. We do not consider parallel execution of the SFU with the processor's functional units because it has been proven that the performance improvement is not significant enough [28]. Benefits of such a design include a system that maintains precise interrupts, the reduction of instructions in the execution pipeline of the processor core, and the increment of operational and data-level parallelism in the SFU. Those benefits have been studied in the literature, and there are numerous works that implement tightly-coupled accelerating systems.

We find the first proposals of customizable processors with tightly-coupled accelerators [28–30] at the end of the 20<sup>th</sup> century. PRISC [29] is a RISC processor extended with a programmable functional unit. In this architecture, the specialized unit is placed as an additional functional unit in the RISC pipeline and performs combinatorial operations using the processor register file for data transfers. The hardware is responsible for updating the configuration of the programmable unit when a CI requests it. CIs are implemented using a preamble of the RISC instruction format. OneChip [28, 30] also proposes an integrated reconfigurable architecture on a MIPS-like

processor. It extends the PRISC concept to allow pipelining in the programmable functional unit. The first OneChip version [30] is implemented on a prototyping board to test the feasibility of the design. A later work [28] extends OneChip as a RISC superscalar processor allowing dynamic scheduling and reconfiguration, and it is simulated. Chimaera [31] is another example of a tightly-coupled reconfigurable unit that extends a superscalar processor. It is able to perform 9-input 1-output integer operations with the support of a compilation chain that identifies groups of instructions that can run in their reconfigurable functional unit. They provide also subword-parallelism as an attempt to introduce data-level parallelism to their system.

Tensilica's Xtensa processor [32], based on a single-issue RISC and from the late 90's, fills the gap of commercial customizable processors. Although designers could choose different configurations adding new instructions, functional units, register files, peripherals and memory interfaces, any customization had to be done before manufacturing. Xtensa is used as the implementation base for other customizable architectures, such as Stretch's software-configurable processor [33]. It combines a RISC core with an instruction-set extension fabric (ISEF) that interchanges operands through the register file. To program it, the compiler identifies functions that are annotated with pragmas and generates the code to load and execute predefined bitstreams for the ISEF. Nios II from Altera [34] is another example of a commercial customizable processor. It is a soft processor that allows up to 256 custom instructions [35] and virtually unlimited hardware accelerators. While custom instructions are integrated within the processor pipeline, hardware accelerators work as coprocessors.

XiRisc [26] is a load/store architecture with a pipelined run-time configurable datapath called PiCoGa. The PiCoGa is integrated in the processor pipeline, and is connected to the register file, with the possibility of 4-input 2-output registers. The configuration of the PiCoGa can be dynamically scheduled at run time, and some configurations may be already stored inside to avoid configuration overhead times. Another project with a tightly-coupled RISC-based processor is CUSTARD [36]. It features a customizable multithreaded processor with different parameterizations beyond CIs, such as the number of threads, the threading type or the datapath bitwidth. They provide a cycle-accurate simulator to evaluate the application-specific optimizations applied with their compiler CoSy.

DySER [37] accelerates applications by extracting computation that is then run on an accelerating functional unit network, tightly coupled with the processor of choice, such as OpenSPARC [38]. They aim to improve both performance and energy efficiency specializing for concrete applications, providing basic control flow inside the special units, and applying

vectorization.

Broadening the definition of tightly-coupled systems, Beret [39], although not completely integrated in the datapath of an ARM processor, presents an execution engine that is still inside the core. Their Trimaranderived toolchain extracts execution pipelines from small loop bodies based on application trace analysis. They aim to accelerate wider code sections than the above works, and focus on reducing energy consumption in general-purpose computing.

Despite that there exist CIs with memory support [40], the SFU of our target architecture is connected to the processor's register file to simplify the design and to not increase energy consumption beyond the processor's baseline, as many other works also do [26,29,30,36,38]. In this thesis, we also do no consider runtime configuration issues [41,42], since the main problem we solve is centered in the CI design process for an application domain. We do not consider other adaptable parts in the microarchitecture [36] except the SFUs. Instead of annotating the code to be accelerated with pragmas [28,33], we use, as other works do [29–31,36,38], a compilation chain that automatically identifies the CIs that run on the SFU. In our case, this exploration is focused on accelerating an application domain, while keeping the power consumption of the design low. In the rest of this section, we explain the details of a specific implementation of the target architecture that we have just introduced.

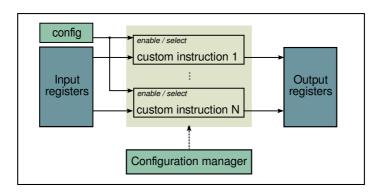

## 2.3.1. The Case for Domain Acceleration

We have seen that the design of an ASIP involves augmenting a general-purpose processor with instructions customized for a particular application. However, if CIs are not frequently executed, the acceleration benefits will not compensate the overall cost and energy consumption of adding new hardware. Domain-specific acceleration increases the applicability of ASIPs, as they can target accelerating several applications that run on the same hardware close in time. Therefore, we present in this section an accelerator model that is reusable across a domain to increase its utilization, thereby improving both performance and energy efficiency.

We focus on the embedded market, where both performance and energy consumption are important factors. Thus, the baseline processor is in-order and low-power. The accelerator, or Domain-Specific Functional Unit (DSFU), is tightly coupled within the general-purpose processor pipeline. This would be technically feasible with the last generation of FPGAs, connecting a processor core to a reconfigurable array seamlessly [42]. We extend the basic ISA with CIs, such as in the traditional ASIP design. These instructions acce-

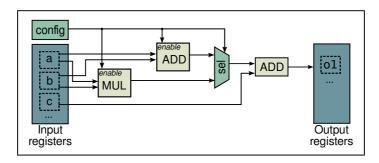

Figure 2.2: Implementation of a merged CI that executes on a DSFU.

lerate the programs by executing a bundle of predicated arithmetic operations in the DSFU.

The rest of this section presents the specification of the DSFU design and its integration in an Intel Atom processor's pipeline.

## 2.3.1.1. DSFU Design