## **Binary Redundancy Elimination**

Author: Manel Fernández Advisor: Roger Espasa

Thesis submitted in fulfillment of the requirements for the degree of *Doctor en Informática*

UNIVERSITAT POLITÈCNICA DE CATALUNYA Department of Computer Architecture Barcelona, Spain

January 2005

© Copyright by Manel Fernández 2005

A mis padres y hermanos. Y muy especialmente, a Laura. iv

## Abstract

Two of the most important performance limiters in today's processor families comes from solving the *memory wall* and handling *control dependencies*. In order to address these issues, *cache memories* and *branch predictors* are well-known hardware proposals that take advantage of, among other things, exploiting both *temporal memory reuse* and *branch correlation*. In other words, they try to exploit the *dynamic redundancy* existing in programs. This redundancy comes partly from the way that programmers write source code, but also from limitations in the compilation model of traditional compilers, which introduces unnecessary memory and conditional branch instructions. We believe that today's optimizing compilers should be very aggressive in optimizing programs, and then they should be expected to optimize a significant part of this redundancy away.

On the other hand, optimizations performed at link-time or directly applied to final program executables have received increased attention in recent years, due to limitations in the traditional compilation model. First, even though performing sophisticated interprocedural analyses and transformations, traditional compilers do not have the opportunity to optimize the program as a whole. A similar problem arises when applying profile-directed compilation techniques: large projects will be forced to re-build every source file to take advantage of profile information. By contrast, it would be more convenient to build the full application, instrument it to obtain profile data and then re-optimize the final binary without recompiling a single source file.

In this thesis we present new profile-guided compiler optimizations for eliminating the redundancy encountered on executable programs at binary level (i.e.: binary redundancy), even though these programs have been compiled with full optimizations using a "state-of-the-art" commercial compiler. In particular, our Binary Redundancy Elimination (BRE) techniques are targeted at eliminating both redundant memory operations and redundant conditional branches, which are the most important ones for addressing the performance issues that we mentioned above in today's microprocessors. These new proposals are mainly based on Partial Redundancy Elimination (PRE) techniques for eliminating partial redundancies in a path-sensitive fashion. Our results show that, by applying our optimizations, we are able to achieve a 14% execution time reduction in our benchmark suite.

In this work we also review the problem of *alias analysis* at the executable program level, identifying why memory disambiguation is one of the weak points of object code modification. We then propose several alias analyses to be applied in the context of link-time or executable code optimizers. First, we present a *must*-alias analysis to recognize memory dependencies in a *path-sensitive* fashion, which is used in our optimization for eliminating redundant memory operations. Next, we propose two *speculative may*-alias data-flow algorithms to recognize memory independencies. These may-alias analyses are based on introducing unsafe speculation at analysis time, which increases alias precision on important portions of code while keeping the analysis reasonably cost-efficient. Our results show that our analyses prove to be very useful for increasing memory disambiguation accuracy of binary code, which turns out into opportunities for applying optimizations.

All our algorithms, both for the analyses and the optimizations, have been implemented within a *binary optimizer*, which overcomes most of the existing limitations of traditional source-code compilers. Therefore, our work also points out the most relevant issues of applying our algorithms at the executable code level, since most of the high-level information available in traditional compilers is lost.

# Acknowledgments/Agradecimientos

I want to thank all the people who provided guidance, help, and support while I was working on this thesis.

Most of all, I am indebted to my advisor Roger Espasa, for his continuous support, great patience, and specially for let me enough freedom to do things I wanted to do the way I thought they should be done. Without his guidance and encouragement this thesis would have never been possible.

I would also like to thank the members of my thesis committee for the effort they put into judging this thesis. Special mention to Professor Jordi Cortadella, for his suggestions and helpful discussions on some ideas that significantly improved this document.

I am specially indebted to Professors Saumya Debray and Cristina Cifuentes, for the chance to work with them, and for their kindness hosting me during my stays at the University of Arizona and Sun Microsystems, respectively. The numerous insightful discussions with them about different research topics have definitely contributed this thesis. My gratitude also to Brian Lewis, Sri Nair, Greg Wright, and everyone at Sun Microsystems Laboratories. And of course, to Emiliano Bartolomé, Malen Flaquer, and Pere Obrador, for making me feel at home during my visits to California.

I am also specially grateful to the people at the Department of Computer Architecture. Thanks to Professors Eduard Ayguadé, Antonio González, and Mateo Valero, for their encouragement in so many different situations, I would also thank to Agustin Fernández, Jordi García, Toni Juan, Josep Lluis Larriba, and Josep Llosa, for their help and friendship along these years. Special thanks to Xavier Vera, who carefully read a draft of this thesis and suggested many improvements. My gratitude also to the administration, LCAC, and CEPBA staff, for their excellent administration an technical support.

Finally, I would like to express my thanks to everyone I have not cited above but has help me, directly or not, in the long way until this thesis has been finished.

Todo proceso sufre una gran influencia del entorno donde se elabora. Por ello, las personas que me han rodeado en los últimos años, tanto a nivel profesional como a nivel personal, han influido en gran medida en la elaboración de este trabajo. Quiero expresar mi agradecimiento a todos los que han sido mis compañeros y amigos en el Departamento de Arquitectura de Computadores, muy especialmente a Jaume Abella, Yolanda Becerra, Ramon Canal, Jesús Corbal, Julita Corbalán, Pepe González, Larisa Miranda, Daniel Ortega, Maite Ortega, Jesús Sanchez, Gladys Utrera y Xavi Vera. Con ellos he compartido no sólo un entorno de trabajo extraordinario, sino también incontables confidencias y vivencias que no podré olvidar nunca. Todo hubiera sido mucho más difícil sin ellos.

Este trabajo no podría haberse desarrollado sin una base sólida en el aspecto educativo, personal y humano. Por ello quiero agradecer a mi familia, especialmente a mis padres Domingo y Josefa, y a mis hermanos Miguel Angel y Merche, el apoyo y cariño que siempre me han brindado. Sin ellos nunca habría llegado tan lejos.

Por último, mi más profundo agradecimiento a Laura, más de lo que aquí podría expresar con palabras. Por su apoyo y ánimo incondicionales, y ante todo por darme la estabilidad necesaria para acabar este trabajo. En definitiva, por todo el amor, el cariño y la alegría que he recibido de ella durante estos años.

This work has been supported by the Intel Labs Barcelona (BSSAD), the Spanish Ministry of Science and Technology, and the European Union (FEDER funds), under grants PN98 46057403-1, CYCIT TIC98-0511 and TIC2001-0995-C02-01.

# Contents

| A  | bstra | ct     |                                                  |       |   | v              |

|----|-------|--------|--------------------------------------------------|-------|---|----------------|

| A  | cknov | wledgn | nents/Agradecimientos                            |       |   | vii            |

| C  | onter | ıts    |                                                  |       |   | ix             |

| Li | st of | Figur  | es                                               |       | : | xiii           |

| Li | st of | Table  | s                                                |       |   | xv             |

| 1  | Intr  | oducti | ion                                              |       |   | 1              |

|    | 1.1   | Motiva | ation                                            |       |   | 2              |

|    |       | 1.1.1  | Binary redundancy                                |       |   | 3              |

|    |       | 1.1.2  | Binary optimizations                             |       |   | 5              |

|    | 1.2   | Thesis | overview                                         |       |   | 7              |

|    |       | 1.2.1  | Thesis objectives                                |       |   | $\overline{7}$ |

|    |       | 1.2.2  | Structure of this document                       | <br>• | • | 8              |

| 2  | Bac   | kgrou  | nd and related work                              |       |   | 11             |

|    | 2.1   | Prelin | ninaries                                         |       |   | 12             |

|    |       | 2.1.1  | Control flow graph                               |       |   | 12             |

|    |       | 2.1.2  | Basic blocks                                     |       |   | 12             |

|    |       | 2.1.3  | Instruction set representation                   | <br>• |   | 13             |

|    | 2.2   | Data-f | flow analysis                                    |       |   | 14             |

|    |       | 2.2.1  | Liveness analysis                                |       |   | 16             |

|    |       | 2.2.2  | Use-def chains                                   |       |   | 17             |

|    |       | 2.2.3  | Alias analysis                                   |       |   | 17             |

|    |       |        | 2.2.3.1 Alias analysis by instruction inspection | <br>• |   | 18             |

|    |       |        | 2.2.3.2 Residue-based global alias analysis      | <br>• |   | 19             |

|    |       | 2.2.4  | Abstract interpretation                          |       |   | 20             |

|                            | 2.3 | Compiler optimizations |                                                           |  |

|----------------------------|-----|------------------------|-----------------------------------------------------------|--|

| 2.3.1 Base optimizations . |     | 2.3.1                  | Base optimizations                                        |  |

|                            |     |                        | 2.3.1.1 Optimization of constant expressions              |  |

|                            |     |                        | 2.3.1.2 Dead/unreachable code elimination                 |  |

|                            |     |                        | 2.3.1.3 Copy propagation and register renaming            |  |

|                            |     |                        | 2.3.1.4 Procedure inlining and cloning                    |  |

|                            |     |                        | 2.3.1.5 Code positioning                                  |  |

|                            |     |                        | 2.3.1.6 Code scheduling                                   |  |

|                            |     | 2.3.2                  | Profile-guided optimizations                              |  |

|                            |     |                        | 2.3.2.1 Types of profile information                      |  |

|                            |     |                        | 2.3.2.2 Profile-guided classical optimizations            |  |

|                            |     | 2.3.3                  | Eliminating program redundancies                          |  |

|                            |     |                        | 2.3.3.1 Partial redundancy elimination                    |  |

|                            |     |                        | 2.3.3.2 Register promotion                                |  |

|                            |     |                        | 2.3.3.3 Elimination of conditional branches               |  |

|                            | 2.4 | Binar                  | y optimizers                                              |  |

|                            |     | 2.4.1                  | Advantages of performing binary optimizations             |  |

|                            |     | 2.4.2                  | Related work                                              |  |

| 3                          | Exp | oerime                 | ental environment 37                                      |  |

|                            | 3.1 | Targe                  | t environment                                             |  |

|                            |     | 3.1.1                  | Target platform    38                                     |  |

|                            |     | 3.1.2                  | Compilation environment                                   |  |

|                            |     |                        | 3.1.2.1 Native compilation                                |  |

|                            |     |                        | 3.1.2.2 Getting profile information                       |  |

|                            |     | 3.1.3                  | Execution environment                                     |  |

|                            |     | Exper                  | imental framework                                         |  |

|                            |     | 3.2.1                  | Binary optimization environment                           |  |

|                            |     |                        | 3.2.1.1 Optimization phases                               |  |

|                            |     |                        | 3.2.1.2 Enhancing optimizer capabilities                  |  |

|                            |     |                        | 3.2.1.3 Execution threshold                               |  |

|                            |     | 3.2.2                  | Simulation environment                                    |  |

|                            | 3.3 | Bench                  | umark suite                                               |  |

|                            |     | 3.3.1                  | SPECint95 characterization                                |  |

|                            |     |                        |                                                           |  |

|                            |     |                        | <b>3.3.1.1</b> Compilation time                           |  |

|                            |     |                        | 3.3.1.1Compilation time483.3.1.2Static characterization49 |  |

|                            |     |                        |                                                           |  |

| 4 | Alia | Alias analysis 5                                                                                                                                        |            |  |  |  |

|---|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|

|   | 4.1  | Introduction                                                                                                                                            | 56         |  |  |  |

|   | 4.2  | Path-sensitive <i>must</i> -alias analysis                                                                                                              | 57         |  |  |  |

|   |      | 4.2.1 Alias analysis by instruction inspection                                                                                                          | 59         |  |  |  |

|   |      | 4.2.2 Path-sensitive memory disambiguation                                                                                                              | 60         |  |  |  |

|   |      | 4.2.3 Evaluation $\ldots \ldots \ldots$ | 62         |  |  |  |

|   |      | 4.2.3.1 Measuring static precision $\ldots \ldots $                               | 62         |  |  |  |

|   | 4.3  | Speculative <i>may</i> -alias analysis                                                                                                                  | 64         |  |  |  |

|   |      | 4.3.1 Region-based speculative alias analysis                                                                                                           | 35         |  |  |  |

|   |      | 4.3.1.1 Dealing with memory contents $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots $                                                  | 68         |  |  |  |

|   |      | 4.3.1.2 Reasoning about data-flow analysis correctness $\ldots \ldots \ldots $                                                                          | <u>5</u> 9 |  |  |  |

|   |      | 4.3.2 Profile-guided speculative alias analysis                                                                                                         | <u>5</u> 9 |  |  |  |

|   |      | 4.3.3 Recovery-based usage of speculative alias analysis                                                                                                | 71         |  |  |  |

|   |      | 4.3.4 Evaluation $\ldots \ldots $                     | 72         |  |  |  |

|   |      | 4.3.4.1 Measuring static precision                                                                                                                      | 73         |  |  |  |

|   |      | 4.3.4.2 Measuring misspeculation rate                                                                                                                   | 75         |  |  |  |

|   | 4.4  | Related work                                                                                                                                            | 79         |  |  |  |

|   | 4.5  | Conclusions                                                                                                                                             | 30         |  |  |  |

| _ |      |                                                                                                                                                         |            |  |  |  |

| 5 |      |                                                                                                                                                         | <b>31</b>  |  |  |  |

|   | 5.1  |                                                                                                                                                         | 32         |  |  |  |

|   | 5.2  |                                                                                                                                                         | 33         |  |  |  |

|   |      | 0 0                                                                                                                                                     | 33         |  |  |  |

|   | ~ 0  |                                                                                                                                                         | 34         |  |  |  |

|   | 5.3  |                                                                                                                                                         | 35         |  |  |  |

|   |      |                                                                                                                                                         | 37         |  |  |  |

|   | 5.4  | 0                                                                                                                                                       | 38         |  |  |  |

|   |      | 5.4.1 Eliminating close redundancy                                                                                                                      |            |  |  |  |

|   |      |                                                                                                                                                         | 39         |  |  |  |

|   | 5.5  |                                                                                                                                                         | )1         |  |  |  |

|   |      |                                                                                                                                                         | )1         |  |  |  |

|   |      |                                                                                                                                                         | 92         |  |  |  |

|   |      | •                                                                                                                                                       | )3         |  |  |  |

|   |      | ·                                                                                                                                                       | )3         |  |  |  |

|   |      | v                                                                                                                                                       | 95         |  |  |  |

|   | •    | •                                                                                                                                                       | 96         |  |  |  |

|   | 5.6  |                                                                                                                                                         | 97         |  |  |  |

|   |      | 5.6.1 A path-sensitive formulation for partial LRE                                                                                                      | 97         |  |  |  |

|   |     | 5.6.2 Eliminating dead stores                             |  |  |  |  |  |

|---|-----|-----------------------------------------------------------|--|--|--|--|--|

|   | 5.7 |                                                           |  |  |  |  |  |

|   |     | 5.7.1 Reduction in number of dynamic references           |  |  |  |  |  |

|   |     | 5.7.2 MRE breakdown of static references                  |  |  |  |  |  |

|   |     | 5.7.3 Effects of procedure inlining on MRE                |  |  |  |  |  |

|   |     | 5.7.4 Compilation time                                    |  |  |  |  |  |

|   |     | 5.7.5 Speed up using MRE                                  |  |  |  |  |  |

|   |     | 5.7.6 Microarchitecture impact of using MRE               |  |  |  |  |  |

|   |     | 5.7.7 Effects of load latency                             |  |  |  |  |  |

|   | 5.8 | Related work                                              |  |  |  |  |  |

|   | 5.9 | Conclusions                                               |  |  |  |  |  |

| 6 | Con | ditional branch redundancy elimination 113                |  |  |  |  |  |

| Ū | 6.1 | Introduction                                              |  |  |  |  |  |

|   | 6.2 | Dynamic conditional branch redundancy                     |  |  |  |  |  |

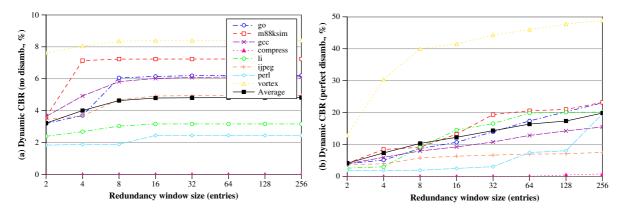

|   |     | 6.2.1 Detecting branch correlation                        |  |  |  |  |  |

|   |     | 6.2.2 Measuring conditional branch redundancy             |  |  |  |  |  |

|   | 6.3 | CBRE on executable code                                   |  |  |  |  |  |

|   |     | 6.3.1 Eliminating close redundancy                        |  |  |  |  |  |

|   |     | 6.3.2 Eliminating distant redundancy                      |  |  |  |  |  |

|   | 6.4 | Path-sensitive profile-guided CBRE                        |  |  |  |  |  |

|   |     | 6.4.1 Eliminating close redundancy                        |  |  |  |  |  |

|   |     | 6.4.2 Eliminating distant redundancy                      |  |  |  |  |  |

|   | 6.5 | Evaluation                                                |  |  |  |  |  |

|   |     | 6.5.1 Reduction in number of dynamic conditional branches |  |  |  |  |  |

|   |     | 6.5.2 Effects of procedure inlining on CBRE               |  |  |  |  |  |

|   |     | 6.5.3 Compilation time                                    |  |  |  |  |  |

|   |     | 6.5.4 CBRE impact in code growth                          |  |  |  |  |  |

|   |     | 6.5.5 Speed up using CBRE                                 |  |  |  |  |  |

|   | 6.6 | Related work                                              |  |  |  |  |  |

|   | 6.7 | Conclusions                                               |  |  |  |  |  |

| 7 | Con | clusions and future directions 135                        |  |  |  |  |  |

|   | 7.1 | Introduction                                              |  |  |  |  |  |

|   | 7.2 | Lessons and observations                                  |  |  |  |  |  |

|   | 7.3 | Summary of contributions                                  |  |  |  |  |  |

|   | 7.4 | Future directions                                         |  |  |  |  |  |

|   |     |                                                           |  |  |  |  |  |

### Bibliography

# List of Figures

| 1.1  | Example of memory and conditional branch redundancies, and its elimination.         | 4  |

|------|-------------------------------------------------------------------------------------|----|

| 2.1  | Sample code where different definitions are reaching a use                          | 17 |

| 2.2  | Techniques for may-alias disambiguation by instruction inspection.                  | 19 |

| 2.3  | Example of profile-guided optimization.                                             | 26 |

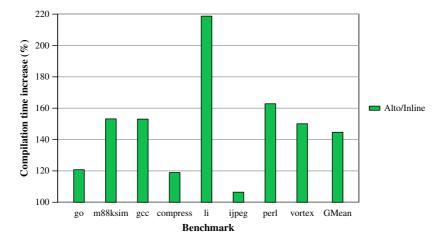

| 3.1  | Effect of applying inlining in Alto compilation time.                               | 48 |

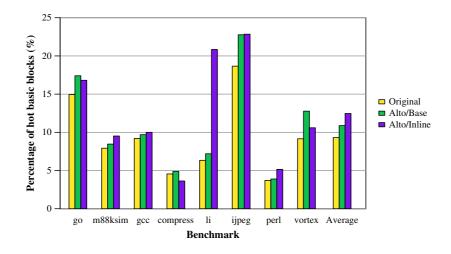

| 3.2  | Percentage of hot basic blocks for the SPECint95 programs                           | 50 |

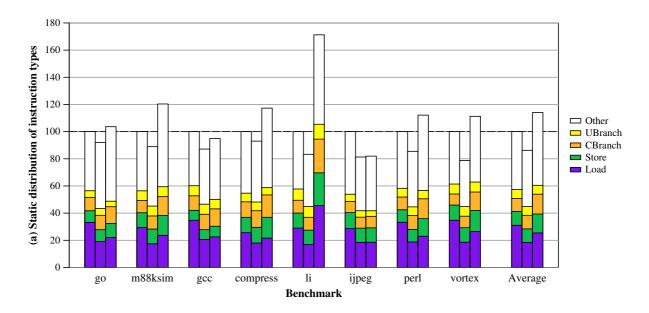

| 3.3  | Static distribution of instruction types for the SPECint95 programs                 | 51 |

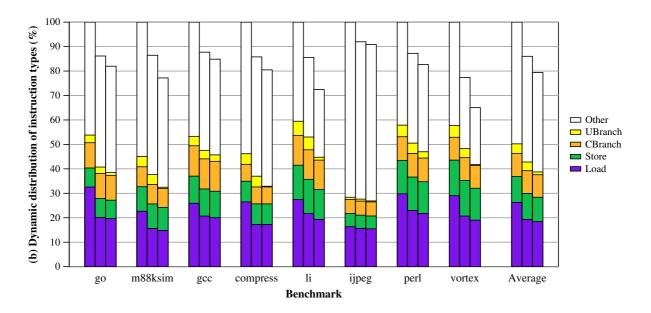

| 3.4  | Dynamic distribution of instruction types for the SPECint95 programs                | 52 |

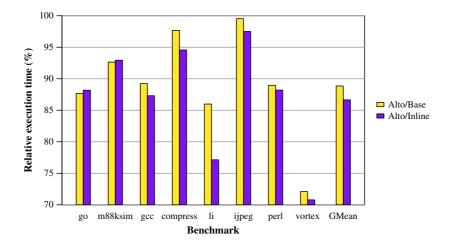

| 3.5  | Effect of Alto optimizations in actual execution time                               | 53 |

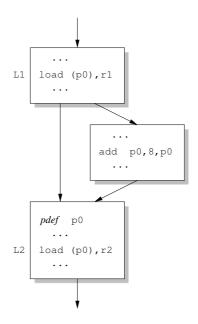

| 4.1  | Example of binary redundancy from an alias analysis point of view.                  | 56 |

| 4.2  | Example of memory references where general inspection fails for disambiguation.     | 58 |

| 4.3  | Path-sensitive memory disambiguation scheme.                                        | 63 |

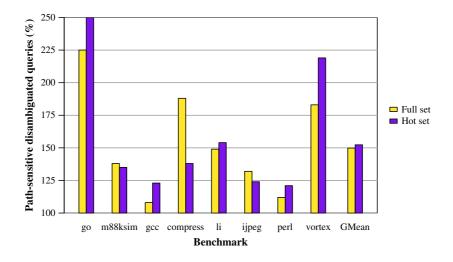

| 4.4  | Precision of the path-sensitive must-alias memory disambiguation scheme             | 64 |

| 4.5  | Sample code where pointer information is lost.                                      | 66 |

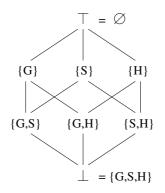

| 4.6  | Region-based alias analysis lattice.                                                | 67 |

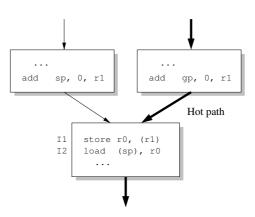

| 4.7  | Different definitions are reaching a use, but there is a more likely executed path. | 70 |

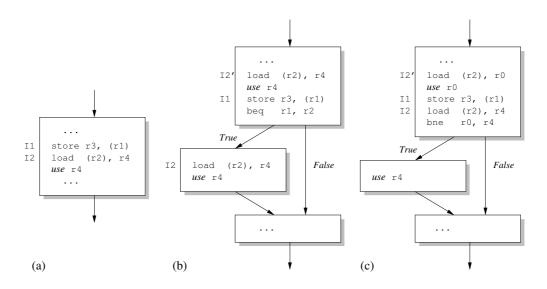

| 4.8  | Reordering memory operations                                                        | 71 |

| 4.9  | Speculative memory disambiguation scheme                                            | 73 |

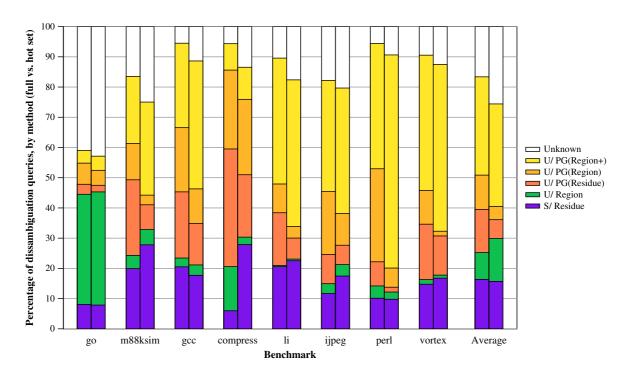

| 4.10 | Breakdown of disambiguation queries, by path-insensitive alias analysis method.     | 74 |

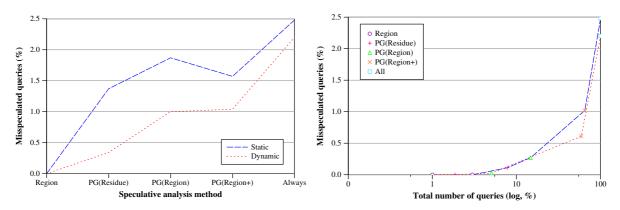

| 4.11 | Percentage of misspeculated queries for every alias analysis methods                | 78 |

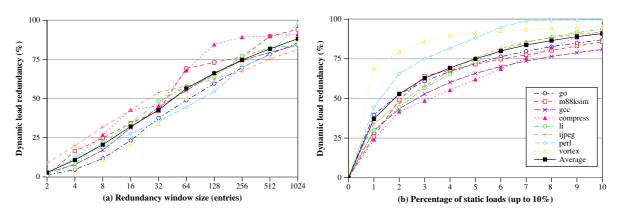

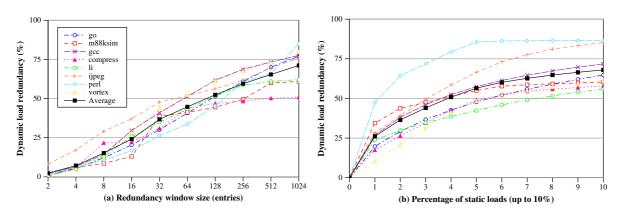

| 5.1  | Dynamic amount of load redundancy.                                                  | 84 |

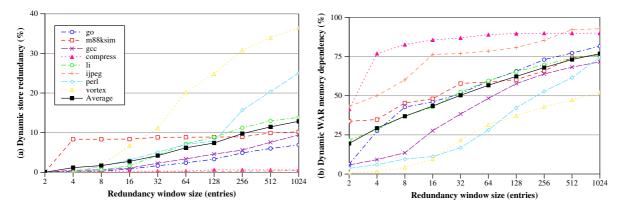

| 5.2  | Dynamic amount of store redundancy, and write-after-read memory dependencies.       | 85 |

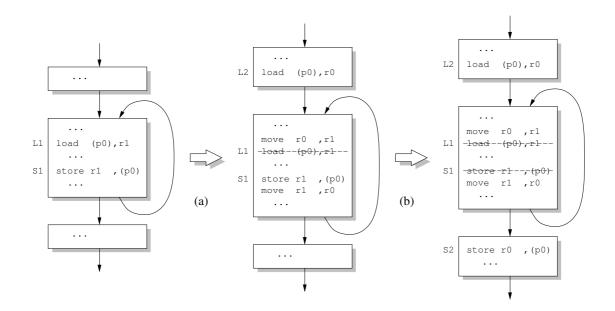

| 5.3  | Elimination of a redundant memory reference within a machine code basic block.      | 86 |

| 5.4  | Elimination of redundant memory references within extended basic blocks             | 88 |

| 5.5  | Elimination of (a) partially redundant load, and (b) partially redundant store.     | 90 |

| 5.6  | Benefit analysis for partial-SRE.                                                   | 96 |

|      |                                                                                     |    |

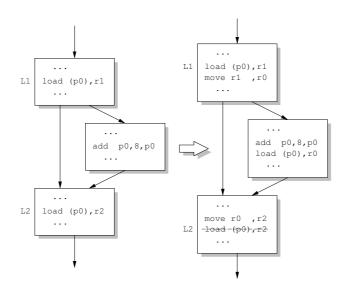

| 5.7  | Elimination of a path-sensitive redundant load                                      |

|------|-------------------------------------------------------------------------------------|

| 5.8  | Elimination of a dead store                                                         |

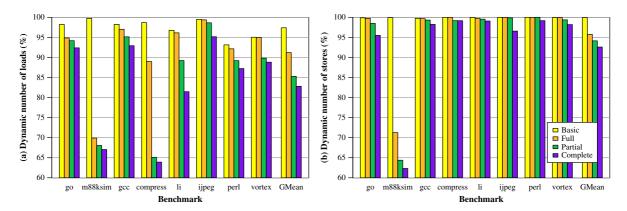

| 5.9  | Effect of different MRE degrees in number of loads and stores at run time $101$     |

| 5.10 | Dynamic amount of load redundancy after complete-MRE                                |

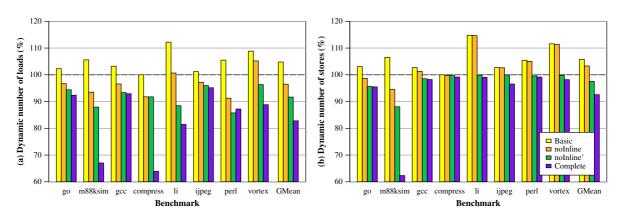

| 5.11 | Effect of procedure inlining on the MRE algorithms                                  |

| 5.12 | Effect of applying MRE in Alto compilation time                                     |

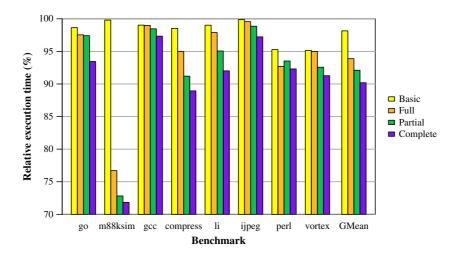

| 5.13 | Effect of different MRE degrees in actual execution time                            |

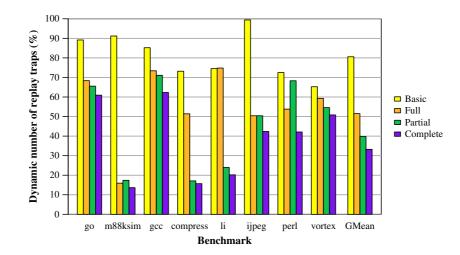

| 5.14 | Effect of different MRE algorithms in number of replay-traps                        |

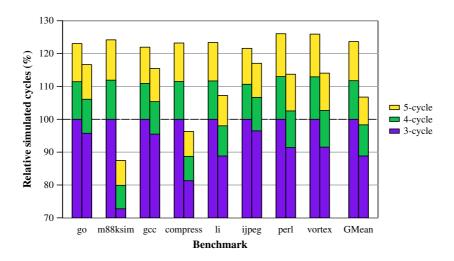

| 5.15 | Effects of load latency, from 3- to 5-cycle hit latency                             |

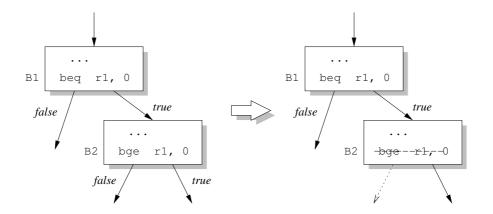

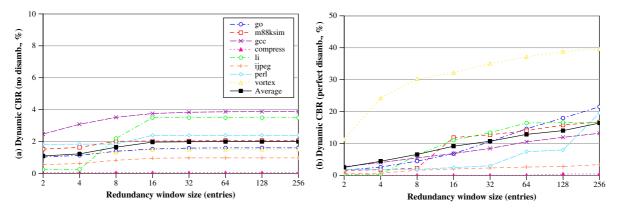

| 6.1  | Example of redundant conditional branch                                             |

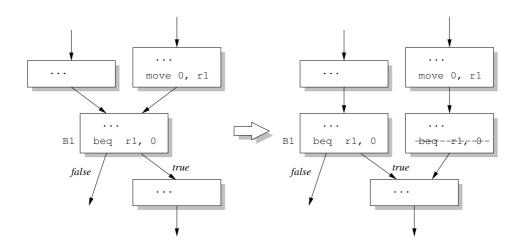

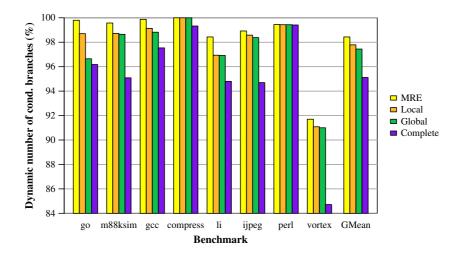

| 6.2  | Dynamic amount of conditional branch redundancy.                                    |

| 6.3  | Elimination of a redundant conditional branch within an extended basic block. $119$ |

| 6.4  | Elimination of a redundant conditional branch in a path-sensitive fashion $121$     |

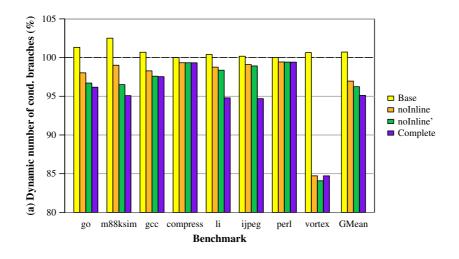

| 6.5  | Effect of CBRE algorithms in number of conditional branches at run time $125$       |

| 6.6  | Dynamic amount of conditional branch redundancy after complete-CBRE 126 $$          |

| 6.7  | Effect of procedure inlining on the CBRE algorithms                                 |

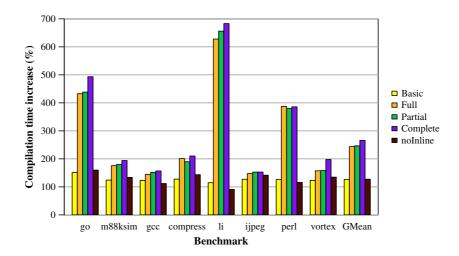

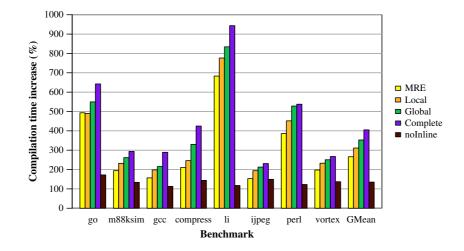

| 6.8  | Effect of applying CBRE in Alto compilation time                                    |

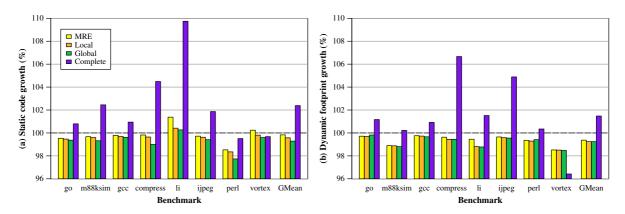

| 6.9  | Effect of different CBRE algorithms in code and footprint growth                    |

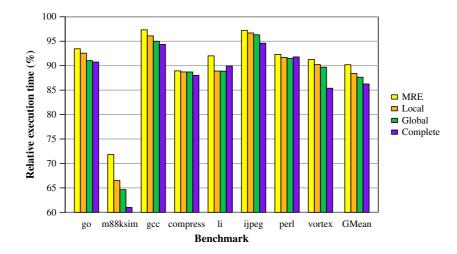

| 6.10 | Effect of different CBRE algorithms in actual execution time                        |

|      |                                                                                     |

# List of Tables

| 3.1 | Compaq/Alpha EV6 21264 processor characteristics                                  |

|-----|-----------------------------------------------------------------------------------|

| 3.2 | SPEC95 integer benchmark suite and their inputs                                   |

| 3.3 | Description of the different benchmark sets under evaluation                      |

| 3.4 | Static characteristics of the SPEC95 integer benchmarks                           |

| 4.1 | Description of must-alias analysis methods for memory disambiguation 62           |

| 4.2 | Description of may-alias analysis methods for memory disambiguation 72            |

| 4.3 | Percentage of queries that were misspeculated at least once                       |

| 4.4 | Percentage of dynamic queries misspeculated                                       |

| 5.1 | Description of the different MRE algorithms under evaluation 100                  |

| 5.2 | Static MRE on loads for the SPEC95 integer benchmark suite                        |

| 5.3 | Static MRE on stores for the SPEC95 integer benchmark suite                       |

| 5.4 | Description of the binaries obtained with/without applying MRE and inlining. 105  |

| 6.1 | Description of the different CBRE algorithms under evaluation                     |

| 6.2 | Description of the binaries obtained with/without applying CBRE and inlining. 127 |

LIST OF TABLES

xvi

## Chapter 1

## Introduction

In this chapter we outline the motivations behind this thesis. We first identify the memory wall and the control dependencies as the major performance factors in today's microprocessors. Then, we define the concept of binary redundancy, that is, the dynamic redundancy observed in binary programs related to these performance issues. We will see that binary redundancy opens new opportunities for compiler optimizations, and how this redundancy removal appropriately fits within link-time or executable code optimizers. Finally, we give a brief description of our objectives and describe the structure of this work.

### 1.1 Motivation

Superscalar processors represent the major trend in high-performance processors in the last several years [SS95]. These processors naturally evolve from pipelined architectures, and try to obtain higher performance rates by simultaneously fetching and executing in parallel several independent instructions in a single cycle. The two major performance limiters for today's superscalar processors are:

The memory wall Overcoming the long latencies caused by the different speed between the processor and the memory subsystem is one of the primary issues for high-performance computing [WM95]. To overcome this problem, the best known hardware solution relies on the use of cache memories [Smi82]. Memory is then organized hierarchically to take advantage of program locality<sup>1</sup>, by exploiting both spatial locality (i.e., the nearby data to that being used is likely to be accessed in the future), and temporal reuse (i.e., the data being used is likely to be accessed again in the future).

Unfortunately, due to Moore's Law [Moo65], the memory wall is growing for each generation of new processors. That's why, even for memory accesses to the first-level cache, memory latency has grown beyond a single cycle in modern processors. As an example, 3 cycles are needed in order to access the 64Kb L1 cache in the Alpha 21264 processor [Kes99].

**Control dependencies** Pipelined processors introduce the problem of fetching one instruction per cycle without waiting for the previous instructions to finish [HP96]. When such instruction is a branch, its outcome is unknown until one or more cycles after the instruction was fetched, making the program control flow uncertain at that point and introducing execution bubbles in the pipeline. This situation is even a major performance issue in superscalar processors due to longer pipelines [SS95].

For handling control dependencies, the best known hardware proposals are based on *predicting* the behavior of conditional branch instructions before the branch is actually executed [Smi81, YP92, CG94, LCM97]. This behavior is defined by the *branch target address*, and the *branch direction*, in case of a conditional branch. Then, the next path is speculatively fetched the next cycle with no delay. In case of misprediction, it will be necessary to squash the wrongly fetched instructions, possibly incurring in additional penalties.

Even though hardware approaches have shown to be very valuable in current superscalar processors, they are not enough to overcome the performance factors pointed out before. From

<sup>&</sup>lt;sup>1</sup>We only address in this work the discussion of *data caches*, since we only want to reason about program data. *Instructions caches*, for which several solutions have been proposed both in hardware [CMMP95, RBS96, FPP97] and software [PH90, GBSC97, RLPN<sup>+</sup>99], are beyond the scope of this work.

our point of view, the compiler can and should help in *overcoming* these issues. The reason is that, as we will show in this work (see Chapter 5 and Chapter 6), it seems that there is still room for improvement in compiled code. Furthermore, the compiler approach is attractive for two reasons:

- 1. It has a null hardware cost, since it does not require additional transistors.

- 2. It provides performance improvements on already existing architectures.

The disadvantage is that the compiler is blind to run-time information. However, we believe that today's optimizing compilers should be very aggressive in applying sophisticated optimizations [Muc97a], in order to minimize the remaining negative impact of the above issues in program performance.

#### 1.1.1 Binary redundancy

As we mentioned earlier, cache memories and branch predictors try to bridge the performance gap due to the negative impact of the memory wall and the control dependencies in current superscalar processors. These hardware structures do take advantage of several factors: among other things, cache memories exploit *temporal memory reuse*, while branch predictors exploit *branch correlation*. In other words, they try to exploit the *dynamic redundancy* existing in programs. In this work, we will be specifically concerned with two types of redundancy:

- **Memory redundancy** This refers to memory instructions that access memory cells already referenced in the past, and that, obviously, increase the temporal reuse of the program.

- **Conditional branch redundancy** That is, conditional branches whose outcome can be statically determined along some paths of the program at compile time.

It is straightforward to note that, unlike more general computation redundancy [MR79, KRS94a, Muc97b, BGS98], these redundancy types are closely related to how binary programs are executed on superscalar processors, since there are hardware structures that try to deal with them explicitly (again, cache memories and branch predictors are good examples). For this reason, we define *binary redundancy* as the redundancy encountered on executable programs at binary level, which refers to both memory and conditional branch redundancy.

In general terms, binary redundancy exposes unnecessary recomputation at program run time of values that are already known, because they have already been computed in the program (by some other instruction or by a prior execution of the same instruction), or because they can be computed at compile time. As a result, binary redundancy exposes optimization opportunities that can be potentially exploited by an optimizing compiler in order to remove these redundancies away.

| (a) | $if(x_n > 0)$ | (b) register $r = *p;$ | <pre>(c) register r = *p;</pre> |

|-----|---------------|------------------------|---------------------------------|

| (a) | if (*p > 0)   | if (r > 0)             | if (r > 0)                      |

|     | 1             | {                      | {                               |

|     | *q =          | *q =                   | *q =                            |

|     | }<br>;f (     | }                      | if (r == 1)                     |

|     | if (*p == 1)  | if (r == 1)            | {                               |

|     | 1             | {                      | • • •                           |

|     | ···           |                        | }                               |

|     | }             | }                      | }                               |

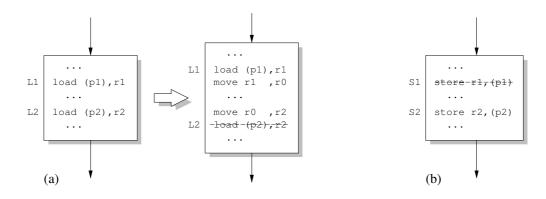

Figure 1.1: Example of memory and conditional branch redundancies, and its elimination: (a) original code, (b) resulting code after eliminating the redundant memory reference, and (c) resulting code after eliminating the redundant conditional branch.

Figure 1.1 illustrates a C code example where cases of memory and conditional branch redundancy can be observed:

- Looking at Figure 1.1a, we can see that memory location referenced by \*p is redundantly accessed in the two conditionals. To remove the redundant memory reference (i.e., the second \*p), the key idea is to reuse the first loaded value rather than load the same value again, by keeping the value in a register while it is needed (as it can be seen in Figure 1.1b).

- On the other hand, condition \*p == 1 is known to be false when condition \*p > 0 evaluates to false. In this example, it means that the outcome of the second conditional branch can be determined sometimes, depending on the outcome of the first conditional branch. To remove such conditional branch redundancy we need in this case to restructure the program, in order to isolate the correlated path form the non-correlated one (as shown in Figure 1.1c).

It is important to note that for removing both memory and conditional branch redundancies, neither pointer p must change between the two \*p read accesses, nor pointer q must be aliased with pointer p in the example. Therefore, in order to detect and eliminate binary redundancies, the need for disambiguating memory references will make *alias analysis* a critical factor [ASU86a, Muc97c, GLS01].

Binary redundancy comes partly from the way that programmers write source code, but also from limitations in the compilation model of traditional compilers [ASU86b]. Thus, for example, a variable may not have been kept in a register by the compiler because it was a global, or because the compiler was unable to resolve aliasing adequately, or because there

#### 1.1. MOTIVATION

were not enough free registers available. Similarly, the compiler may not have the opportunity to perform intraprocedural analyses and optimizations, thus continuously evaluating conditional branches that could be statically determined otherwise. These constraints are often responsible for a significant number of unnecessary memory and conditional branch instructions in binary programs [Bod99].

In summary, binary redundancy exists even in reasonably well-written programs, but is often hard to remove. In general, the removal of redundant instructions may speed up the program in two ways:

- 1. When the redundant instruction is removed, there are fewer instructions to execute. As a result, there is less contention for hardware resources (e.g., functional units, registers, cache ports, etc.), which allows scheduling the remaining instructions earlier. Note that the resource constraints restriction could be overcome with wider processors, making this benefit of somewhat less important for future high-performance processors.

- 2. Because the reused value is available sooner than the recomputed one, subsequent instructions that need the value can be scheduled earlier. Essentially, removing an instruction breaks some paths of data dependences among instructions. When the redundancy removal breaks the critical path of a program, it may be possible to schedule such program in fewer machine cycles. Observe in this case that the critical path constraint is a manifestation of the data-flow limit of the program [Wal91], and hence cannot be overcome without program transformation, making this restriction more important for future processors.

Note that the instruction schedule is improved regardless of whether it is created statically (i.e., by a compiler) or dynamically (i.e., by an out-of-order processor). Binary redundancy elimination is thus beneficial for both statically and dynamically scheduled processors.

#### 1.1.2 Binary optimizations

Optimizations performed at link time or directly applied to final program executables have received increased attention in recent years [SW92, RVL+97, Goo97, CGLR97, MDWdB01, SDAL01, SDA02, LMP+04], mainly due to limitations in the traditional compilation model. Large programs tend to be compiled using separate compilation, that is, one or a few files at a time. Therefore, the compiler does not have the opportunity to optimize the program as a whole, even when performing sophisticated interprocedural analyses and transformations. Furthermore, basic knowledge about the program objects (e.g., whether a variable is stored on the heap, stack or global area) is also lost when moving from one file or compilation unit to the next.

Vendors have tried to overcome these limitations by compiling separate files that contain intermediate representations rather than final object code [Wal86, Sil99]. Later, at link time, these "fake" intermediate object files are fully compiled and optimized together with the rest of the program units. The drawback of this approach is that it does not mix well with traditional Makefile-based software development environments. Furthermore, the implemented analyses and optimizations are possibly limited to only code that is available for examination at compile time. This means that code involving calls to procedures defined in separately compiled modules, and to dynamically dispatched "virtual functions" in object oriented languages (in the case where the virtual function is never overridden) cannot be effectively optimized. This is even valid for interprocedural analyses and optimizations performed by sophisticated optimizing compilers [JNMW00, LCH<sup>+</sup>03], since the source code of programs is not always available such as in old legacy software or library code. As a consequence, link-time or executable code optimizers that are based solely on the final object representation (i.e., when the *entire* program is available for inspection) have the attraction of being able to work on a full program basis and be fully integrated on a normal compile-build-test cycle.

A second reason for the recent interest in binary optimization has been the emergence of profile-directed compilation techniques [PH90, CMCH92, CL96, GBF98, FLM<sup>+</sup>01, GMZ02]. As it has been shown in several studies [Sar89, BL96, CFE97, BMS98], the compiler can use to great advantage the profiling information to identify new optimization opportunities that are frequently observed during program execution but are not detected by a simple static analysis. However, the same problem of separate compilation plagues the production use of profile feedback. After a previous run of the program to collect profile data, large projects will be forced to re-build every file to take advantage of profile information. Furthermore, the profile-collection phase needs to be specially coded into the Makefile environment. By contrast, it would be more convenient to be able to build the full application, instrument it to obtain profile data and then re-optimize the final binary without recompiling a single source file. This is the approach taken by Spike [CGLR97, FLM<sup>+</sup>01], for example, and is only possible if using binary optimization techniques.

Binary optimizers overcome most of the existing limitations of traditional source-code compilers. However, since most of the high-level information available in traditional compilers is lost, working at executable code level has its own set of issues:

- Machine code usually has much less semantic information than source code, which makes it much more difficult to discover control-flow or data-flow information.

- Traditional compiler analyses are usually carried out on representation of source programs in terms of high-level language constructs that often ignore "nasty" features typically encountered in executable programs (e.g., type casts, obfuscated pointer arithmetic, out-of-bounds array accesses, etc.), since such features result in non-standard

conforming programs whose behavior are not guaranteed to be preserved under compiler optimizations.

• Executable programs tend to be significantly larger than the original source programs they were derived from.

In most cases, sophisticated analyses that are practical at the source level (which usually operate on a per module or per function basis) turn out to be of limited utility at the executable code because of their time or space requirements. When working on executable code, therefore, it is often necessary to make tradeoffs between precision and efficiency.

### 1.2 Thesis overview

In this section we provide a brief description of the topics we deal with in this thesis dissertation. We present the problems we are trying to solve, the approaches we take to solve them, and the structure of this work.

#### 1.2.1 Thesis objectives

In this thesis we present new *profile-guided compiler optimizations* for eliminating the *binary* redundancy encountered on executable programs at binary level, even though these programs have been compiled with full optimizations using a "state-of-the-art" commercial compiler. Our *Binary Redundancy Elimination* (*BRE*) optimizations will be targeted at eliminating both redundant memory operations and redundant conditional branches, which are the most important ones for addressing the major performance issues in today's microprocessors. The main contributions of this work are the following:

**Computing alias information** We first review the problem of *alias analysis* at the executable program level, identifying why memory disambiguation is one of the weak points of object code modification. Then, we present several alias analyses to be applied in the context of link-time or executable code optimizers. First, we propose a *must-alias* analysis to recognize memory dependencies in a *path-sensitive* fashion (this scheme will be used in our optimization for eliminating redundant memory operations). Next, we present two *speculative may-alias* data-flow algorithms to recognize memory independencies. These may-alias analyses are based on introducing unsafe speculation at analysis time, which increases alias precision on important portions of code and keeps the analysis reasonably cost-efficient. Our results will show that our analyses prove to be very useful for increasing memory disambiguation accuracy of binary code, which translates into additional opportunities for applying optimizations.

- Eliminating memory redundancies We discuss the discovery and elimination of memory operations that are redundant and can be safely removed in order to speed up a program, an optimization that we call *Memory Redundancy Elimination (MRE)*. We quantify these effects and show that a high percentage of memory references at program run time can be considered redundant because they are accessing memory locations that have been referenced in a near past. We then present several profile-based MRE algorithms targeted at optimizing away these redundancies. These optimization algorithms are mainly based on *Partial Redundancy Elimination (PRE)* techniques for eliminating partial redundancies in a path-sensitive fashion. Our results will show that a significant amount of memory redundancy can indeed be eliminated, which translates into important reductions in execution time.

- **Eliminating conditional branch redundancies** Finally, we propose several optimization techniques for detecting and eliminating redundant conditional branches on executable code. These are branches whose outcome can be determined at compile time, and thus they can be safely removed in order to speed up a program. We call this optimization *Conditional Branch Redundancy Elimination (CBRE)*. We first show that important amounts of conditional branches in a program can be considered redundant because their outcomes can be determined from a previous short dynamic execution frame. We also see how important memory disambiguation is in order to catch branch redundancy. Then, we present several CBRE algorithms targeted at optimizing away these redundancies. Our results will show that a significant amount of redundant conditional branches can be removed with moderate levels of code growth.

All our algorithms, both for the analyses and the optimizations, will be implemented within a *binary optimizer*, which overcomes most of the existing limitations of traditional source-code compilers. Therefore, our work also points out the most relevant issues of applying our algorithms at the executable code level, since most of the high-level information available in traditional compilers is lost.

#### 1.2.2 Structure of this document

The work we present in this document is organized as follows:

- Chapter 2 introduces some terminology for program analysis and optimization we use in this work, and also presents a brief description of the most significant related work in this research field.

- Chapter 3 presents our research environment. We give an overview of our experimental framework at all levels (i.e., compilation, execution and simulation), and also introduce the benchmark suite and the methodology used for evaluation.

- Chapter 4 reviews the problem of alias analysis at the executable program level. We then present several alias algorithms to be applied in the context of link-time or executable code optimizers, that prove to be very useful for increasing memory disambiguation accuracy of binary code.

- Chapter 5 presents our techniques addressed to eliminate redundant memory operations on executable code. These proposals are mainly based on new applications of PRE techniques for eliminating partial redundancies in a path-sensitive fashion.

- Chapter 6 shows our optimizations targeted at removing conditional branch redundancies at binary programs. Our algorithms are even able to detect and eliminate partial conditional branch redundancies, applying code restructuring when needed.

- Finally, Chapter 7 summarizes the main contributions of this thesis and presents the open areas for future research.

## Chapter 2

# Background and related work

In this chapter we introduce some preliminary background on compiler analyses and optimizations in general, focusing on techniques related to the work presented in this document. We also review the state of the art on several topics: (a) profile-guided optimizations, (b) optimizations targeted at eliminating redundancy, and (c) binary optimizers. In particular, we discuss previous work closely related to what is developed in this thesis.

### 2.1 Preliminaries

We start this chapter by reviewing some basic compiler concepts related to the work presented in this dissertation. The rest of this work is developed from first principles [ASU86c, Muc97d].

#### 2.1.1 Control flow graph

An important part of a compiler's internal representation relies on characterizing the control structure of a program, by transforming it into some intermediate form more suitable for further modifications. We define the control flow in a program as a rooted, directed graph with a set of nodes and a set of edges connecting such nodes.

**Definition 2.1.1** A directed graph G is a pair (N, E) where N is the node set and E is the edge set such that  $E \subseteq N \times N$ . Immediate predecessor and successor of nodes are defined with maps pred and succ, such that  $pred(n) = \{m|(m,n) \in E\}$  and  $succ(n) = \{m|(n,m) \in E\}$ . A finite path of G is a sequence  $\omega = n_1, \ldots, n_k$  of nodes such that  $(n_i, n_{i+1}) \in E$  for all  $1 \leq i < k$ .  $\Box$

We then use a *Control Flow Graph* (CFG) as the underlying program representation because it is the most commonly used intermediate program representation in both production and research compilers.

**Definition 2.1.2** A control-flow graph G = (N, E, start, end) is a directed graph (N, E), in which nodes  $n \in N$  represent basic blocks containing individual program statements (instructions). Edges  $(m, n) \in E$  represent the non-deterministic branching structure of the program. Nodes start and end are the unique start node and end node of G; they are assumed to have no predecessors and no successors, respectively. It is also assumed that every node  $n \in N$  lies on a path  $\omega = start, \ldots, end$ . We also say that node m dominates n (written m dom n) if every possible path w from start to n includes m. Similarly, node n postdominates m (written n pdom m) if every possible path w from m to end includes n.  $\Box$

The above definition is valid for representing the flow graph of both a program and a *procedure* or *routine*. Because CFG directly exposes program's control-flow paths, it enables an intuitive and efficient formulation of code analysis and optimization, and thus become the standard representation in optimizing compilers.

#### 2.1.2 Basic blocks

As we have mentioned, nodes in a CFG are called basic blocks. A *basic block* is, informally, a straight-line sequence of instructions that can be entered only at the first of them and exited only from the last of them. The first instruction in a basic block is called a *leader*.

A natural extension of a basic block is known as *Extended Basic Block (EBB)*, which is a set of basic blocks with either (a) a single entry point but multiple exit points, or (b) a single exit point but multiple entry points. The latter is also known as *reverse extended basic block*. An EBB can be thought of as a tree of basic blocks, where the EBB *root* corresponds to the single entry or exit point, respectively. Extended basic blocks are interesting in some contexts, where analyses and transformations are more effective when done on EBBs than on simple basic blocks.

#### 2.1.3 Instruction set representation

For the machine code examples of this document, we assume for simplicity a canonical RISC instruction set. We can distinguish between the following type of instructions:

• Memory is accessed only through explicit load and store instructions, which have the form load  $k(r_b), r_a$  and store  $r_a, k(r_b)$ . Memory instructions have the effect of read-ing/writing from/to the location whose address is  $k + contents(r_b)$ , where k is a constant offset and  $r_b$  is the base register.

Two special registers, denoted as sp or stack pointer, and gp or global pointer, point to the program stack and global data areas, respectively.

- For arithmetic and logic instructions we assume the form  $op \ src_1, src_2, dst$ , where op denotes an operation, dst is a destination register, and  $src_1$  and  $src_2$  are source registers<sup>1</sup>. For instance, an add instruction computes the sum of  $src_1$  and  $src_2$  into dst. Many other operations can be expressed in terms of this form.

- To determine control-flow information, we consider the usual set of conditional branches, and direct and indirect unconditional branch instructions. For conditional branches, we have the "test and branch" form  $bop \ src_1, src_2$ , which means that the branch will be taken if the relationship between  $src_1$  and  $src_2$  holds the condition defined by the instruction opcode.

We assume this generic machine code instruction set to be the compiler intermediate language as well. Although this might seem to be very non-portable, this representation is in fact very similar to the low-level intermediate representation used in many compilers [ASU86d, Mah92, Muc97e, Mor98].

<sup>&</sup>lt;sup>1</sup>To simplify the discussion we abuse notation and allow either  $src_1$  or  $src_2$  to be an integer constant, denoting an immediate operand. We also allow the lack of one of the source operands so that register moves can be modeled.

### 2.2 Data-flow analysis

Before actually applying code transformations, compilers perform a variety of analysis to find out how program data is being used [BGS94]. The purpose of *data-flow analysis* is to provide such information, and serve as a bridge between the program representation and the actual program optimization. This section describes the most important ideas of applying data-flow analysis for understanding the behavior of a program.

**Performing data-flow analysis** Data-flow analysis is usually performed on a controlflow graph. It attempts to track the flow of data through the program's variables and to characterize the values of variables at various points of execution. By traversing each path, the analysis verifies the algebraic rules posed by the representation (e.g., whether a variable has been redefined). Thus, by being a tool for summarizing global program properties, dataflow analysis identifies patterns, which are then used to guide the program transformation phase of a particular optimization.

There are two primary strategies for performing data-flow analysis:

1. Develop a set of equations that are applied to basic blocks, which yields a list of variables that match some desired criteria [Muc97f]. For example, suppose we wish to compute the set of values that are available at the exit of a given basic block B. Conventionally, this set is name *out*. The equation to compute out(B) is

$$put(B) = gen(B) \cup (in(B) - kill(B))$$

$$(2.1)$$

where gen(B) is the set of values generated inside the block B, in(B) is the set of values that reach B from some other block, and kill(B) is the set of values that were overwritten in B (by an assignment statement, for example). A straightforward method for computing the data-flow information, which is also the most widely used, is to apply Equation 2.1 iteratively until reaching a fixed point [ASU86a].

Perform data-flow analysis based on *chains* [Muc97g]. The idea is to identify where variables are assigned a value (called a *definition*) and where the value is used (a *use*). By connecting definitions with uses the compiler can perform a wide variety of analysis. Thus, either uses will be connected to definitions or definitions will be connected to uses (and even both in some cases).

In both cases, we must be certain that a data-flow analysis computes information that does not misrepresent what the program being analyzed does, in the sense that it must not indicate that a transformation of the code is safe to perform that, in fact, is not safe. We must guarantee this by careful design of the analysis and by being sure that the solution computed is, if not an exact representation of the program's manipulation of its data, at least a conservative approximation of it. However, to obtain the maximum possible benefit from optimization, we seek to pose data-flow analyses as aggressive as we can make them. Thus, we shall always attempt to walk the fine line between being as aggressive as possible in the information we compute and being conservative, so as to get the greatest possible benefit form the analyses and code transformations we perform without ever modifying program's semantic.

**Characterizing data-flow analysis** Data-flow analysis can be categorized along several dimensions, including the following [NNH99]:

- Flow direction Corresponds to the direction of information flow. Almost all the data-flow problems are one-directional, either *forward* (i.e., in the direction of program execution) or *backward* (i.e., opposite to the direction of program execution). *Bidirectional* problems require forward and backward propagation at the same time and are significantly more complicated to formulate, understand, and solve than one-directional problems. Fortunately, bidirectional data-flow problems are rare.

- Flow sensitivity The *flow-insensitive* versus *flow-sensitive* classification indicates whether a data-flow analysis is independent of the control flow encountered or not. This distinction is important because it determines the computational complexity of the problem under consideration. Flow-insensitive problems can be solved by solving subproblems and then combining their solutions to provide a solution for the whole problem, independent of control flow. Flow-sensitive problems, on the other hand, require the algorithm to follow the control-flow paths through the flow graph to compute the solution.

- May vs. must information It is useful to distinguish may information from must information. The former indicates what may occur on some path through a flow graph, while the latter indicates what must occur on all paths through the flow graph. The may vs. must classification is important because it indicates whether a property must hold, and hence can be counted on, or that it only may hold, and so must be allowed for but cannot be counted on.

- **Intra- vs. inter-procedurality** Compilers often limit their program analyses to individual procedures. That is, they are *intraprocedural*, which means they are applied without regard to the calling context in which that procedure is used or the procedures it calls. As a result, one must generally assume that a called procedure may use or change any variable it might be able to access, which clearly inhibits optimization opportunities. By contrast, *interprocedural* approaches are ones that use the calling relationships among

a set of procedures to drive the analysis. The intra- versus inter-procedural distinction can also be applied when reasoning about compiler optimizations.

Context-sensitivity Interprocedural data-flow analyses can be either *context insensitive* or *context sensitive*. Context-insensitive analyses simply combine the control-flow graphs for individual procedures into a large graph and analyze this using standard intraprocedural techniques, without keeping track of which return edges correspond to which call edges. This has the advantages of simplicity and efficiency: nothing special needs to be done to handle interprocedural control flow, and a procedure does not have to be re-analyzed for its various call-sites [CR82]. The problem is that such analyses can suffer from a loss of precision because they can explore execution paths containing call/return pairs that do not correspond to each other and therefore cannot occur in any execution of the program. Context-sensitive analyses, by contrast, avoid this problem by maintaining information about which return edges correspond to which call sites, and propagating information only along realizable call/return paths [EGH94]. The price paid for this improvement in precision is an increase in the cost of the analysis.

We next discuss the most popular data-flow analysis strategies for understanding the behavior of a program. We also give additional information on the corresponding existing techniques for analyzing executable code.

#### 2.2.1 Liveness analysis

Liveness analysis is a well-known technique employed by most compilers to guide optimizations based on transforming variables [ASU86a, Muc97f], such as useless code elimination (see Section 2.3.1.2) and register allocation [Muc97h]. The analysis attempts to determine whether a value kept in a variable or storage location may be used later on during program execution. A variable is said to be *live* at a particular point in a program if there is a path to the exit of a given block of code along which its value may be used before it is redefined. It is *dead* if there is no such path. A simple backward data-flow analysis is usually performed to compute this information at each point in a flow graph.

Liveness analysis can also be performed on executable code if we let registers take the place of variables [SW92, Goo97]. The problem is in this case simplified by the fact that, commonly, there is no aliasing between registers, and the number of registers for a given processor is bounded by a constant. As a result, *register liveness analysis*, unlike traditional liveness analysis which is usually intraprocedural, can be now applied interprocedurally or in a context-sensitive fashion in order to achieve higher precision rates with a moderate increase in the cost of analysis [Mut98]. Nevertheless, what makes the analysis difficult are anomalies of the control-flow graph and scalability issues, which are the common problems that appear when working at executable code level (as already mentioned in Section 1.1.2).

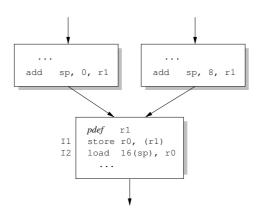

Figure 2.1: Sample code where different definitions are reaching a use. A *pseudo definition* is introduced for register  $r_1$ .

#### 2.2.2 Use-def chains

*Use-def chains* are a sparse representation of data-flow information about variables, which simplifies the implementation of several well-known optimizations, such as common subexpression elimination [ASU86a]. A *ud-chain* for a variable connects a use of that variable to all the definitions that may flow to it. Abstractly, a ud-chain is a function from a variable and a basic-block-position pair to sets of basic-block-position pairs, where every element corresponds to each definition [Muc97f].

As far as executable code is concerned, register use-def chains is an analysis that provides, for each use of a machine register, a pointer to its definition. The ud-chains form a directed graph whose nodes are instructions and whose edges are use-def pointers. When there are several definitions of a register reaching a use, as depicted in Figure 2.1, it is common to introduce a *pseudo instruction* at an appropriate confluence point which also defines that register, thereby shadowing the other definitions. This is analogous to  $\phi$  functions used with the *Static Single Assignment (SSA)* form [CFR<sup>+</sup>91], although pseudo insertions in this case result in "less accurate" use-def information. All registers are enforced to be defined before they are used by inserting pseudo instructions at all entry nodes of the graph.

#### 2.2.3 Alias analysis

Alias analysis refers to the determination of all the storage locations that may be accessed in two or more ways [ASU86a]. For example, a variable in a C program may have its address computed and be assigned to or read from both by variable name and through a pointer. Determining the range of possible aliases in program is essential for optimizing it correctly, while minimizing the sets of aliases found is important for doing optimizations as aggressively as possible. At the machine code level, the problem of alias analysis or *memory disambiguation* is to statically determine the relationship of every pair of memory references in a program. A *reference* typically identifies a memory address and an access size. Then, for two particular references, there are four possible answers that an alias disambiguator can return:

- They are *identical*, which means that both references always point to the same location.

- They are *intersecting*. This means that memory accessed by both references partially overlaps.

- They are *disjoint*, which means that they are never aliased, and therefore, independent.

- Unknown. That is, the disambiguator cannot determine statically the relationship between the two references.

The aliasing problem can be formulated by a combination of *may-alias* analysis, which answers whether two memory references are independent, and *must-alias* analysis, which checks references for memory dependencies. Performing *no alias analysis* conservatively leads to the assumption that every load and store instruction is always dependent on every previous store instruction.

While there is an extensive body of work on pointer alias analysis of various kinds [WL95, SH97, DWM98, CH00, GLS01], these are mostly high-level analyses carried out in terms of source language constructs that turn out to be of limited utility at the machine code level. In fact, the problem of memory disambiguation is one of the weak points of object code modification, because important information typically available in an ordinary compiler is lost at executable code level, where the contents of every register is potentially an address.

#### 2.2.3.1 Alias analysis by instruction inspection

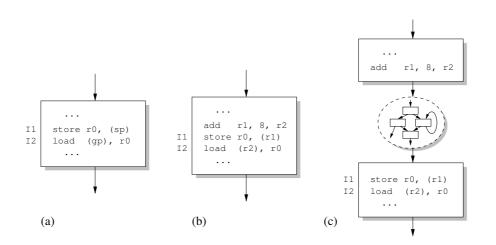

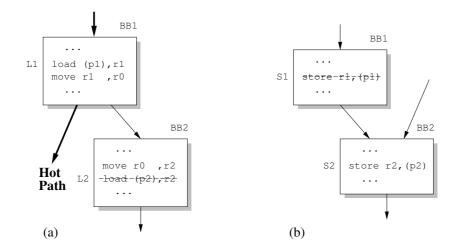

For disambiguating references, a common technique in compile-time instruction schedulers is alias analysis by instruction inspection [Muc97g]. Here, two memory references are considered within an extended basic block to see if it is obvious that they point to either the same or different memory addresses. For example, independence between instructions  $I_1$  and  $I_2$  in Figure 2.2 can be proved if either of the following conditions hold:

- Different memory regions are referenced. For example, one of the instructions uses a register known to point to the stack and the other uses a register known to point to the global data area, as shown in Figure 2.2a.

- They access data at addresses  $k_1(r_1)$  and  $k_2(r_2)$ , as shown in Figure 2.2b. Base registers  $r_1$  and  $r_2$  are computed by two (possibly empty) sequences of instructions such that

Figure 2.2: Sample code with different techniques for may-alias disambiguation by instruction inspection: (a) knowing that accesses point to different memory regions; (b) using register copies and address arithmetic propagation; (c) general case beyond extended basic block boundaries, using *use-def* chains.

$r_1 = c_1 + contents(r_0)$  and  $r_2 = c_2 + contents(r_0)$ , for some register  $r_0$ . Both accesses are non-aliased if both chains use the same definition of  $r_0$ , and  $c_1 + k_1$  and  $c_2 + k_2$ do not overlap<sup>2</sup>. To detect the definition of register  $r_0$  a simple backwards data-flow algorithm may be used.

All other memory instruction pairs are considered to be aliasing. Unfortunately, this simple approach does not work if information about register copies and address arithmetic needs to be propagated across extended basic block boundaries. To do so, *register use-def chains* are required, as presented in Section 2.2.2. In the general case, an instruction inspection algorithm tries to derive a symbolic description for each memory instruction and then compare these descriptions for checking independency, as shown in Figure 2.2c.

#### 2.2.3.2 Residue-based global alias analysis

Instruction inspection fails when several definitions are reaching a use. For example, looking back to Figure 2.1, register  $r_1$  is defined with two possible stack values. However, possible locations accessed at instruction  $I_1$  are disjoint with respect to the location accessed by instruction  $I_2$ . Debray *et al.* [DMW98] propose an interprocedural algorithm to reason about may-alias information of executable code. The analysis, which is implemented in the context of a link-time optimizer, can handle complex pointer arithmetic and features usually ignored by traditional alias analysis algorithms.

<sup>&</sup>lt;sup>2</sup>In case that  $c_1 + k_1 = c_2 + k_2$  the two references point to the same location, which indicates a dependency between the two accesses.

An alias analysis will in general associate each register with a set of possible addresses at each program point. The basic idea of the algorithm is to reason about arithmetic computations modulo some pre-selected value k. A set of addresses is then represented by an address descriptor, which is a pair  $\langle I, S \rangle$ , where I is the defining instruction for a machine register r, and S is a set of mod-k residues with respect to the value computed by instruction I. This representation can then distinguish between addresses involving distinct "small" displacements (i.e., less than k) from a base register. Comparing descriptors can be reduced to a comparison of mod-k sets, using dominator information to handle loops correctly. Since k is fixed, S can be represented as a bit vector of length k. Their implementation corresponds to mod-k residues with k = 64, in part determined by the fact that the set of mod-k residues for this choice of k corresponds to a bit vector that fits exactly in one 64-bit machine word. This means that set operations such as union, intersection, checking containment, etc., are compactly representable and can be carried out in O(1), which is cheap enough to be practical for the analysis of large binaries.

As far as the analysis is concerned, a data-flow system is used to propagate values through the control-flow graph. They use a conservative operation to "merge" the information coming along the incoming edges at vertices in the interprocedural control-flow graph [CC77]. Thus, if the values for a register r being propagated along two incoming edges at a vertex in the flow graph are described by address descriptors  $\langle I_1, S_1 \rangle$  and  $\langle I_2, S_2 \rangle$  respectively, and  $I_1 \neq I_2$ , then the information about r is generalized to the conservative value  $\perp$  [NNH99], denoting a total lack of information. The essential idea behind this operation is to associate a single descriptor with a register at each program point of interest, rather than a set of descriptors, keeping the memory requirements of the analysis reasonable: for each basic block one address descriptor per register is needed, corresponding to the *out* register set at the exit of the basic block<sup>3</sup>. For a given choice of value k, the analysis requires RN(k + w) bits of memory for a program with N basic blocks on a machine with R registers, where w is the number of bits per machine word.

Amme *et al.* [ABZT98] present a method to detect data dependencies in assembly code by using symbolic value propagation. However, the algorithm does not work beyond procedure boundaries, and symbolic values are not propagated through memory when registers are saved and restored. Although it has been applied to assembly code, it is not obvious that using the algorithm for interprocedural whole-program analysis would scale up to problems of this size.

#### 2.2.4 Abstract interpretation

Abstract interpretation [CC77, CC79] is a mathematical approach to statically analyze the dynamic properties of software applications at compile time, without executing the program

<sup>&</sup>lt;sup>3</sup>The *in* register set can be computed easily from the *out* register sets of its predecessors.

itself. It may be seen as an extension of compilation techniques that enable compilers to predict how a program will behave, before actually executing the application. Debray [Deb95] discusses the role of abstract interpretation in low-level compiler optimizations.

In the spirit of abstract interpretation, several methods have been proposed for obtaining dynamic program properties by using *symbolic evaluation* and simple algebraic rules [Rau91, TP95, ABD<sup>+</sup>02, DLS02]. Some of these techniques have been focused on a wide variety of program optimizations based on propagating information about value ranges of variables [Pat95, SBA00, BGSW00, MRS<sup>+</sup>01, CGS04].

# 2.3 Compiler optimizations