### Departamento de Ingeniería Electrónica

# SISTEMAS DIGITALES DE INSTRUMENTACIÓN Y CONTROL

# **TEMA 3**Diseño de Subsistemas Aritméticos

Rafael Ramos Lara Febrero 2007

### TEMA 3

#### Diseño de Subsistemas Aritméticos

#### Indice (I)

- 3.1. Formatos de representación numérica

- 3.2. Arquitecturas serie, paralelo y pipelined

- 3.3. Sumadores/restadores

- 3.3.1. Sumadores/restadores Serie-Serie

- 3.3.2. Sumadores/restadores Paralelo

- 3.4. Multiplicadores

- 3.4.1. Multiplicadores Array (Paralelo)

- 3.4.1.1. Multiplicadores Array Unsigned

- 3.4.1.2. Multiplicadores Array c.a.2

- 3.4.2. Multiplicadores Serie-Paralelo

- 3.4.2.1. Multiplicadores Serie-Paralelo *Unsigned* con algoritmo CSAS

- 3.4.2.2. Multiplicadores Serie-Paralelo *Unsigned* con algoritmo FSP

- 3.4.2.3. Multiplicadores Serie-Paralelo c.a.2 con algoritmo CSAS

- 3.4.2.4. Multiplicadores Serie-Paralelo c.a.2 con algoritmo FSP

- 3.4.2.5. Multiplicadores Serie-Paralelo MSB-primero Tema 3: Diseño de Subsistemas Aritméticos

### Indice (II)

- 3.4.3. Multiplicadores Serie Secuencial

- 3.4.4. Multiplicadores Serie-Serie

- 3.4.5. Multiplicadores Pipelined

- 3.4.6. Algoritmo L-Booth

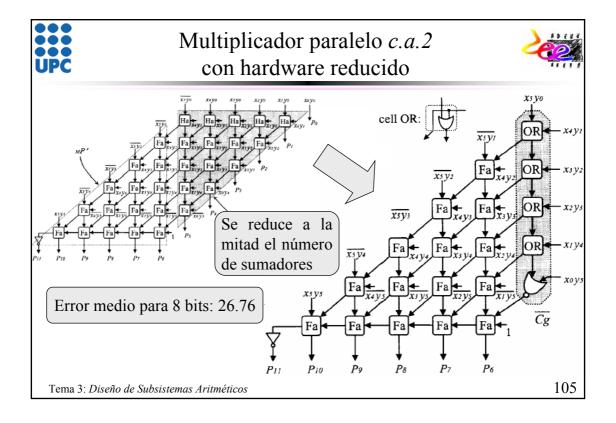

- 3.4.7. Multiplicadores de hardware reducido

- 3.5 Divisores

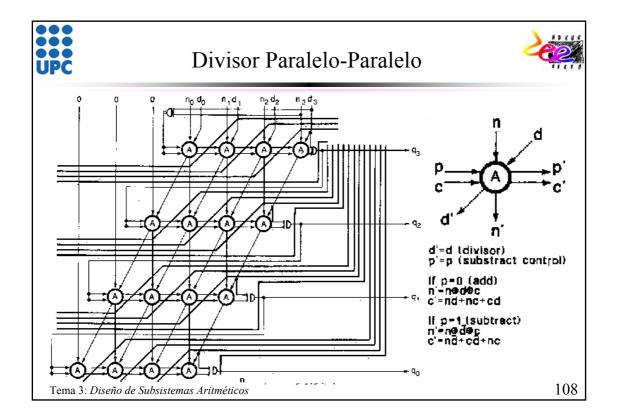

- 3.5.1. Divisor Paralelo-Paralelo

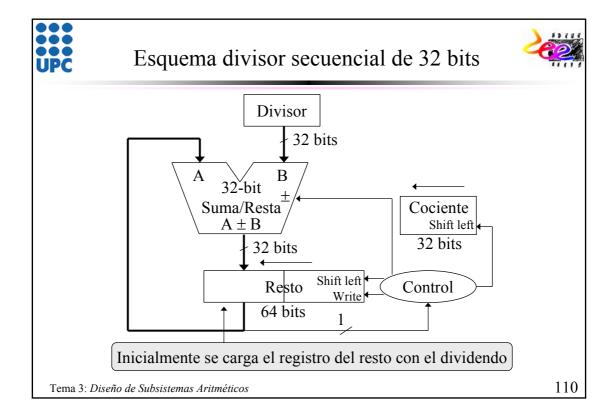

- 3.5.2. Divisor secuencial

Tema 3: Diseño de Subsistemas Aritméticos

3

### Indice (III)

- 3.6. Operaciones aritméticas en coma flotante

- 3.6.1. Formatos de representación en coma flotante

- 3.6.2. Suma/Resta en coma flotante

- 3.6.3. Multiplicación en coma flotante

- 3.7. Funciones especiales

- 3.7.1. Multiplicación por una constante

- 3.7.2. Raíz cuadrada

- 3.7.3. Cuadrado de un número: X<sup>2</sup>

- 3.7.4. Multiplicación de complejos

# Indice (IV)

- 3.8. Bloques aritméticos en FPGA's

- 3.8.1. Multiplicadores de la familia *Spartan-3*

- 3.8.2. XtremeDSP de la familia Virtex-4: DSP48

- 3.8.3. *XtremeDSP* de la familia *Virtex-5*: DSP48E

Tema 3: Diseño de Subsistemas Aritméticos

5

# 3.1 Formatos de representación numérica

#### Formatos normales de datos numéricos

- Existen diversos formatos de representación numérica de uso común en los sistemas digitales

- El formato concreto a utilizar dependerá de las características (magnitud, signo y precisión) de los número que intervienen en el proceso

Los tipos de representaciones más habituales son:

- Números enteros sin signo

- Números negativos: signo más magnitud absoluta

- complemento a 1

- complemento a 2

- BCD (números Decimales Codificados en Binario)

- Coma flotante

Tema 3: Diseño de Subsistemas Aritméticos

7

#### Números enteros sin signo

Es la forma más sencilla de representar números

El rango de números que se puede representar depende de la longitud del dato:

- 8 bits: rango de representación: 0 <-> 255

- *16 bits*: rango de representación: 0 <-> 65535

#### Ventajas:

• Los circuitos lógicos que realizan operaciones con este formato son sencillos de diseñar y realizar

#### Inconvenientes:

- El intervalo de números está limitado a la longitud del dato

- No se puede representar números negativos o fraccionarios

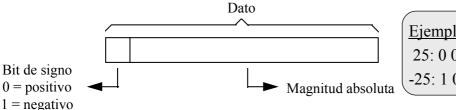

#### Números negativos: signo más magnitud absoluta

El bit de mayor peso es el bit de signo, y el resto de bits representa su magnitud absoluta

Ejemplo:

25:00011001

-25: 1 0 0 1 1 0 0 1

Si, por ejemplo, el dato es de 8 bits, se pueden representar los siguientes números:

- positivos: del 0000 0000 al 0111 1111 (0 al 127)

- negativos: del 1000 0000 al 1111 1111 (0 al -127)

Tema 3: Diseño de Subsistemas Aritméticos

9

#### Números negativos: complemento a 1

El valor negativo de un número en complemento a 1 se obtiene invirtiendo todos los dígitos  $(d_{n-1}...d_0)$  del número expresado en positivo:

Bit de signo

$$N = -\left(2^{n-1} - 1\right)d_{n-1} + \sum_{i=0}^{n-2} d_i \cdot 2^i \longrightarrow \text{Resto de bits}$$

Si, por ejemplo, el dato es de 8 bits, el rango de representación es:

- positivos: del 0000 0000 al 0111 1111 (0 al 127)

- negativos: del 1111 1111 al 1000 0000 (0 al -127)

#### Números negativos: complemento a 2

Con este formato y con un dato de N bits, un número negativo -M se representa como:  $2^{\rm N}$  - M

Bit de signo

$$N = -2^{n-1} \cdot d_{n-1} + \sum_{i=0}^{n-2} d_i \cdot 2^i$$

Resto de bits

Si, por ejemplo, el dato es de 8 bits, se pueden representar los siguientes números:

- positivos: del 0000 0000 al 0111 1111 (0 al 127)

- negativos: del 1111 1111 al 1000 0000 (-1 al -128)

Tema 3: Diseño de Subsistemas Aritméticos

11

#### Código BCD: Números Decimales Codificados en Binario

- Es un código binario utilizado para representar números decimales

- Cada dígito decimal se expresa con cuatro bits

- Permite representar de forma directa números decimales

| Dígito<br>Decimal | BCD  |

|-------------------|------|

| 0                 | 0000 |

| 1                 | 0001 |

| 2                 | 0010 |

| 3                 | 0011 |

| 4                 | 0100 |

| 5                 | 0101 |

| 6                 | 0110 |

| 7                 | 0111 |

| 8                 | 1000 |

| 9                 | 1001 |

- El rango de valores representable es pequeño

- Con 8 bits se puede representar: 0....99d

Decimal: 7 5 BCD: 0111 0101 Binario: 101011

Tema 3: Diseño de Subsistemas Aritméticos

#### Coma Flotante

- El formato de números en coma flotante se define como:  $\pm$  A · 2  $\pm$ B

- A: mantisa, B: exponente

- Permite representar números fraccionarios, enteros, positivos y negativos

- La precisión depende del número de bits de la mantisa

- Inconveniente: la complejidad de los circuitos que realizan operaciones con este formato

Tema 3: Diseño de Subsistemas Aritméticos

13

# 3.2 Arquitecturas serie, paralelo y pipelined

### Arquitecturas para el procesado aritmético

El tipo de arquitectura adecuada para implementar un subsistema de procesado aritmético depende de:

- *Velocidad de muestreo*: varia entre las velocidades muy bajas propias de aplicaciones de voz o comunicaciones, y velocidades muy altas propias de sistemas de radar, sonar, video y procesado de imagen

- *Recursos hardware*: el número y tipo de componentes digitales que incorpora un PLD, así como la arquitectura interna (distribución de componentes y recursos de interconexión)

Tipos de arquitectura:

- Arquitectura serie: procesan un bit del dato por cada ciclo de reloj

- Arquitectura paralelo: procesan un dato por cada ciclo de reloj

- Arquitectura pipelined: permite realizar en paralelo varias operaciones a la vez

Tema 3: Diseño de Subsistemas Aritméticos

15

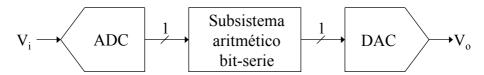

#### Arquitectura serie

- Procesa un bit del dato por cada ciclo de reloj

- Requiere menos recursos hardware que otras arquitecturas

- Necesita menos interconexiones y menos pines de entrada/salida

- Son idóneas en aplicaciones de baja frecuencia donde la velocidad de proceso no es un parámetro restrictivo

- Normalmente se utilizan junto con ADC y DAC serie

#### Esquema arquitectura serie

Tema 3: Diseño de Subsistemas Aritméticos

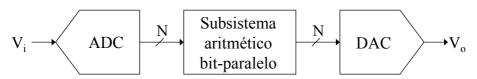

#### Arquitectura paralelo

- Procesa un dato por cada ciclo de reloj

- Es la arquitectura que requiere mas recursos hardware

- Necesita mas interconexiones y pines de entrada/salida

- Son idóneas en aplicaciones de muy alta frecuencia

- Normalmente se utilizan junto con ADC y DAC paralelo con elevada velocidad de conversión (ADC Flahs)

#### Esquema arquitectura paralelo

Tema 3: Diseño de Subsistemas Aritméticos

17

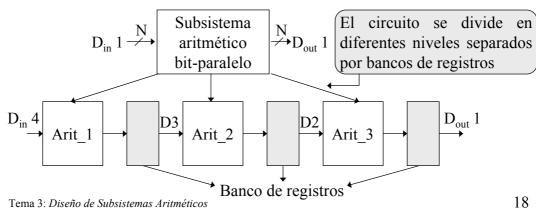

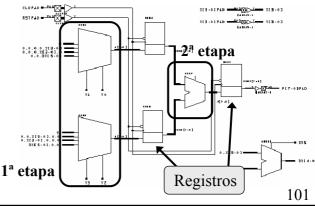

#### Arquitectura Pipelined

- Se introducen bancos de registros entre los niveles de lógica

- Permite procesar varias muestras a la vez

- Aumenta la velocidad de cálculo en estructuras bit-paralelo

#### Esquema arquitectura pipelined

### 3.3 Sumadores/restadores

19

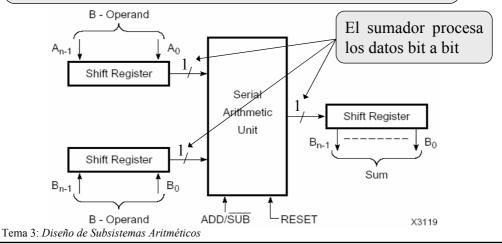

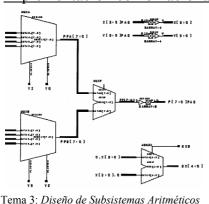

# 3.3.1 Sumadores/restadores Serie-Serie

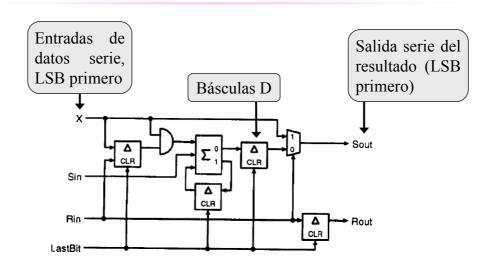

#### Esquema sumador/restador Serie-Serie

- Los dos operandos se introducen en registros de desplazamiento

- La unidad aritmética procesa los operandos bit a bit

- Se procesa primero el bit de menor peso

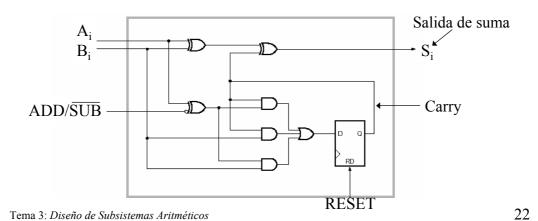

# Esquema de la célula básica sumador/restador serie

- Sumador/restador de 1 bit con salida de suma y bit de carry/borrow registrado

- Para completar la suma de dos datos de N bits se requieren N ciclos de reloj

- La unidad aritmética se puede implementar en un solo CLB

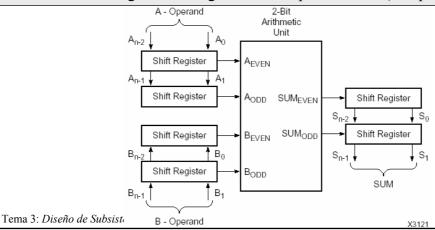

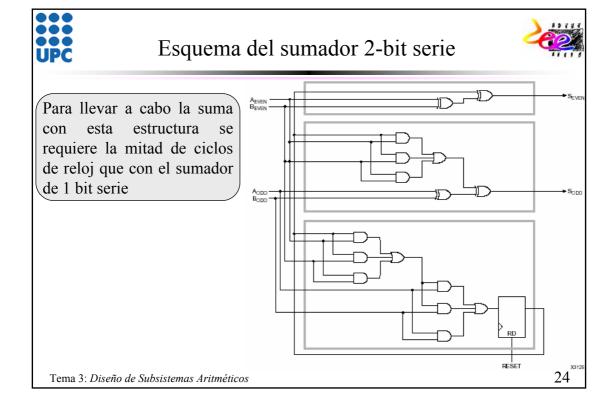

#### Arquitectura 2-bit serie

- Se puede aumentar la velocidad procesando dos bits simultáneamente

- Los bits pares e impares se cargan en registros de desplazamiento separados

- La unidad aritmética suma dos bits en cada ciclo de reloj

- El resultado se carga en dos registros de desplazamiento (bits par e impar)

#### 3.3.2 Sumadores/restadores Paralelo

25

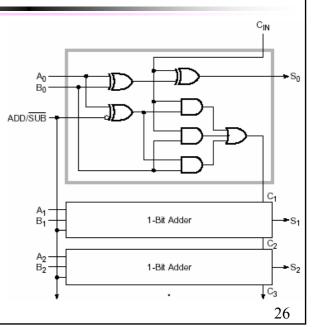

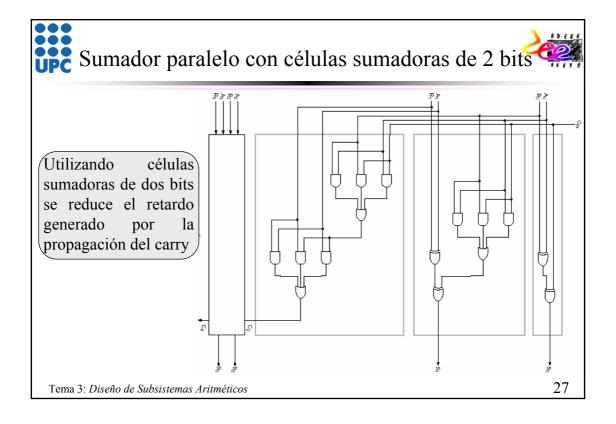

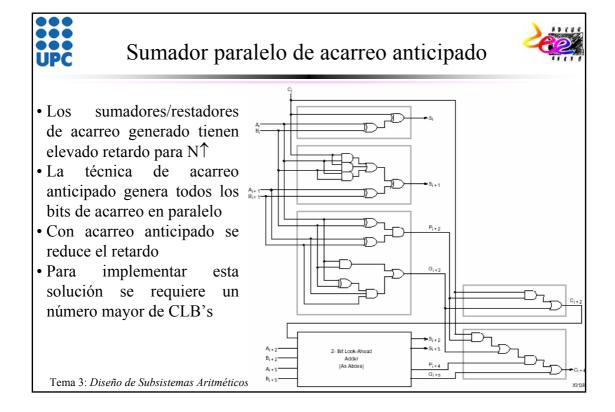

#### Sumador paralelo con acarreo propagado

- Compuesto básicamente de N células sumadoras de 1 bit donde se ha suprimido la báscula que almacena el acarreo

- Utiliza un CLB por bit (menos que otros sumadores paralelo)

- El retardo es N veces el equivalente a un CLB

- Utilizando células sumadoras de dos bits se puede reducir el retardo

Tema 3: Diseño de Subsistemas Aritméticos

# 3.4 Multiplicadores

29

#### Introducción

- El multiplicador es un componente fundamental en algoritmos *DSP*

- El producto de un número *A* de "*n*" bits por otro número *B* de "*m*" bits genera un producto *P* de "*m*+*n*" bits

- Tipos de multiplicadores:

- Array (paralelo): los operandos de entrada y el resultado se procesan en paralelo

- Serie-paralelo: un operando se carga en paralelo y el otro se introduce en serie, el resultado se obtiene en serie

- Serie-Serie: los dos operandos entran en serie, el resultado aparece en serie

- Multiplicadores pipelined: procesan varios productos a la vez

- Multiplicadores de hardware reducido

# 3.4.1 Multiplicadores Array (Paralelo)

31

3.4.1.1 Multiplicadores Array Unsigned

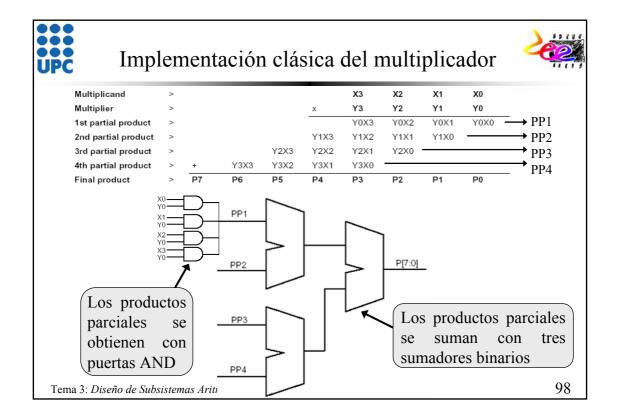

#### Multiplicación binaria unsigned

- El producto se obtiene multiplicando (función AND) bit a bit los operandos X e Y y sumando los resultados parciales (función suma)

- Para operandos de "n" y "m" bits, el resultado es de "n+m" bits

El producto de dos números enteros positivos viene dado por:

$$X = x_{n-1} x_{n-2} x_{n-3} \dots x_0 = \sum_{i=0}^{n-1} x_i 2^i$$

$$Y = y_{n-1} y_{n-2} y_{n-3} \dots y_0 = \sum_{j=0}^{n-1} y_j 2^j$$

$$XY = \sum_{i=0}^{n-1} \sum_{j=0}^{n-1} 2^{i+j} x_i y_j \leftarrow \text{Productos y sumas}$$

Tema 3: Diseño de Subsistemas Aritméticos

33

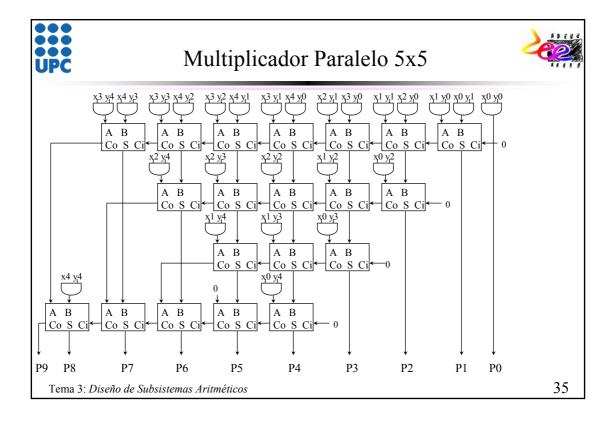

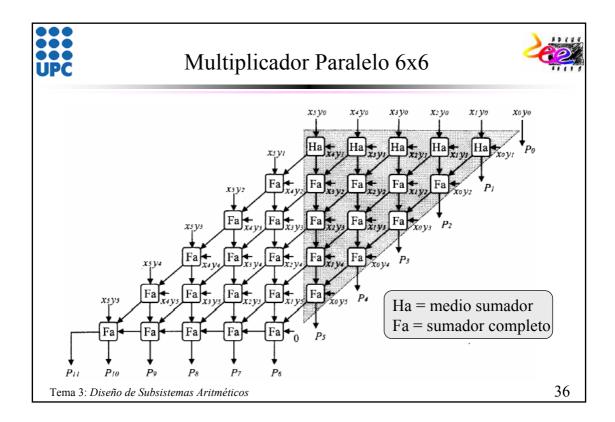

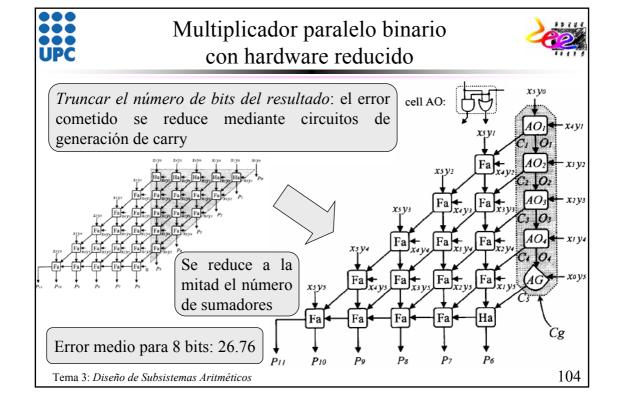

#### Implementación multiplicador paralelo unsigned

- Se implementan directamente todos las puertas AND y sumadores que intervienen en la realización del producto

- Emplea más recursos hardware que otras soluciones pero el producto se obtiene sin señal de reloj

| Multiplicand        | > |    |              |      |      | X3   | X2   | X1   | X0   |

|---------------------|---|----|--------------|------|------|------|------|------|------|

| Multiplier          | > |    |              |      | х    | Y3   | Y2   | Y1   | Y0   |

| 1st partial product | > |    | AND          |      |      | Y0X3 | Y0X2 | Y0X1 | Y0X0 |

| 2nd partial product | > |    |              |      | Y1X3 | Y1X2 | Y1X1 | Y1X0 |      |

| 3rd partial product | > |    | $\downarrow$ | Y2X3 | Y2X2 | Y2X1 | Y2X0 |      |      |

| 4th partial product | > | +  | Y3X3         | Y3X2 | Y3X1 | Y3X0 |      |      |      |

| Final product       | > | P7 | P6           | P5   | P4   | P3   | P2   | P1   | P0   |

Tema 3: Diseño de Subsistemas Aritméticos

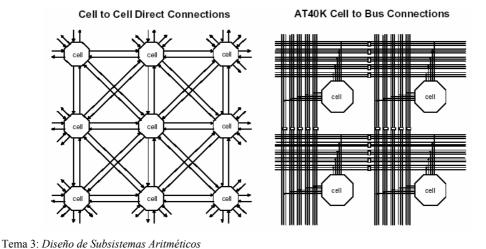

### Implementación con FPGA AT40K de Atmel

Las conexiones diagonales entre células de la FPGA *AT40K* permite la fácil implementación de multiplicadores haciendo uso de menos puertas lógicas

37

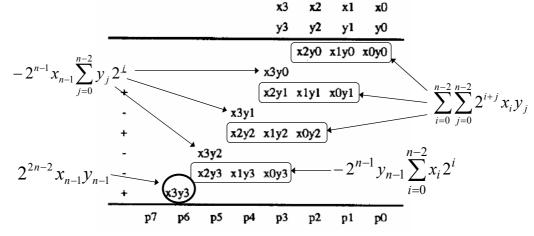

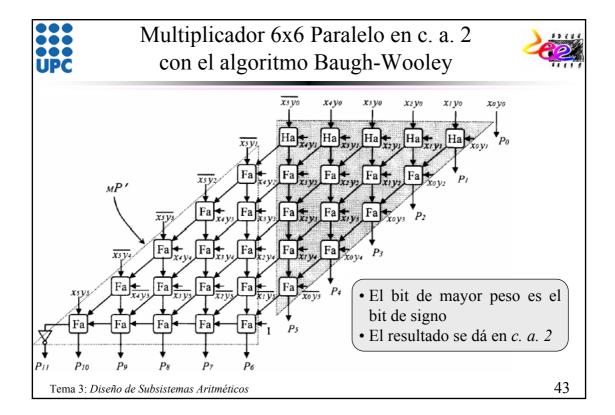

# 3.4.1.2 Multiplicadores Array c.a.2

#### Multiplicación binaria en c.a.2

El producto de dos números expresados en complemento a dos viene dado por:

$$X = x_{n-1} x_{n-2} x_{n-3} \dots x_0 = -2^{n-1} x_{n-1} + \sum_{i=0}^{n-2} x_i 2^i$$

$$Y = y_{n-1} y_{n-2} y_{n-3} \dots y_0 = -2^{n-1} y_{n-1} + \sum_{j=0}^{n-2} y_j 2^j$$

$$XY = \left( -2^{n-1} x_{n-1} + \sum_{i=0}^{n-2} x_i 2^i \right) \cdot \left( -2^{n-1} y_{n-1} + \sum_{j=0}^{n-2} y_j 2^j \right) =$$

$$\sum_{i=0}^{n-2} \sum_{j=0}^{n-2} 2^{i+j} x_i y_j + 2^{2n-2} x_{n-1} y_{n-1} - 2^{n-1} x_{n-1} \sum_{j=0}^{n-2} y_j 2^j - 2^{n-1} y_{n-1} \sum_{j=0}^{n-2} x_i 2^j$$

#### Implementación multiplicador paralelo en c.a.2

39

En este caso se necesitan sumadores y restadores para realizar el producto

Tema 3: Diseño de Subsistemas Aritméticos

Tema 3: Diseño de Subsistemas Aritméticos

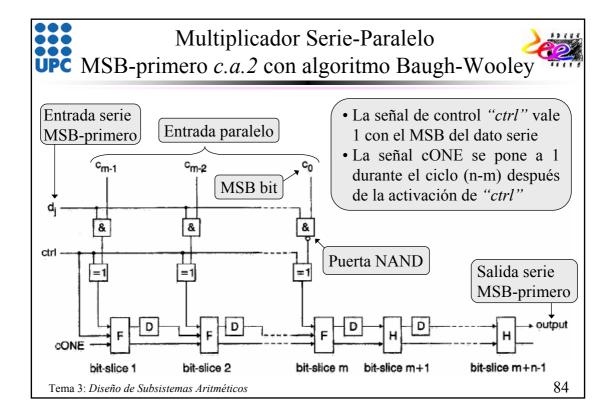

# Algoritmo Baugh-Wooley para multiplicar en *c.a.2* (I)

Permite realizar el producto utilizando sólo sumadores y puertas AND, NAND

$$\begin{split} AB = & \left( -2^{n-1}a_{n-1} + \sum_{i=0}^{n-2}a_{i}2^{i} \right) \cdot \left( -2^{n-1}b_{n-1} + \sum_{j=0}^{n-2}b_{j}2^{j} \right) = \\ & \sum_{i=0}^{n-2}\sum_{j=0}^{n-2}2^{i+j}a_{i}b_{j} + 2^{2n-2}a_{n-1}b_{n-1} - 2^{n-1}a_{n-1}\sum_{j=0}^{n-2}b_{j}2^{j} - 2^{n-1}b_{n-1}\sum_{i=0}^{n-2}a_{i}2^{i} = \\ & \sum_{i=0}^{n-2}\sum_{j=0}^{n-2}2^{i+j}a_{i}b_{j} + 2^{2n-2}a_{n-1}b_{n-1} + 2^{n-1}\sum_{j=0}^{n-2}a_{n-1}b_{j}2^{j} + 2^{n-1}\sum_{i=0}^{n-2}b_{n-1}a_{i}2^{i} + 2^{n} - 2^{2n-1} \right) \end{split}$$

Tema 3: Diseño de Subsistemas Aritméticos

41

# Algoritmo Baugh-Wooley para multiplicar en *c.a.2* (II)

$$2^{n-1} \sum_{j=0}^{n-2} \overline{a_{n-1}b_{j}} 2^{j} \underbrace{\overline{a_{3}b_{1}} \ a_{2}b_{1} \ a_{1}b_{1} \ a_{0}b_{1}}_{\overline{a_{3}b_{2}} \ a_{1}b_{2} \ a_{1}b_{2} \ a_{0}b_{2}} \underbrace{\sum_{i=0}^{n-2} \sum_{j=0}^{n-2} 2^{i+j} a_{i}b_{j}}_{i=0} 2^{i+j} a_{i}b_{j}$$

$$-2^{2n-1} \longrightarrow 1 \underbrace{a_{3}b_{3}}_{\overline{a_{2}b_{3}} \ \overline{a_{1}b_{3}} \ \overline{a_{0}b_{3}}}_{\overline{a_{2}b_{3}} \ \overline{a_{1}b_{3}} \ \overline{a_{0}b_{3}}} \underbrace{-2^{n-1} \sum_{i=0}^{n-2} \overline{b_{n-1}a_{i}} 2^{i}}_{i=0} 2^{i-1} \underbrace{\sum_{i=0}^{n-2} \overline{b_{n-1}a_{i}} 2^{i}}_{i=0}$$

$p_2$

$p_1$

$p_0$

Tema 3: Diseño de Subsistemas Aritméticos

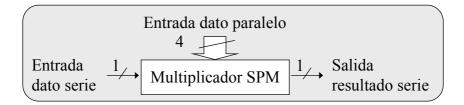

# 3.4.2 Multiplicadores Serie-Paralelo

#### Multiplicadores Serie-Paralelo (SPM)

- Dispone de una entrada de operando serie, otra entrada de operando paralelo y salida del resultado serie

- El hardware empleado en su diseño es más reducido que el multiplicador paralelo

- El producto se realiza secuencialmente bajo el control de una señal de reloj

Tema 3: Diseño de Subsistemas Aritméticos

45

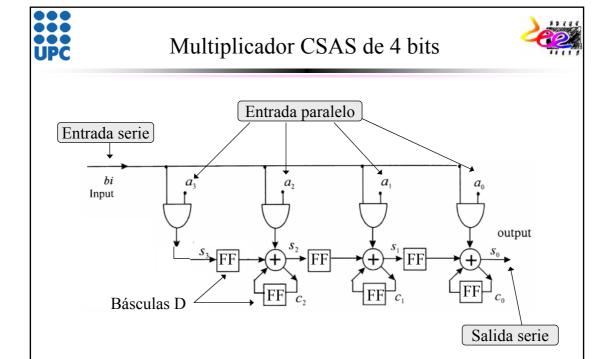

# 3.4.2.1 Multiplicadores Serie Paralelo Unsigned con algoritmo CSAS

#### SPM con algoritmo CSAS

- CSAS: Carry-Save Add-Shift

- Su funcionamiento se basa en el algoritmo de suma-desplazamiento:

- El dato paralelo se multiplica por cada uno de los bits del dato serie mediante puertas AND

- El resultado de cada producto se desplaza una posición a la derecha

- Cada nuevo producto parcial se suma con la acumulación desplazada de los anteriores productos

- Si N es el número de bits del dato serie y M del dato paralelo, el resultado de N+M bits se obtiene después de N+M ciclos de reloj

- Durante los primeros N ciclos se introduce el dato serie empezando por el LSB

- Durante los *M* ciclos siguientes se aplica un cero en la entrada serie y se propagan los bits de carry almacenados en los registros hacia la salida

Tema 3: Diseño de Subsistemas Aritméticos

47

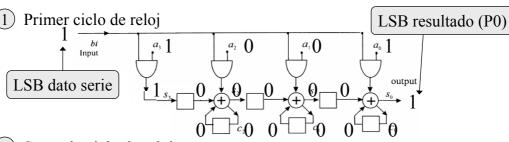

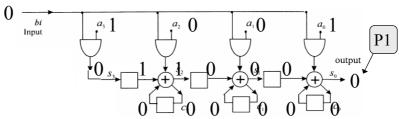

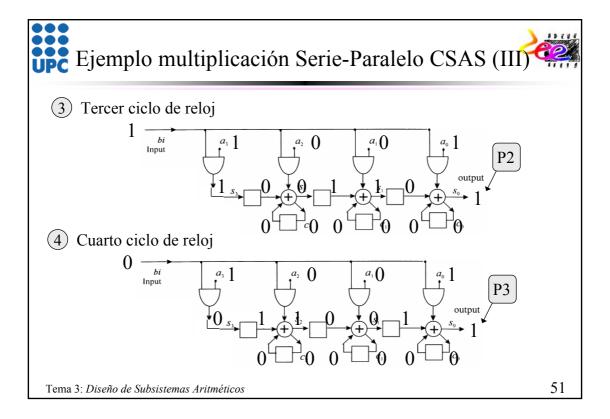

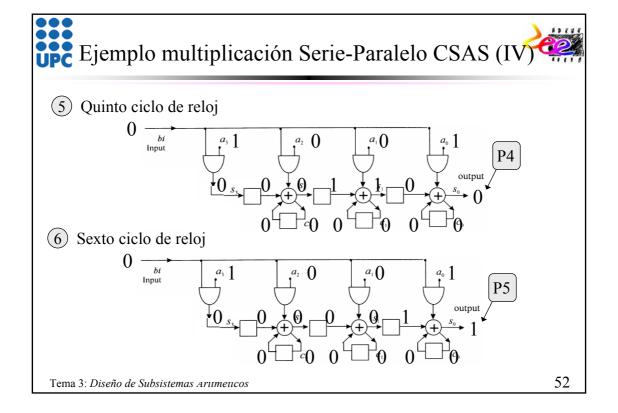

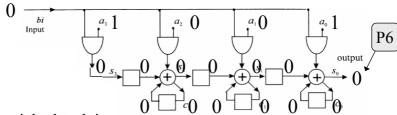

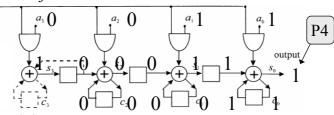

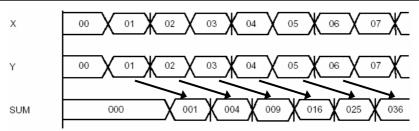

#### Ejemplo multiplicación Serie-Paralelo CSAS (I)

*Ejemplo:* multiplicador SPM de 4 bits, producto de 9d x 5d

El resultado de 8 bits se obtiene después de 8 ciclos de reloj:

- 4 ciclos para hacer los 4 productos parciales

- 4 ciclos para propagar los bits de carry hacia la salida serie

Tema 3: Diseño de Subsistemas Aritméticos

49

#### Ejemplo multiplicación Serie-Paralelo CSAS (II)

2 Segundo ciclo de reloj

Tema 3: Diseño de Subsistemas Aritméticos

### Ejemplo multiplicación Serie-Paralelo CSAS (V

(7) Séptimo ciclo de reloj

(8) Octavo ciclo de reloj

Tema 3: Diseño de Subsistemas Aritméticos

53

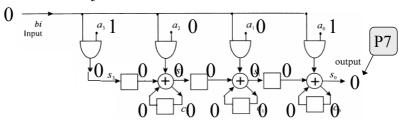

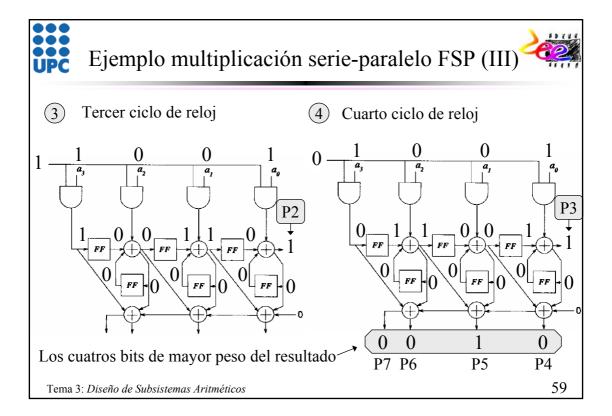

# 3.4.2.2 Multiplicadores Serie-Paralelo Unsigned con algoritmo FSP

#### SPM con algoritmo FSP

- FSP: Fast Serial-Parallel

- Realiza el producto en tan solo N ciclos de reloj (igual al número de bits del multiplicador u operando serie)

- Durante los primeros *N-1* ciclos funciona como una multiplicador *CSAS*, en el siguiente ciclo funciona como un sumador de *M-1* bits para extraer en paralelo los bits de carry remanentes

Tema 3: Diseño de Subsistemas Aritméticos

55

Tema 3: Diseño de Subsistemas Aritméticos Salida paralelo suma de acarreos remanentes 56

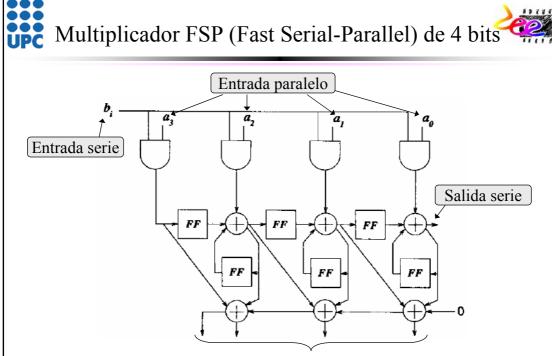

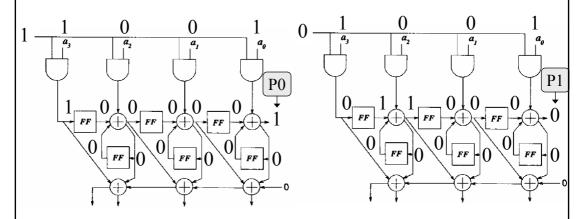

### Ejemplo multiplicación serie-paralelo FSP (I)

*Ejemplo:* multiplicador SPM de 4 bits, producto de 9d x 5d

El resultado de 8 bits se obtiene después de 4 ciclos de reloj:

- 3 ciclos para hacer los 3 primeros productos parciales

- 1 ciclo para hacer el último producto parcial y extraer en paralelo los 4 bits de mayor peso

Tema 3: Diseño de Subsistemas Aritméticos

57

#### Ejemplo multiplicación serie-paralelo FSP (II)

- 1) Primer ciclo de reloj

- 2 Segundo ciclo de reloj

Tema 3: Diseño de Subsistemas Aritméticos

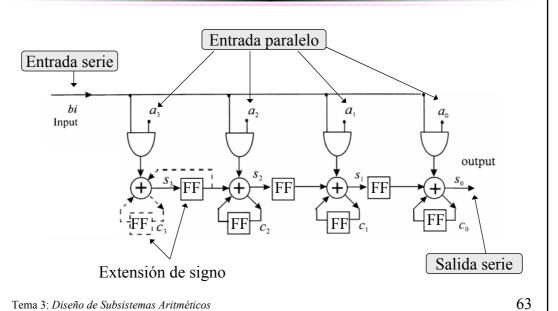

3.4.2.3 Multiplicadores Serie Paralelo c.a.2 con algoritmo CSAS

#### Multiplicador SPM c.a.2

Para realizar el producto serie-paralelo se utilizan dos técnicas:

- Extensión de signo: requiere más recursos hardware

- Algoritmo de Baugh-Wooley

Tema 3: Diseño de Subsistemas Aritméticos

61

### Algoritmo de extensión de signo

Se extiende el signo de ambos números N+I veces donde N es la longitud de los operandos que intervienen en el producto

|        |      |      |      |      |      |      |      |      |            | _<br>人 |            |              |            |             |           |            |                        |

|--------|------|------|------|------|------|------|------|------|------------|--------|------------|--------------|------------|-------------|-----------|------------|------------------------|

|        |      |      |      |      |      |      | 1    | x3   | <b>x</b> 3 | x3     | x3         | <b>x</b> 3   | <b>x</b> 3 | <b>x</b> 2  | x1        | <b>x</b> 0 |                        |

|        |      |      |      |      |      |      |      | у3   | у3         | у3     | у3         | у3           | у3         | y2          | y1        | <b>y</b> 0 |                        |

|        |      |      |      |      |      |      |      | x3y0 | x3y0       | x3y0   | x3y0       | x3y0         | x3y0       | x2y0        | x1y0      | x0y0       | 7                      |

| ٠      |      |      |      |      |      |      | x3y1 | x3y1 | x3y1       | x3y1   | x3y1       | <b>x3y</b> 1 | x2y1       | x1y1        | x0y1      |            |                        |

| +      |      |      |      |      |      |      | -    |      |            | -      | -          | x2y2         | -          | x0y2        |           |            |                        |

| +      |      |      |      |      | -    | -    | - 1  |      | -          | -      | -          | x1y3         |            | $/_{\rm T}$ | érm       | inos       | que intervienen en el  |

| +      |      |      |      |      | x3y3 |      |      |      |            |        |            |              | /ĸ         | ` -         | •         |            | cálculo del resultado  |

| +      |      |      |      | x3y3 |      |      |      |      |            |        |            |              |            | `,          | r         |            |                        |

| +      |      |      |      | x3y3 |      |      |      |      |            |        |            |              |            | 1           | Las       | opera      | aciones a realizar son |

| +      |      |      |      | x3y3 |      |      |      |      |            |        |            |              |            |             | 1         | las m      | ismas que en caso de   |

| + x3y3 | x3y3 | x3y3 | x3y3 | x3y3 | x3y3 | x2y3 | x1y3 | x0y3 | _          |        |            |              |            |             |           |            | números positivos      |

|        |      |      |      |      |      |      |      | p7   | p7         | р6     | <b>p</b> 5 | <b>p</b> 4   | р3         | p2          | <b>p1</b> | p0         | nameros positivos      |

|        |      |      |      |      |      |      |      |      |            | - D    | 1.         | 1            | 1 1        |             | 1         |            |                        |

Tema 3: Diseño de Subsistemas Aritméticos

Resultado del producto

# Multiplicador Serie-Paralelo *c.a.2* CSAS de 4 bits con extensión de signo

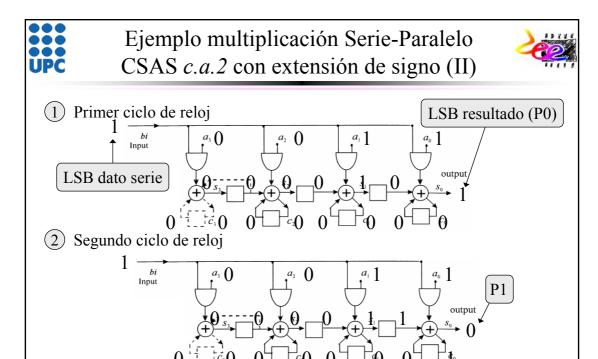

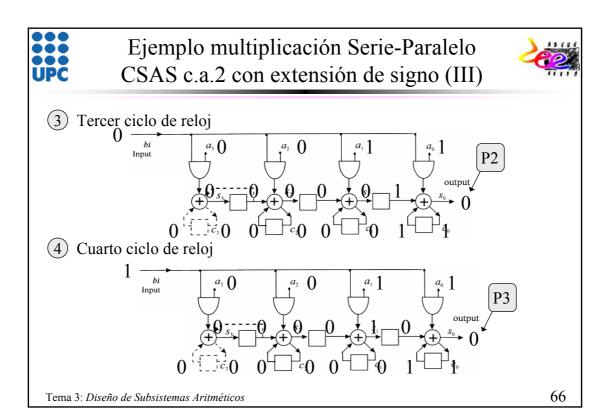

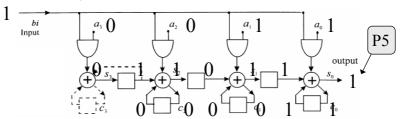

# Ejemplo multiplicación Serie-Paralelo CSAS *c.a.2* con extensión de signo (I)

*Ejemplo:* multiplicador SPM de 4 bits, producto de -5d x 3d

Tema 3: Diseño de Subsistemas Aritméticos

Tema 3: Diseño de Subsistemas Aritméticos

# Ejemplo multiplicación Serie-Paralelo CSAS c.a.2 con extensión de signo (IV)

Input

6) Sexto ciclo de reloj

Tema 3: Diseño de Subsistemas Aritméticos

67

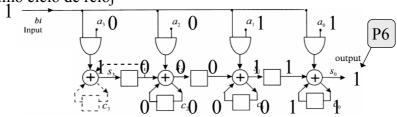

# Ejemplo multiplicación Serie-Paralelo CSAS c.a.2 con extensión de signo (V)

7 Séptimo ciclo de reloj

(8) Octavo ciclo de reloj

Tema 3: Diseño de Subsistemas Aritméticos

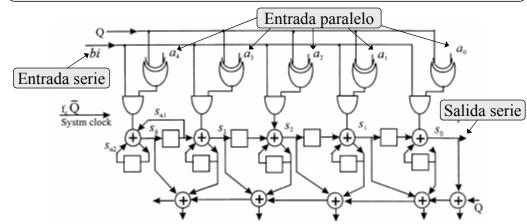

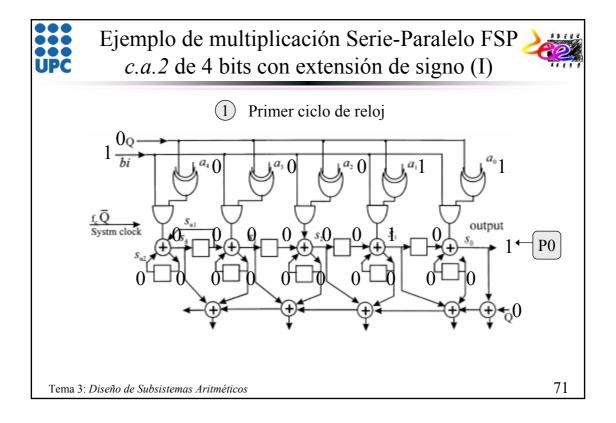

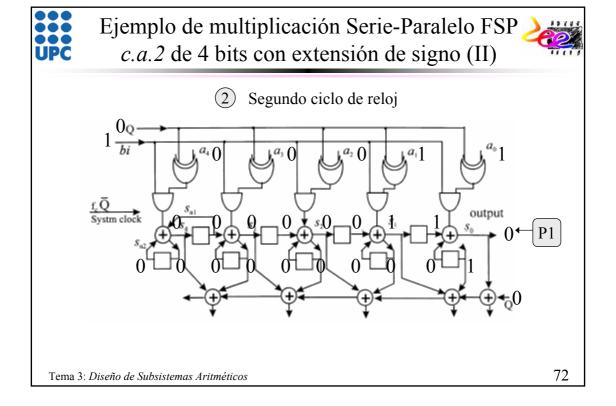

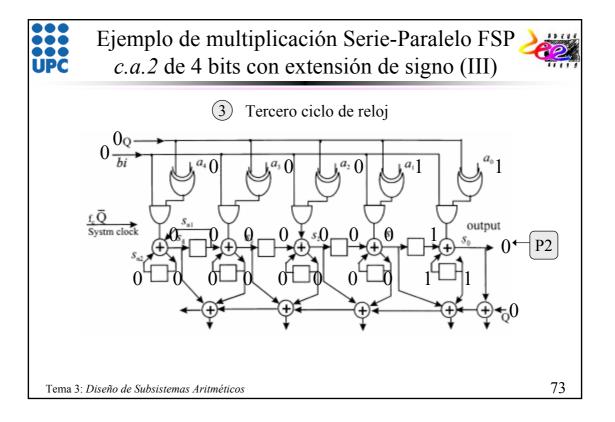

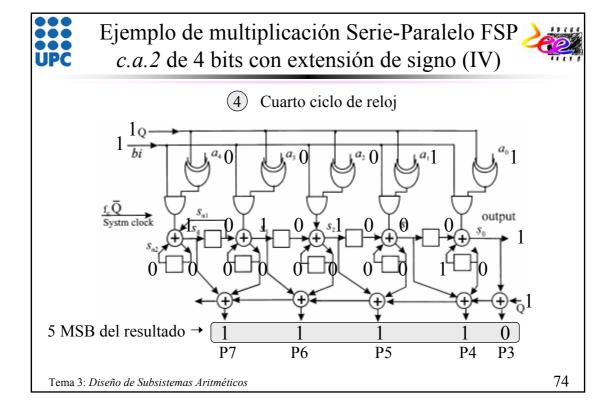

# 3.4.2.4 Multiplicadores Serie Paralelo c.a.2 con algoritmo FSP

69

# Multiplicación Serie-Paralelo FSP *c.a.2* de 4 bits con extensión de signo

- Vale cero el resto durante los *N-1* primeros periodos de reloj y el circuito actúa como un CSAS

- La entrada Q vale uno en el ciclo N de reloj

Tema 3: Diseño de Subsistemas Aritméticos

## UPC

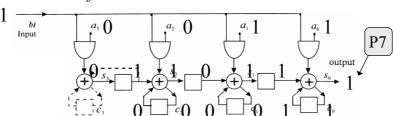

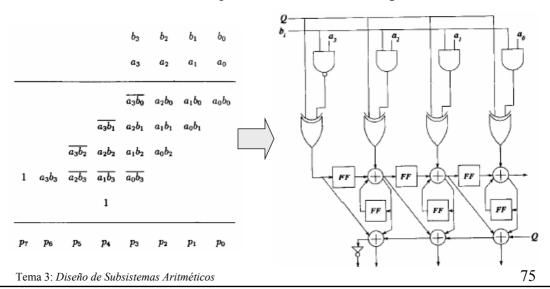

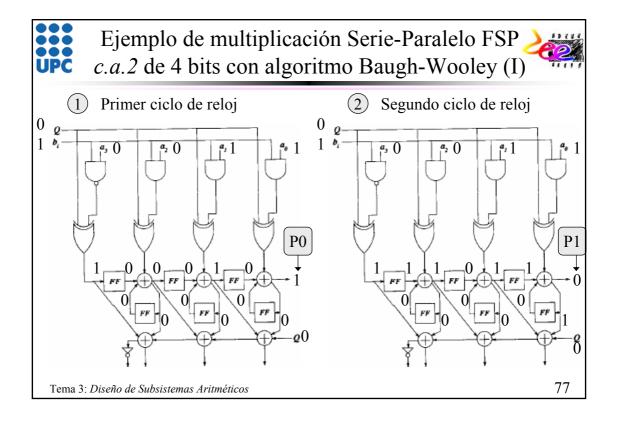

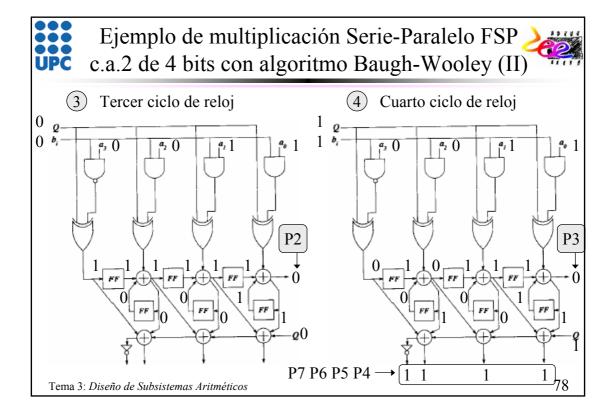

## Multiplicación Serie-Paralelo FSP

## c.a.2 de 4 bits con algoritmo Baugh-Wooley (I)

El hardware es más reducido que en caso de FSP con signo extendido

## Multiplicación Serie-Paralelo FSP c.a.2 de 4 bits con algoritmo Baugh-Wooley (II)

- Durante los N-1 primeros productos parciales Q = 0, y se realizan una operación NAND y N-1 AND

- En el último producto parcial, Q = 1 y se realiza una operación AND y *N-1* NAND

*Ejemplo:* multiplicador SPM de 4 bits, producto de 3d x -5d

$$\begin{array}{c}

0011 \quad (3d) \longleftarrow \text{ Dato paralelo} \\

\underline{x \quad 1011} \quad (-5d) \longleftarrow \text{ Dato serie} \\

1011 \\

+ \quad 1000 \\

10100 \\

\hline

P_7P_6P_5P_4P_3P_2P_1P_0 \longrightarrow 11110001 \quad (-15d)

\end{array}$$

Tema 3: Diseño de Subsistemas Aritméticos

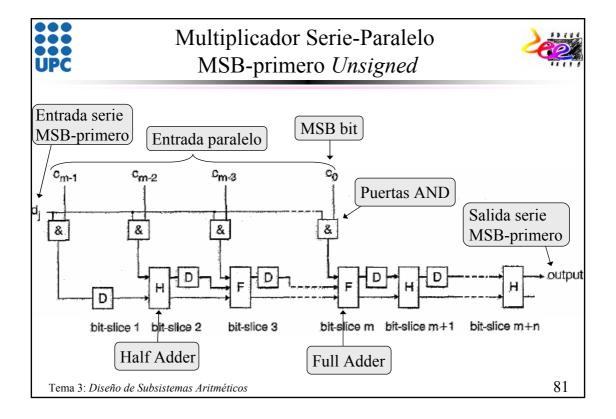

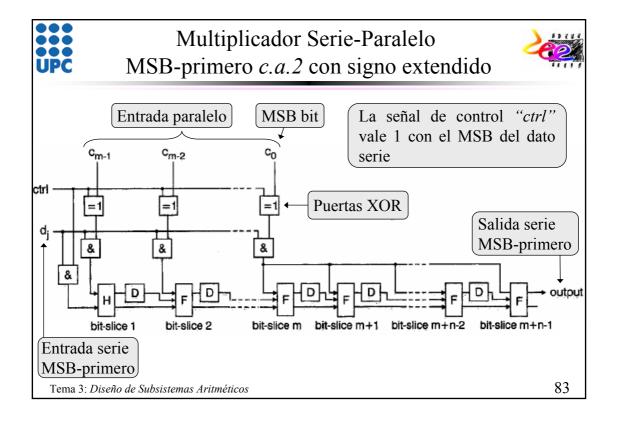

## 3.4.2.5 Multiplicadores Serie Paralelo MSB-primero

79

#### Introducción

- El en SPM MSB-primero, el operando serie se introduce en el multiplicador empezando por el bit de mayor peso y el resultado se obtiene empezando por el MSB

- Ventajas:

- Los convertidores ADC de aproximaciones sucesivas y pipelined proporcionan el resultado de la conversión empezando por el MSB

- Los algoritmos que calculan la raíz cuadrada y la división son del tipo MSB-primero

- Con el multiplicador MSB-primero es más fácil truncar el resultado o eliminar los bits menos representativos

- La ausencia de realimentación en la estructura de este tipo de multiplicadores permite incrementar la velocidad del reloj

### Latencia en el SPM MSB-primero Unsigned

*Latencia*: nº de ciclos de reloj desde que entra el MSB del dato hasta que sale el MSB del resultado

- En el multiplicador MSB-primero *Unsigned* la latencia es igual al número de bits del operando serie

- En el multiplicador LSB-primero la latencia es de un ciclo de reloj

En determinados casos es conveniente utilizar el MSB-primero ya que la latencia global del diseño es menor

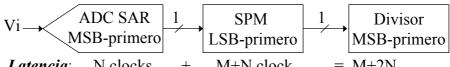

$\it Ejemplo:$  Cálculo de la latencia global de un sistema procesador con multiplicador de  $\it MxN$

*Latencia*: N clocks + M+N clock = M+2N

Con multiplicador MSB-primero la latencia es:  $1 \operatorname{clock} + \operatorname{N} \operatorname{clock} = \operatorname{N+1}$

## 3.4.3 Multiplicadores Serie Secuencial

85

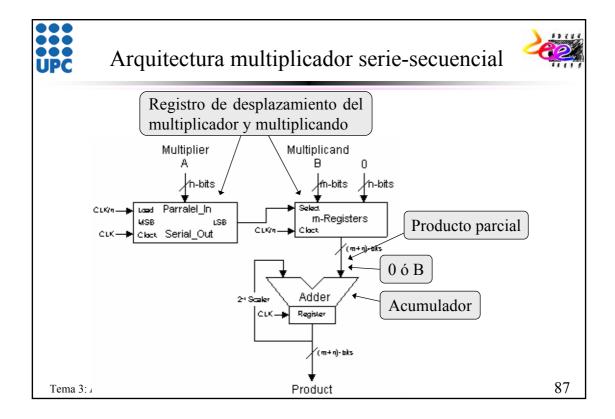

### Algoritmo multiplicador Serie Secuencial

- El algoritmo de funcionamiento es similar al multiplicador Serie-Paralelo

- La diferencia está en la utilización de un sumador paralelo en lugar de un sumador serie para sumar los productos parciales

- Algoritmo:

- El multiplicando (M bits) y el multiplicador (N bits) se cargan en sendos registros de desplazamiento

- Se realizan los productos parciales de los bits del multiplicador (bit a bit) con el multiplicando empezando por el LSB

- Los sucesivos productos parciales se suman con el acumulador

- El resultado definitivo se obtiene después de N+M ciclos de reloj

3.4.4 Multiplicadores Serie-Serie

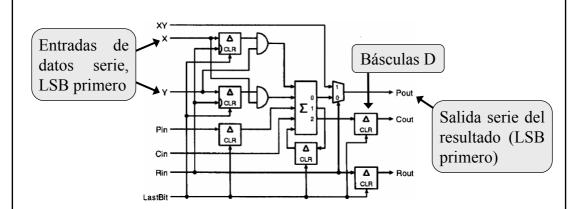

### Algoritmo del multiplicador Serie-Serie

- Mediante un cálculo iterativo se puede extraer el valor del producto de dos números X e Y de N bits de longitud

- El algoritmo es válido para números positivos y para números en c.a.2

- Si los dos números no son de igual longitud, se debe igualar su longitud:

- No's Unsigned: se rellena con ceros a la izquierda

- No's Signed: se extiende el signo

- El resultado se obtiene después de 2N iteraciones

#### Algoritmo de cálculo de producto

$$\overline{Q}_i = \left[ \frac{1}{2} \cdot \left( \overline{Q}_{i-1} + x_i \cdot Y_{i-1} + y_i \cdot X_{i-1} + 2^i \cdot x_i \cdot y_i \right) \right] \quad para \quad i < N$$

$$\overline{Q}_{i} = \left[ \frac{1}{2} \cdot \left( \overline{Q}_{i-1} + x_{N-1} \cdot Y_{N-2} + y_{N-1} \cdot X_{N-2} \right) \right] \quad para \quad i \ge N$$

$x_i$ : entrada actual,  $X_i$ : entrada anterior

Tema 3: Diseño de Subsistemas Aritméticos

89

### Célula básica del multiplicador Serie-Serie

Tema 3: Diseño de Subsistemas Aritméticos

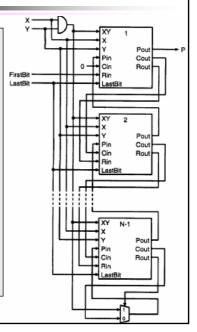

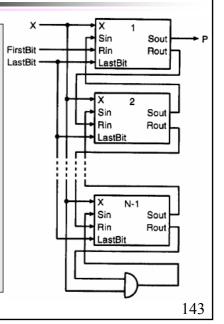

#### Multiplicador Serie-Serie

- Se necesitan *N-1* células básicas para hacer el producto de dos números de *N* bits

- El resultado se obtiene después de 2N ciclos de reloj

- Durante los *N* primeros ciclos se introducen los 2 operandos (*LSB* primero) por las entradas serie

- Durante el resto de ciclos se introducen ceros (nº positivos) o se extiende el signo (nº c.a.2)

- Entradas de control del multiplicador:

- *FirsBit:* Se pone a nivel alto durante el primer ciclo de señal de reloj

- *LastBit*: Se pone a 1 durante el ciclo que precede a la siguiente multiplicación

Tema 3: Diseño de Subsistemas Aritméticos

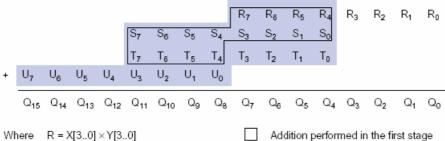

## 3.4.5 Multiplicadores Pipelined

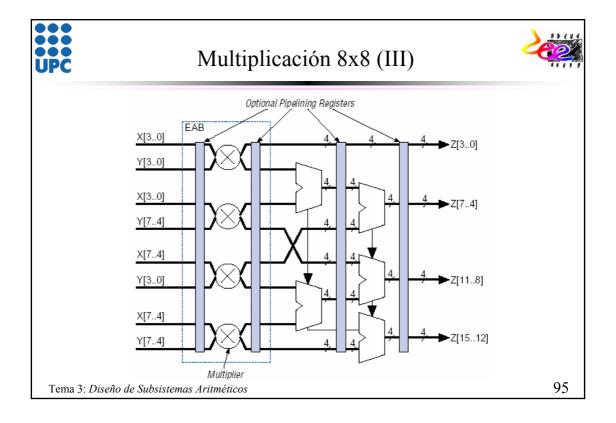

## Multiplicación 8x8 (I)

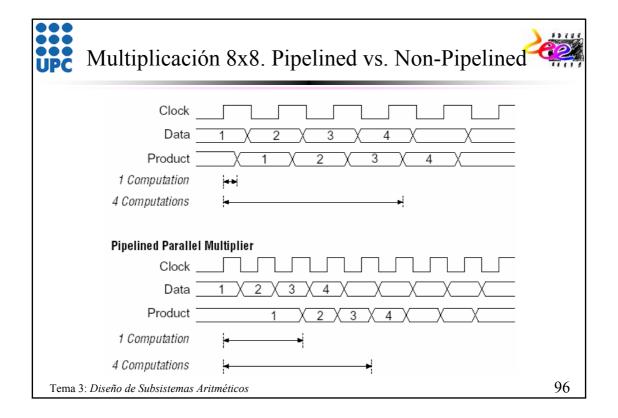

- Los multiplicadores pipelined permiten aumentar la velocidad de cálculo realizando varios productos en paralelo

- El producto se puede realizar mediante con 4 multiplicadores y 2 etapas de sumadores

X[7..4] parte alta del dato X

X[3..0] parte baja del dato X

Y[7..4] parte alta del dato Y

Y[3..0] parte baja del dato Y

X[7..4] X[3..0]  $\times Y[7..4]Y[3..0]$

$X[7..4] \times Y[3..0]$

$X[3..0] \times Y[3..0]$

$X[7..4] \times Y[7..4]$

$X[3..0] \times Y[7..4]$

$X[7..4] \times Y[7..4] \times 16^{2} + ((X[7..4] \times Y[3..0]) + (X[3..0] \times Y[7..4])) \times 16^{1} + X[7..4] \times Y[3..0] \times 16^{0}$

Tema 3: Diseño de Subsistemas Aritméticos

93

## Multiplicación 8x8 (II)

- Cada producto parcial se realiza con un multiplicador de 4x4 bits

- Los resultados parciales de los productos se suman con 2 etapas de sumadores de 4+4 bits

Where  $R = X[3..0] \times Y[3..0]$

$S = X[3..0] \times Y[7..4]$

$T = X[7..4] \times Y[3..0]$

$U = X[7..4] \times Y[7..4]$

Tema 3: Diseño de Subsistemas Aritméticos

94

Addition performed in the second stage

## 3.4.6 Algoritmo L-Booth

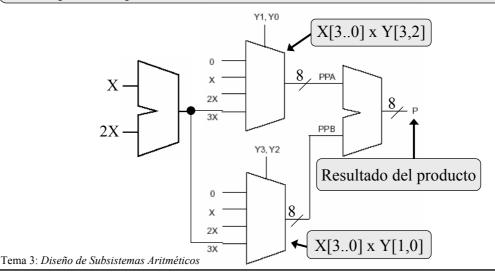

### Producto 4x4 con algoritmo L-Booth

El producto se realiza en dos partes: X[3..0] x Y[1,0] y X[3..0] x Y[3,2]

|                                         |      |      |      |       |       | X3    | X2    | X1    | X0   |

|-----------------------------------------|------|------|------|-------|-------|-------|-------|-------|------|

| Only 2 LSB used                         | >    |      |      |       | x     |       |       | Y1    | Y0   |

| if Y1=0,Y0=0                            | 1    | 0    | 0    | 0     | 0     | 0     | 0     | 0     | 0    |

| ifY1=0,Y0=1                             | 1    | 0    | 0    | 0     | 0     | Х3    | X2    | X1    | X0   |

| if Y1=1, Y0=0                           | 1    | 0    | 0    | 0     | Х3    | X2    | X1    | XO    | 0    |

| ifY1=1, Y0=1                            | - 1  | 0    | 0    | 0     | Х3    | X3+X2 | X2+X1 | X1+X0 | 0    |

| Multiplexer A result                    | >    | 0    | 0    | PPA5  | PPA4  | PPA3  | PPA2  | PPA1  | PPA0 |

| Draduates maraiales                     |      |      | ,    |       |       |       |       |       |      |

| Productos parciales                     |      |      |      |       |       | X3    | X2    | X1    | X0   |

| Only 2 MSB used                         | >    |      |      |       | x     | Y3    | Y2    |       |      |

| if Y3=0,Y2=0                            | 1    | 0    | 0    | 0     | 0     | 0     | 0     | 0     | 0    |

| if Y3=0, Y2=1                           |      | 0    | 0    | X3    | X2    | X1    | X0    | 0     | 0    |

| if Y3=1, Y2=0                           |      | 0    | Х3   | X2    | X1    | X0    | 0     | 0     | 0    |

| if Y2=1, Y2=1                           |      | 0    | Х3   | X3+X2 | X2+X1 | X1+X0 | 0     | 0     | 0    |

| Multiplexer B result                    | >    | PPB7 | PPB6 | PPB5  | PPB4  | PPB3  | PPB2  | 0     | 0    |

| El producto final es la sun             | าล   |      |      |       |       |       |       |       |      |

| _                                       |      | 0    | 0    | PPA5  | PPA4  | PPA3  | PPA2  | PPA1  | PPA0 |

| de los dos productos parciale           | S +  | PPB7 | PPB6 | PPB5  | PPB4  | PPB3  | PPB2  | 0     | 0    |

| Final product                           | _> _ | P7   | P6   | P5    | P4    | P3    | P2    | P1    | P0   |

| Tema 3: Diseño de Subsistemas Aritmétic | OS   |      |      |       |       |       |       |       | 99   |

|                                         |      |      |      |       |       |       |       |       |      |

## Implementación del multiplicador con el algoritmo L-Booth

100

La implementación del algoritmo *L-Booth* está basada en multiplexores que es ideal para la arquitectura interna de las FPGAs de *Actel*

### Multiplicador L-Booth Pipelined

- Para aumentar la velocidad se introducen registros entre los niveles de lógica

- La distribución de registros es óptima cuando cada etapa tiene un retardo similar

#### Implementación combinacional

#### Implementación pipelined

## Latencia y velocidad de cálculo con implementación Pipelined

- Con la implementación pipelined el resultado se retarda tantos ciclos de reloj como etapas de registros se añaden.

- En este caso la latencia o retardo que existe entre las entradas de datos y la salida del sumador es de un ciclo de reloj

Velocidad de cálculo del multiplicador implementado con la FPGA de *Actel* 1225XL-1: combinacional -> 24 MHz

pipelined -> 57MHz

## 3.4.7 Multiplicadores de hardware reducido

## 3.5.1 Divisor Paralelo-Paralelo

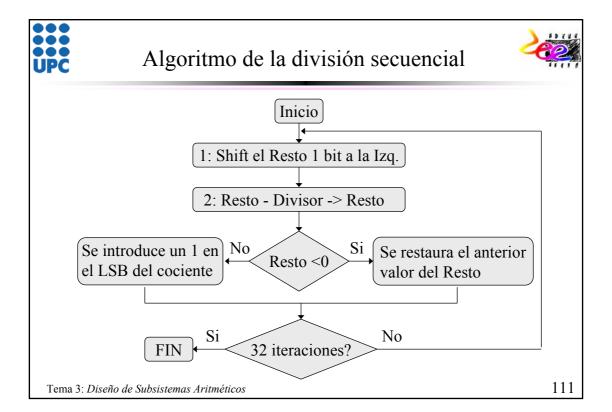

## 3.5.2 Divisor secuencial

## Ejemplo de división con el algoritmo secuencial

#### División de 0000 0111 por 0010: cociente = 0011

| Iteración | Paso                                         | Cociente | Divisor | Resto     |

|-----------|----------------------------------------------|----------|---------|-----------|

| 0         | Valor inicial                                | 0000     | 0010    | 0000 0111 |

| 1         | 1: Shift Resto Izq.                          | 0000     | 0010    | 0000 1110 |

|           | 2: Resto = Resto-Divisor                     | 0000     | 0010    | 1110 1110 |

|           | 3b: Resto $<0 \Rightarrow$ +Div, sll Q, Q0=0 | 0000     | 0010    | 0000 1110 |

| 2         | 1: Shift Resto Izq.                          | 0000     | 0010    | 0001 1100 |

|           | 2: Resto = Resto-Divisor                     | 0000     | 0010    | 1111 1100 |

|           | 3b: Resto $<0 \Rightarrow$ +Div, sll Q, Q0=0 | 0000     | 0010    | 0001 1100 |

| 3         | 1: Shift Resto Izq.                          | 0000     | 0010    | 0011 1000 |

|           | 2: Resto = Resto-Divisor                     | 0000     | 0010    | 0001 1000 |

|           | 3a: Resto≥0 => sll Q, Q0=1                   | 0001     | 0010    | 0001 1000 |

| 4         | 1: Shift Resto Izq.                          | 0001     | 0010    | 0011 0000 |

|           | 2: Resto = Resto-Divisor                     | 0001     | 0010    | 0001 0000 |

|           | 3a: Resto≥0 => sll Q, Q0=1                   | 0011     | 0010    | 0001 0000 |

sll: desplazamiento a la izquierda

# 3.6 Operaciones aritméticas en coma flotante

113

3.6.1 Formatos de representación en coma flotante

## Representación en coma flotante Standard IEEE 754 (I)

Existen diferentes formatos para representar números en coma flotante Formato IEEE 754:

$(-1)^{S}$  x (1+Mantisa) x  $2^{E}$

| Simple precisión: | 1 bit   | 8 bits    | 23 bits |

|-------------------|---------|-----------|---------|

|                   | Signo 1 | Exponente | Mantisa |

|                   | 1 bit   | 11 bits   | 20 bits |

Doble precisión:

| Signo | Exponente | Mantisa |  |

|-------|-----------|---------|--|

|       |           | 32 bits |  |

|       |           | Mantisa |  |

Tema 3: Diseño de Subsistemas Aritméticos

115

## Representación en coma flotante Standard IEEE 754 (II)

Signo (S):  $\begin{cases} 0 \text{ para números positivos} \\ 1 \text{ para números negativos} \end{cases}$

#### Mantisa:

- Representa un número *unsigned* fraccionario entre 0 y 1

- El MSB de la mantisa tiene peso 2<sup>-1</sup>

#### **Exponente**:

- Se utiliza formato llamado biased notation

- Este formato permite representar números positivos y negativos utilizando solo números positivos

- Al manejar solo números positivos se simplifica el cálculo del exponente en operaciones aritméticas

#### Exponente en formato Bias Notation

- Para simple precisión se debe sumar al exponente el valor 127 y para doble precisión el valor 1023

- Para simple precisión el margen de valores del exponente con formato *Bias Notation* y en valor real es:

Formato *Bias* del exponente: 0 < -> 255 Valor real del exponente: -127 < -> 128

• Para doble precisión el margen de valores del exponente con formato *Bias Notation* y en valor real es:

Formato Bias del exponente: 0 <-> 2047Valor real del exponente: -1023 <-> 1024

Tema 3: Diseño de Subsistemas Aritméticos

117

## Ejemplos de formato IEEE 754 (I)

Ejemplo 1: El número -0.75 decimal en binario sería -1.1 x 2-1

• La representación en coma flotante con simple precisión es:

$$(-1)^S$$

x  $(1 + Mantisa)$  x  $2^{(exponente real+127)}$

lo que dá lugar:

$$(-1)^1$$

x  $(1 + .1000\ 0000\ 0000\ 0000\ 0000\ 000)$  x  $2^{(-1+127)}$

Signo: 1

Mantisa: 1000 0000 0000 0000 0000 000

Exponente: 0111 1110

- Con doble precisión:

Signo: 1

0000 0000

Exponente: 01111111110

### Ejemplos de formato IEEE 754 (II)

Ejemplo 2: Cúal es el valor del número siguiente en decimal

Signo: 1

Mantisa: 0100 0000 0000 0000 0000 000

Exponente: 1000 0001

$(-1)^1$  x  $(1 + .0100\ 0000\ 0000\ 0000\ 0000\ 000)$  x  $2^{(129-127)}$

$$(-1)^1 \times (1 + 0.25) \times 2^{(129-127)} = -1 \times 1.25 \times 2^2 = -1.25 \times 4 = -5.0$$

Tema 3: Diseño de Subsistemas Aritméticos

119

#### Notación coma flotante de Altera

Signo (S):  $\begin{cases} 1 & \text{para números positivos} \\ 0 & \text{para números negativos} \end{cases}$

#### Mantisa:

- Representa un número *unsigned* fraccionario entre 0 y 1

- El MSB de la mantisa tiene peso 2<sup>-1</sup>

- El resultado de las operaciones se ajusta para que MSB = 1 y aprovechar al máximo la precisión que proporciona la mantisa

#### **Exponente**:

- Se utiliza el formato llamado *offset 2*<sup>(n-1)</sup>

- Este formato permite representar números positivos y negativos utilizando solo números positivos

- Al manejar solo números positivos se simplifica el cálculo del exponente en operaciones aritméticas

## Exponente en formato offset 2<sup>(n-1)</sup>

- Se debe sumar al exponente el valor  $2^{(n-1)}$ , donde n es el número de bits utilizados para expresar el exponente

- Por ejemplo para n = 7,  $2^{(n-1)} = 64$ , y el margen de valores del exponente en formato *offset*  $2^{(n-1)}$  y en valor real es:

Formato *offset* del exponente: 0 < > 127Valor real del exponente: -64 < > 63

• Ejemplos:

Exponente real Formato offset  $2^{(n-1)}$ 10 74 -10 54

Tema 3: Diseño de Subsistemas Aritméticos

121

## Ejemplos de coma flotante con formato de Altera (I)

#### Mantisa de 8 bits y exponente de 7 bits

#### Ejemplo 1: Mayor número positivo:

+ 1111 1111b 1111111b

$= +0.1111 \ 11111b \ x \ 2^{(11111111b-1000000b)}$

$= +0.1111 \ 11111b \ x \ 2^{01111111b}$

$= +0.1111 \ 11111b \ x \ 2^{63d}$

$= +1111 \ 1111.0b \ x \ 2^{55d}$

$= +255 d \times 2^{55 d} = +9.187343239836 e+18$

#### Ejemplo 2: Mayor número negativo:

-1111 1111b 1111111b

$= -255 d \times 2^{55 d} = -9.187343239836 e + 18$

## Ejemplos de coma flotante con formato de Altera (II)

#### Ejemplo 3: Menor número (próximo a cero):

$\pm 1000\ 0000b\ 0000000b$

$= \pm \ 0.1000 \ 0000b \ x \ 2^{(0000000b-1000000b)}$

$= \pm 0.1000~0000b~x~2^{(0d - 64d)}$

$= \pm 0.1000~0000b \text{ x } 2^{-64d}$

$= \pm 1000\ 0000.0b \ x \ 2^{-72d}$

$= \pm 128 d \times 2^{-72 d} = \pm 2.71050543121 \text{ e-}20$

#### Ejemplo 2: Valor típico:

-1100 0111b 1001001b

$= +0.1100\ 0111b\ x\ 2^{(1001001b-1000000b)}$

$= +0.1100\ 0111b\ x\ 2^{1101b}$

$= +0.1100 \ 0111b \ x \ 2^{9d}$

$=+1100\ 0111.0b\ x\ 2^{1d}$

$= +199 d \times 2 = +398$

Tema 3: Diseño de Subsistemas Aritméticos

123

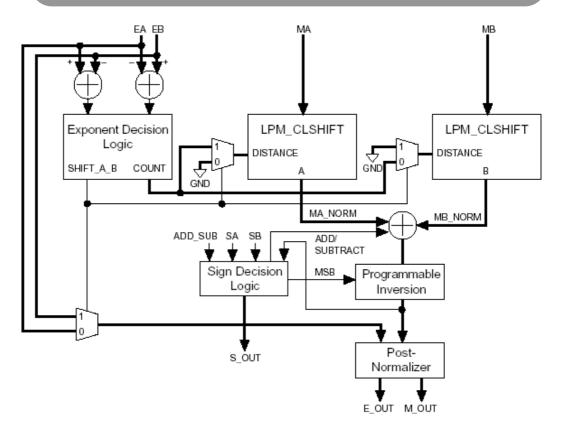

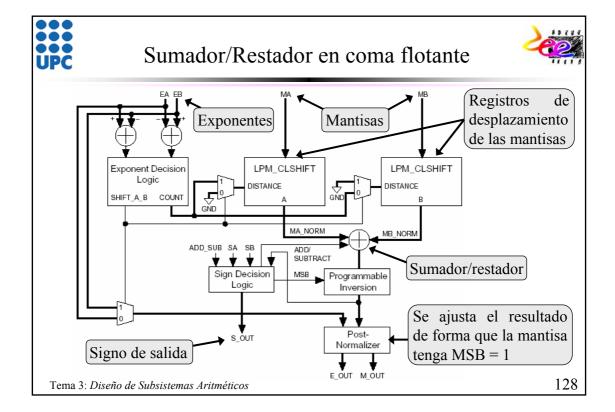

## 3.6.2 Suma/Resta en coma flotante

#### Suma/resta en coma flotante

El proceso de suma/resta en coma flotante involucra los siguientes pasos:

- Paso 1: se igualan los exponentes

- Se comparan los exponentes para determinar el número mayor

- Se desplaza a la derecha la mantisa del número menor tantas posiciones como resulte de la diferencia de exponentes (se pierde resolución en el número menor)

- Si el número de desplazamientos es superior al número de bits de la mantisa se desprecia el operando menor (= 0)

- Paso 2: Se realiza la suma/resta de las mantisas con un restador binario convencional

- Paso 3: Si el resultado de la suma/resta de las mantisas es negativo se invierte para obtener la mantisa en positivo

Tema 3: Diseño de Subsistemas Aritméticos

125

## Ejemplos de suma/resta en coma flotante (I)

Ejemplo 1: suma de dos números positivos:

$0.3046875d \times 2^{45} + 0.34375 \times 2^{44}$

$= +0.01001110b \times 2^{45} + +0.01011000b \times 2^{44}$

$= +0.01001110b \times 2^{45} + +0.00101100b \times 2^{45}$

$= +0.01111010b \times 2^{45}$

$= +0.11110100b \times 2^{44}$

$= +0.953125 d \times 2^{(44-64)} = +0.953125 d \times 2^{-20} = +9.089708328 e-7$

Ejemplo 2: número negativo más número positivo:

$-0.82421875d \times 2^{76} + +0.25390625 \times 2^{75}$

$= -0.11010011b \times 2^{76} + +0.01000001b \times 2^{75}$

=  $-0.11010011b \times 2^{76} + +0.00100000b \times 2^{76}$

$= -0.10110011b \times 2^{76}$

=  $-0.69921875 d \times 2^{(76-64)} = -0.69921875 d \times 2^{12} = -2.864 e3$

126

El desplazamiento de

pérdida de resolución

mantisa

### Ejemplos de suma/resta en coma flotante (II)

#### *Ejemplo 3*: número negativo más número positivo (insignificante):

$-0.5d \times 2^{89} + +0.5d \times 2^{68}$

= -0.100000000b x  $2^{89} + +0.100000000$ b x  $2^{68}$

$= -0.100000000 \text{ x } 2^{89} + +0.000000000 \text{ x } 2^{89}$

$= -0.100000000 \text{ x } 2^{89}$

$= -0.5 d \times 2^{89} = -0.5 d \times 2^{(89-64)} = -1.6777216 e7$

## El operando positivo es insignificante comparado con el negativo

#### Ejemplo 4: número positivo más número negativo:

$+0.5 \times 2^{64} + -0.875 \times 2^{63}$

$= +0.100000000b \times 2^{64} + -0.111000000b \times 2^{63}$

$= +0.100000000 \text{ x } 2^{64} + -0.011100000 \text{ x } 2^{64}$

$= +0.00010000b \times 2^{64}$

= +0.100000000b x  $2^{61}$  = +0.5 x  $2^{(61-64)}$  = +0.5 x  $2^{-3}$  = 0.0625d

Tema 3: Diseño de Subsistemas Aritméticos

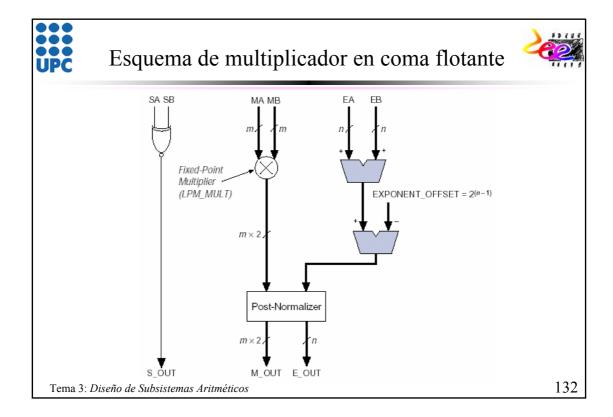

## 3.6.3 Multiplicación en coma flotante

129

### Multiplicación en coma flotante

El proceso de multiplicación en coma flotante involucra los siguientes pasos:

- Paso 1: Se multiplican las mantisas con un multiplicador convencional

- *Paso 2:* Se suman los exponentes y se resta el offset del resultado:  $(EA-2^{(n-1)}) + (EB-2^{(n-1)}) = EA+EB -2 \times 2^{(n-1)}$   $(EA+EB -2 \times 2^{(n-1)}) 2^{(n-1)} = EA+EB -2^{(n-1)}$

- *Paso 3:* El signo del resultado se obtiene con la operación XNOR entre el signo de número A (SA) y el signo del número B (SB)

- *Paso 4:* Si es necesario se ajusta el resultado para que la mantisa tenga MSB=1

## Ejemplo de multiplicación en coma flotante

#### Multiplicación de 39936 y 13303808

| Decimal Equivalent<br>(Exponent in Excess 0)                   | Binary<br>(Exponent in Excess 64)                              |

|----------------------------------------------------------------|----------------------------------------------------------------|

| $(39 \times 2^{10d}) \times (203 \times 2^{6d})$               | $(00100111.0 \times 2^{74}) \times (11001011.0 \times 2^{70})$ |

| $(0.609375 \times 2^{16d}) \times (0.79296875 \times 2^{14d})$ | $(0.10011100 \times 2^{80}) \times (0.11001011 \times 2^{78})$ |

| 7917 × 2 <sup>16d</sup>                                        | 0.0001111011101101 × 280                                       |

| 63336 × 2 <sup>13d</sup>                                       | 0.1111011101101000 × 2 <sup>77</sup>                           |

| 518,848,512                                                    | _                                                              |

Tema 3: Diseño de Subsistemas Aritméticos

#### Detección de errores en coma flotante

Errores habituales en operaciones en coma flotante:

- *Overflow*: cuando el valor del exponente sobrepasa el número de bits disponibles.

- Por ejemplo, para 7 bits de exponente se tiene *overflow* cuando el exponente es mayor de 63.

- *Underflow*: cuando el valor del exponente está por debajo del valor mínimo.

- Por ejemplo, para 7 bits de exponente se tiene *underflow* cuando el exponente es menor de -64.

Tema 3: Diseño de Subsistemas Aritméticos

133

## 3.7 Funciones especiales

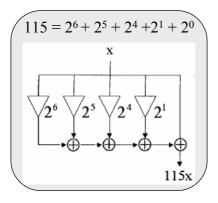

## 3.7.1 Multiplicación por una constante

135

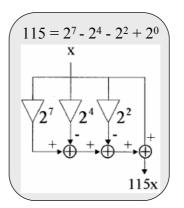

## Algoritmo Dempster-Macleod

Permite diseñar un multiplicador mediante un número mínimo de sumadores/restadores

Ejemplo: multiplicación por 115

Tema 3: Diseño de Subsistemas Aritméticos

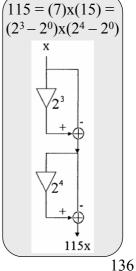

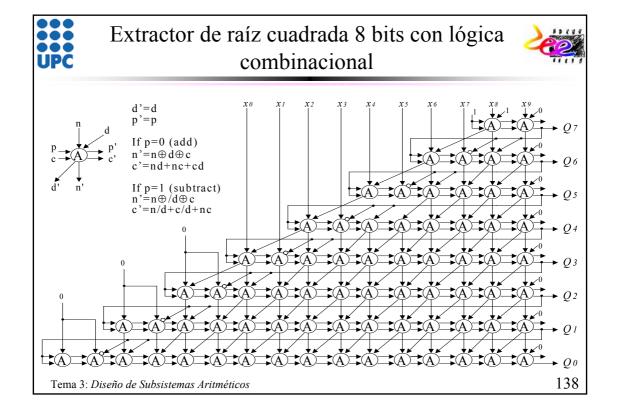

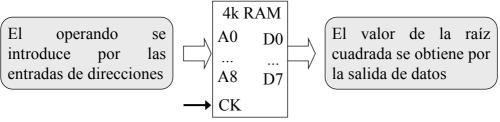

## 3.7.2 Raíz cuadrada

## Extractor de raíz cuadrada 8 bits basado en LUT

- Se almacena en una LUT implementada mediante memoria RAM los valores de la raíz cuadrada

- La velocidad de calculo se incrementa considerablemente ya que equivale al tiempo de acceso de la memoria RAM

- La memoria RAM de las FPGA's de Xilinx permiten implementar con LUT este tipo de funciones aritméticas

#### Bloque memoria RAM

Tema 3: Diseño de Subsistemas Aritméticos

139

## 3.7.3 Cuadrado de un número: X<sup>2</sup>

## Algoritmo de X<sup>2</sup> Serie-Serie

- Mediante un cálculo iterativo se puede extraer el valor de X<sup>2</sup>

- El algoritmo es un caso particular del multiplicador Serie-Serie, pero utilizando un hardware simplificado

- El resultado correcto se obtiene después de 2N iteraciones

#### Algoritmo de cálculo de X<sup>2</sup>

$$\overline{Q}_{i} = \left[\frac{1}{2} \cdot \left(\overline{Q}_{i-1} + 2 \cdot x_{i} \cdot X_{i-1} + 2^{i} \cdot x_{i}\right)\right] \quad para \quad i < N$$

$$\overline{Q}_{i} = \left[\frac{1}{2} \cdot \left(\overline{Q}_{i-1} + 2 \cdot x_{N-1} \cdot X_{N-2}\right)\right] \quad para \quad i \ge N$$

$x_i$ : entrada actual

$X_i$ : entrada anterior

Tema 3: Diseño de Subsistemas Aritméticos

141

## Célula básica del algoritmo X<sup>2</sup>

# Multiplicador X<sup>2</sup>

- Se necesitan *N-1* células básicas para obtener el cuadrado de un número de *N* bits

- El resultado se obtiene después de 2N ciclos de reloj

- Durante los *N* primeros ciclos se introduce el operando (*LSB* primero) por la entrada serie

- Durante el resto de ciclos se introducen ceros (nº positivos) o se extiende el signo (nº c.a.2)

- Entradas de control del elevador al cuadrado:

- *FirsBit*: Se pone a nivel alto durante el primer ciclo de señal de reloj

- *LastBit*: Se pone a 1 durante el ciclo que precede a la siguiente multiplicación

Tema 3: Diseño de Subsistemas Aritméticos

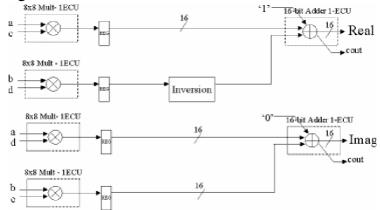

# 3.7.4 Multiplicación de complejos

# Multiplicación de complejos

La multiplicación de números complejos viene dada por:

- (a + jb)(c + jd) = (ac-bd) + j(ad + bc)

- Parte Real = ac-bd

- Parte Imaginaria = ad+bc

Tema 3: Diseño de Subsistemas Aritméticos

145

# 3.8 Bloques aritméticos en FPGA's

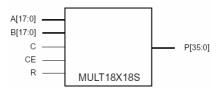

# 3.8.1 Multiplicadores de la familia Spartan-3

147

### Características generales

- La familia Spartan-3 dispone de multiplicadores 18x18 bits (c.a.2) integrados

- Prestaciones:

- ➤ Realizan el producto con y sin signo (17x17 bits unsigned)

- Se pueden conectar en cascada o con CLB's para realizar funciones complejas

- ➤ Pueden realizar funciones adicionales: desplazamiento, generación de valor absoluto, generación del complemento a 2 de un número, etc...

#### <u>Multiplicador Combinacional</u>

# A[17:0] — P[35:0] B[17:0] — MULT18X18

#### Multiplicador con registro

Tema 3: Diseño de Subsistemas Aritméticos

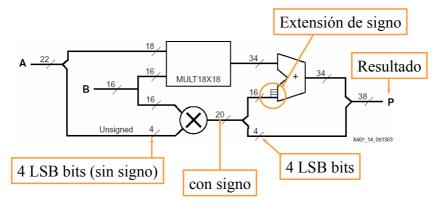

#### Multiplicación expandida

- Es posible multiplicar números mayores de 18 bits descomponiendo el producto en procesos más simples

- Ejemplo: producto 22 x 16 bits con signo

Tema 3: Diseño de Subsistemas Aritméticos

149

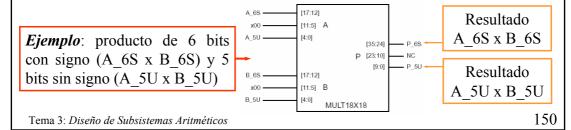

# Dos productos en un Multiplicador

• Es posible realizar dos multiplicaciones de dos números pequeños con un solo multiplicador siempre y cuando no se solapen los resultados

#### Tamaños permitidos para los operandos

| X * X       |               | Y * Y       |               |

|-------------|---------------|-------------|---------------|

| Signed Size | Unsigned Size | Signed Size | Unsigned Size |

| 7 X 7       | 6 X 6         | -           | 4 X 4         |

| 6 X 6       | 5 X 5         | -           | 5 X 5         |

| 5 X 5       | 4 X 4         | 3 X 3       | 6 X 6         |

| 4 X 4       | 3 X 3         | 3 X 3       | 7 X 7         |

| 3 X 3       | 2 X 2         | 4 X 4       | 8 X 8         |

# Aplicaciones alternativas: desplazamiento

- Un multiplicador se puede utilizar para desplazar un operando de 0 a 16 posiciones multiplicando por 2<sup>n</sup>

- Dos tipos de desplazamiento:

- ➤ Lógico → el bit de mayor peso del dato a desplazar es cero (positivo) ⇒ los bits de mayor peso del resultado son cero

- ➤ Aritmético → se extiende el bit de signo del dato a desplazar ⇒ los bits de mayor peso del resultado tienen el signo del dato desplazado

Tema 3: Diseño de Subsistemas Aritméticos

151

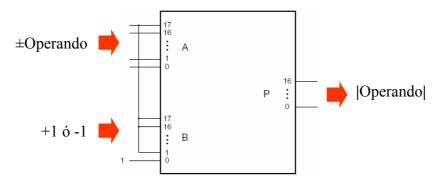

# Aplicaciones alternativas: valor absoluto

- Para calcular el valor absoluto de un número se multiplica por 1 si es positivo y por -1 si es negativo

- En c.a.2:

- ➤ 1 positivo ⇒ 00 0000 0000 0000 0001

- ➤ 1 negativo ⇒ 11 1111 1111 1111

Tema 3: Diseño de Subsistemas Aritméticos

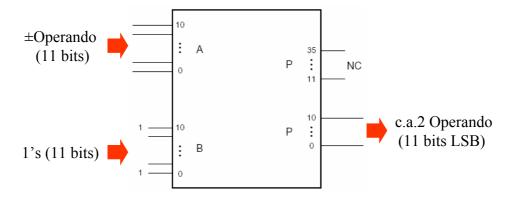

# Aplicaciones alternativas: generación c.a.2

• Para generar el c.a.2 de un operando se multiplica por un número de 1's de la misma longitud que el operando

Tema 3: Diseño de Subsistemas Aritméticos

153

# Aplicaciones alternativas: producto de complejos producto en coma flotante

- Producto de dos números complejos:  $(a+ib)\cdot(c+id) = ac-bd + i(ad+cb)$

- Se puede solucionar con tres productos reales: ac, bd y (a+b)(c+d)

- ➤ Parte real del resultado: ac-bd

- ➤ Parte imaginaria del resultado: (a+b)(c+d)-ac-bd = ad+cb

- Se puede implementar un multiplicador en coma flotante de 32 bits con 4 multiplicadores y algunos CLB

# 3.8.2 XtremeDSP de la familia Virtex-4: DSP48

155

# Características generales

- La familia *Virtex-4* dispone de 32 a 192 elementos de procesado digital de señal denominados *XtremeDSP*

- Cada *XtremeDSP* incorpora 2 DSP48 *slices* que pueden realizar múltiples funciones:

- ➤ Multiplicación

- ➤ Multiplicación y acumulación (MACC)

- ➤ Multiplicación y suma

- > Sumador de tres entradas

- **≻** Comparador

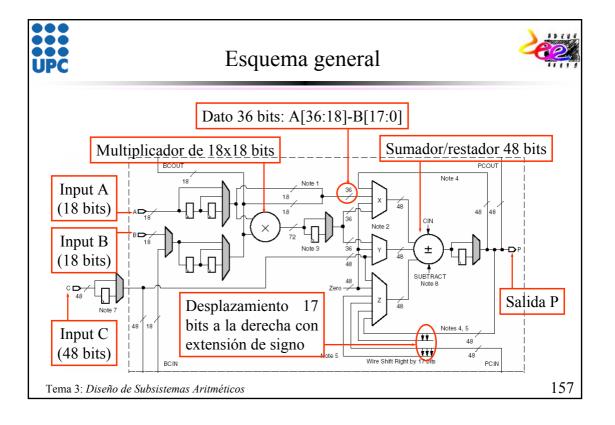

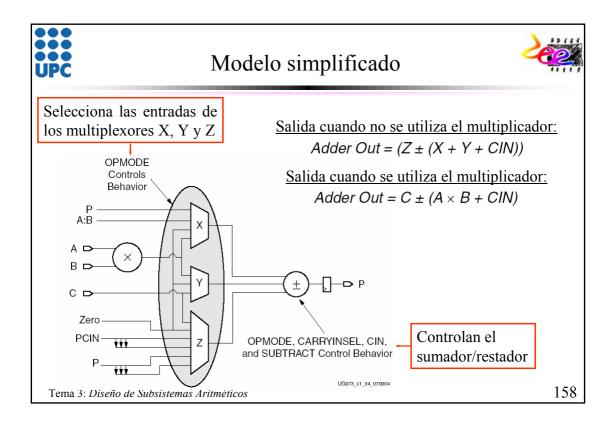

# Aplicaciones: producto 35x18 bits c.a.2 (I)

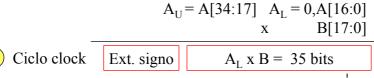

Un *slice* puede realizar múltiples operaciones parciales durante sucesivos periodos de reloj que combinadas den lugar a operaciones complejas Ejemplo: Producto 35x18 bits = A[34:0] x B[17:0] en dos ciclos de reloj

A se descompone en dos números: uno negativo  $A_U = A[34:17]$  y otro positivo  $A_L = 0, A[16:0]$

Tema 3: Diseño de Subsistemas Aritméticos

159

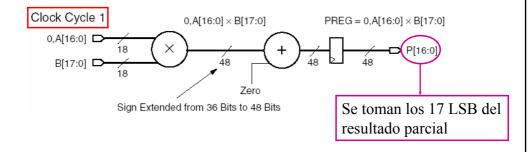

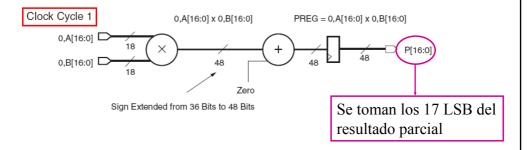

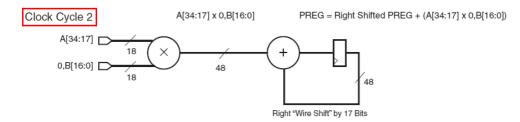

1 Ciclo clock

# Aplicaciones: producto 35x18 bits c.a.2 (II)

1 Ciclo clock

En el primer ciclo de reloj se realiza el producto parcial  $P = (0,A[16:0]) \times B[17:0]$

OPMODE: Multiplicación

Tema 3: Diseño de Subsistemas Aritméticos

#### Aplicaciones: producto 35x18 bits c.a.2 (III)

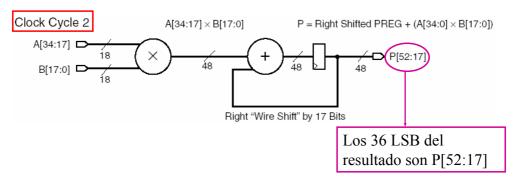

Ciclo clock

En el segundo ciclo de reloj se realiza el producto parcial  $P = A[34:17] \times B[17:0]$

#### OPMODE: 17-bits Shift P y Multiplicación con suma

Tema 3: Diseño de Subsistemas Aritméticos

161

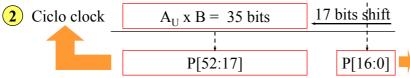

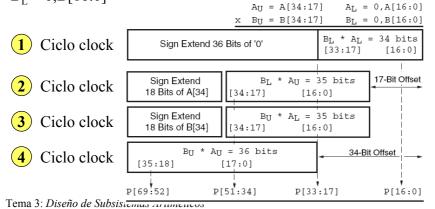

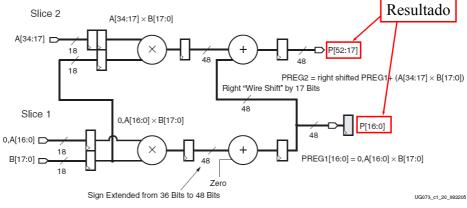

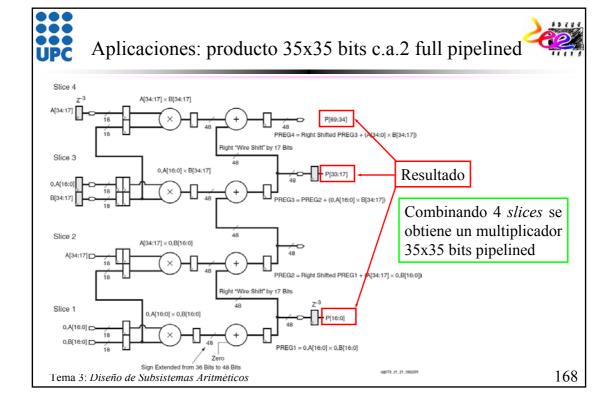

# Aplicaciones: producto 35x35 bits c.a.2 (I)

Ejemplo: 35x35 bits  $\Rightarrow$  A[34:0] x B[34:0]=P[69:0] en cuatro ciclos de reloj

- A se descompone en dos números: uno negativo  $A_U = A[34:17]$  y otro positivo  $A_U = 0, A[16:0]$

- B se descompone en dos números: uno negativo  $B_U = B[34:17]$  y otro positivo  $B_U = 0, B[16:0]$

# Aplicaciones: producto 35x35 bits c.a.2 (II)

Ciclo clock

Se realiza el producto parcial P = 0, $A[16:0] \times 0$ ,B[16:0]

#### OPMODE: Multiplicación

Tema 3: Diseño de Subsistemas Aritméticos

163

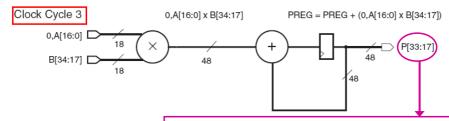

# Aplicaciones: producto 35x35 bits c.a.2 (III)

Ciclo clock

Se realiza el producto parcial  $P = A[34:17] \times 0,B[16:0]$

#### OPMODE: 17-bits Shift P y Multiplicación con suma

# Aplicaciones: producto 35x35 bits c.a.2 (IV)

Ciclo clock

Se realiza el producto parcial P = 0,  $A[16:0] \times B[34:17]$

#### OPMODE: Multiplicación con suma

Se toman los 17 LSB del resultado parcial que se corresponden con P[33:17]

Tema 3: Diseño de Subsistemas Aritméticos

165

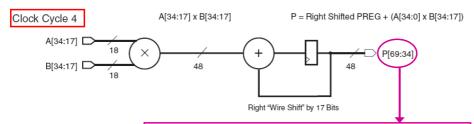

# Aplicaciones: producto 35x35 bits c.a.2 (V)

Ciclo clock

Se realiza el producto parcial  $P = A[34:17] \times B[34:17]$

#### OPMODE: 17-bits Shift P y Multiplicación con suma

Se toman los 36 LSB del resultado parcial que se corresponden con P[69:34]

Tema 3: Diseño de Subsistemas Aritméticos

#### Aplicaciones: producto 35x18 bits c.a.2 full pipelined

- Muchas aplicaciones DSP requieren alta velocidad de proceso

- Combinando varios DSP48 slice se puede realizar operaciones pipelined

- $\bullet$  Pipelined  $\Rightarrow$  con cada periodo de reloj se obtiene un nuevo resultado

Ejemplo: 35x18 bits = A[34:0] x B[17:0]

Tema 3: Diseño de Subsistemas Aritméticos

#### Otras funciones matemáticas básicas

Con un DSP48 *slice* se pueden realizar muchas funciones matemáticas básicas como:

- Sumar/restar

- Acumulación

- MAC: multiplicación mas suma

- Multiplexado

- Registro de desplazamiento

- Contador

- Multiplicador/divisor

- Raiz cuadrada

Tema 3: Diseño de Subsistemas Aritméticos

169

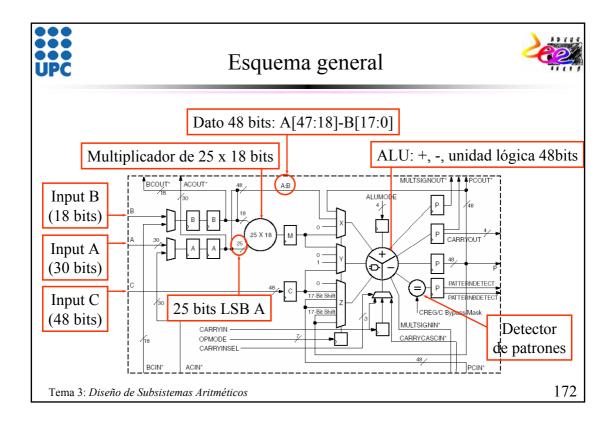

# 3.8.3 XtremeDSP de la familia Virtex-5: DSP48E

#### Características generales

- La familia *Virtex-5* dispone de 32 a 192 elementos DSP denominados DSP48E que pueden realizar múltiples funciones:

- ➤ Multiplicación

- ➤ Multiplicación y acumulación (MACC)

- > Sumador de tres entradas

- ➤ Comparador

- > Funciones lógicas

- ➤ Detección de patrones

- Colocando en cascada múltiples DSP48E se pueden generar funciones matemáticas complejas, filtros digitales, etc sin tener que utilizar recursos generales de la FPGA

Tema 3: Diseño de Subsistemas Aritméticos

# Bibliografía (I)

- Ernest Jamro, Kazimierz Wiatr, "Constant Coefficient Convolution Implemented in FPGAs", Proceedings of the Euromicro Symposium on Digital System Design (DSD'02)

- Keshab K. Parhi, "A Systematic Approach for Design of Digit-Serial Signal Processing Architectures", IEEE Transactions on Circuits and Systems, Vol. 38, no. 4, pp. 358-375, April 1991.

- Paolo Ienne and Marc A. Viredaz, "*Bit-Serial Multipliers and Squarers*", IEEE Transactions on Computers, Vol. 43, no. 12, pp. 1445-1450, Dec. 94.

- Richard Hartley and Peter Corbett, "*Digit-Serial Processing Techniques*", IEEE Transactions on Circuits and Systems, Vol. 37, no. 6, pp. 707-719, June 1990.

- Luigi Dadda, "*On Serial-Input Multipliers for Two's Complement Numbers*", IEEE Transactions on Computers, Vol. 38, no. 9, pp. 1341-1345, Sep. 89.

- Fuminori Kobayashi, Taro Tsujino, and Hirokazu Saitoh, "Efficient FPGA Implementation of Multiplier-Adder, Quotient-Remainder Approach", IEEE, pp. 227-230, 1998.

Tema 3: Diseño de Subsistemas Aritméticos

173

# Bibliografía (II)

- Javier Valls and Eduardo Boemo, "Efficient FPGA-Implementation of Two's Complement Digit-Serial/Parallel Multipliers", IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, Vol. 50, no. 6, pp. 317-322, June 2003.

- Jer Min Jou, Shiann Rong Kuang, and Ren Der Chen, "*Design of Low-Error Fixed-Width Multipliers for DSP Applications*", IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, Vol. 50, no. 6, pp. 836-842, June 1999.

- R. H. Turner, T. Courtney and R. Woods, "Implementation of Fixed DSP Functions Using the Reduced Coefficient Multiplier", IEEE, pp. 881-884, 2001.

- Ray Andraka, "A Survey of CORDIC Algorithms for FPGA Based Computers"

- J. C. Majithia, "A cellular array for the nonrestoring extraction of square roots", IEEE Transactions on Computers, Vol. C-20, pp. 1617-1618, Dec. 71.

- M. A. Ashour, H. I. Saleh, "An FPGA implementation guide for some different types of serial-parallel multiplier structures", Microelectronics Journal 31, pp. 161-168, 2000.

# Bibliografía (III)

- S. Sunder, F. El-Guibaly, A. Antoniou, "Two's-complement fast serial-parallel multiplier", IEE Proc.-Circuits Devices Syst., Vol. 142, no 1, pp. 41-44, Feb. 1995.

- K. Adaos, G. Alexiou, N. Kanopoulos, "Development of reusable serial FIR filters with reprogrammable coefficients designed for serial dataflow architectures", IEEE 2000.

- Leland B. Jackson, James F. Kaiser, Henry S. McDonald, "An Approach to the *Implementation of Digital Filters*", IEEE Trans. on Audio and Electroacoustics, Vol. AU-16, no 3, pp. 413-421, Sep. 1968.

- P. Larsson-Edefors, W. P. Marnane, "Most-significant-bit-first serial/parallel multipliers", IEE Proc.-Circuits Devices Syst., Vol. 145, no 4, pp. 278-284, Aug. 1998.

- Kiamal Z. Pekmestzi, "*Multiplexer-Based Array Multipliers*", IEEE Trans. On Computers, Vol. 48, no 1, pp. 15-23, Jan. 1999.

Tema 3: Diseño de Subsistemas Aritméticos

175

# Bibliografía (IV)

www.actel.com

- Application Note: Synchronous Dividers in Actel FPGAs

- Application Note: Implementing Multipliers with Actel FPGAs

- Application Note: Designing FIR Filters with Actel FPGAs

- Altera Corporation, "Using Soft Multipliers with Stratix and Stratix GX Devices", Stratix Device Handbook, Volume 2, Cap 9, 2003.

- AN053: Implementing Multipliers in Flex 10K Devices

- PIB21: Implementing Logic with the Embedder Array in Flex 10K Devices

- FS02: Floating-Point Adder-Subtractor

- FS04: Floating-Point Multiplier

# Bibliografía (V)

#### www.xilinx.com

- XAPP022: Adders, Subtracters and Accumulators in XC3000

- *DSPX5DEV*: Gregory R. Goslin, "Using Xilinx FPGA's to Design Custom Signal Processing Devices"

- XAPP054: Constant Coefficient Multipliers for the XC4000E

- XAPP018: Estimating the Performance of XC4000E Adders and Counters

- DS099: Spartan-3 FPGA Family: Complete Data Sheet

- XAPP467: Using Embedded Multipliers in Spartan-3 FPGAs

- GS093: XtremeDSP for Virtex-4 FPGAs User Guide

Tema 3: Diseño de Subsistemas Aritméticos

177

# Bibliografía (VI)

#### www.atmel.com

- *Application Note:* FPGA-based FIR Filter Using Bir-Serial Digital Signal Processing

- Application Note: Implementing Bit-Serial Digital Filters in AT6000 FPGAs

www.latticesemiconductor.com

• AN8014: Adder and Subtractor Macros Using Lattice Design Tools

# Bibliografía (VII)

• APPNOTE53: Wai-Leng Lim, "QuickDSP Complex Multiplier"

Tema 3: Diseño de Subsistemas Aritméticos