## RISC-V core optimization in 22nm FD-SOI technology

Max Doblas Font

Supervised by: Francesc Moll Echeto Miquel Moretó Planas

In partial fulfillment of the requirements for the master degree in: Master's degree in Advanced Telecommunication Technologies (MATT)

October 2021

UNIVERSITAT POLITÈCNICA DE CATALUNYA BARCELONATECH E scola Tècnica Superior d'Enginyeria de Telecomunicació de Barcelona

# Abstract

The thesis aims to design and implement an in-order core named Sargantana using the open RISC-V Instruction Set Architecture (ISA). Sargantana targets to improve the in-order 5-stage Lagaro-Hun core used in the early iterations of the DRAC project. Sargantana has a more mature 7-stage pipeline with out-of-order write back, register renaming, and a non-blocking memory pipeline.

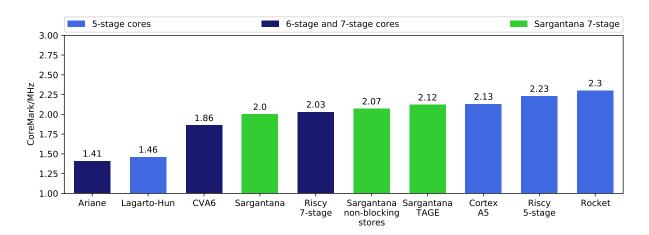

Also, this thesis applies microarchitectural design space exploration into Sargantana to balance the cycle performance and the clock frequency. 22nm FD-SOI commercial technology libraries are used to take physical effects into account in the register-transfer level (RTL) design. In this way, the processor's bottlenecks are analyzed to reach the maximum clock frequency using realistic technology. With this exploration, Sargantana achieves 2 CoreMark/MHz and 1 GHz in the worst corner (and up to 1,88 GHz in the faster) using 22nm FD-SOI commercial technology libraries. Sargantana obtains over its predecessor, the 5-stage Lagarto-Hun, an IPC speed-up of 1,37X.

**Keywords:** Microarchitecture, ASIC synthesis, In-order core, SRAM memories, Critical path, SystemVerilog, RISC-V.

# Resum

La tesi té com a objectiu dissenyar i implementar un processador en ordre anomenat Sargantanal, el qual implementa el set d'instruccions (ISA) lliure RISC-V. Sargantana té com a objectiu millorar el processador Lagarto-Hun de cinc etapes, utilitzat en les primeres iteracions del projecte DRAC. Sargantana té una pipeline de set etapes més madura amb escriptura fora d'odre i una pipeline de memòria que no bloquejant.

A més, aquesta tesi aplica una exploració espacial de disseny microarquitectònic a Sargantana per equilibrar el IPC i la freqüència del rellotge. S'han utilitzat les llibreries tecnològiques comercials FD-SOI de 22 nm per tenir en compte els efectes físics en el disseny digital. D'aquesta manera, s'analitzen els punts limitants del processador per tal d'assolir una freqüència de rellotge màxima mitjançant una tecnologia realista. Amb aquesta exploració, Sargantana aconsegueix 2 CoreMark/MHz i 1 GHz en les pitjors condicions (i fins a 1,88 GHz en les millors) mitjançant les llibreries tecnològiques comercials FD-SOI de 22 nm. Sargantana obté sobre el seu predecessor, el Lagarto-Hun de cinc etapes, una millora en IPC de 1,37X.

**Paraules clau:** Microarquitectura, síntesi ASIC, processador en ordre, Memòries SRAM, Camí crític, SystemVerilog, RISC-V.

# Acknowledgements

I would like to express my gratitude to Miquel Moretó for allowing me to join his research at BSC for nearly three years now. He has taken an active interest in my growth both on academic and personal levels.

Moreover, I would like to thank Francesc Moll. He has supervised my work directly from UPC. I have learned a lot of physical design concepts from him. Moreover, he is a lovely person to work with that also makes you always feel welcome.

I also want to thank the help of Víctor Soria, Guillem López, Narcís Roda, Xavier Carril, Neiel Leyva and Gerard Candón. They always have been there to work with me, facing the difficulties of this project. They also have done a spectacular job in the Sargantana core. Thanks to Victor for all the architectural ideas that he has brought to this stunning Sargantana design. I want to thank Gerard for sharing his excellent knowledge of vector processing on RISC-V, and his excellent debug skills. I want to thank Guillem for his expertise on the RTL environment tools and his always appreciating SystemVerilog structs. I want to thank Narcís for his versatility on the project. He was able to manage smoothly all the different things that he had faced. Thanks, Neiel, for its instruction cache design. Also, I would like to thank all the people involved in the Lagarto designs in Barcelona and Mexico. I want to thank Xavier for reviewing the documentation in order to improve the quality of the document. Finally, I want to thank all the other members from the synthesis and physical design group and the verification group that worked on the project for helping with the physical design and verification environments.

Moreover, I want to thank the help of Nehir Sonmez and Roger Figueres. They always have been there to help me to face the difficulties of this project. Nehir has followed all my progression, and he has given me advice and confidence to keep going. Roger has helped me with the technical part, which I have learnt a lot.

Finally, I would like to thank Professor Arvind and his research group for the knowledge obtained during the MIT fellowship. This knowledge has been advantageous during the Sargantana implementation in order to achieve higher performance in the end.

It has been a pleasure to work with all of them. With this group of people, everything was easier. I hope to work with them in the future.

# Contents

| A             | bstra | nct            |                                                                            | i   |

|---------------|-------|----------------|----------------------------------------------------------------------------|-----|

| $\mathbf{Li}$ | st of | Figur          | es                                                                         | vii |

| $\mathbf{Li}$ | st of | Table          | 3                                                                          | ix  |

| A             | crony | $\mathbf{yms}$ |                                                                            | x   |

| 1             | Intr  | oducti         | on and Motivation                                                          | 1   |

|               | 1.1   | Docur          | nent Structure                                                             | 2   |

| <b>2</b>      | Bac   | kgrou          | nd                                                                         | 4   |

|               | 2.1   | Microa         | architecture Background                                                    | 4   |

|               |       | 2.1.1          | Pipeline Hazards                                                           | 5   |

|               |       | 2.1.2          | IPC Optimizations                                                          | 7   |

|               |       |                | 2.1.2.1 Basic Optimizations: Bypassing, Branch Prediction, and Caches      | 8   |

|               |       |                | 2.1.2.2 Superscalar Pipeline                                               | 10  |

|               |       |                | 2.1.2.3 Out-Of-Order Issue and Execution                                   | 11  |

|               |       |                | 2.1.2.4 $$ Single Instruction Multiple Data (SIMD) and Vector Processor .  | 12  |

|               | 2.2   | Physic         | al Implementation                                                          | 13  |

|               |       | 2.2.1          | Standard Cell Libraries                                                    | 13  |

|               |       | 2.2.2          | Hard IP Blocks                                                             | 14  |

|               |       | 2.2.3          | Performance of a Digital Circuit. Process, Voltage, Temperature Variations | 15  |

|               | 2.3   | RTL S          | imulation, FPGA Emulation, and Gate Level Simulation                       | 16  |

|               | 2.4   | Proces         | sor Benchmarking                                                           | 17  |

|               |       | 2.4.1          | CoreMark                                                                   | 18  |

|               |       | 2.4.2          | EEMBC AutoBench Performance Benchmark Suite                                | 18  |

|               |       |                |                                                                            |     |

### 3 Related Work

|   | 3.1 | RISC-                   | V ISA      |                                                                 | 20 |  |  |  |

|---|-----|-------------------------|------------|-----------------------------------------------------------------|----|--|--|--|

|   | 3.2 | In-Ore                  | ler Desigi | 18                                                              | 20 |  |  |  |

|   |     | 3.2.1                   | Ariane (   | Core                                                            | 21 |  |  |  |

|   |     | 3.2.2                   | Rocket6    | 4 Core                                                          | 23 |  |  |  |

|   |     | 3.2.3                   | Riscy In   | -Order Core                                                     | 24 |  |  |  |

|   | 3.3 | Out-o                   | f-Order D  | esigns                                                          | 26 |  |  |  |

|   |     | 3.3.1                   | RiscyOO    | )                                                               | 26 |  |  |  |

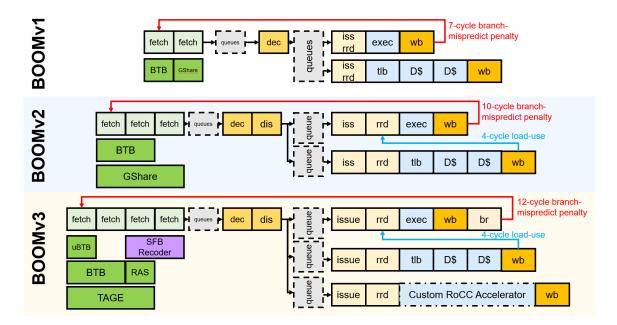

|   |     | 3.3.2                   | Berkeley   | v Out-of-Order Machine (BOOM)                                   | 27 |  |  |  |

| 4 | Exp | oerime                  | ntal Env   | ironment                                                        | 29 |  |  |  |

|   | 4.1 | RTL I                   | Environm   | ent                                                             | 29 |  |  |  |

|   | 4.2 | ASIC                    | Tool-Flow  | v Environment                                                   | 29 |  |  |  |

|   |     | 4.2.1                   | Standar    | d Cell Libraries                                                | 29 |  |  |  |

|   |     | 4.2.2                   | Hard IP    | Blocks                                                          | 30 |  |  |  |

| 5 | Mic | croarch                 | itectura   | l Design of Sargantana                                          | 31 |  |  |  |

|   | 5.1 | 5-stag                  | e Lagarto  | -Hun Analysis                                                   | 31 |  |  |  |

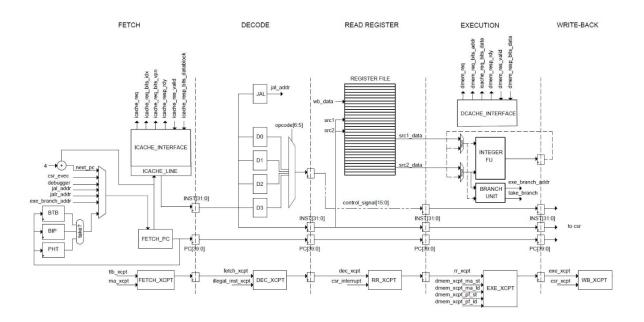

|   |     | 5.1.1                   | Pipeline   | Description                                                     | 32 |  |  |  |

|   |     | 5.1.2                   | IPC Ana    | alysis                                                          | 34 |  |  |  |

|   |     | 5.1.3                   | Critical   | Path Analysis                                                   | 35 |  |  |  |

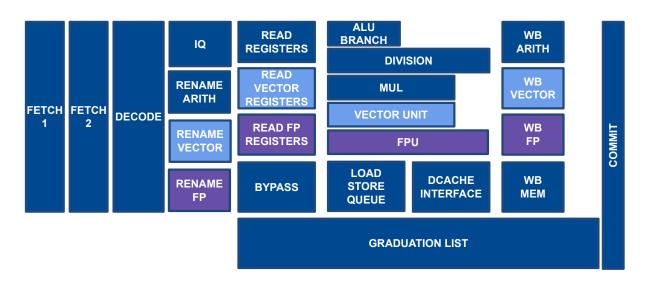

|   | 5.2 | 5.2 Sargantana Pipeline |            |                                                                 |    |  |  |  |

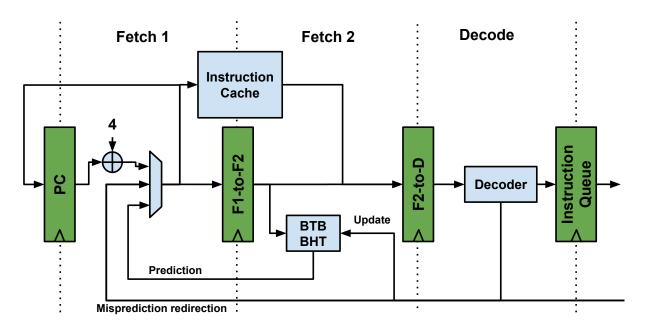

|   |     | 5.2.1                   | Frond-E    | nd Implementation                                               | 36 |  |  |  |

|   |     | 5.2.2                   | Back-Er    | d Implementation                                                | 37 |  |  |  |

|   |     |                         | 5.2.2.1    | Renaming and Register Files                                     | 37 |  |  |  |

|   |     |                         | 5.2.2.2    | Issue, Write-Back and Forwarding Mechanisms                     | 40 |  |  |  |

|   |     |                         | 5.2.2.3    | Graduation List and Commit Stage                                | 41 |  |  |  |

|   |     |                         | 5.2.2.4    | ALU, FPU, Multiplication Unit and Division Unit                 | 41 |  |  |  |

|   |     |                         | 5.2.2.5    | Memory Pipeline                                                 | 42 |  |  |  |

|   |     |                         | 5.2.2.6    | SIMD Pipeline                                                   | 44 |  |  |  |

|   |     | 5.2.3                   | Verificat  | ion and Performance Evaluation Infrastructure                   | 45 |  |  |  |

|   |     |                         | 5.2.3.1    | RTL Simulation Environment: Waveforms, Commit Traces and Konata | 45 |  |  |  |

|   |     |                         | 5.2.3.2    | FPGA Environment and Linux Boot                                 | 46 |  |  |  |

|   |     |                         | 5.2.3.3    | Physical Design and Gate-Level Simulations                      | 47 |  |  |  |

| 6  | Eva             | luatior | 1                                                 | 48 |  |  |  |

|----|-----------------|---------|---------------------------------------------------|----|--|--|--|

|    | 6.1             | Synthe  | esis Experiments of Sargantana                    | 48 |  |  |  |

|    | 6.2             | IPC E   | valuation Using the EEMBC AutoBench               | 49 |  |  |  |

|    |                 | 6.2.1   | IPC Evaluation Against the 5-stage Lagarto-Hun    | 50 |  |  |  |

|    |                 | 6.2.2   | IPC Evaluation Against Other Designs              | 50 |  |  |  |

|    |                 | 6.2.3   | Deeper IPC Analysis of Sargantana's IPC Penalties | 51 |  |  |  |

|    | 6.3             | IPC E   | valuation Using the EEMBC AutoBench               | 53 |  |  |  |

| 7  | Con             | clusio  | ns                                                | 54 |  |  |  |

|    | 7.1             | Future  | e Work                                            | 54 |  |  |  |

| Bi | Bibliography 56 |         |                                                   |    |  |  |  |

# List of Figures

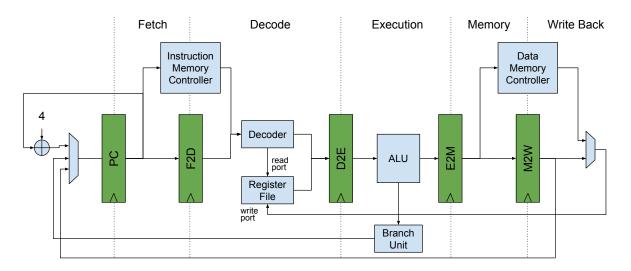

| 2.1 | Pipelining a simple in-order core design                                                                                                                               | 5  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Different types of data hazards                                                                                                                                        | 7  |

| 2.3 | Pipeline execution with a control hazard. A branch instruction redirects the PC, and the pipeline has to be flushed                                                    | 7  |

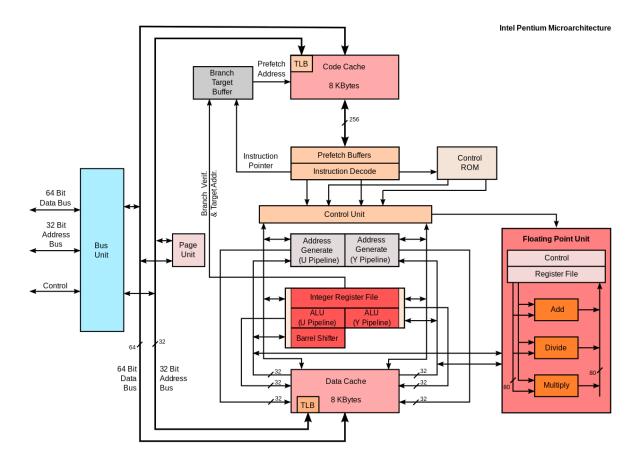

| 2.4 | Intel Pentium P5 pipeline diagram. Source: [1]                                                                                                                         | 11 |

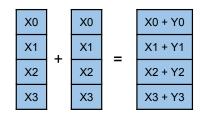

| 2.5 | SIMD addition of a vector of 4 elements                                                                                                                                | 13 |

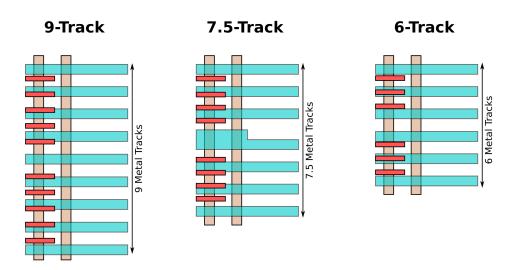

| 2.6 | Comparation between different standard cells with different tracks $[2]$                                                                                               | 14 |

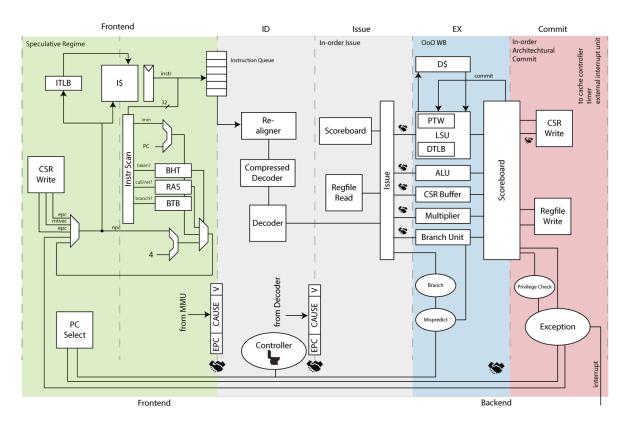

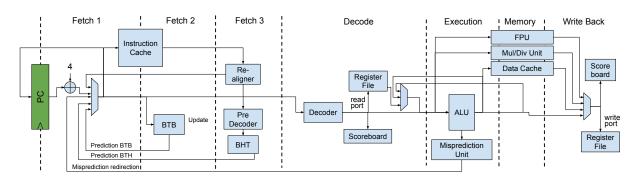

| 3.1 | Blockdiagram of Ariane. Source: [3]                                                                                                                                    | 22 |

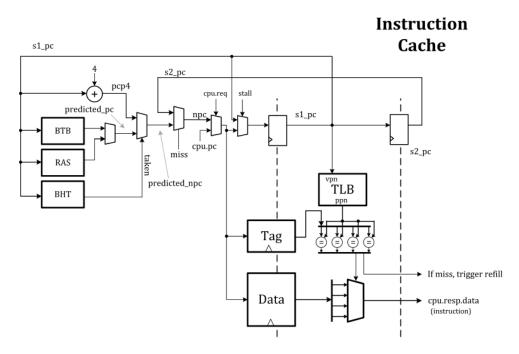

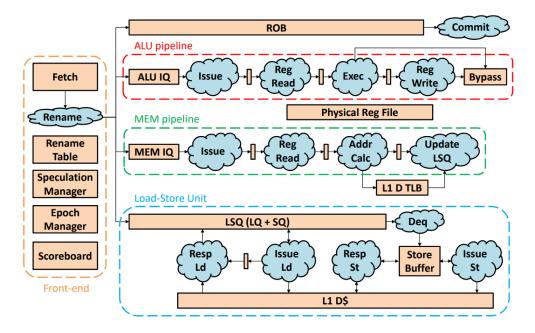

| 3.2 | Blockdiagram of Rocked core frontkend. Source: [4]                                                                                                                     | 24 |

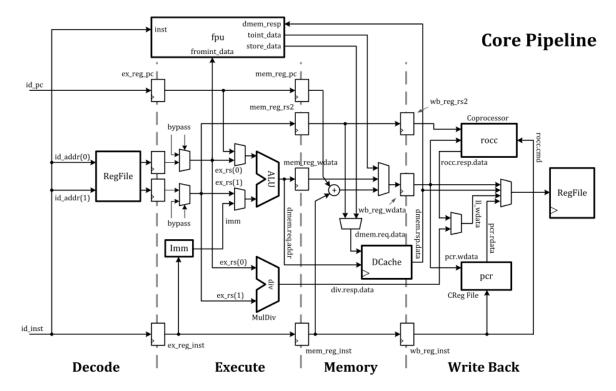

| 3.3 | Blockdiagram of Rocked core backend. Source: [4]                                                                                                                       | 25 |

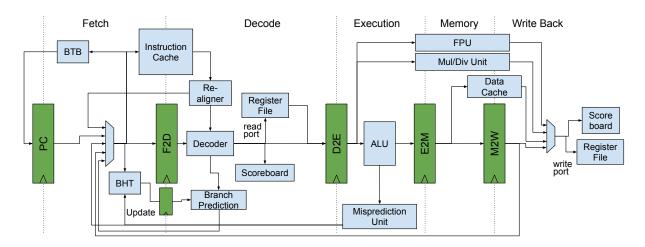

| 3.4 | Diagram of the original Riscy 5-stage pipeline                                                                                                                         | 25 |

| 3.5 | Diagram of the original Riscy 7-stage pipeline                                                                                                                         | 26 |

| 3.6 | RiscyOO structure diagram                                                                                                                                              | 27 |

| 3.7 | Evolution of the BOOM pipeline                                                                                                                                         | 28 |

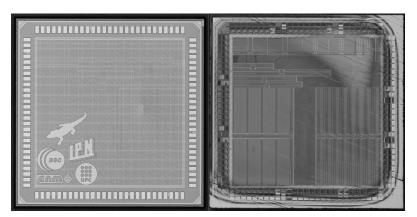

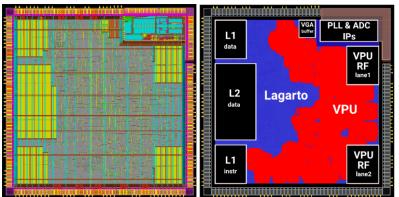

| 5.1 | Layout of the different 5-stage Lagarto-Hun tape-outs                                                                                                                  | 32 |

| 5.2 | 5-stage Lagarto-Hun pipeline                                                                                                                                           | 33 |

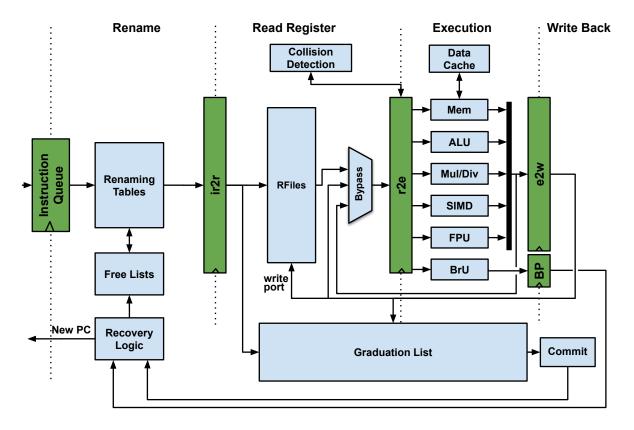

| 5.3 | Simplified block diagram of Sargantana pipeline                                                                                                                        | 35 |

| 5.4 | Block diagram of Sargantana front-end.                                                                                                                                 | 36 |

| 5.5 | Block diagram of Sargantana back-end.                                                                                                                                  | 38 |

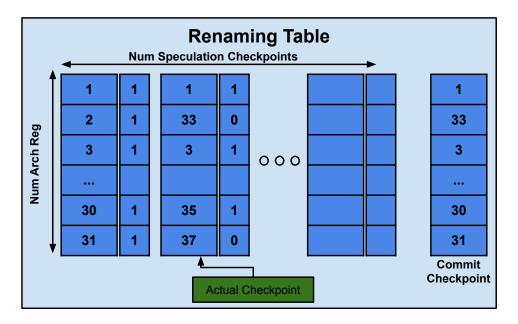

| 5.6 | Block diagram of the renaming table                                                                                                                                    | 39 |

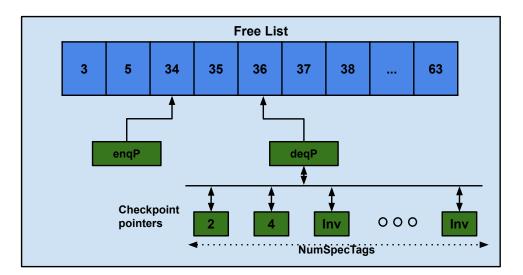

| 5.7 | Block diagram of the free list                                                                                                                                         | 40 |

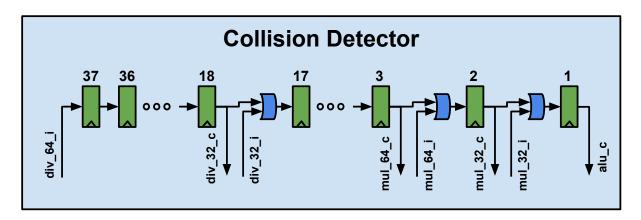

| 5.8 | Write-back collision detection in the ALU and Mul/Div pipeline. The suffix $_i$ indicates a new issue of the particular type of instruction. The suffix $_c$ indicates |    |

|     | a collision of the particular type of instruction.                                                                                                                     | 41 |

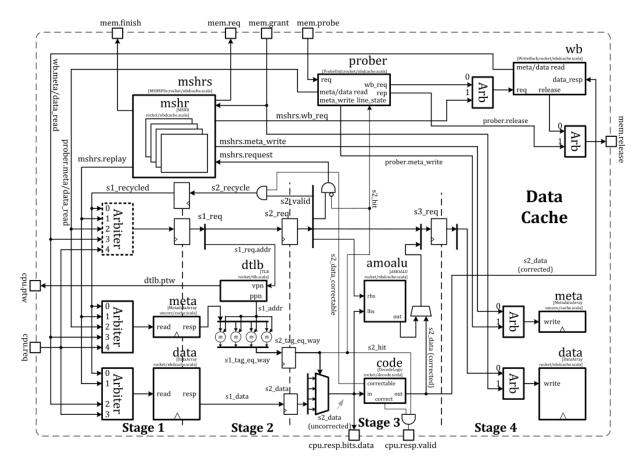

| 5.9 | Block diagram of the first level data cache. Source: [4]                                                                                                               | 43 |

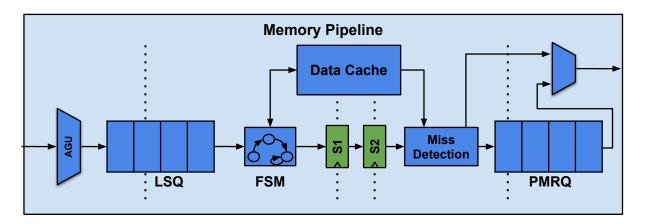

| 5.10 | Block diagram of the memory pipeline                                                                                                                                                       | 44 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.11 | Konata visualization of a Sargantana execution                                                                                                                                             | 46 |

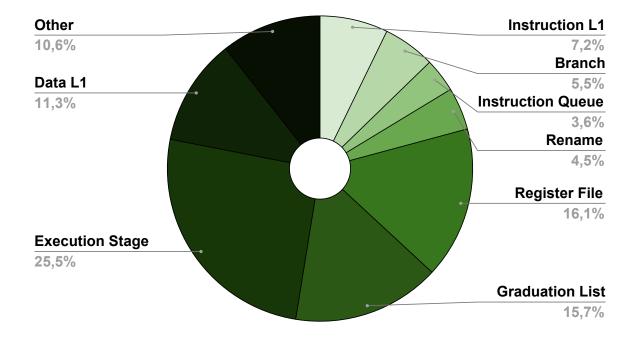

| 6.1  | Area distribution inside the Sargantana core (first-level caches included) $\ . \ . \ .$                                                                                                   | 49 |

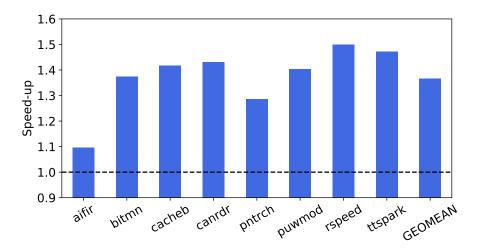

| 6.2  | Speed-up of the integer benchmarks of the AutoBench suite of Sargantana against the 5-stage Lagarto-Hun. The geometric mean of all the benchmarks is shown on the right bar.               | 50 |

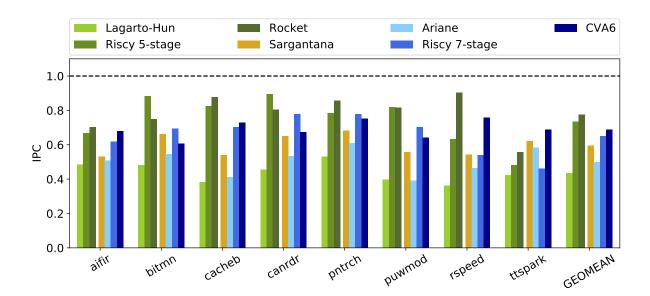

| 6.3  | IPC of the integer benchmarks of the AutoBench suite for different cores grouped<br>by the number of stages. The geometric mean of all the benchmarks is shown on<br>the right bar         | 51 |

| 6.4  | IPC of the floating point benchmarks of the AutoBench suite for different cores<br>grouped by the number of stages. The geometric mean of all the benchmarks is<br>shown on the right bar. | 51 |

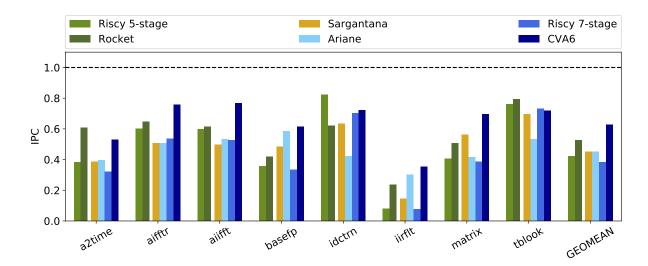

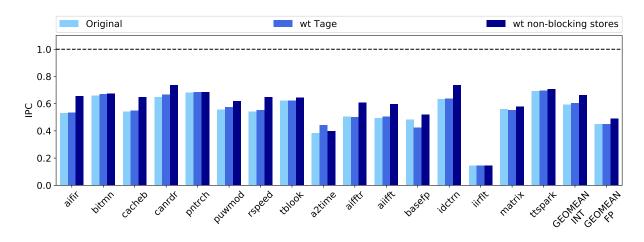

| 6.5  | Speed up and IPC of the AutoBench suite for the different possible modifications on Sargantana.                                                                                            | 52 |

| 6.6  | CoreMark/MHz score of the different cores. The cores are separated by number of stages.                                                                                                    | 53 |

# List of Tables

| 2.1 | Different types of simulation and emulation approaches together with their properties                                                                                       | 17 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | RISC-V: base Integer ISAs and extensions                                                                                                                                    | 21 |

|     | List of Standard Cell libraries used in the design for Globalfoundries 22FDX List of SRAM cells used in the design for Globalfoundries 22FDX                                |    |

| 6.1 | Maximum frequency for the 5-stage Lagarto-hun, Riscy cores and Sargantana in the slow corner (0.72V@125°C), the typical corner (0.8V@25°C) and the fast corner (0.88@-40°C) | 49 |

# Acronyms

- ALU Arithmetic Logic Unit

- ASIC Application-Specific Integrated Circuit

- **BHT** Branch History Table

- **BSV** Bluespec SystemVerilog

- **BTB** Branch Target Buffer

- **CMD** Composable Modular Design

- **CPU** Central Processing Units

- **CPP** Contacted Poly Pitch

- ${\bf CRC}~$  Cyclic Redundancy Check

- ${\bf CSR}$   $\;$  Control and Status Register  $\;$

- **DRAM** Dynamic Random Access Memory

- **EDL** Event Driven Language

- EHR Ephemeral History Register

- FD-SOI Fully Depleted Silicon On Insulator

- FPGA Field-Programmable Gate Array

- FPU Floating Point Unit

- **IP** Intellectual Property core

- **IPC** Instructions Per Cycle

- **ISA** Instruction Set Architecture

- I/O Input/Output

- LUT LookUp Table

- MCU Mcicrocontrollers

- **MSHR** Miss Status Holding Registers

- MIT Massachusetts Institute of Technology

- **MMU** Memory Management unit

- **MOSFET** Metal Oxide Semiconductor Field Effect Transistor

- **NoC** Network on Chip

- **PC** Program Counter

- **PnR** Place And Route

- **PIPT** Physically Indexed, Physically Tagged

- **PIVT** Physically Indexed, Virtually Tagged

- $\mathbf{PVT}$  Process, Voltage, Temperature

- **RAS** Return Address Stack

- ${\bf RAW}\,$  Read After Write

- **ROB** Re-Order Buffer

- **ROCC** Rocket Custom Co-processor Interface

- **RTL** Register-Transfer Level

- **SIMD** Single Instruction, Multiple Data

- SoC System on Chip

- SRAM Static Random Access Memory

- ${\bf TLB} \quad {\rm Translation \ Lookaside \ Buffer}$

- **VIPT** Virtually Indexed, Physically Tagged

- **VIVT** Virtually Indexed, Virtually Tagged

- $\mathbf{WAR}\ \mathrm{Write}\ \mathrm{After}\ \mathrm{Read}$

- ${\bf W\!A\!W}$  Write After Write

# **1** Introduction and Motivation

Every day, nanotechnology is advancing in a faster way. These technology advances allow the manufacturers to design circuits using smaller, faster, and cheaper transistors [5]. The field of computer architecture has taken advantage of the transistors improvements to evolve the processor designs continuously. Every day, computer architects can design more complex circuits making processors faster, cheaper, and more efficient for targeted applications. This, in turn, opens the door to other fields of study outside the computer architectural world, like autonomous driving, machine learning, or Internet-of-Things (IoT), to exploit this computational power to real-world use.

Apart from the technological improvements, open Instruction Set Architectures (ISA) have been proposed very recently. They bring the promise of a similar revolution in the hardware design that open-source software has represented in computing. Even achieving the spectacular revolution that Linux had represented on the operating system side. Since the release of the open RISC-V ISA, many implementations of processors have risen both from industry and academia. Many projects have been created to push the RISC-V ISA to the industrial level, designing and implementing capable cores and a reliable software stack to show its potential. One of this projects is DRAC (Designing RISC-V-based Accelerators for next-generation Computers). The project's objective is to design and successfully tape-out in 22nm FD-SOI technology an out-of-order processor along with accelerators for applications as genomics or computer vision.

This thesis aims to design and implement an in-order core named Sargantana using the open RISC-V ISA. Sargantana aims to improve the in-order processor 5-stage Lagarto-Hun used in the early stages of the DRAC project. Lagarto-Hun is a 5-stage core developed in a collaboration between the Instituto Politécnico Nacional de Mexico and the Barcelona Supercomputing Center (BSC). Two versions of the 5-stage Lagarto-Hun have been taped-out using a 65 nm process node from TSMC.

Although the Lagarto-Hun core was successfully taped-out with a frequency of 600 MHz, the Instructions Per Cycle (IPC) performance of the design could be improved. The first objective of Sargantana is to improve the IPC performance to be competitive with the other state-of-the-art academic cores. Some complex optimizations like out-of-order write-back are implemented in Sargantana to achieve that needed performance.

In this project, a second objective is set. In order to achieve good performance with an Application-Specific Integrated Circuit (ASIC) target, not only the IPC is important. The clock frequency plays a significant role in the performance of a processor. Sargantana has as an objective to achieve a high clock frequency of 1 GHz with a modern 22nm technology. This

frequency of 1 GHz is high enough to force us to make some architectural changes, but it is not as demanding as requiring some fine-tune modifications.

The entire design and verification process is described in the thesis. It describes the new Sargantana pipeline with all the IPC optimizations implemented and its impact on the maximum frequency. The thesis also contains all the environments implemented to validate the performance of the design. It describes the Register-Transfer Level (RTL) simulation/emulation environment for validating the IPC and the physical design flow to validate the maximum frequency that the design can achieve. Also, it includes all the verification followed to prove the correct behavior of the design.

A team of about 10 people has been involved in the implementation of the Sargantana core design, the SoC, and all the verification and validation environment. In particular, I was involved in nearly all the Sargantana core development parts, and I took part in the Sargantana design decisions. I have designed and implemented the new front-end of the core and the modification in the data cache to execute memory operations of 128-bit. I have implemented all the modules and modifications related to the privilege ISA, such as the Control and Status Register (CSR) that enable the boot of Linux distribution, which I have modified for the project. I have developed part of the validation environment, such as the Konata trace visualizer. I worked with other people on several modules of the core back-end as the memory pipeline, the integration of the Floating Point Unit (FPU) and Single Instruction, Multiple Data (SIMD) unit. Also, I have made all the evaluations and performance discussions in this thesis, having to adapt all the benchmarks used for all the cores evaluated.

Finally, and no less important, I am responsible for achieving the clock frequency and area targets of the design. I have done the initial synthesis flow to get feedback on the ASIC synthesis to continuously improve the design, achieving the right balance of frequency and IPC to get the maximum performance. All this work is described in this thesis.

### 1.1 Document Structure

The rest of this thesis is structured as follows:

- Chapter 2 provides a basic background on computer architecture and physical design implementation concepts to make the document self-contained.

- Chapter 3 introduces the RISC-V open-source ISA and presents the most relevant academic processor designs. It explains the specific design and shows IPC and clock frequency achieved by each core.

- Chapter 4 introduces all the tools and benchmarks used in RTL design and also the technology libraries used for ASIC synthesis.

- Chapter 5 does an in-depth analysis of the 5-stage Lagarto-Hun and introduces all the improvements that have been carried out on the Sargantana processor to achieve the expected frequency of 1 GHz with a good IPC.

- Chapter 6 evaluates the final design and compares it with the other academic designs.

• Finally, Chapter 7 discusses the results and concludes this work.

# 2 Background

First of all, it is important to introduce some concepts on computer architecture that will be used during this project. Not only purely architectural design concepts need to be presented, but the introduction of the physical design process and technology used for digital designs are necessary.

First, the basics about computer architecture design like pipeline hazards and how to mitigate them with basic optimizations are introduced. Some basic optimizations as forwarding or branch prediction are described. After that, there is the introduction of some advanced IPC optimization, some of which will be used in this project.

Finally, it is crucial to explain how a processor design is physically implemented, introducing the concept of standard cell libraries and hard Intellectual Property core (IP). At this point, the concept of the critical path is also needed. It is important to emphasize why it is so essential in the computer architecture field.

### 2.1 Microarchitecture Background

As it is known, a processor performs basic arithmetic operations, logic operations, memory operations or Input/Output (I/O) operations described by the instructions in a program. These instructions must modify the state of the processor as the register file, memory system, or special registers in the order specified by the program. The Instruction Set Architecture (ISA) specifies the processor behavior for each particular instruction.

The processor used to be divided into three main parts: the core (or cores in a multiprocessor), the memory hierarchy, and the I/O. In particular, this thesis focus only on the core part and some details of the memory hierarchy.

As it is explained in the physical design section, a processor design will be physically implemented using standard cells, which are implemented by transistors. Those transistors are not ideal and have some associated propagation delay of the signal. Then, a critical path can be defined as the logical path (all the gates between two registers) with more propagation delay on the design. Let us assume a processor that does all the defined steps (fetch, decode, and execution) in one clock cycle. The logic path in a processor like this will be enormous, limiting the maximum frequency of the design. To solve that situation and to be able to achieve higher clock frequencies, the concept of *pipeling* is used.

The instruction's execution can be divided into different parts, also known as stages, in which

Figure 2.1: Pipelining a simple in-order core design

each stage is executed in a clock cycle and executed concurrently. Figure 2.1 shows an example of a processor with five distinctive stages. The processor is composed of these stages:

- Fetch (F): This module asks for the next instruction to memory and updates the Program Counter (PC).

- Decode and Read Register (D): This module receives the instruction from memory, decodes it, and reads the register needed for each instruction.

- Execution (E): It executes the instruction decoded using the values read from the register file.

- Memory (M): A memory request is performed if the instruction is a load or a store.

- Write Back (W): If the instruction is a load, it receives the data from memory. It writes the result of the instruction to the register file if it is needed.

Thus, the clock frequency of this particular design can be up to five times faster than a onestage core. However, applying the pipeline concept also has some drawbacks that are important to take into account. These drawbacks are known as pipeline hazards that are explained in depth in Subsection 2.1.1. Basically, the pipeline hazards make the core unable to finish or commit one instruction per cycle (assuming that the one cycle version of the core commits at most one instruction per cycle), reducing the final throughput of the core.

#### 2.1.1 Pipeline Hazards

An ideal processor that executes a complete instruction in one cycle has an IPC of one. However, this ideal IPC is impossible to achieve in a pipelined processor. Different factors introduce hazards that can force the next instruction to not execute in the following clock cycle. These hazards will result in not finishing an instruction every cycle. There are three primary hazards in a pipeline: structural hazard, data hazard, and control hazards.

**Structural hazard** The structural hazard is produced when two (or more) operations processed in the pipeline need the same resource. A simple example of a structural hazard can be found in a small core with a unified memory used to store instructions and data. The processors with a unified memory (the instructions and the data are located on the same physical memory) can experiment structural hazards when a memory instruction is on the execution stage (in the memory stage or pipeline for those processors that implement it). When a memory instruction is on the execution stage, the core makes a petition to the unified memory blocking it during that cycle. Since the core is pipelined, the fetch stage will also try to access the unified memory. However, the unified memory is locked by the older memory instruction. At this point, the fetch stage will not be able to fetch a new instruction. Thus, the core will have one empty cycle without committing an instruction. An easy solution to this hazard is duplicating the resources to allow both instructions to access the memory hierarchy. Two different memories, one for instructions and another for data, can be used in this case.

To sum up, the structural hazards are produced by a lack of physical hardware and can be solved by adding more hardware. However, adding more hardware increments the area and power consumption. Thus, it is a trade-off between area, power cost, and performance.

**Data hazard** Data hazards can be encountered when two or more instructions exhibit dependencies on a particular data during the execution of different stages of the pipeline. The potential data hazards have to be solved to avoid possible race conditions that can modify the expected execution result. Thus, if there is a data race condition, the result of the program will not follow the definition that the programmer expects. Three situations can produce a data hazard depending on each instruction's action (reading or writing) implicated in the data hazard. However, not all situations can be found on any processor because some combinations of instructions will not happen to a particular architecture. The three different data hazards are:

- Read After Write (RAW), a true dependency: It happens when one instruction needs a result that will be written by an older instruction. In the example in Figure 2.2a, instruction  $i_2$  needs to read from register  $r^2$  that is written by instruction  $i_1$ . Maybe  $i_1$  is not completed when  $i_2$  reads the register. Thus,  $r^2$  has not computed the result yet and it still has the old value. The solution is to stall the pipeline and wait for  $i_1$  to finish before  $i_2$  reads register  $r^2$ .

- Write After Read (WAR), an anti-dependency: refers to a situation where a younger instruction writes to a register that has to be read by an older instruction. It can only happen when the instructions are executed concurrently or out-of-order, and the younger instruction has been reordered before an older instruction for any reason. An example is shown in Figure 2.2b. The instruction  $i_3$  needs to be read from the register r1 before the instruction  $i_4$  overwrites the data in that register.

- Write After Write (WAW), an output dependency: It happens when two instructions have to write in the same register. The younger instruction's write-back needs to wait until the older one does it. As well as the WAR hazard, the WAW hazard can only

| $i_1: r2 \leftarrow r1 + r3$ | $i_3: r2 \leftarrow r1 + r3$ | $i_5: r2 \leftarrow r4 + r1$ |

|------------------------------|------------------------------|------------------------------|

| $i_2: r4 \leftarrow r5 + r2$ | $i_4: r1 \leftarrow r5 + r4$ | $i_6: r2 \leftarrow r3 + r5$ |

| (a) RAW                      | (b) WAR                      | (c) WAW                      |

Figure 2.2: Different types of data hazards

|                               | Execution Cycles |   |     |   |   |   |   |   |   |    |    |    |

|-------------------------------|------------------|---|-----|---|---|---|---|---|---|----|----|----|

| Program Instructions          | 1                | 2 | 3   | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 11: bne r1, r2, 18 (it jumps) | F                | D | , E | М | W |   |   |   |   |    |    |    |

| 12: li r3, 7                  |                  | F | x   |   |   |   |   |   |   |    |    |    |

| 13: addi r4, r4, 4            |                  |   | x   |   |   |   |   |   |   |    |    |    |

| l8: li r1, 0                  |                  |   | F   | D | Е | М | w |   |   |    |    |    |

|                               |                  |   |     |   |   |   |   |   |   |    |    |    |

Figure 2.3: Pipeline execution with a control hazard. A branch instruction redirects the PC, and the pipeline has to be flushed

be found in concurrent environments. However, in this case, not only an out-of-order issue architecture has this problem. With an architecture able to write back out-of-order is enough to encounter WAW dependencies. An example is shown in Figure 2.2c. The instructions  $i_5$  and  $i_6$  need to write to the same register.

**Control Hazard** A control hazard occurs when there is a control instruction or an exception in the pipeline that modifies the sequential order of the program. In a pipeline, several instructions are being executed in different stages. Thus, when a control instruction or an exception is detected and computed, the corresponding stage knows the new order of the program. Then, the younger instructions inside the pipeline that do not follow the new order on the program have to be discarded. In Figure 2.3, we show an example of a control hazard. In the example, a 5-stage pipeline design knows the result of a branch instruction in the execution stage. There is a branch instruction inside the execution stage. This branch instruction is executed as taken; thus, the next instruction will not be sequential. The instructions inside the fetch and decode stages have to be flushed because they are not in the program path anymore. As shown, the control hazards have a big impact on IPC since every time the program's sequential order is broken, at least two instructions will be flushed. In a core with more stages between fetch and the stage in which the control instruction is detected, the penalty will even be bigger.

#### 2.1.2 IPC Optimizations

As we can see in Section 2.1.1, several factors introduce hazards. The only solution for these hazards is stalling the pipeline. A lot of lost cycles can be introduced in the pipeline, which can

degenerate the IPC and the performance of a core.

It is necessary to apply some optimizations to the pipeline in order to reduce or eliminate the hazard effects and achieve a proper IPC. In this section, several optimizations, some more simple and some more advanced, are exposed that can be implemented in a core pipeline to boost the IPC of a core. Apart from analyzing the impact on the IPC for each optimization, it is important to look at the impact on the maximum frequency that each optimization introduces.

#### 2.1.2.1 Basic Optimizations: Bypassing, Branch Prediction, and Caches

The basic optimizations are introduced before jumping to more advanced ones. The basic optimizations are:

**Bypassing** (also known as forwarding). It is the action of routing a value from a source (the stage that generates the data) to a user (a stage that uses the data), bypassing a designated destination register.

Primarily for static pipelines, this allows the value produced to be used earlier in the pipeline without waiting for the write-back to the register file. Bypasses can nearly eliminate all the data hazards inside a pipeline. Each pipeline will implement the bypasses differently depending on the architectural design.

However, not all the effects of the bypasses are beneficial for the design. Bypasses introduce mainly two types of penalties. Firstly, bypasses augment the resources consumed (i.e., area in an ASIC target or number of LookUp Table (LUT) in an Field-Programmable Gate Array (FPGA) implementation). Forwarding needs extra wires to propagate the values and multiplexers to select from where the operands are coming from. Take into account that on a 64bit pipeline, the buses and multiplexers need to be of 64bit width. Also, it adds extra logic on the control side. It is worth mentioning that the increase in resources is not high on a simple single-issue processor, and it is not problematic. However, in a superscalar processor, the number of possible bypasses tends to grow in a quadratic way since there will be one bypass for each pair of issue ports and functional unit.

Secondly, and usually more critical, bypassing can add new, very long paths to the design. These paths can, in the worst-case, notably increase the critical path. To avoid that effect, the bypasses need to be appropriately selected. It is recommended to place all bypasses always at the start of stages or all at the end. Doing that, we ensure that the delay of an entire pipeline is not propagated to the start point of another pipeline doubling the critical path of the design.

**Branch Prediction and Early PC Redirection** As it is mentioned in the pipeline hazards subsection, control hazards have a notorious impact on pipeline performance, even more on the more complex pipelines with a considerable number of stages. This fact is more worrying, taking into account that control instruction in a program can be more than 20% of a normal workload [6]. There are two main optimizations to reduce the impact of the control hazards: the branch prediction and the early PC redirection.

Early PC redirection is based on redirecting the PC as soon as the instruction that breaks

the sequential execution of the program is detected and the new PC is obtained. For example, if a branch instruction is completely executed on the execution stage, it is unnecessary to wait until the commit stage for redirection. Alternatively, another example can be an unconditional jump. This type of instruction has the destination codified inside the instruction. Thus, it can be redirected at the decoder stage.

Consequently, it is possible to encounter other PC redirections in different stages at the same time. It is essential to maintain the priority of the redirection. The predominant redirection must be the redirection produced by the older instruction in the pipeline.

Nevertheless, early PC redirection has similar disadvantages as bypassing. Extra logic as multiplexers is placed. This new logic increases the power and area consumed. However, in this optimization, the number of points that need these new paths is much less than the bypassing. On the other hand, these new redirections can introduce new broad paths generating a new extensive critical path.

The second way to reduce the control hazards is doing *branch prediction*. A branch predictor is a hardware mechanism that predicts the address of the instruction following the branch. The predictors that are the most commonly used in simple processors are Branch Target Buffer (BTB), Branch History Table (BHT), and Return Address Stack (RAS).

- Branch Target Buffer remembers recent target PCs of the control instructions. It has a cache-like structure that stores the target address for a set of instructions. Like the caches, the set is usually obtained from the last bits of the control instruction PC. Then, when a new control instruction accesses the table, the table returns a prediction depending on the set mapped by the particular instruction. The BTB has to be updated at every PC misprediction with the new target PC.

- Branch History Table remembers how the branch was resolved previously, allowing to predict if the branch is taken or not before the execution of the condition. There are many implementations of this predictor. Some of them are simple as the Bimodal predictor, which is a simple array of two-bit saturated counters that crease or decrease depending if the branch is correctly predicted or not. If the upper bit is set, the predictor predicts a taken. However, more sophisticated versions of BTB predictors have been published like Gshare [7] or TAGE [8] which also adds a historical component to the prediction that enables the predictor to detect patterns.

- Return Address Stack is a predictor that is specified to predict return instructions destinations. BTB does not predict return instructions well because the return address does not always have the same direction (different parts of the program can call the same function). Return instructions always return to the last procedure call instruction and return address stacks are highly accurate. The implementation is relatively simple. Every time a CALL instruction is executed, its return address is pushed onto the stack. Every time a RETURN instruction enters the pipeline, the following address is popped off the stack, and the processor continues fetching from it.

All the different branch predictors have more or less the same type of penalties. All of them need new memories to store the information in order to make the prediction. These new memories add extra area and power consumption to the design. Also, since these vast memories used to be implemented with SRAMs in an ASIC design, the Branch predictors tend to have substantial critical paths that can affect the maximum frequency of the design.

#### 2.1.2.2 Superscalar Pipeline

With the basic optimizations, there is a limit of performance that cannot be overpassed easily. The main limitation is that the maximum IPC for a simple single-issue processor is 1 since the maximum number of instructions issued per cycle is only 1. However, during the execution, we will encounter pipeline hazards that will always decrease this optimum IPC.

To optimize the core further, one possible optimization is a superscalar pipeline. A superscalar processor is a single processor that implements a form of parallelism called instruction-level parallelism. Compared with a scalar processor that can execute at most one instruction per clock cycle, a superscalar processor can execute multiple instructions by dispatching multiple instructions to different execution units on the processor simultaneously in one clock cycle. Therefore, it allows more throughput (the number of instructions that can be executed per unit of time) than is possible at a given clock rate.

In order to implement this optimization, a considerable modification of the pipeline is needed. Nearly all the different parts of the pipeline have to be replicated in order to be able to execute multiple instructions in parallel. First of all, the fetch unit needs to be able to fetch at least the number of instructions that will execute in parallel. Also, a new issue logic has to be implemented to detect conflicts between the instructions issued in the same cycle. Also, it needs to track the availability of the resources in the execution stage to know if a particular type of instructions can be executed at that moment or not. This logic tends to be complex and very critical in terms of maximum frequency. Next, the core needs to implement several functional units in the execution stage in order to perform several operations in parallel. Usually, not all the functional units are replicated since some of them, like the FPU, are very expensive in terms of area. Finally, the commit stage also has to be replicated in order to finish several instructions per cycle.

To sum up, this optimization multiplies the maximum limit of the IPC by N (being N the number of parallel instructions on each stage). However, this maximum IPC is difficult to achieve, and the real IPC will be much lower since, with more instructions in parallel, the number of hazards will increase notoriously. Now multiple instructions can have data dependencies, structural dependencies on the same cycle. For example, imagine that there are two instructions, and the second one needs the result of the first one as an operand. Thus, the second instruction will not be issued in the same cycle as the first one. Another example can be on a dual-issue processor with only an FPU. If two floating point instructions must be issued at the same cycle, the second one will need to wait for one cycle since we have encountered a structural hazard. The Intel Pentium P5 [1] was the first modern processor to implement the superscalar concept. In Figure 2.4, there is the diagram of the P5 core. The core has two separate integer pipelines (U and Y) that can be executed in parallel.

Finally, it is essential to see the downsides of these optimizations. As mentioned before, the increment in area is directly proportional to the number of parallel instructions in the core.

Figure 2.4: Intel Pentium P5 pipeline diagram. Source: [1]

Thus, it is a costly optimization. Also, the critical path on the issue stage can be problematic due to the increment of the issue logic complexity.

#### 2.1.2.3 Out-Of-Order Issue and Execution

As shown in the superscalar section, although adding optimizations, there are still some hazards that are hard to solve, like the back-to-back dependency of two instructions, which prevents issuing both instructions at the same time. At this point, on an in-order processor, the second instruction will be blocked until all the hazards are solved. This blocked instruction stalls all the younger instructions since the execution of the instructions should respect the order of the program. In order to remove this strict blocking situation, the OoO (out-of-order) concept is introduced.

The key concept of OoO processing is to allow the processor to avoid stalls by filling these "slots" during execution time with other instructions that are ready to be executed (that do not have any hazard this cycle). However, the result of the instructions must be committed (modify the state of the processor) with the order described on the program (program order). Thus, the instructions must be reordered at the end to appear that the instructions were processed as usual. A reasonably complex circuitry is needed to maintain that program order.

The complex point of an out-of-order design is the issue stage. The issue stage needs to

track which instructions are ready to be executed (the operands are already computed). This optimization is not in the scope of this thesis. However, some mechanisms and ideas of out-of-order processors can be implemented on an in-order design, increasing the performance without making the design that complex. In this thesis, there is a concept that will be used, which is the out-of-order write-back.

Having an out-of-order write-back basically allows two instructions to finish in a different order than the program order. This characteristic is beneficial in terms of performance because a short latency operation can now be executed after a very long latency operation without waiting for the longest to finish. For example, imagine a memory load instruction that misses on the cache. If there is an arithmetic operation with no data dependencies with this load, the arithmetic instruction can be executed before the load gets the data.

Out-of-order write-back is usually implemented alongside the register renaming mechanism. Register renaming is a feature that is consistently implemented on out-of-order designs. Register renaming removes the WAW dependencies (and WAR dependencies on cores in which the access to the register file does not follow the program order) by having more physical registers than architectural registers and maintaining a map of those for each instruction. with register renaming, an instruction can write its result to an architectural register before an older instruction reads the old value of that register. It can be done since the younger instruction will write on a different physical register that later will be mapped as the conflicting architectural register.

Finally, in the out-of-order write-back is essential to reorder the instruction before committing it to follow the program order. This reordering is usually done by a Re-Order Buffer (ROB). The ROB tracks the state of all in-flight instructions in the pipeline. The role of the ROB is to provide the illusion to the programmer that his program executes in order. Once the instructions are decoded and renamed, they are dispatched to the ROB. As instructions finish execution, they inform the ROB and are marked not busy. Once the head of the ROB is no longer busy, the instruction is committed, and its architectural state becomes visible.

#### 2.1.2.4 Single Instruction Multiple Data (SIMD) and Vector Processor

Single instruction, multiple data (SIMD) is a type of parallel processing. As the name suggests, it takes an operation specified in one instruction and applies it to more than one set of data elements simultaneously. For example, a simple arithmetic operation in a traditional scalar processor would operate over two data operands and store the result in the destination register. In SIMD processing, several independent operand pairs operate with the same operation specified on the instruction to produce the same number of independent result data. In Figure 2.5, there is an example of a SIMD addition of a vector of 4 elements.

A processor that implements SIMD exploits data-level parallelism, but not concurrency: at the end, it can process data simultaneously (parallel). However, each computing unit performs the same instruction with different data. SIMD is particularly applicable to common tasks such as matrix multiplication, vector operations used in multimedia, machine learning, and other applications. Most modern CPU designs include SIMD instructions to improve the performance of this kind of application. The first widely deployed desktop SIMD was with Intel's MMX extensions to the x86 architecture [9].

Figure 2.5: SIMD addition of a vector of 4 elements

### 2.2 Physical Implementation

All the processor parts and optimizations explained until now are a collection of combinational functions and memories chosen precisely to achieve maximum performance and efficiency. However, these elements have to be somehow implemented to be used in the real world. These logic circuits and registers are physically implemented using a large assembly of logic gates. Logic gates are simple circuits that generate a digital signal as output that depends on one or more digital signals inputs. The final physical implementation of those logic gates depends on the technology used. For example, we can map all the gates of one design to one FPGA.

FPGAs contain many programmable logic blocks and a hierarchy of reconfigurable interconnects that connect the different blocks. Logic blocks can be configured to calculate complex logic functions or act as simple logic gates like AND and XOR. Also, logic blocks include memory elements. In this case, synthesis and placing tools only have to map the design to the already fabricated logic gates and memories and do routing using the already fabricated interconnection layers.

In the case of an ASIC design, tools do not have a restriction in terms of the logic blocks available. In this case, the tools have more freedom to implement the design. The limits are set by the silicon area available for the design and the maximum power consumption that the design will consume. In ASIC design, the logic will be implemented with transistors. However, the complexity of the tools would be very high if the minimum element were the transistor. The synthesis and place and route tools use already designed essential elements known as standard cells to avoid this complexity.

#### 2.2.1 Standard Cell Libraries

A standard cell is a group of interconnected transistors with its own layout that implements a boolean logic function (e.g., AND, OR, NAND, XOR, NOT) or a storage function (flip-flop or latch). Inside the boolean logic functions, there are simple operations like NAND, NOR, and XOR and more complex functions such as 2-bit full-adder or muxed D-input flip-flop. Many vendors are designing and selling standard cell libraries as Synopsys, Globalfoundries, or TSMC. It is worth mentioning that a particular standard cell can only be used for the particular technology fabrication node associated with it because the essential part of the standard cells is the layout. This layout is made expressly for a particular technology.

Standard cells are designed to optimize the design for a particular purpose. There are standard cells optimized for power, area, or performance. Thus, there are several types of

Figure 2.6: Comparation between different standard cells with different tracks [2]

standard cells, depending on those parameters. There are many parameters on a technology node that can be configured, such as the number of tracks, gate pitch, minimum metal pitch, cell ratio, possible PMOS width, and NMOS width [10]. Selecting those parameters is done by the vendor. The vendor provides several libraries with specific configurations.

The user has to select a specific library depending on the particular design. Usually, the parameters which the user can select are the technology node (65nm, 22 nm, 7 nm), transistor gate pitch, which is also referred to as Contacted Poly Pitch (CPP) (104CPP, 116CPP), the number of tracks (7T, 8T, 12T), or the threshold voltage (regular-Vt, high-Vt f, low-Vt).

The number of tracks is generally used as a unit to define the height of the std cell. It can be related to metal lanes that can be horizontally routed inside the standard cell. For example, a 9 track library implies that 9 routing tracks are available for routing 9 parallel wires with minimum pitch inside a standard cell. In Figure 2.6

If we compare, for example, 6T and 9T libraries, 9T will be faster because it will have more area, and it can have higher drive strength transistors or more transistors to make a more complex operation. Thus, it will give better performance. However, using the 9T library will consume more area and power for the same circuit.

- 9T library is used for higher performance.

- 6T library is used for higher density and low power.

#### 2.2.2 Hard IP Blocks

Standard cell libraries give enough modularity to implement any digital logic. However, sometimes the efficiency or performance achievable with those cells is not enough. Maybe the design has an analog part that is not implementable with the standard cells. For these situations, Hard IP blocks are used. Hard IP blocks are defined as IP cores that cannot be modified. Because they have a low-level representation, hard IP offers better predictability of chip performance in terms of timing and area. Thus, analog IP (SerDes, PLLs, DAC, ADC, PHYs) are provided to chip makers in transistor-layout format. Also, some digital circuits like SRAMs (very dense memories) are given in a hard IP format.

### 2.2.3 Performance of a Digital Circuit. Process, Voltage, Temperature Variations

The performance of a single-core processor is the direct multiplication of the IPC and the clock frequency, and therefore it is essential to give the same importance to both parameters. Sometimes the most challenging part of the design is to achieve the right balance of these two parameters to get the maximum performance. The computer architects use instructions-per-cycle (IPC) as a performance metric, but often *ignore* the length of the clock cycle itself.

The achievable clock frequency of a circuit depends basically on two different parts. The digital design itself will determine how many standard cells will have the critical path. The other factor is the delay associated with each standard cell. This delay is associated with the underlying technology used to implement them. Nowadays, processors mainly use Metal Oxide Semiconductor Field Effect Transistor (MOSFET) as the base technology, where all transistors and the interconnection paths have some associated delay. This delay is cumulative and applies to all signals that flow through a given path.

This standard cell delay is not equal for all the chips of the same technology. It can also depend on the chip's conditions. A fundamental concept for synthesis and physical design are Process, Voltage, Temperature (PVT) variations. Since a chip has to work into very different conditions correctly, some characterization of the technology is needed for a wide range of conditions. To ensure that the design is capable of performing correctly in the target frequency, it is necessary to simulate it at different conditions of the process, voltage, and temperature, which the integrated circuit may face after fabrication. These conditions are called corners.

**Process variation** is the deviation in attributes of the transistor during the fabrication. Not all the dies in a wafer are manufactured with the same characteristics. These differences come from process variations like a bad centering of the tools or the not uniform distribution of metal particles. This variation is dominant in lower node technologies (<65nm).

Voltage variation is significant nowadays since the operation voltages of modern technology nodes are near or below 1 V. Thus, a minimal variation in the power supply can produce a significant variation of the operating point of the transistors. We need to consider voltage variation in the design process. Multiple factors can produce voltage variation, such as the parasitic resistance of the power grid. Another factor is the parasitic inductance of the circuit, which is a rapid increment of the current flowing in the circuit that can cause voltage spikes. However, this voltage variation can be used intentionally to reduce the power consumption or be augmented to increase performance.

**Temperature variation** is not only related to the ambient temperature. In the end, the temperature on the chip is the sum of the ambient temperature, and a large amount of power

is dissipated in a tiny chip area that increases the temperature significantly. The temperature inside the chip can vary within a big range depending mainly on the power dissipation of the chip. That is why temperature variation needs to be considered. In the end, temperature variation has to be considered because the delay of the cells varies with the temperature. On all technologies, the delay increases with temperature. However, this is not true for modern technology nodes. For deep sub-micron technologies, exists a phenomenon called temperature inversion [11].

## 2.3 RTL Simulation, FPGA Emulation, and Gate Level Simulation

In processor design, a huge part of the development efforts is spent on verifying the design. It is essential to test the design constantly to find errors and evaluate the applied modifications' performance implications. Testing regularly the design makes it easier to find which step of the implementation has produced some error and fix it early. The most common thing is testing the design at different levels.

In the early stages, when the design is even in the specification stage, the computer architects use high-level simulators to evaluate the early specifications of the design. There are accurate cycle simulators for single or small multi-core processors [12], simulators for large multi-core processors [13, 14], and simulators for massive multi-core HPC systems with more than 2048 cores [15]. However, these simulators only give the computer architects some estimation of the performance they will get to the final design.

When the design is implemented or even partially implemented, the most commonly used strategy is the RTL simulation. RTL simulation is the cheapest way for complexity and infrastructure development to simulate a design since the only necessary thing is the RTL design. The simulator makes a model of the completed digital design, which models the logic function. Also, the simulators maintain the naming of each variable in the HDL design, and it can give the cycle state of each variable for debugging purposes. RTL simulations are cycle-accurate. However, it is impossible to compute the sub-cycle delays since it does not have a physical technology model. In terms of simulation time, RTL simulations are slow since the computer has to compute the result of all the registers and wires one by one for each cycle. This peculiarity makes the simulation very suitable for debugging purposes but not suitable for benchmarking very large programs. New ideas like [16] allow connecting small RTL modules to a high-level full-system simulator allowing the execution of larger benchmarks taking advantage of the fast execution of these simulators.

For benchmarking of very large programs, it is necessary to emulate the processor design on an FPGA. FPGAs give the developer a much easier physical implementation of the design than ASIC. In the end, the physical design process is similar, but since the FPGA is reconfigurable nearly in real-time, the loop from having a design to having that design implemented and running on an FPGA is much faster than having a custom ASIC running. The FPGA performance can be ten times lower than ASIC. However, it is more than enough to be used as a benchmarking platform. FPGA prototyping has the necessity of using hard IPs for external communication and to obtain resulting data. Apart from this extra circuitry needed, FPGAs have a big downs side compared to the RTL simulation that is the fact of not having the possibility to know the value of all the wires or registers cycle by cycle. This happens because the FPGA does not have enough outputs to give that amount of information. Therefore, possible errors are hard to find and solve. Another downside of the FPGA prototyping compared with the RTL simulation is the compilation/synthesis time. The design synthesis is quite slow, and for small runs, the gain on emulation speed of FPGA over the RTL simulation is not worth it.

Finally, with the two ways of simulation/emulation described, it is not possible to ensure that the design is bug-free. Also, it is impossible to know the performance expected in the final ASIC implementation since it is not possible to obtain the frequency of the design. For that purpose, gate-level simulations are used. Mainly, the gate-level simulations are used to ensure the correct operation of the circuit in the post-synthesis and post-P&R states. This type of simulation is really accurate because it includes all the information of the technology node that will be used for fabrication. It uses the model of the technology standard cells and hard IPs. With this information, it is possible to find timing constraints violations, find glitches, and find possible propagation of X values (e.i., uninitialized registers). In Table 2.1, there is a summary of all the different simulations and emulations approaches with their properties.

|                       | Speed      | Information               | Time Stamp               |

|-----------------------|------------|---------------------------|--------------------------|

| High level simulator  | Fast       | High level information    | Cycle                    |

| RTL simulation        | Slow       | Register and wires state  | Cycle                    |

| FPGA emulation        | Fast       | Limited by the I/O        | Limited by the I/O speed |

| Gate level simulation | Super slow | Post-synthesis gate state | Sub-cycle                |

Table 2.1: Different types of simulation and emulation approaches together with their properties

## 2.4 Processor Benchmarking

It is not easy to compare two processor designs in terms of performance. Even having very similar specifications, the performance can vary a lot depending on the implementation of the system. Similarly, it is challenging to predict how a modification will affect the overall performance of a processor. Moreover, a processor will not perform equally on all the different workloads.

For this reason, it is essential to have a methodology to measure the design performance after each microarchitectural decision. Also, it will be needed for comparing different designs. This methodology is known as benchmarking. Benchmarks are small programs designed to mimic a particular type of workload on the compact program's design. Benchmarks extract the critical algorithms of an application, which contains the performance-sensitive aspects of that application. Exists two types of benchmarks. The first type is the synthetic benchmarks. These benchmarks are specially created programs that stress some particular components of the architecture. Secondly, the application benchmarks run real-world programs on the design to evaluate the performance of a real-world application in a very accurate manner. The application benchmarks have an accurate representation of real-world problems. Synthetic benchmarks help test individual processor parts in a specific way.

During this project, two benchmarks have been used. Embedded Microprocessors Benchmarks Consortium (EEMBC) CoreMark has been selected, a compact benchmark, to quickly evaluate the performance impact of the different modifications made to the processor during this thesis. Also, it is useful for a quick comparison of our design to other competitors since it returns a simple score output. The second benchmark is the EEMBC AutoBench suite. EEMBC AutoBench gives a more robust performance evaluation since it has several benchmarks emulating different applications. This way is easier to see in which application the processor is still not achieving the target results.

#### 2.4.1 CoreMark

EEMBC's CoreMark [17] is a benchmark that measures the performance of CPUs used in embedded systems. It is intended to become an industry standard, replacing the widely used Dhrystone benchmark [18]. CoreMark returns a performance indicator generated by the execution of a simple code (CoreMark and CoreMark/MHz) replacing the DMIPS/MHz obtained in the Dhrystone. However, this simple code is not entirely arbitrary and synthetic. The code for the benchmark uses basic data structures and algorithms that are common in practically any application. CoreMark executes the following list of basic algorithms: list processing (find and sort), state machine (determine if an input stream contains valid numbers), matrix manipulation (common matrix operations), and Cyclic Redundancy Check (CRC). CoreMark also sets specific rules about how to run the code and report results, thereby eliminating inconsistencies. To avoid aggressive optimizations from the compiler side, every algorithm in the benchmark derives a value that is not available at compile time.

Finally, it is worth mentioning that the CRC algorithm serves another function, a part of the computational complexity. It works as a linked list's hash function to ensure the CoreMark benchmark's correct operation, essentially providing a self-checking mechanism.

CoreMark is commonly used to compare performance between processors quickly. Indeed, it can not be completely reliable, but it gives an initial idea to rank different processors quickly and with some level of trust.

#### 2.4.2 EEMBC AutoBench Performance Benchmark Suite

AutoBench 1.1 [19] is a suite of benchmarks created by EEMBC focused on the performance evaluation for microprocessors in automotive, industrial, and general-purpose applications. This benchmark suite has 16 kernels divided into two groups depending on whether they have ,or not floating point operations. The two groups are:

• Integer kernels: Finite Impulse Response (FIR) (aifirf), Bit Manipulation (bitmnp), Cache "Buster" (cacheb), CAN Remote Data Request (canrdr), Pointer Chasing (pntrch), Pulse Width Modulation (PWM) (puwmod), Road Speed Calculation (rspeed), Tooth to Spark (ttspark). • floating point benchmarks: Angle to Time Conversion (a2time), Fast Fourier Transform (FFT) (aifftr), Fourier Transform (iFFT) (aifft), Basic Integer and Floating Point (basefp), Inverse Discrete Cosine Transform (iDCT) (idctrn), Inverse Fast Infinite Impulse Response (IIR) Filter (iirflt), Matrix Arithmetic (matrix), and Table Lookup and Interpolation (tblook).

# 3 Related Work

Nowadays, RISC-V, with its open-source nature, is pushing universities and research centers to start on the development of open-source processors and platforms. Many designs are being developed, from very simple in-order designs to superscalar out-of-order designs with huge complexity. This new opportunity that the open-source environment is giving to the academy is pushing computer architecture research into a promising future. This section presents the most well-known academic designs proposed by the different research centers and universities.

### 3.1 RISC-V ISA

RISC-V is an open instruction set architecture (ISA) that originated in 2010 from a research project at the University of California at Berkeley and is now supported by the RISC-V Foundation, counting over 100 international institutions, including universities and research centers, and companies worldwide. RISC-V is a new ISA initially designed to support computer architecture research and education, but it is sophisticated enough to become a standard in the industry.

The RISC-V ISA is defined as avoiding implementation details as much as possible (although a commentary is included in implementation-driven decisions). It should be read as the software-visible interface to a wide variety of implementations rather than designing a particular hardware artifact. The RISC-V manual is structured in two volumes. There is the unprivileged volume [20] that covers the design of the base unprivileged instructions, including optional unprivileged ISA extensions. Unprivileged instructions are generally used in all privilege modes in all privileged architectures, though behavior might not vary depending on privilege mode and privilege architecture. The second volume provides [21] the design of the privileged architecture.

The unprivileged ISA can be separated into two blocks, base integer ISA and extensions. It allows small designs to implement only the specific extensions that it needs in each case. In this way, the design can still be efficient in a specific field. The most commonly used extensions are listed in Table 3.1.

### 3.2 In-Order Designs

There are many in-order designs in academia since the complexity is lower than other designs, and it is easy to have a functional version implemented. It can be quickly implemented and

| Name                                                      | Description                                                   |  |  |  |  |  |  |

|-----------------------------------------------------------|---------------------------------------------------------------|--|--|--|--|--|--|

|                                                           | Base                                                          |  |  |  |  |  |  |

| RV32I                                                     | Base Integer Instruction Set, 32-bit                          |  |  |  |  |  |  |

| RV32E                                                     | Base Integer Instruction Set (embedded), 32-bit, 16 registers |  |  |  |  |  |  |

| RV64I                                                     | Base Integer Instruction Set, 64-bit                          |  |  |  |  |  |  |

| <b>RV128I</b> Base Integer Instruction Set, 128-bit       |                                                               |  |  |  |  |  |  |

|                                                           | Extension                                                     |  |  |  |  |  |  |

| M Standard Extension for Integer Multiplication and Divis |                                                               |  |  |  |  |  |  |

| A Standard Extension for Atomic Instructions              |                                                               |  |  |  |  |  |  |

| F                                                         | Standard Extension for Single-Precision floating point        |  |  |  |  |  |  |

| D                                                         | Standard Extension for Double-Precision floating point        |  |  |  |  |  |  |

| <b>G</b> Shorthand for the base and above extensions      |                                                               |  |  |  |  |  |  |

| С                                                         | Standard Extension for Compressed Instructions                |  |  |  |  |  |  |

| V                                                         | Standard Extension for Vector Operations                      |  |  |  |  |  |  |

Table 3.1: RISC-V: base Integer ISAs and extensions

verified thanks to its simple nature. In this section, there are a few examples of in-order designs with more relevant information.

#### 3.2.1 Ariane Core