Master in Electronic Engineering

Master's Thesis

# Genomic Co-processor for Long Read Assembly

Advisor:

Prof. Marco D. Santambrogio (Politecnico di Milano)

**Co-advisor:** Prof. Jordi Cosp Vilella (Universitat Politècnica de Catalunya)

Author: Marina Martí Quesada

Barcelona, June 2021

#### Abstract

Genomics data is transforming medicine and our understanding of life in fundamental ways; however, it is far outpacing Moore's Law. Third-generation sequencing technologies produce 100X longer reads than second generation technologies and reveal a much broader mutation spectrum of disease and evolution.

However, these technologies incur prohibitively high computational costs. In order to enable the vast potential of exponentially growing genomics data, domain specific acceleration provides one of the few remaining approaches to continue to scale compute performance and efficiency, since general-purpose architectures are struggling to handle the huge amount of data needed for genome alignment.

The aim of this project is to implement a genomic-coprocessor targeting HPC FPGAs starting from the Darwin FPGA co-processor. In this scenario, the final objective is the simulation and implementation of the algorithms described by Darwin using Alveo boards, exploiting High Bandwidth Memory (HBM) to increase its performance.

## **Acknowledgements**

I take this section to express my gratitude to several people who have helped me and given me their support during the development of this project.

First of all, I want to thank Professor Marco D. Santambrogio, advisor of this project, for giving me the opportunity to write my Master's Thesis in Politecnico di Milano.

In addition, I would like to thank Alberto Zeni, PhD Student in the NECSTLab of Politecnico di Milano, for providing me all the necessary information to start the project, mentoring me during all the semester, and for all his help and support during the realization of this project.

I express my gratitude also to Emanuele Del Sozzo and Davide Conficcioni, also PhD Students in the NECSTLab.

Also, I would like to thank Jordi Cosp for his support in this thesis and in other projects developed during the Bachelor's and Master's.

Additionally, I would like to thank Romà Macario, Asier Zubeldia, Sílvia Farràs, Jia Puig, Jenthe Goossens, Nahida Aktar, Franzi Andreas and Nesrin Kerschek for their support and their advice.

Finally, I would like to thank my parents and sister for their support since I started my university studies until now.

Thank you all very much.

# Table of contents

| Absilac                                                                                         | t                                                                                                   |                                                                                                                                                                                             | 1                                                                                |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Acknow                                                                                          | ledge                                                                                               | ements                                                                                                                                                                                      | 2                                                                                |

| Table o                                                                                         | f cont                                                                                              | tents                                                                                                                                                                                       | 3                                                                                |

| List of F                                                                                       | igure                                                                                               | 9S                                                                                                                                                                                          | 5                                                                                |

| List of T                                                                                       | ables                                                                                               | 5                                                                                                                                                                                           | 7                                                                                |

| 1. Intr                                                                                         | oduc                                                                                                | tion                                                                                                                                                                                        | 8                                                                                |

| 1.1.                                                                                            | Ger                                                                                                 | nome Assembly                                                                                                                                                                               | 8                                                                                |

| 1.2.                                                                                            | Stat                                                                                                | tement of purpose                                                                                                                                                                           | 11                                                                               |

| 2. Sta                                                                                          | te of                                                                                               | the art                                                                                                                                                                                     | 13                                                                               |

| 2.1.                                                                                            | Smi                                                                                                 | th-Waterman Algorithm                                                                                                                                                                       | 13                                                                               |

| 2.2.                                                                                            | Ger                                                                                                 | nome alignment heuristics                                                                                                                                                                   | 16                                                                               |

| 2.3.                                                                                            | Dar                                                                                                 | win co-processor                                                                                                                                                                            | 18                                                                               |

| 2.3                                                                                             | .1.                                                                                                 | D-SOFT Algorithm                                                                                                                                                                            | 18                                                                               |

| 2.3                                                                                             | .2.                                                                                                 | GACT Algorithm                                                                                                                                                                              | 19                                                                               |

| 2.3                                                                                             | 3                                                                                                   | Accelerator Design                                                                                                                                                                          | 20                                                                               |

| 2.0                                                                                             |                                                                                                     |                                                                                                                                                                                             |                                                                                  |

| 2.4.                                                                                            | -                                                                                                   | dware Acceleration                                                                                                                                                                          |                                                                                  |

| 2.4.                                                                                            | Har                                                                                                 | ·                                                                                                                                                                                           | 23                                                                               |

| 2.4.                                                                                            | Hare<br>thodo                                                                                       | dware Acceleration                                                                                                                                                                          | 23<br>26                                                                         |

| 2.4.<br>3. Me                                                                                   | Hard<br>thodo<br>AXI                                                                                | dware Acceleration                                                                                                                                                                          | 23<br>26<br>26                                                                   |

| 2.4.<br>3. Me<br>3.1.                                                                           | Haro<br>thodo<br>AXI<br>.1.                                                                         | dware Acceleration<br>blogy<br>Interface                                                                                                                                                    | 23<br>26<br>26<br>28                                                             |

| 2.4.<br>3. Me<br>3.1.<br>3.1<br>3.1                                                             | Hard<br>thodo<br>AXI<br>.1.<br>.2.                                                                  | dware Acceleration<br>blogy<br>Interface<br>AXI Transactions                                                                                                                                | 23<br>26<br>26<br>28<br>30                                                       |

| 2.4.<br>3. Me<br>3.1.<br>3.1<br>3.1                                                             | Haro<br>thodo<br>AXI<br>.1.<br>.2.<br>.3.                                                           | dware Acceleration<br>blogy<br>Interface<br>AXI Transactions<br>AXI4-Lite                                                                                                                   | 23<br>26<br>26<br>28<br>30<br>30                                                 |

| 2.4.<br>3. Me<br>3.1.<br>3.1<br>3.1<br>3.1                                                      | Haro<br>thodo<br>AXI<br>.1.<br>.2.<br>.3.<br>Bloo                                                   | dware Acceleration<br>blogy<br>Interface<br>AXI Transactions<br>AXI4-Lite<br>AXI interface implementation                                                                                   | 23<br>26<br>26<br>28<br>30<br>30<br>33                                           |

| 2.4.<br>3. Me<br>3.1.<br>3.1<br>3.1<br>3.1<br>3.2.                                              | Haro<br>thodo<br>AXI<br>.1.<br>.2.<br>.3.<br>Bloo<br>Sim                                            | dware Acceleration<br>blogy<br>Interface<br>AXI Transactions<br>AXI4-Lite<br>AXI interface implementation<br>ck Design                                                                      | 23<br>26<br>26<br>28<br>30<br>30<br>33<br>36                                     |

| 2.4.<br>3. Me<br>3.1.<br>3.1<br>3.1<br>3.1<br>3.2.<br>3.3.                                      | Haro<br>thodo<br>AXI<br>.1.<br>.2.<br>.3.<br>Bloo<br>Sim<br>High                                    | dware Acceleration<br>blogy<br>Interface<br>AXI Transactions<br>AXI4-Lite<br>AXI interface implementation<br>ck Design<br>ulations                                                          | 23<br>26<br>28<br>30<br>30<br>30<br>33<br>36<br>38                               |

| 2.4.<br>3. Me<br>3.1.<br>3.1<br>3.1<br>3.2.<br>3.3.<br>3.4.<br>3.5.                             | Haro<br>thodo<br>AXI<br>.1.<br>.2.<br>.3.<br>Bloo<br>Sim<br>High<br>Hos                             | dware Acceleration<br>blogy<br>Interface<br>AXI Transactions<br>AXI4-Lite<br>AXI4-Lite<br>AXI interface implementation<br>ck Design<br>ulations<br>h Bandwidth Memory (HBM)                 | 23<br>26<br>28<br>30<br>30<br>30<br>30<br>33<br>36<br>38<br>42                   |

| 2.4.<br>3. Me<br>3.1.<br>3.1<br>3.1<br>3.2.<br>3.3.<br>3.4.<br>3.5.<br>4. Re                    | Haro<br>thodo<br>AXI<br>.1.<br>.2.<br>.3.<br>Bloo<br>Sim<br>High<br>Hos<br>sults.                   | dware Acceleration<br>blogy<br>Interface<br>AXI Transactions<br>AXI4-Lite<br>AXI interface implementation<br>ck Design<br>ulations<br>h Bandwidth Memory (HBM)<br>at Processor              | 23<br>26<br>26<br>30<br>30<br>30<br>30<br>33<br>36<br>38<br>42<br>43             |

| 2.4.<br>3. Me<br>3.1.<br>3.1<br>3.1<br>3.2.<br>3.3.<br>3.4.<br>3.5.<br>4. Re<br>5. But          | Haro<br>thodo<br>AXI<br>.1.<br>.2.<br>.3.<br>Bloo<br>Sim<br>High<br>Hos<br>sults.<br>dget           | dware Acceleration<br>blogy<br>Interface<br>AXI Transactions<br>AXI4-Lite<br>AXI4-Lite<br>AXI interface implementation<br>ck Design<br>ulations<br>h Bandwidth Memory (HBM)<br>at Processor | 23<br>26<br>26<br>28<br>30<br>30<br>30<br>30<br>33<br>36<br>38<br>42<br>43<br>45 |

| 2.4.<br>3. Me<br>3.1.<br>3.1<br>3.1<br>3.2.<br>3.3.<br>3.4.<br>3.5.<br>4. Re<br>5. But<br>6. Co | Hard<br>thodc<br>AXI<br>.1.<br>.2.<br>.3.<br>Bloc<br>Sim<br>High<br>Hos<br>sults .<br>dget<br>nclus | dware Acceleration                                                                                                                                                                          | 23<br>26<br>26<br>30<br>30<br>30<br>33<br>36<br>38<br>42<br>43<br>43<br>45<br>48 |

# List of Figures

| Figure 1. Genomics Data growth comparison with Moore's Law and CPU performance from 2000 to 2018                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2. Genome assembly example9                                                                                                                    |

| Figure 3. Example of input genome sequence (orange), its copies (blue), and its set of reads (green)                                                  |

| Figure 4. Example of a set of ordered reads from an input sequence (left), and the actual reads obtained from the input, with unknown order (right)10 |

| Figure 5. Sequence alignment scoring scheme example13                                                                                                 |

| Figure 6. Four macro phases of the Smith-Waterman algorithm14                                                                                         |

| Figure 7. Smith-Waterman matrix calculation example15                                                                                                 |

| Figure 8. Smith-Waterman traceback matrix example16                                                                                                   |

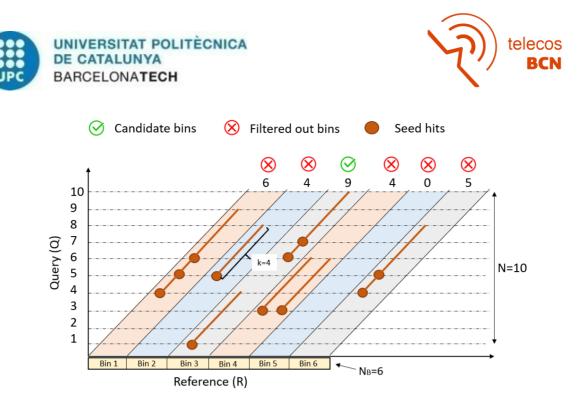

| Figure 9. Illustration of D-SOFT algorithm for k=4, N=10, h=8, NB=619                                                                                 |

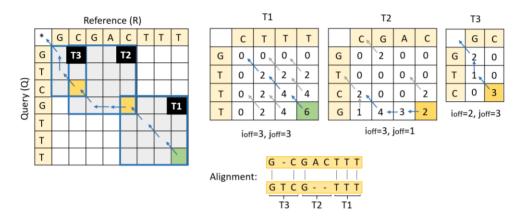

| Figure 10. Illustration of extension stage in GACT algorithm using an example dynamic programming (DP) matrix for parameters (T=4, O=1)20             |

| Figure 11. Reference-guided and de novo assembly (overlap step) using D-SOFT and GACT20                                                               |

| Figure 12. Darwin's systolic array architecture21                                                                                                     |

| Figure 13. Darwin's systolic array architecture with traceback storage                                                                                |

| Figure 14. Comparison between the X-drop algorithm and the GACT algorithm22                                                                           |

| Figure 15. Darwin's outer-loop parallelism23                                                                                                          |

| Figure 16. Host CPU augmented with Xilinx FPGAs in Alveo Cards24                                                                                      |

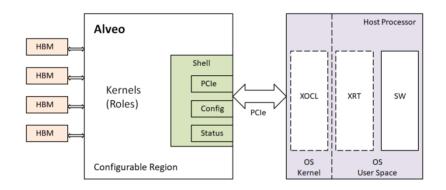

| Figure 17. Software stack (left) and hardware components (right) communication through PCIe                                                           |

| Figure 18. Alveo card shell and role topology25                                                                                                       |

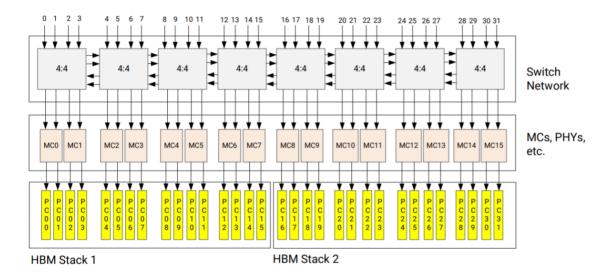

| Figure 19. High-Level Diagram of Two HBM Stacks. [2]                                                                                                  |

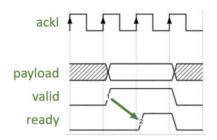

| Figure 20. Basic handshake mechanism of the AXI protocol27                                                                                            |

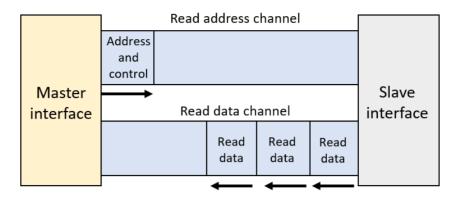

| Figure 21. AXI Read Address and Read Data channels                                                                                                    |

| Figure 22. AXI Write Address, Write Data and Write Response channels                                                                                  |

| Figure 23. AXI Read transaction example                                                                                                               |

| Figure 24. AXI Write transaction example                                                                                                              |

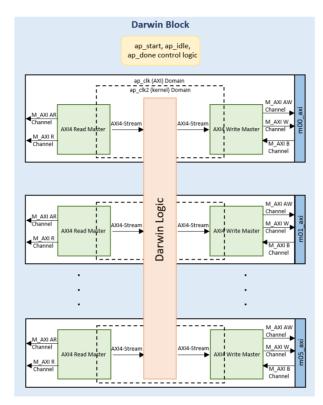

| Figure 25. Top-level Darwin kernel structure                                                                                                          |

| Figure 26. Darwin kernel RTL block structure                                                                                                          |

| Figure 27. Function prototype and register map for the Darwin kernel                                                                                  |

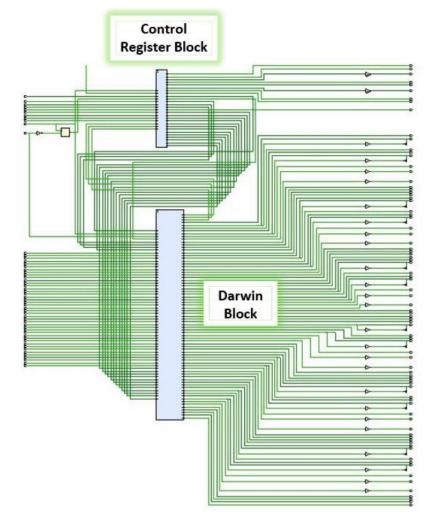

| Figure 28. To  | op-level blocks of the design (control register and Darwin).          | 35 |

|----------------|-----------------------------------------------------------------------|----|

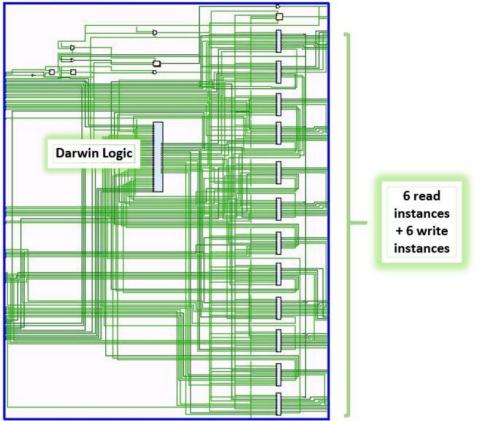

| Figure 29. Da  | arwin Block design                                                    | 36 |

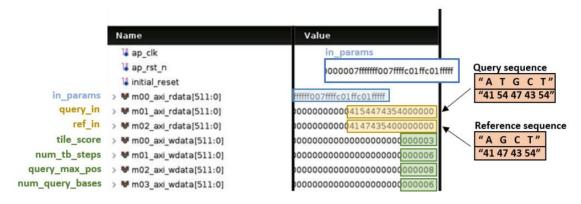

| Figure 30. Q   | Query and reference sequences used for simulation.                    | 36 |

| Figure 31. Si  | imulation results for the query "ATGCT" and reference sequence "AGCT" | 37 |

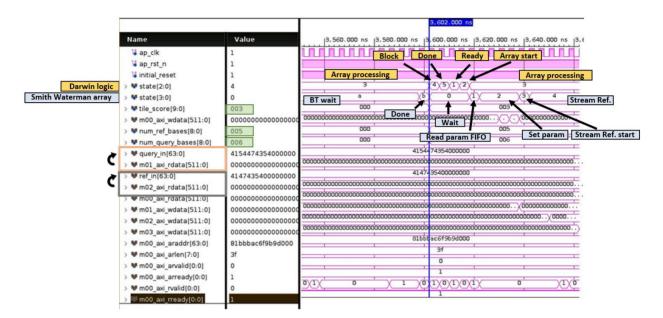

| Figure 32. AX  | XI Master 0 interface signals in Vivado Simulation.                   | 37 |

| Figure 33. Da  | parwin Logic simulation results for Q = "ATGCT" and R = "AGCT"        | 38 |

| Figure 34. Al  | lveo U280 board with the two HBM stacks                               | 39 |

| Figure 35. Ar  | rchitecture of Alveo HBM subsystem.                                   | 40 |

| Figure 36. Pl  | latform diagram in Vitis Analyzer tool                                | 40 |

| Figure 37. Int | formation about the kernel bitstream generation, provided by Vitis    | 41 |

| Figure 38. Da  | arwin Kernel system diagram obtained through Vitis HLS.               | 41 |

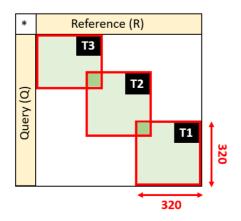

| Figure 39. G   | GACT array for tile size T = 320                                      | 43 |

# List of Tables

| Table 1. Short and long read assembly required hours                            | 10 |

|---------------------------------------------------------------------------------|----|

| Table 2. AXI configurations used for each GACT input in the RTL kernel          | 33 |

| Table 3. Resource utilization of the final design implemented in the Alveo U280 | 43 |

| Table 4. Design timing summary                                                  | 43 |

| Table 5. Temporal analysis of the project.                                      | 45 |

| Table 6. Breakdown of the project budget                                        | 46 |

# 1. Introduction

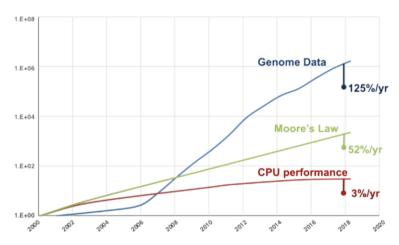

Genomics data is transforming medicine and our understanding of life in fundamental ways; helping the diagnosing and decoding of diseases, the understanding of ancestry through genotype-phenotype matching, understanding molecular bases of evolution, and much more. However, from 2001 to 2018, the growth of genomics data has been of 125% per year, and it is far outpacing the Moore's Law. In contrast, CPU performance has slowed down significantly; from 20% per year in early 2000's to only 3% per year today, which results as a considerable gap between CPU performance and genomics data. This gap is expected to keep increasing in the future, as genomics data continues to double every year, as shown in figure 1.

Figure 1. Genomics Data growth comparison with Moore's Law and CPU performance from 2000 to 2018.

#### 1.1. Genome Assembly

Genome assembly is the process where many copies are chopped up into fragments from a genome, then these fragments are sequenced, and finally they are put together to obtain the original genome from those reads previously sampled.

| Genome     |

|------------|

|            |

|            |

| Sequencing |

| Reads      |

| Assembly   |

| Genome     |

|            |

|            |

Figure 2. Genome assembly example.

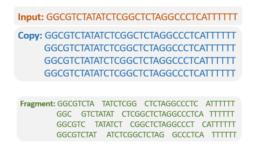

As figure 2 shows, genome assembly can be understood like putting together a puzzle without being able to know what it looks like. The input of the assembly process is a genome sequence, for example, the sequence of the figure 3 (in orange). As shown, a genome sequence consists of a list of nucleotides (A, C, G and T for DNA genomes) that make up all the chromosomes of an individual or a species. From that input sequence, many copies are taken and fragmented into pieces, which are then read using DNA sequencers. This process is called whole-genome "shotgun" sequencing, where "shotgun" refers to the random fragmentation of the whole genome, like it was fired from a shotgun.

Figure 3. Example of input genome sequence (orange), its copies (blue), and its set of reads (green).

The problem is that the reads are not known where they come from, we do not have the total ordering of the reads, only having the read sequences, the assembly process has to figure out what the order of those reads were on the original genome, like shown in figure 4.

Input: GGCGTCTATATCTCGGCTCTAGGCCCTATTTTT CTCTAGGCCCTCATTTTT GGCTCTAGGCCCTCATTTTT CTCTGGGCCTCAGGCCCTCATTTTT CTCCGGCTCTAGGCCCTCATTTTT TATCTCGGCTCTAGGCCCTCA TATCTCGGCTCTAGGCC CTCTATATCTCGGCTCTAGG GGCGTCTATATCT GGCGTCTATATCT GGCGTCTATATCT

CTAGGCCCTCATTTTT GGCGTCTATATCT CTCTAGGCCCTCATTTTT TCTATATCTCGGCTCTAGG GGCTCTAGGCCCTCATTTTT CTCGGCTCTAGGCCCTCATTTT TATCTCGGCTCTAGGCCCTCA GGCGTCTATATC TATCTCGGCTCTAGGCC GGCGTCTATATCTCG

Input: GGCGTCTATATCTCGGCTCTAGGCCCTCATTTTT

Figure 4. Example of a set of ordered reads from an input sequence (left), and the actual reads obtained from the input, with unknown order (right).

There are two types of genome assembly; referenced assembly and *de novo* assembly. In the referenced assembly, two input sequences are used, the reference and the query, where the reference sequene give an approximation of the ordering of the original genome. On the other hand, in *de novo* assembly nothing is known about the original genome, only having the set of reads, and the original sequence has to be reconstructed from the query sequence.

The target application of this work is genomics assembly. The reason why we have such a massive growth in genomics data is due the technology of DNA sequencing, which enables us to read raw nucleotides from a DNA sample. However, the result sequences can be different from the original sequence from which the read was taken, and in particular, the read will have a certain number of substitutions, deletions or insertions with respect to the original sequence, and that is what we call alignment. Most of these errors tend to be stochastic in nature, and so we can naturally lower the errors or fix them, using a consensus of multiple alignment reads, and this process is what we call assembly.

As sequencing technologies incur prohibitively high computational costs, in order to enable the vast potential of exponentially growing genomics data, domain specific acceleration provides one of the few remaining approaches to continue to scale compute performance and efficiency, since general-purpose architectures are struggling to handle the huge amount of data needed for genome alignment.

Long reads tend to be very noisy, with a 15-40% of error rate, compared to 0-2% error rate in short reads. As a result, the assembly process, typically when using a reference sequence to guide the assembly, takes up to 5000 CPU hours, and when we assemble the genome *de novo* without the bias or help of a reference genome it can take upt to 60000 CPU hours, which is orders of magnitude higher than in short read sequencing. This is the reason why the acceleration for long read assembly is needed.

|                             | Reference-guided assembly | De novo assembly       |

|-----------------------------|---------------------------|------------------------|

|                             | (54x human)               | (54x human)            |

| Short reads                 | Up to 200 CPU hours       | Up to 2,000 CPU hours  |

| (~100bp, 0-2% error rate)   |                           |                        |

| Long reads                  | Up to 5,000 CPU hours     | Up to 60,000 CPU hours |

| (~10Kbp, 15-40% error rate) |                           |                        |

Table 1. Short and long read assembly required hours.

Long reads are considered to be the holy grail of sequencing for many reasons. It is the only technology which enables us to read a wide spectrum of mutations, in particular structure variations, which is tandem duplications, inversions or pseudo gene insertions in haplotype phasing, which is to distinguish maternal a paternal mutations, and in resolving the repeats, since around 50% of the human genome is repetitive.

In 2008-2009, sequencing technologies that took a different approach than second-generation platforms were dubbed "third-generation."

Pacific Biosciences and Oxford Nanopore Technology are two businesses that are at the forefront of third-generation sequencing technology development. When it comes to sequencing single DNA molecules, these businesses take very different approaches.

PacBio invented the real-time sequencing platform for single molecules (SMRT).

Passing a DNA molecule through a nanoscale pore structure and then monitoring changes in the electrical field surrounding the pore is how Oxford Nanopore's technology works.

#### 1.2. <u>Statement of purpose</u>

The aim of this project is to implement a genomic co-processor targeting high performance computing (HPC) FPGAs, starting from the Darwin co-processor, previously developed by Yatish Turakhia, Gill Bejerano and William J. Dally, from Standford University in 2018 [1]. Darwin is a co-processor for genomic sequence alignment that provides up to 15,000x speedup over the state-of-the-art software for reference-guided assembly of third generation reads. Darwin achieves this speedup through hardware-software co-design, by combining a novel filtering algorithm, D-SOFT, and a hardware-accelerated version of GACT, a novel alignment algorithm. Darwin has been implemented for their developers in an Intel Arria 10 FPGA. In this project the target hardware is HPC FPGAs, specifically the Xilinx Alveo boards [2].

Field Programming Gate Arrays (FPGAs) are a particular family of integrated circuits intended for custom hardware implementation, with the key property of being capable of reconfiguration for an infinite number of times. Currently FPGAs are the state of the art of Programmable Logic Devices. Reconfiguring an FPGA means changing its functionality to support a new application, and it is equal to have some new pieces of hardware mapped on the FPGA chip, having to implement a new functionality. In other words, FPGA make it possible to have custom-designed high-density hardware in an electronic circuit, with the added bonus of having the possibility of changing it whenever there is the need, even while the whole application is still running. Nowadays we can find FPGAs in the cloud, like in the Amazon F1 instances, moreover, the "incorporation" of reconfigurable array logic into a microprocessor provides an alternative growth path that allows application specialisation while benefiting from the full effects of commoditisation. Like modern reconfigurable logic arrays, a single microprocessor design can be employed in a wide variety of applications. Application acceleration and system adaptation can be achieved by specialising the reconfigurable logic in the target system or application. This has led to a new concept for computing: if a processor can be coupled with one or more FPGA-like devices, it could in theory support a specialised application specific circuit for each program, or even for each stage of a program's

execution. The unlimited reconfigurability of an FPGA permits a continuous sequence of custom circuits to be employed, each optimised for the task of the moment.

There are several accelerators that can be used: examples are GPUs and FPGAs. On one hand, GPUs offer better parallel performance, more efficient computing and an easy to use programming model. On the other hand, FPGAs bring higher performance-perwatt, improved hardware acceleration performance, and lower inter-device latency. Moreover, when used in cloud infrastructures, the advantages introduced by extending these infrastructures with Xilinx FPGAs technologies are even more clear. In this context FPGAs are essentially a systems-on-a-chip coupled with one or more host CPUs via a PCI Express connection. This scenario is basically turning the FPGA into a custom accelerator for the code running on the CPU. This is extremely interesting and convenient because FPGA resources are ready to be used upon purchase and can be elastically scaled.

The huge amount of data they need to process and the complexity of the genomic algorithms, have raised the problem of increasing the amount of computational power needed to perform the computation. In this scenario, hardware accelerators reveal to be efficient in achieving a speed-up in the computation of this algorithms, while at the same time, saving power consumption. Among the algorithms used in genomics, and in the Darwin itself, the Smith-Waterman (SW) algorithm is a dynamic programming algorithm, guaranteed to find the optimal local alignment between two nucleotide strings. Successive FPGA-based hardware acceleration in this algorithm is used to perform pairwise alignment of DNA sequences.

Comparing Intel FPGAs, where the original Darwin is implemented, to Xilinx HPC FPGAs, where the co-processor is implemented in the present work, these last ones are mode widely available since, for instance, they can be used online, available in the cloud, as mentioned before. Some examples of Xilinx FPGA-based cloud infrastructures are Baidu FPGA Cloud Server, the Huawei FPGA Accelerated Cloud Server (FACS), or the Amazon Elastic Compute Cloud (EC2 F1). Implementing Darwin in Xilinx FPGAs instead of Intel FPGAs enables the fact that the co-processor algorithm can be used on multiple architectures, and not only on Intel specific ones. Xilinx FPGAs can deliver the flexibility, application breadth, and feature velocity required by complex and constantly changing application workloads.

## 2. <u>State of the art</u>

#### 2.1. Smith-Waterman Algorithm

Among multiple tasks performed in bioinformatics to analyse DNAs, one of the most compute intensive one is the task of identifying regions of similarity between sequences of DNA, RNA or protein, called sequence alignment. The majority of hardware acceleration efforts for genomic alignment have focused on the Smith-Waterman (SW) and Neeldman-Wunsch (NW) algorithms. These algorithms find exact pair wise alignments and have quadratic complexity in the length of the reads.

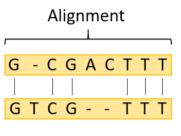

The sequence alignment problem takes a query sequence Q of letters in {A, C, G, T}, corresponding to the four nucleotide bases, and tries to find the best match (alignment) with a reference sequence R, assigning each letter in R and Q to either a single letter in the opposite sequence, or to a gap. The scoring scheme rewards matching bases, and penalises mismatches and gaps. For example:

Score = 9

Figure 5. Sequence alignment scoring scheme example.

The SW algorithm is a dynamic programming (DP) algorithm, guaranteed to find the optimal local alignment between two genome strings or sequences. This algorithm has been firstly introduced in 1981 by Mr Smith and Mr Waterman and it is based on the previously published algorithm called Needleman-Wunsch. The SW algorithm performs local sequence alignment between two strings, usually referred as query, or read, and the reference sequences.

The SW is a DP algorithm as it decomposes a big problem into smaller ones, storing the intermediate results and using them again when solving the next sub-problem.

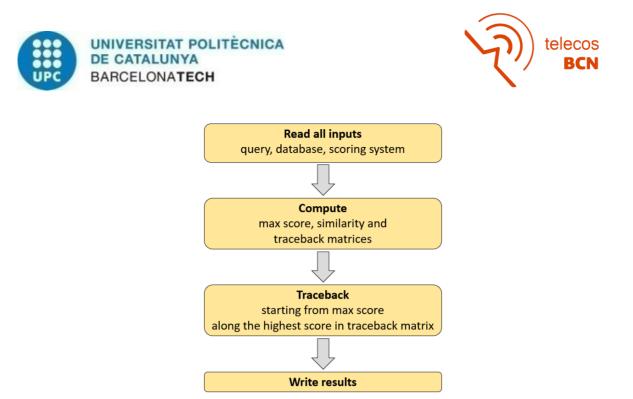

Figure 6. Four macro phases of the Smith-Waterman algorithm.

As figure 6 shows, the SW algorithm can be organised into four macro phases: Read, Compute, Traceback, and Store or Write.

Given a query Q, a reference M, a similarity system and an affine gap function, the algorithm calculates the scoring matrix S and the Traceback Matrix T, whose dimension is QxM each. Finally it traces back the path of elements starting from the index identifying the maximum element in the similarity matrix, and terminating whenever a value with value zero is found. One of the most important features of these algorithms is that it is guaranteed to find the optimal local alignment between the two strings, with respect to the scoring system that is provided as an input.

Because of the high computational needs required by the algorithm, it has been modified during the years and multiple heuristic methodologies have been introduced. These heuristics, on one hand allow to increase the overall performance of the system, but on the other hand decrease the precision of the algorithm, that does not guarantee anymore the optimality of the alignment found.

Furthermore, they may not be able to find similarities for sequences that are very distant. The right trade off in between algorithm precision and system performance has to be found. To avoid the lost in precision, several solutions have been tried over the years to achieve better performance but without loosing in precision. Because of this, in the state of the art it is possible to find multiple implementations of this algorithm using general purpose CPU, and different hardware accelerators such as Graphical Processing Unit and FPGAs.

As seen in figure 6, it is true that the SW algorithm is composed by four phases but, considering that the first one is used to read all the necessary inputs and the last one has the objective of giving back the computed results, it can be basically considered as a 2 phase, or steps, algorithm. The first step can be referred as matrices calculation phase, while the second one as traceback step.

Given a query N, a reference M, a similarity system and an affine gap function, the algorithm calculates the scoring matrix and the traceback matrix, whose dimension is NxM each. Finally, it traces back the path of elements starting from the index identifying the maximum element in the similarity matrix, and terminating whenever a value with

value zero is found. During the calculation of the similarity matrix, it is as well needed to keep track of the index of the maximum element found, as these values are going to be used for the second step of the algorithm. Each element of the similarity matrix is populated by using the relation presented in the following formula.

$$S(i,j) = \begin{cases} S(i-1,j-1) + s(N_i,M_j) & Match/Mismatch\\ \max_{k \le 1} S(i-k,j) + gap_{del} & Deletion\\ \max_{k \le 1} S(i,j-l) + gap_{ins} & Insertion\\ 0 & \end{cases}, 1 \le i \le m, 1 \le j \le n$$

(1)

Where *S* is used to identify the Similarity Matrix, S(i,j) is the *i*, *j* element in the Similarity Matrix,  $S(N_i, M_j)$  represents the similarity function over the two strings  $N_i$  and  $M_j$ ,  $gap_{del}$  is the gap scoring value in case of deletion, and finally  $gap_{ins}$  is the gap scoring value in case of an insertion.

|   | С | G   | Т        | G | G |

|---|---|-----|----------|---|---|

| G | 0 | 2   | 0        | 2 | 2 |

| С | 2 | 2   | 2        | 2 | 2 |

| G | 0 | 3 – | <b>4</b> |   |   |

| Т | 0 |     |          |   |   |

| С | 2 |     |          |   |   |

Figure 7. Smith-Waterman matrix calculation example.

As an example of matrix calculation, in figure 7, for each element of the matrix it is necessary to compute its three dependency values first. These dependency values are the ones highlighted in green in the figure, and are; the value above the current one, or north value, the value on the left of the one considering, or west value, and the value that is positioned in the upper left position, or north-west value.

Once these values are computed, then is possible to compute the current one by performing some basic operations. For all the cell of the matrix where there is not one of the dependency value, as for the first row and first column, the dependency values are supposed to be equal to zero. While computing the similarity matrix as described so far, it is necessary to keep a track of what is the maximum value inside the matrix, and in particular, in the index of this value, so that it can be used in the traceback.

The similarity matrix in fact, is not the only matrix that needs to be computed at this stage. It is also necessary to compute the traceback matrix in parallel to the first one. This second matrix is used to store all the directions that the second step will have to follow so that the final string can be obtained. Figure 8 shows an example of a traceback matrix.

|   | С   | G   | Т   | G   | G   |

|---|-----|-----|-----|-----|-----|

| G | С   | С   |     |     |     |

| С | N_W | Ν   |     |     |     |

| G | С   | N_W |     |     |     |

| Т | N_W | N   | w   | N   | w   |

| С | С   | N   | N_W | w   | Y   |

| С | С   | w   | N   | N_W | N_W |

Figure 8. Smith-Waterman traceback matrix example.

As it can be understood from the formula (1), the similarity store will hold the maximum value between zero and the three dependency values. The first one is a value composed of the sum of the element that lies on the anti-diagonal and another value that depends on the similarity function applied. The second element is the sum of the value on the left of the one considered and the gap value in case of deletion. The third value is composed of the gap value in case of insertion and the element over the one considered.

Once identified the maximum between these three values, the algorithm stores in the traceback matrix the position of the value that originated the identified maximum. In the example of the figure 8, in case of the maximum value is the first one, the program will store in the traceback matrix the value north-west (N\_W), in the second case it will store west (W) and in the third one north (N). In case none of the previous is the maximum, it means that the maximum value is a zero, then the program will store centre (C).

At the end of the first step of the algorithm, two matrices are produced; the similarity matrix and the traceback matrix. After this, the second step of the computation is the traceback. This is the final step and produces the real output, the optimal local alignment between the query and the reference. This step, starts from the maximum index identified before and iteratively passes through the elements in the traceback matrix by following the stored directions. The process continues until a cell where the stored value is centre is encountered. Finally, it outputs how the query sequence aligns to the reference one. The output can be generated or provided by using multiple formats. An output example can be represented by the cigar string, which specifies the length of the bases aligned as well as the associated operation that can be base alignment, both match and mismatch, deletion and insertion of bases.

#### 2.2. <u>Genome alignment heuristics</u>

Other heuristic approximations to the Smith-Waterman algorithm for pairwise alignment of sequences include Banded Smith-Waterman [3], X-drop [4] and Myers bit-vector algorithm [5]. All existing heuristics complete the matrix-fill step before starting traceback, and therefore, having a memory requirement that grows at least linearly with the length of the sequences being aligned.

Banded Smith-Waterman is an algorithm for aligning two sequences within a diagonal band that requires only O(NW) computation time and O(N) space, where N is the length of the shorter of the two sequences and W is the width of the band [3].

The X-drop algorithm [4] avoids the full quadratic cost by searching only for high-quality alignments, and can be viewed as an approach to accelerate both NW and SW. Most applications of alignment will throw out low quality alignments, which arise when the two

strings are not similar. Instead of exploring the whole NxW space, the X-drop algorithm searches only for alignments that results in a limited number of edits between the two sequences. X-drop keeps a running maximum score and does not explore cell neighbourhoods whose score decreases by a user-specified parameter X. It gets its performance benefits from searching a limited space of solutions and stopping early when a good alignment is not possible.

The Myers bit-vector algorithm [5] is a design that finds all spots where a query of length M matches a fragment of a sequence of length N with k-or-fewer variations using simple and practical bit-vector algorithms. By calculating a bit model of the relocatable dynamic programming matrix for the string-matching problem, the Myers approach requires just O(NM/w) time, being *w* the word size of the machine (e.g., 32 or 64). Thus, the algorithm performance is independent of k.

The Darwin co-processor [1], which is the starting point for the current project, and is defined with detail in the following section, uses two novel algorithms, D-SOFT and GACT. The co-processor is based on the classical *seed-and-extend* paradigm. This approach starts with substrings (the *seeds*) of fixed size k drawn from the query sequence (Q), and finds their exact matches in the reference sequence R (called *seed hits*). Once seed hits are found, the cells surrounding the hits are explored, using a dynamic programming approach. This avoids the high cost of exploring the full space. A drawback of the *seed-and-extend* approach is that alignments with no exactly matching substrings of length greater than or equal to k will not be discovered, reducing the algorithm's sensitivity.

In Darwin, the *seeding* step is handled by the D-SOFT algorithm, whereas the *extension* phase is handled by GACT. D-SOFT falls under the group of *seed-and-extend* algorithms, which were popularized by BLAST [6], and subsequent filtration techniques based on measuring the number of seed hits preserved in a band of diagonals. Two-hit BLAST, GraphMap [7], and BLASR [8] are among them.

BLAST [6] is a sequence alignment method that directly approximates alignments that optimize the maximum segment pair (MSP) score, a measure of local similarity. The core approach is straightforward and reliable; it may be implemented in a variety of ways and used in a variety of situations, such as analysing several regions of similarity in long DNA sequences.

GraphMap [7] is a mapping approach for analysing Oxford Nanopore sequencing reads that gradually refines candidate alignments to reliably handle potentially high-error rates and uses a fast graph traversal to match lengthy reads with speed and precision (>95%).

DALIGNER [9] was the first way to directly count the bases in the *seed hits* of a diagonal band, eliminating the need to multiple count overlapping bases in the hits. Darwin's D-SOFT was inspired by this algorithm. DALIGNER is a threaded filter that suggests seed points between pairs of readings that are likely to pass through a significant local alignment. D-SOFT and DALIGNED differ in their implementation. DALIGNER finds overlaps by sorting and merging large pairs of read blocks, which necessitates a large number of random accesses to off-chip memory, whereas D-SOFT performs highly sequential accesses to off-chip DRAM using a seed position table, and random accesses during filtration are handled by fast on-chip memory, making the algorithm better suited to hardware acceleration.

There are filtration approaches that are not focused on counting seeds in a band of diagonals nor the number of bases, such as BWA-MEM [10]. Instead, BWA-MEM, use super maximum seeds.

Other examples include Canu [11], M-HAP [12] and LSH-ALL-PAIRS [13], which are based on probabilistic, locality-sensitive hashing of seeds.

Prior work, like Darwin's, has concentrated on developing a complete sequence alignment framework that includes filtration as well as sequence alignment with very adjustable parameters and hardware acceleration. TimeLogic [14] is one such example. TimeLogic provides FPGA-based framework for BLAST, Smith-Waterman, HMM profile search, and gene finding algorithms, running sophisticated high-throughput and time-consuming comparisons, reducing the computational time of whole human genome to under 20 minutes.

#### 2.3. Darwin co-processor

Darwin employs an extension approach that is the first approximate Smith-Waterman technique with a constant memory demand for the compute-intensive step, allowing for hardware acceleration of arbitrarily long sequence alignments. Furthermore, its alignments are empirically optimal when there is enough overlap.

Darwin is a long read assembly coprocessor based on hardware-software co-design. It makes use of the two innovative algorithms D-SOFT and GACT, which were mentioned earlier. The coprocessor is built on the *seed-and-extend* paradigm, in which D-SOFT does the seeding and GACT does the extension. The methods are built to take advantage of hardware acceleration.

The extension step, which is employed by the GACT technique, is more computeintensive, whereas D-SOFT's purpose is to drastically minimize the search space for it during the alignment of a reference R with a query Q.

#### 2.3.1. D-SOFT Algorithm

D-SOFT starts with *N k*-length substrings (*seeds*) selected from *Q* and finds their exact matches (*seed hits*) in *R*. *R* is pre-processed to create a seed position table, which allows for quick retrieval of seed hits for a given seed. *R* is then divided into  $N_B$  unique bins, each of which is paired with a diagonal band with a slope of 1.

The number of unique bases in *Q* covered by seed hits in each diagonal band is then counted by D-SOFT, and if the count in a given band exceeds *h* bases, the band is chosen for further extension. This procedure is shown in Figure 9 for k = 4, N = 10, h = 8, and  $N_B = 6$ .

There are six bins in all, with bins 1 and 3 having three seed hits each. However, bin 1 only covers six bases in seed hits, but bin 3 covers nine bases, implying a larger likelihood of finding a high-scoring alignment. Only bin 3 is chosen as a candidate bin because the h threshold is set to 8.

Because overlapping bases in seed hits are not tallied multiple times, counting unique bases in a diagonal-band allows the algorithm to be more exact at high sensitivity than strategies that merely count the number of seed hits. D-SOFT's parameters can be tweaked to match the needs of various sequencing technologies.

Figure 9. Illustration of D-SOFT algorithm for k=4, N=10, h=8, NB=6.

## 2.3.2. GACT Algorithm

In the seed-and-extend paradigm, GACT executes the extension step, in which dynamic programming (DP) is employed around the seed hit to assign gaps ("-") to R and Q in order to produce an alignment that optimizes the score. Prior heuristics lower the optimal Smith-Waterman algorithm's space and time complexity from O(mn) to linear O(m+n), where m and n are the lengths of the two sequences to be aligned.

Previous methods required prohibitive traceback pointer storage for hardware implementation, whereas long read sequencing technology requires alignment to two lengthy sequences. The GACT technique is notable for finding arbitrarily lengthy alignment extensions with a constant amount of traceback memory (as opposed to linear or quadratic in earlier algorithms), as illustrated in Figure 10, by following the optimal path among overlapping tiles of a given maximum size.

GACT traceback is a modification of the original Smith-Waterman technique that allows you to combine numerous tile alignments into a single alignment. The tile size *T* and the overlap threshold *O* are the two parameters used. With appropriate values of *T* and *O*, this algorithm produces an optimal result (similar to Smith-Waterman), requiring only  $T^2$ pointers to be held in memory for a tile of size *T*.  $T_{max} = 512$  base-pairs is supported by GACT hardware, which is sufficient to create empirically ideal alignments for lengthy reads. This reduces the storage required for a tile's traceback pointer to just 128 KB, allowing GACT to be massively parallelized on specialized hardware.

**Figure 10.** Illustration of extension stage in GACT algorithm using an example dynamic programming (DP) matrix for parameters (T=4, O=1).

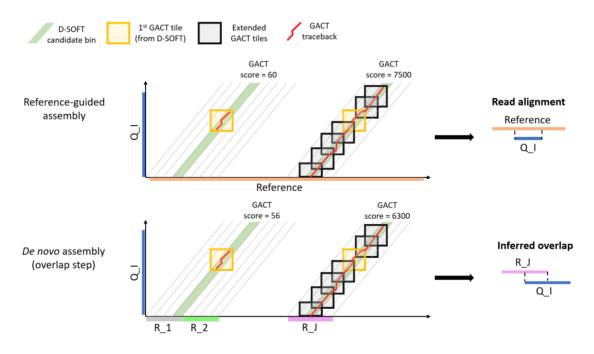

Figure 11 depicts the use of Darwin for reference-guided and *de novo* assembly. The forward and reverse complements of *P* reads in  $S = \{R_1, R_2, ..., R_P\}$  are employed as  $Q_1$  queries into a reference sequence *R* in both circumstances.

In reference-guided assembly, an actual reference sequence is used, but in *de novo* assembly, Darwin speeds up the most compute-intensive overlap phase, which involves applying the  $O(P^2)$  algorithm to discover pairs of overlapping reads. The last-hit position of each candidate bin is supplied to a GACT array, and *N* seeds from each query  $Q_I$  are fed to D-SOFT. The alignment is extended and scored using GACT.

Figure 11. Reference-guided and de novo assembly (overlap step) using D-SOFT and GACT.

#### 2.3.3. Accelerator Design

In the Darwin co-processor, D-SOFT, as explained before, implements the filtration component of the alignment, in particular is used to reduce the search space for the more

compute-intensive dynamic programming step. Whereas GACT is an algorithm which uses constant time and space O(1) for the most compute-intensive step that it has, in order to do arbitrary long alignments using dynamic programming, and it is heuristic to the Smith-Waterman algorithm.

Darwin's sources of acceleration can be summed up in hardware-software codesign, specialized operations, parallelism (outer and inner loop), usage of local memories, optimized memory accesses and reduced overhead.

The first step to accelerate the alignment phase is to implement specialized operations, accelerating the Smith-Waterman algorithm, computing a dynamic programming matrix between a reference and a query sequence, using the following equations.

$$I(i,j) = max \begin{cases} H(i,j-1) + gap\_open\\ I(i,j-1) + gap\_ext \end{cases}$$

(2)

$$D(i,j) = max \begin{cases} H(i-1,j) + gap\_open\\ D(i-1,j) + gap\_ext \end{cases}$$

(3)

$$H(i,j) = max \begin{cases} 0 \\ I(i,j) \\ D(i,j) \\ H(i-1,j-1) + W(r_i,q_j) \end{cases}$$

(4)

For insertions (*I*) and deletions (*D*), equations 2 and 3 compute the affine gap penalty. Equation 4 calculates the cell's overall score. For each cell, a four-bit traceback pointer is computed: one bit for equations 2 and 3 to indicate whether the insertion (deletion) score was obtained by opening or extending a gap, and two bits for equation 4 to indicate whether the final score was reached by null (terminating), horizontal, vertical, or diagonal cell.

Computing these equations in a CPU, they have 35 arithmetic instructions plus 15 load/store operations, and they will take 37 clock cycles because of the dependencies. However, using a specialized unit (Processing Element – PE), these operations can be done in one single cycle.

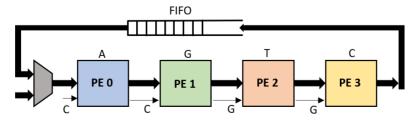

Darwin's accelerator exploits parallelism, making use of systolic array of these processing elements to exploit the wave-front parallelism that is available in the Smith-Waterman equations, having 64 PEs per array. Each PE maintains the maximum score and corresponding position for the cells it has computed. The communication is very simple, one-way nearest neighbour.

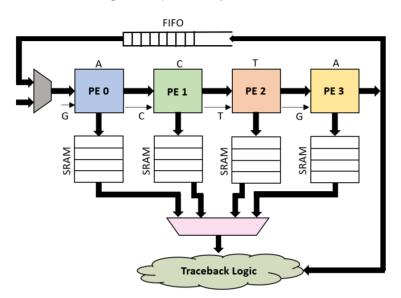

Figure 12. Darwin's systolic array architecture.

The *H* and *D* scores of equations 3 and 4 of the last PE of the array are stored in a FIFO, as shown in figure 12, and are consumed by the first PE during the computation of the next query block. The depth of this FIFO is  $T_{max}$ , which corresponds to the DP-matrix's maximum number of columns.

It is also needed to store some traceback state for each of these tiles, and so each processing element is connected to each unique bank of SRAM, which is only 2KB in size, as shown in figure 13. In this way, accessing local memories is orders of magnitude cheaper compared to accessing off-chip memory.

Figure 13. Darwin's systolic array architecture with traceback storage.

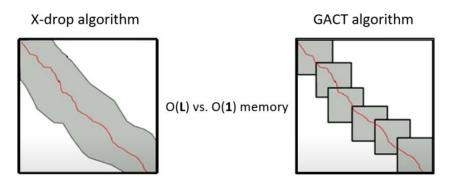

GACT is a classic example where co-design is used to enable local memory. Comparing the X-drop algorithm [4], which is used in BLAST [6], this would require order of length of the aligning sequences to be stored in the memory, and as a result accessing off-chip memory would be required. In GACT, by means of changing the co-design algorithm and doing the computation as a series of overlapping tiles, it is only needed to store the memory for a single tile, which is constant. Figure 14 shows the differences between the X-drop algorithm [4] and the GACT algorithm [1], the first one requiring O(L) space in the memory, while the second one using constant space O(1) to be stored.

Figure 14. Comparison between the X-drop algorithm and the GACT algorithm.

Darwin also exploits outer-loop parallelism, replicating a lot of the arrays of figure 12, using 64 independent arrays, each array having 64 PEs.

Figure 15. Darwin's outer-loop parallelism.

Increasing outer-loop parallelism results in the need of more storing states, which is what Darwin stores per tile, for that, the co-processor has a good balance between how much of outer-loop parallelism and inner-loop parallelism is exploited.

## 2.4. <u>Hardware Acceleration</u>

This project has been developed making use of the Xilinx Vitis development environment, implementing it on the Alveo u280 board. Genomic applications are ideally suited to be implemented on a system where they can gain advantages by being accelerated because of the presence of an FPGA, exploiting massive parallelism and deep pipe aligning. The Alveo cards consist of a host CPU coupled with Xilinx FPGA. In particular, the Alveo u280 instance is using Xilinx UltraScale+ XCU280-L2FSVH2892E. The Alveo u280 counts with 32-pseudo channels of High Bandwidth Memory (HBM), offering a total of 8 GB of HBM, at 460 GB/s, providing high-performance and adaptable acceleration for memory bound, compute-intensive applications, as is genomic alignment in Darwin.

With these specifications this card allows for massive IOs transfer and massive parallelism, and obviously because of the fact that it inherits all the benefits of being an FPGA device, it is ideal for accelerating compute intensive applications.

Alveo cards consist of a host CPU augmented with Xilinx FPGAs, and their acceleration works by moving compute intensive and deeply pipeline parts of application under execution to the FPGA, where customized implementation of hardware accelerator can be added to provide the needed performance boost. The Alveo instances are not providing only FPGA devices, therefore, the rest of the remaining part of the application will be executed on the x86 CPU.

Figure 16. Host CPU augmented with Xilinx FPGAs in Alveo Cards.

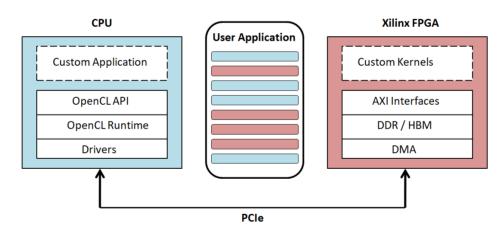

As figure 17 shows, on the left side there is the software stack running on the x86 CPU (host). As seen, on the host CPU the custom application interacts with the FPGA by using the OpenCL API, and the OpenCL Runtime is responsible for managing and servicing the various acceleration requests sent to the FPGA.

The same thing can be done with the FPGA. Therefore, on the right side of figure 17, the red box represents the hardware components that are implemented on the FPGA. The communication infrastructure between the CPU and the FPGA is carried over the PCI Express interface. Within this context at the very lowest level, the drivers handle the PCI transfer between the two devices. Once the DDR or HBM memory is loaded with the necessary data, the customer isolation kernels can then read it, process the data, and write it back to the DDR or HBM using standard AXI interfaces.

Figure 17. Software stack (left) and hardware components (right) communication through PCIe.

As it can be seen in the figure 17, the host code and the hardware kernels are provided by the developer of the accelerated application. Within this context, by using standard OpenCL and AXI interfaces, Alveo hides the complexity involved in building a platform based on an heterogeneous hardware architecture, and it lets the developers to focus on what matters most to them, getting the best in terms of performance out of their application. The application developer is not only designing the FPGA accelerated IPs but also creating customer code to be executed on the x86. The application execution stack is based on OpenCL, which is following a master-slave model which clearly separates the application code from the kernel logic. The host application submits work to FPGA kernels using standard OpenCL API, and the OpenCL runtime and drivers enable the communication between the host and the FPGA. The rationality behind the choice of

using OpenCL within the Alveo context is quite strong and it can be summarized in the following. OpenCL is being designed to be platform independent, which makes the code portable across CPUs, GPUs, and obviously FPGAs, which is again a huge opportunity when working within heterogeneous architecture. OpenCL is widely used, well-documented, and supported, and by using it, it is possible to dynamically wrap and load different kernels. The OpenCL runtime manages all of the communication between the host and the device, and takes away all the burden of the complexity of optimizing parallel computing application, delivering fast time to results.

To sum up, each Alveo u280 card includes three key components: a powerful FPGA for acceleration, high-bandwidth HBM2 memory banks, and high-bandwidth PCIe Gen3x16 connectivity to a host server. Between the Alveo card and the host, this link can transport around 16 gigabytes of data per second.

Alveo designs are split into a *shell and role* conceptual model to ensure that the PCle link, system monitoring, and board health interfaces are always available to the host processor. External links, settings, timing, and other static functionality are all contained in the shell. The model's role component is filled with bespoke logic that implements the user's customized algorithms. This topology is reflected in figure 18.

Figure 18. Alveo card shell and role topology.

Multiple super logic regions (SLRs) are separated into the Alveo FPGA, which aid in the building of very high-performance systems. Only the Alveo u280 has HBM memory banks, and the cards have several on-card DDR4 memories. These memories, which have a high bandwidth to and from the Alveo device, are collectively referred to as the *device global memory* in OpenCL. Each DDR4 memory bank has a 16-gigabyte capacity and runs at 2400 MHz DDR. This RAM has a lot of bandwidth, and modified kernels can easily saturate it if they want to. However, reading from or writing to this memory incurs a latency penalty, especially if the addresses accessed are not contiguous or the data beats are short.

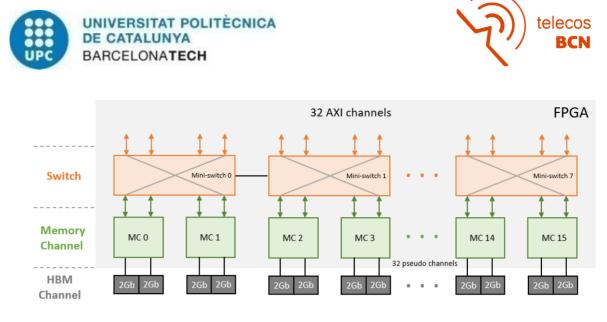

4 GB HBM stacks are included in Alveo U280 High Bandwidth Memory (HBM) devices. The programmable logic connects with the HBM stacks via memory controllers using stacked silicon interconnect technology. The U280 has access to two 4 GB HBM stacks, each with 16 pseudo channels and direct 256 MB access. Below, there is a high-level

diagram of the two HBM stacks. There are 32 HBM AXI interfaces on the programmable logic. Through a built-in switch, HBM AXI interfaces can access any memory address in any of the 32 HBM PCs on any of the HBM stacks, giving them access to the entire 8 GB memory space. The programmable logic and HBM stacks' flexible connectivity allows for easy floorplanning and timing closure, as well as kernel implementation flexibility.

Figure 19. High-Level Diagram of Two HBM Stacks. [2]

# 3. <u>Methodology</u>

This section explains in detail the development of the project, the AXI interface design, as well as the connections between the interface and the Darwin co-processor, and its implementation making use of the High Bandwidth Memory Banks of the Alveo U280 FPGA.

## 3.1. AXI Interface

The Advanced eXtensible Interface (AXI) is a parallel high-performance, synchronous, high-frequency, multi-master, multi-slave communication interface primarily developed for on-chip communication.

With the AMBA3 specification, AXI was first presented in 2003. The AXI4, AXI4-Lite, and AXI4-Stream protocols were defined in 2010 by AMBA4, a new iteration of AMBA. Separate address/control and data phases, support for unaligned data accesses, burst-based transfers, separate and independent read and write channels, support for pending transactions, and more are all available with AXI.

AMBA AXI provides several optional signals that can be incorporated or excluded according on the design's individual requirements, making AXI an adaptable bus for a variety of applications.

While communication on an AXI bus is limited to a single master and slave, the specification includes precise descriptions and signals that allow the bus to be extended to topologies with multiple masters and slaves.

AXI defines a basic handshake mechanism consisting of two signals: xVALID and xREADY. The source sends the xVALID signal to the destination entity to alert it that the payload on the channel is valid and can be read from that clock cycle forward. Similarly, the receiving entity sends the xREADY signal to indicate that it is ready to accept data.

The data payload is deemed "transferred" when both the xVALID and xREADY signals are high in the same clock cycle, and the source can either send a fresh data payload by keeping xVALID high or stop the transmission by de-asserting xVALID. A single data transfer, such as a clock cycle in which both xVALID and xREADY are high, is referred to as a "beat."

For the control of these signals, there are two fundamental rules:

- A source must not assert xVALID until xREADY is high.

- A source must maintain a high xVALID until a handshake happens once claimed.

Both the source and the destination can regulate the flow of data using this handshake method, limiting the speed if necessary.

Figure 20. Basic handshake mechanism of the AXI protocol.

The destination entity in the example transaction shown in figure 20 waits for a high VALID before asserting its own READY.

Five channels are mentioned in the AXI specification:

- Read Address channel (AR)

- Read Data channel (R)

- Write Address channel (AW)

- Write Data channel (W)

- Write Response channel (B)

Aside from some basic ordering rules, each channel is self-contained, with its own set of xVALID/xREADY handshake signals.

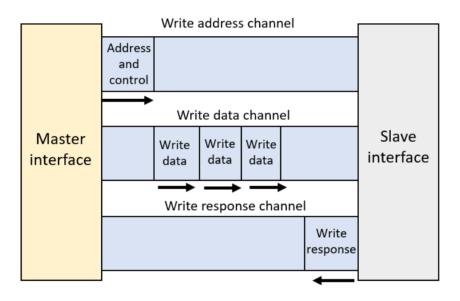

Figure 21. AXI Read Address and Read Data channels.

Figure 22. AXI Write Address, Write Data and Write Response channels.

AXI is a burst-based protocol, which means that a single request may result in numerous data transfers (or beats). This makes it handy in situations when a significant volume of data must be transferred from or to a specified pattern of addresses. The three types of bursts in AXI are FIXED, INCR, and WRAP, which are selectable by the signals ARBUSRTS (for reads) or AWBURST (for writes). Each beat inside the transmission has the same address in FIXED bursts. INCR bursts, on the other hand, have an address equal to the previous one plus the transfer size for each beat. WRAP bursts are similar to INCR bursts in that each transfer has an address equal to the previous one plus the "Wrap boundary" if it crosses the "Higher Address boundary."

#### 3.1.1. AXI Transactions

#### Reads

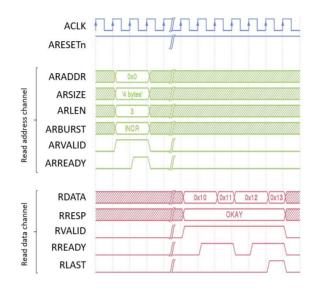

To initiate a read transaction, the master must give the start address on ARADDR, the burst type, either FIXED, INCR, or WRAP, on ARBUST (if present), and the burst duration on ARLEN on the Read address channel (if present).

If other auxiliary signals are provided, they are also utilized to define more particular transfers. The slave must send the data corresponding to the specified address(es) on RDATA and the status of each beat on RRESP, plus any additional optional signals, over the Read data channel after the standard ARVALID/ARREADY handshake.

Each beat of the slave response is signalled by an RVALID/RREADY handshake, and the slave must assert RLAST on the last transfer to indicate that no more beats will be sent without a new read request.

Figure 23. AXI Read transaction example.

Figure 23 shows how the master requests four beats (ARLEN+1) of four bytes each, starting at address 0x0, with INCR type. The slave returns 0x10 for address 0x0, 0x11 for address 0x4, 0x12 for address 0x8, and 0x13 for address 0xC. The figure only shows the most important signals.

#### Writes

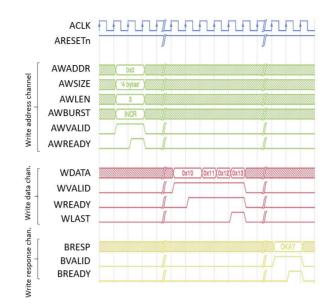

To begin a write operation, the master must give both address and data information.

The start address must be provided on AWADDR, the burst type, either FIXED, INCR, or WRAP, on AWBURST (if present), the burst length on AWLEN (if present), and all the optional signals must be provided on the Write address channel, in a similar manner to a read operation.

A master must also send data on the Write data channel related to the given address(es); data on WDATA and the "strobe" bits on WSTRB, which conditionally label particular WDATA bytes as "valid" or "invalid."

The master must assert WLAST on the last data word, just like in the read path. After both transactions are complete, the slave must report the status of the write to the master over the Write response channel, returning the result via the BRESP signal.

Figure 24. AXI Write transaction example.

In the example of figure 24, the master writes 0x10 for address 0x0, 0x11 for address 0x4, 0x12 for address 0x8, and 0x13 for address 0xC in four beats (AWLEN+1) each starting from address 0x0 with INCR type. For the entire transaction, the slave returns 'OKAY' as a write response. The figure only shows the most important signals.

#### 3.1.2. AXI4-Lite

AXI4-Lite is a subset of the AXI4 protocol that offers a register-like structure with fewer features and a lower level of complexity. The fact that all bursts are composed of only one beat and that all data accesses use the full data bus width, which can be either 32 or 64 bits, are notable contrasts.

AXI4-Lite omits several AXI4 signals while adhering to the AXI4 specification for the rest. Its transactions are fully compatible with AXI4 devices since they are a subset of AXI4, allowing for interoperability between AXI4-Lite masters and AXI4 slaves without the need for additional conversion logic.

#### 3.1.3. AXI interface implementation

The GACT array accelerators handle the compute-intensive *align* routine in GACT, with the rest of the algorithm implemented in software. The arrays are originally implemented on an Intel FPGA. In this work, they have been implemented using the Alveo Card U280, exploiting HBM to increase its performance.

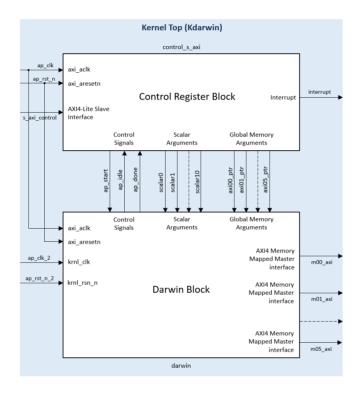

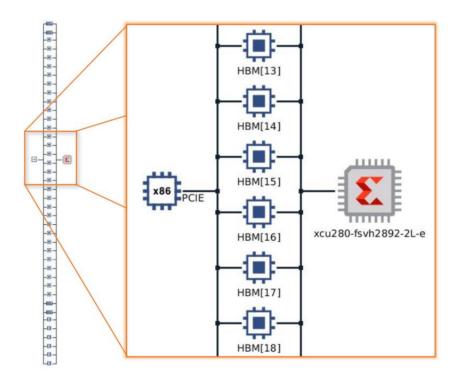

The kernel has been written in RTL, and the communication between the host and the kernel occurs across an AXI bus. The main data processed by the kernel, which is in a large volume, is transferred through the global memory banks on the FPGA board, making use of 6 HBM banks. The kernel accesses the data from those global memory banks, in burst, and after it finishes the computation, the resulting data is transferred back to the host machine through the HBM memory banks.

The AXI4 master interfaces for global memory access are a total of six, which all have 64-bit addresses, which are the query sequence and the reference sequences with their respective addresses, and the direction read address. Each partition in the global

memory becomes a kernel argument, and the memory offset for each partition is set by a control register programmed via the AXI4-Lite slave interface.

With respect to the scalar arguments, which are directly written to the kernel through the AXI4-Lite slave interface, there are a total of 11, which are the input register for the Darwin GACT logic. These inputs are control variables directly loaded from the host machine and they do not use global memory banks.

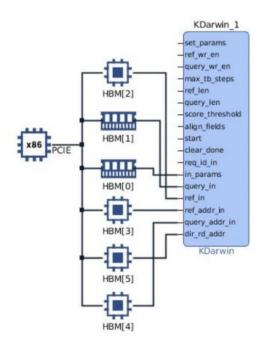

The RTL Darwin kernel consists of a top-level Verilog design which contains a control register and the Darwin sub-modules with a read and write module for each AXI4 master. The following figure illustrates the top-level design configured with six AXI4-master interfaces.

Figure 25. Top-level Darwin kernel structure.

The Darwin block, shown in the following figure, consists of the GACT Darwin logic, six AXI4 read masters, and six AXI4 write masters. Each master reads 16 KB of data, performs the necessary operations in the Darwin logic block, and then writes out the Darwin outputs back in place. Each master AXI uses a different HBM memory bank, from HBM[0] to HBM[5].

Figure 26. Darwin kernel RTL block structure.

The design environment used for this project has been Vivado Design Suite and Vitis Unified Software Platform, and the HDL design has been written down in Verilog and SystemVerilog.

Vivado Design Suite is a software suite for synthesis and analysis of HDL designs, produced by Xilinx, which replaces Xilinx ISE and adds functionality for system on a chip development and high-level synthesis. Vivado is a complete rewriting and rethinking of the entire design process (compared to ISE). ISIM, an in-built logic simulator, is included.

On heterogeneous Xilinx platforms such as FPGAs, SoCs, and Versal ACAPs, the Vitis Unified Software Platform facilitates the development of embedded software and accelerated applications. It offers a single programming model for Edge, Cloud, and Hybrid computing applications.

External memory interfaces, custom input/output interfaces, and software runtime are all part of the Vitis target platform, which provides the fundamental hardware and software architecture as well as the application context for Xilinx platforms.

The Vitis target platform automatically configures the PCIe interfaces that connect and manage communication between the FPGA accelerators and the x86 Application code for Xilinx accelerator cards on-premise or in the cloud.

In the current project, the interfaces of the original Darwin co-processor have been adapted to the Xilinx boards, specifically for the Alveo U280 Accelerator Card, in order to make use of the High Bandwidth Memory banks (HBM), since it is a much faster RAM, and the fact that the original Darwin co-processor was memory bound can be exploited.

The following table shows the type of AXI interface for each GACT input of the Darwin coprocessor.

Table 2. AXI configurations used for each GACT input in the RTL kernel.

| Darwin inputs   | AXI configurations |

|-----------------|--------------------|

| in_params       | AXI master         |

| set_params      | AXI-Lite           |

| query_in        | AXI master         |

| ref_in          | AXI master         |

| ref_addr_in     | AXI master         |

| query_addr_in   | AXI master         |

| ref_wr_en       | AXI-Lite           |

| query_wr_en     | AXI-Lite           |

| max_tb_steps    | AXI-Lite           |

| ref_len         | AXI-Lite           |

| query_len       | AXI-Lite           |

| score_threshold | AXI-Lite           |

| align_fields    | AXI-Lite           |

| start           | AXI-Lite           |

| clear_done      | AXI-Lite           |

| dir_rd_addr     | AXI master         |

| req_id_in       | AXI-Lite           |

#### 3.2. Block Design

The RTL Kernel has been created using the Vitis RTL Kernel wizard. This allows RTL code to be used in a Vitis design. The kernel has been written in Verilog and SystemVerilog. The project has been developed using Vivado Design Suite. After the simulation verification of the design, the generated Vivado project has been packed into an xo kernel file.

The eleven scalar kernel input arguments (AXI-Lite configuration) are all *uint* type (32 bit long), and the six arguments passed through Global Memory are of width 64 bytes, or which is the same, 512 bits.

-1

The function prototype and register map for the kernel are shown in the following figure. Note that the control register and the scalar operands are accessed via the S AXI CONTROL interface. The control register is at offset 0x0 and the scalar operands start at offset 0x10.

| VLNV:               | xilinx.com:kernel:KDarwin:1.0 |

|---------------------|-------------------------------|

| Target<br>platform: | xilinx:u280:xdma:201920.3     |

Function

void KDarwin( const uint set\_params, const uint ref\_wr\_en, const uint query\_wr\_en,

prototype:

const uint max\_tb\_steps, const uint ref\_len, const uint query\_len, const uint score\_threshold, const uint align\_fields, const uint start, const uint clear\_done, const

uint req\_id\_in, global void \*in\_params, global void \*query\_in, global void \*ref\_in, global void \*ref\_addr\_in, global void \*query\_addr\_in, global void \*dir\_rd\_addr);

Regist n

| ID  | Name            | Offset | Type (bits)          | Interface     |

|-----|-----------------|--------|----------------------|---------------|

| N/A | Control         | 0x000  | N/A                  | S AXI CONTROL |

| 0   | set_params      | 0x010  | uint (32)            | S_AXI_CONTROL |