# Virtualization extension to a RISC-V processor

Author: Gerard van den Berg Project Director: Juan Jose Costa Prats Departament d'Arquitectura de Computadors Grau en Enginyeria Informàtica - Enginyeria de Computadors Facultat d'Informàtica de Barcelona Universitat Politècnica de Catalunya – April 2021

#### Abstract

This work consist on implementing the hypervisor specification of the RISC-V ISA on an already existing CPU. This includes adding new registers to the CPU, including virtual ones, modifying the interrupt and exception management, implementing new instructions and designing a Two Step Address translation mechanism. The objective of this report is to document the process, and to serve as reference to others wanting to implement it.

#### **Resumen:**

Este trabajo consiste en implementar la especificación del hypervisor de la ISA RISC-V en una CPU ya existente. Esto incluye la adición de nuevos registros a la CPU, incluidos los virtuales, la modificación de la gestión de interrupciones y excepciones, la implementación de nuevas instrucciones y el diseño de un mecanismo de traducción de direcciones en dos pasos. El objetivo de este informe es documentar el proceso y servir de referencia a otros que quieran implementarlo.

#### Resum:

Aquest treball consisteix a implementar l'especificació de l'hypervisor de la ISA RISC-V en una CPU ja existent. Això inclou l'addició de nous registres a la CPU, inclosos els virtuals, la modificació de la gestió d'interrupcions i excepcions, la implementació de noves instruccions i el disseny d'un mecanisme de traducció d'adreces en dos passos. L'objectiu d'aquest informe és documentar el procés i servir de referència a altres que vulguin implementar-lo.

# **1** Acknowledgements:

First of all, I would like to extend my sincerest thanks to Juan for giving me support and guidance during the full duration of the project.

I would also like to thanks my parents, for their unwavering faith in me, and their confidence that I would be able to pull through.

Also thanks to Max Doblas, from the BSC, without whom I would have been completely unable to undertand the Lagarto Source code and to the support of the Catalan government through the project RIS3CAT DRAC number 001-P-001723.

Finally I would like to thank my friend David, for being by my side for all these years,

# Contents

| 1        | Ack  | nowledgements:                                                                        | 3  |

|----------|------|---------------------------------------------------------------------------------------|----|

| <b>2</b> | Intr | oduction                                                                              | 9  |

|          | 2.1  | Context                                                                               | 9  |

|          | 2.2  | Motivation                                                                            | 10 |

|          | 2.3  | Stakeholders                                                                          | 10 |

|          | 2.4  | Justification:                                                                        | 11 |

| 3        | Pro  | ject Planing                                                                          | 12 |

| 4        | Sco  | pe and Obstacles                                                                      | 12 |

|          | 4.1  | Reach: objectives and subojectives                                                    | 12 |

|          | 4.2  | Risks                                                                                 | 13 |

|          |      | 4.2.1 Implementation issues $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 13 |

|          |      | 4.2.2 Lack of technical knowledge:                                                    | 13 |

|          |      | 4.2.3 Excessive Design Scope:                                                         | 13 |

| <b>5</b> | Met  | bodology and Rigor                                                                    | 13 |

|          | 5.1  | Methodology                                                                           | 14 |

|          | 5.2  | Monitoring tools                                                                      | 14 |

| 6        | Tasl | k Description                                                                         | 15 |

|          | 6.1  | Project Management:                                                                   | 15 |

|          |      | 6.1.1 Scope                                                                           | 15 |

|          |      | 6.1.2 Planning                                                                        | 15 |

|          |      | 6.1.3 Cost and Sustainability                                                         | 15 |

|          |      | 6.1.4 Documentation                                                                   | 15 |

|          | 6.2  | Agile                                                                                 | 16 |

|          |      | 6.2.1 General Planning                                                                | 16 |

|          |      | 6.2.2 Sprint Planning                                                                 | 16 |

|                                      | 6.2.3 QA Reunion and Control Reunion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16                                                                                                         |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 6.                                   | 3 Spec Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16                                                                                                         |

|                                      | 6.3.1 Reading The Privileged Spec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16                                                                                                         |

|                                      | 6.3.2 Reading Additional Specs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17                                                                                                         |

| 6.                                   | 4 Target System Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                                                                         |

| 6.                                   | 5 Setting up Development Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17                                                                                                         |

| 6.                                   | 6 Designing the solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                                                                                                         |

| 6.                                   | 7 Implementing the solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 17                                                                                                         |

| 6.                                   | 8 Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18                                                                                                         |

| 6.                                   | 9 Final WriteUp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18                                                                                                         |

| 7 G                                  | antt graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18                                                                                                         |

| 8 R                                  | isk Management:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19                                                                                                         |

| 9 B                                  | udget                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20                                                                                                         |

| 9.                                   | 1 Human Cost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                                                                         |

| 9.                                   | 2 Generic Cost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21                                                                                                         |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                            |

|                                      | 9.2.1 Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21                                                                                                         |

|                                      | 9.2.1Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21<br>22                                                                                                   |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                            |

| 9.                                   | 9.2.2       Non Amortizable costs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22                                                                                                         |

| 9.<br>9.                             | 9.2.2       Non Amortizable costs       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .< | 22<br>22                                                                                                   |

| -                                    | 9.2.2       Non Amortizable costs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22<br>22<br>23                                                                                             |

| 9.                                   | 9.2.2       Non Amortizable costs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22<br>22<br>23<br>23                                                                                       |

| 9.<br>9.<br>9.                       | 9.2.2       Non Amortizable costs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22<br>22<br>23<br>23<br>23                                                                                 |

| 9.<br>9.<br>9.<br>10 St              | 9.2.2       Non Amortizable costs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>22</li> <li>22</li> <li>23</li> <li>23</li> <li>23</li> <li>23</li> </ul>                         |

| 9.<br>9.<br>9.<br><b>10 St</b><br>10 | 9.2.2       Non Amortizable costs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>22</li> <li>22</li> <li>23</li> <li>23</li> <li>23</li> <li>23</li> <li>24</li> </ul>             |

| 9.<br>9.<br>9.<br><b>10 Su</b><br>10 | 9.2.2       Non Amortizable costs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>22</li> <li>22</li> <li>23</li> <li>23</li> <li>23</li> <li>23</li> <li>24</li> <li>24</li> </ul> |

| 1 | 1 | The | RISCV |

|---|---|-----|-------|

|   |   |     |       |

| 12 RISC-V Privileged Instruction Set - Standard Extension for                                                       | •  |

|---------------------------------------------------------------------------------------------------------------------|----|

| Hypervisor                                                                                                          | 28 |

| 12.1 Trap Handling                                                                                                  | 28 |

| 12.2 Two-Stage Address Translation                                                                                  | 28 |

| 12.3 Registers                                                                                                      | 29 |

| 12.4 New instructions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$              | 30 |

| 12.4.1 Virtual-machine load and store                                                                               | 30 |

| 12.4.2 Fences                                                                                                       | 30 |

| 13 Choosing the right implementation.                                                                               | 30 |

|                                                                                                                     |    |

| 14 The Development environment                                                                                      | 31 |

| 14.1 Chisel                                                                                                         | 31 |

| 14.2 SystemVerilog                                                                                                  | 31 |

| 14.3 GNU toolchain                                                                                                  | 31 |

| 14.4 Testing software                                                                                               | 32 |

| 15 Lagarto Lowrisc                                                                                                  | 32 |

| 16 Implementing Hypervisor mode                                                                                     | 33 |

| 16.1 New CSRs                                                                                                       | 33 |

| 16.1.1 Reading and Writing to CSRs                                                                                  | 39 |

| 16.1.2 Testing $\ldots$                                                                                             | 41 |

| 16.1.3 Modifying existing CSRs                                                                                      | 42 |

| 16.2 Trap Handling                                                                                                  | 43 |

| 16.3 Two Step translation $\ldots$ | 43 |

| 16.4 New Instructions                                                                                               | 44 |

| 16.4.1 Hypervisor Load and Store Instructions                                                                       | 44 |

| 17 Deviation from initial planning         | <b>45</b> |

|--------------------------------------------|-----------|

| 17.1 Project Management:                   | 45        |

| 17.2 Spec analysis                         | 45        |

| 17.3 Choosing the Target System            | 45        |

| 17.4 Development environment               | 45        |

| 17.5 Designing the Solution                | 46        |

| 17.6 Implementing and Testing the solution | 46        |

| 17.7 Final Write up                        | 46        |

| 17.8 Final Cost of the Project             | 46        |

| 18 Conclusion and future work              | 48        |

| 19 Bibliography                            | <b>49</b> |

# List of Figures

| 1  | Gantt summary                                                       | 18 |

|----|---------------------------------------------------------------------|----|

| 2  | Gantt Graph                                                         | 19 |

| 3  | Role Salary/h                                                       | 20 |

| 4  | Task Human cost                                                     | 21 |

| 5  | Resource cost                                                       | 22 |

| 6  | Total generic costs                                                 | 22 |

| 7  | Total Budget                                                        | 23 |

| 8  | sustainability matrix                                               | 24 |

| 9  | Hypervisor specific registers                                       | 29 |

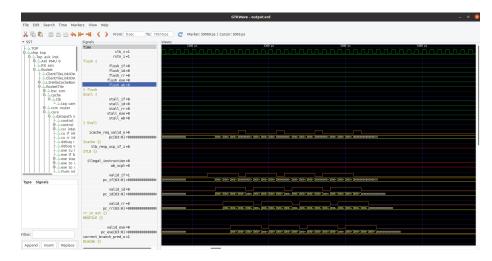

| 10 | Gtkwave loading the results of a test                               | 32 |

| 11 | CSR declarations                                                    | 34 |

| 12 | Hstatus type declaration                                            | 35 |

| 13 | Virtual CSR                                                         | 36 |

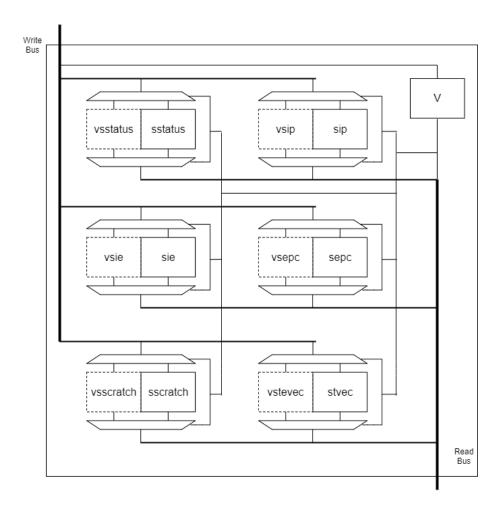

| 14 | Using Multiplexers to access the virtual registers                  | 37 |

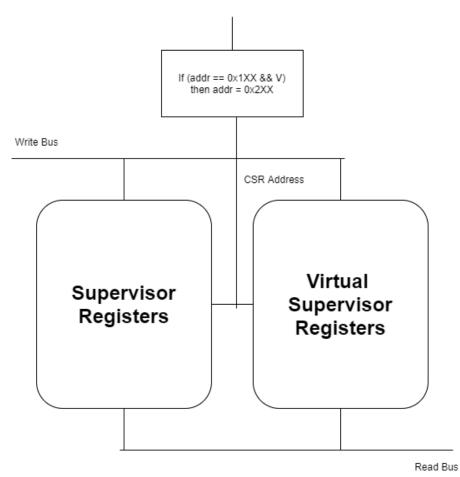

| 15 | Address altering approach                                           | 38 |

| 16 | Code used to change the address while reading or writing a register | 39 |

| 17 | Read switch case snippet                                            | 40 |

| 18 | Intercepting writes                                                 | 41 |

| 19 | Simple Test for the new Virtual Registers                           | 42 |

| 20 | Reference of CSRs to modify                                         | 42 |

| 21 | Trap handling functionality                                         | 43 |

| 22 | Reference of CSRs accessed by the Hypervisor Load/Store in-         |    |

|    | structions                                                          | 44 |

| 23 | Human cost table                                                    | 47 |

# 2 Introduction

The objective of this Project is to implement the Hypervisor Extension in an existing RISC-V implementation, in this chapter, we're going to explain the context of the project as well as its motivation and implied parties.

## 2.1 Context

Virtualization, as a term, appeared in the 1960s and at the time it was used to refer to the concept of dividing a mainframe resources between different applications, however, nowadays it refers to creating a virtual machine, a software that emulates a real computer with its own operative system.

These virtual machines offer numerous advantages over their bare metal counterparts, such as being easy to deploy on different under different hardware configurations, and allowing a single machine to run many virtual machines. Enterprises like Amazon Web Services, use virtualization extensively[1].

However virtualization itself can be quite slow if managed entirely via software, this is why most commercial CPU's offer hardware support to accelerate virtualization, this is done implementing a Hardware level Hypervisor.

An Hypervisor allows a computer system to run multiple guest virtual machines inside one Host system, there exist 2 types of hypervisors:

- Type-1 hypervisors run directly on the host machine hardware, and are often referred as bare metal hypervisors,

- Type-2 hypervisors run like a conventional program inside of the host operative system, for the purposes of this project, we will focus exclusively in the first type.

For this project we will use the RISC-V architecture, because that it is the most well known example of of free and open source hardware. The RISC-V architecture was first developed at the University of Berkeley, California in 2010 [2]. aiming to create a Free and extensible ISA improved by global collaboration, this contrasts with others such as Intel or ARM which have closed sourced ISAs.

# 2.2 Motivation

The main motivator for this project is the technical challenge and the personal growth opportunity it presents, The skills and knowledge the author will acquire in the fields of specification and implementation of hardware, the RISC-V architecture, as well as virtualization as a whole are of great interest.

Another reason resides in the university context. Being able to understand a specification and build a working implementation based on that makes use of many skills learnt in the Computer Engineering specialization, and the degree as a whole.

Furthermore, this projects documentation could benefit future developers and researchers that aimed to implement a hypervisor in their own RISC-V implementation, as well as a general introduction to RISC-V itself for all kinds of research and development.

# 2.3 Stakeholders

The development of this project will involve different people, some of those will be detailed:

- **Project author:** I, will be in charge to design, implement and testing the hypervisor, as well as documenting the whole process.

- Future Hypervisor implementer: The aim of this project is also to act as a reference document for anyone that wanted to implement the RISC-V hypervisor in the future.

- Barcelona Super Computing Center: Given the fact that the *Lagarto* is one of the possible RISC-V implementations to be chosen for this

project, their assistance may be needed, furthermore, a successful Hypervisor implementation could be useful in future endeavors.

• **Project Director:** This projects director will be supervising the development of the project, as well as provide aid when necessary.

# 2.4 Justification:

At the time of writing, an open source Type-1 Hypervisor hasn't been implemented yet, while it is true that many commercial CPUs implement such an hypervisor, I think that there is value in an hypervisor which implementation is completely transparent and auditable by any third party.

Being the spec itself not final, a working implementation would also be suitable to evaluate the specification itself

# 3 Project Planing

In this chapter, we'll go over the different aspects of the project, such as its scope, The methodology used, the expected risks, its planned budget, and sustainability concerns.

# 4 Scope and Obstacles

This section will explain the objectives of this project, as well as some possible obstacles and pitfalls to surpass or avoid.

## 4.1 Reach: objectives and subojectives

The main objective of this project is the implementation of the RISC-V Hypervisor Specification on an existing RISC-V Implementation, this has yet to be done, as of the start of this project the specification is not final, and the target processor is yet to be chosen, finally it is also my objective to document exactly what is needed to implement the hypervisor for future reference. All in all the objectives needed to complete the project are the following:

- Study the Hypervisor specification.

- List requirements for the target implementation.

- Choose an initial RISC-V implementation.

- Study the implementation.

- Design the Hypervisor implementation.

- Implement the design and tests.

- Document the process.

### 4.2 Risks

During the project development, different obstacles may occur that could hinder the process, I will proceed to detail them and possible solutions.

#### 4.2.1 Implementation issues

It is necessary to consider the possibility that the current state of the chosen processor implementation has insufficient support for the Hypervisor, extending the development time excessively.

**Solution:** Look for additional implementations for backup will allow me to avoid this.

#### 4.2.2 Lack of technical knowledge:

Given that a lot of the project consists on research of both the specification and the chosen implementation, the time estimates are bound to be more speculative. **Solution:** The best strategy to try to mitigate this issue is to plan around this lack of information.

#### 4.2.3 Excessive Design Scope:

It is possible that during the investigation phase, the design requirements end up being too large.

**Solution:** An analysis of the essential features will be made in order to cut non essential requirements.

# 5 Methodology and Rigor

This section will detail both the work methodology and the tools used to monitor the progress.

# 5.1 Methodology

Taking into account the breadth and complexity of the Hypervisor specification and related material, the project will be separated in 3 parts.

- Analysis of the specification to identify what needs to be implemented

- Analysis of the chosen processor.

- Design and implementation of the hypervisor.

To archive that, we will apply an agile methodology based on "scrum" strategy, this will consist of doing small "sprints" each week with small doable objectives, then at the start of the week a reunion will be held with the project director and new objectives will be added to the next sprint based on the previous sprint performance.

## 5.2 Monitoring tools

For the Design and Implementation of the Hypervisor, I'll use git, an open source version control system, to track and safeguard the progress in the implementation.

I'll also keep a diary-like document detailing the tasks done to facilitate writing of the documentation. The project will be successful if a working Hypervisor is implemented. this will be tested using tests provided by the RISC-V foundation [3] as well as my own.

# 6 Task Description

In the following section I will define the tasks that need to be performed as well as the expected completion time, due to the investigative nature of the project, the expected time to completion as my vary as well as the number and nature of the tasks.

### 6.1 **Project Management:**

This group of tasks involve the management of different aspects of the project.

#### 6.1.1 Scope

this section is important, as it involves defining the scope of the project as well as defining its general structure, this tasks will take 10 hours to ensure the project foundation is solid.

#### 6.1.2 Planning

This task consists of making a timeline of the project tasks as well as designing alternative plans and forecasting obstacles, this task will take 5 hours as part of this task is already done in **Scope**

#### 6.1.3 Cost and Sustainability

This tasks are about documentation and can be done concurrently, each individual task should take the same as the planning, 5 hours.

#### 6.1.4 Documentation

An important part of the project is to document it for future reference, as such an hour will be dedicated each week to document the week progress, as well as any insights, this should take 15 hours total.

## 6.2 Agile

As Agile is planned in sprints (Short week long intervals) we need a task to plan how to implement Agile **General Planning** and a set of recurrent tasks that plan each sprint **Sprint Planning**, **QA Reunion and Control Reunion**

### 6.2.1 General Planning

This task involves scheduling reunions with the Project director as well as planning how to use Agile in the project, this should take 5 hours.

### 6.2.2 Sprint Planning

In order to make use of the Reunions with the Project Director, half an hour should be set aside to prepare this reunions and the plans for the next sprint.

#### 6.2.3 QA Reunion and Control Reunion

The reunions can be QA Reunions, Control Reunions or both, QA Reunions are about checking the quality of the work being done, while the Control Reunions are about the work to be done, because I expect an even number of both, I expect that I'll need to dedicate 15 hours in total in reunions.

# 6.3 Spec Analysis

The First part of the project involves Reading and understanding the RISC-V Specification, this will be divided in two tasks:

### 6.3.1 Reading The Privileged Spec

This task consists of reading the main body of interest, The Privileged Hypervisor specification, reading and synthesizing its contents should take 15 hours given the complexity of the material but it's relative short length

#### 6.3.2 Reading Additional Specs

Given the technical nature of the main document, it will become necessary to cross reference other RiSC-V Specs, like the Supervisor SPEC, the Standard SPEC or the Debugging SPEC, this should take an additional 5 hours and will be done concurrently with **Reading the Privileged Spec**

# 6.4 Target System Evaluation

After reading the documentation, the next task consists in looking at the already existing implementations and choosing the most fit for the task, I expect 2 o 3 candidates to evaluate and about 7 hours of work.

# 6.5 Setting up Development Environment

Once the Target has been chosen, I need to set up a development environment, this task may include, setting up a Linux Virtual Machine, installing specific computer software, including tooling and testing software, and other possible necessities, due to the large unknown component of this task I estimate 15 hours to complete it.

## 6.6 Designing the solution.

This part is both the most opaque one and probably the most time demanding one, it requires to design the necessary hardware modifications that need to be implemented, due to the amount and nature of such changes currently being unknown, I make an estimate of 45 hours, this task will start once the Dev environment is close to being complete.

# 6.7 Implementing the solution

After the Design is done, it will be time to implement it, given that the design is done properly, the implementation should be done somewhat faster, henceforth I estimate 30 hours.

# 6.8 Testing

This task will both test the correctness of the solution, as well as its performance, this task will take 20 hours and serve as a buffer in case more time is needed in **Designing The solution** or **Implementing the solution**

# 6.9 Final WriteUp

This task is to take all the documentation and the results of the **Testing** task and write the final document, I want to dedicate 20 hours to that task.

# 7 Gantt graph

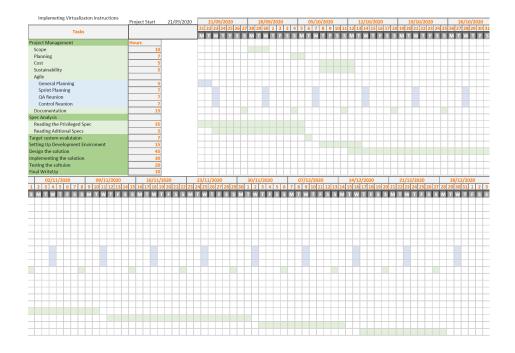

| Tasks                             |         |       |                   |            |            |            |

|-----------------------------------|---------|-------|-------------------|------------|------------|------------|

| Project Management                | ID      | Hours | Role              | Start      | End        | Dependency |

| Scope                             | PM-1    | 10    | Project Lead      | 28/09/2020 | 30/09/2020 |            |

| Planning                          | PM-2    | 7     | Project Lead      | 21/09/2020 | 05/10/2020 | PM-1       |

| Cost                              | PM-3    | 5     | Project Lead      | 08/10/2020 | 12/10/2020 | PM-2       |

| Sustainability                    | PM-4    | 5     | Project Lead      | 08/10/2020 | 12/10/2020 | PM-2       |

| Agile                             | PM-AX   |       |                   |            |            |            |

| General Planning                  | PM-A1   | 5     | Project Lead      | 21/09/2020 | 00/01/1900 |            |

| Sprint Planning                   | PM-A2   | 7     | Project Lead      | Rec        | urrent     | PM-A1      |

| QA Reunion                        | PM-A3   | 7     | Project Lead      | Rec        | urrent     | PM-A2      |

| Control Reunion                   | PM-A4   | 7     | Project Lead      | Rec        | urrent     | PM-A3      |

| Documentation                     | PM-5    | 15    | Project Lead      | Rec        | urrent     |            |

| Spec Analisis                     | DEV-1   |       |                   |            |            |            |

| Reading the Privileged Spec       | DEV-1-1 | 35    | Hardware engineer | 21/09/2020 | 05/10/2020 |            |

| Reading Aditional Specs           | DEV-1-2 | 5     | Hardware engineer | 23/09/2020 | 05/10/2020 |            |

| Target system evalutaion          | DEV-2   | 7     | Hardware engineer | 06/10/2020 | 07/10/2020 | DEV-1      |

| Setting Up Development Enviroment | DEV-3   | 15    | Hardware engineer | 08/10/2020 | 13/10/2020 | DEV-2      |

| Design the solution               | DEV-4   | 45    | Hardware engineer | 12/10/2020 | 10/11/2020 | DEV-3      |

| Implementing the solution         | DEV5    | 30    | Hardware engineer | 12/11/2020 | 01/12/2020 | DEV-4      |

| Testing the soltuion              | DEV-6   | 20    | Hardware engineer | 03/12/2020 | 15/12/2020 | DEV-5      |

| Final WriteUp                     | DEV-7   | 10    | Project Lead      | 17/12/2020 | 28/12/2020 | DEV-6      |

Figure 1: Gantt summary

Figure 2: Gantt Graph

# 8 Risk Management:

Due to the nature of this project, it is very possible that certain tasks take longer than initially expected, especially those after **Reading other Specs**, in other to mitigate that, I designed the testing phase to be open ended and thus easily re sizeable also I overestimated all linearly dependant tasks outside of project management to account for unexpected obstacles. in the event that the progress starts to slow down during sprints, the amount of hours will be increased by 50% for the following week.

Given a 25% risk of that happening on each of the 15 sprints on average it will lead to a possible increase of up to 62.6 hours to the project.

# 9 Budget

In this section, we'll examine the economic cost of the project, in order to do that, we'll analyze all the aforementioned task of the project, as well as "generic costs" that would apply to all steps of the project.

# 9.1 Human Cost

First, we'll employ the social network Linkedin to obtain the average salary of a Project Lead and a Hardware engineer [4], the two essential roles for this project. While I considered a tester role for the testing task, it would not be adequate as most of the task involves work that resembles more that of an engineer that a dedicate testing role.

| Role              | Salary | Salary w/ Taxes(+30%) |  |

|-------------------|--------|-----------------------|--|

| Hardware engineer | 14.42€ | 18.7€                 |  |

| Project Lead      | 24.52€ | 31.9€                 |  |

Figure 3: Role Salary/h

We use this data to calculate the human cost of each task.

| Tasks                             |         |       |                   |                |

|-----------------------------------|---------|-------|-------------------|----------------|

| Project Management                | ID      | Hours | Role              | Estimated cost |

| Scope                             | PM-1    | 10    | Project Lead      | 318.76€        |

| Planning                          | PM-2    | 7     | Project Lead      | 223.13€        |

| Cost                              | PM-3    | 5     | Project Lead      | 159.38€        |

| Sustainability                    | PM-4    | 5     | Project Lead      | 159.38€        |

| Agile                             | PM-AX   |       |                   |                |

| General Planning                  | PM-A1   | 5     | Project Lead      | 159.38€        |

| Sprint Planning                   | PM-A2   | 7     | Project Lead      | 223.13€        |

| QA Reunion                        | PM-A3   | 7     | Project Lead      | 223.13€        |

| Control Reunion                   | PM-A4   | 7     | Project Lead      | 223.13€        |

| Documentation                     | PM-5    | 15    | Project Lead      | 478.14€        |

| Spec Analisis                     | DEV-1   |       |                   |                |

| Reading the Privileged Spec       | DEV-1-1 | 35    | Hardware engineer | 656.11€        |

| Reading Aditional Specs           | DEV-1-2 | 5     | Hardware engineer | 93.73€         |

| Target system evalutaion          | DEV-2   | 7     | Hardware engineer | 131.22€        |

| Setting Up Development Enviroment | DEV-3   | 15    | Hardware engineer | 281.19€        |

| Design the solution               | DEV-4   | 45    | Hardware engineer | 843.57€        |

| Implementing the solution         | DEV5    | 30    | Hardware engineer | 562.38€        |

| Testing the soltuion              | DEV-6   | 20    | Hardware engineer | 374.92€        |

| Final WriteUp                     | DEV-7   | 10    | Project Lead      | 318.76€        |

| TOTAL Human cost                  |         | 235   |                   | 5,429.45€      |

Figure 4: Task Human cost

The estimate human cost of the project is 5,429.45 euros.

# 9.2 Generic Cost

# 9.2.1 Resources

First of all, the main resource used in this project will be the authors personal computer, valued in 1,400 euros (peripherals included) and an expected life span of 8 years.

All software used on the project is free open source software, with a total cost

of 0 euros.

**Amortized cost:** In order to calculate the amortized cost of the computer we use the following formula

$$Amortized \ cost = resource \ cost * \frac{project \ span}{resource \ lifespan}$$

| Resource      | Cost(€) | Lifespan(months) | Amortized |

|---------------|---------|------------------|-----------|

| Work Computer | 1,500€  | 96               | 62.50€    |

| Software      | 0.00€   |                  | 0.00€     |

#### 9.2.2 Non Amortizable costs

**internet:** Using a 45€/month contract during the 4 months of the project for a total of 180€ given that only 235h out of 4 month of internet are used for the project the cost is:  $180^{*}(235/(4^{*}30^{*}24)) = 14.69$  euros

**Electricity:** Using this resource [5] we establish the kWh cost at 0,147743 euro. assuming I use the computer for every task of the project (235h) and given the fact that the computer uses 500W, henceforth 0,147743\*500\*235/1000=17.36 euros

### 9.2.3 Total

The total generic cost is the sum of the previously mentioned costs:

| Concept     | Cost   |

|-------------|--------|

| Resources   | 62.50€ |

| Internet    | 14.69€ |

| Electricity | 17.36€ |

| Total       | 94.55€ |

Figure 6: Total generic costs

# 9.3 Contingency

As it is customary in this types of projects we should add a 15% contingency, taking into account the big variability of the project, 828,60 euros.

# 9.4 Risks

The main risks exposed previously is the risk that the time allocated proved to be insufficient, the main mitigation strategy consists on reallocating testing hours to the overdue task, if that is insufficient, additional time will be allocated, up to 20 additional hours as a hardware engineer (374.92 euros), given the nature of the project I think there is at least a 25% chance of this occurring, given an estimated cost of 93.73 euros.

### 9.5 Total

Adding up all together we get the following budget:

| Concept           | Cost      |

|-------------------|-----------|

| Human Cost        | 5,429.45€ |

| Generic Cost      | 94.55€    |

| Contingeny        | 828.60€   |

| Risks             | 93.73€    |

| Total             | 6,446.33€ |

| Total + IVA (21%) | 7,800.06€ |

| Figure  | 7:  | Total | Budget |

|---------|-----|-------|--------|

| I ISure | ••• | rouar | Duugou |

# 9.6 Control

Using the Agile methodology allow us to readjust the hours dedicated to each task as well as keep track of the time and resources spent on each sprint.

# 10 Sustainability report

# 10.1 Survey

Before starting the report, a survey was answered in order to become more aware of subjects related to sustainability in engineering projects.

The survey contained questions about knowledge about sustainability as a concept as well as techniques for identifying and preventing issues of that nature. Mainly due to a lack of experience on the subject, and little to none coverage of this subjects in the curriculum, the survey reflected a lack knowledge in the field, these results weren't surprising.

The next sections will cover sustainability from different perspectives, it is based on the following sustainability matrix.

|               |                                                                                                        | PPP                                                                                                                                                                                   | Exploitation                                                                                                                                                                                                  | Risks                                                                                              |  |

|---------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|

|               | I                                                                                                      | Have you estimated the environmental impact of<br>undertaking the project? Have you considered<br>how to minimise the impact, for example by<br>reusing resources?                    | How is the problem that you wish to address<br>resolved currently (state of the art)? In what ways will<br>your solution environmentally improve existing<br>solutions?                                       |                                                                                                    |  |

| Environmental | F                                                                                                      | Have you quantified the environmental impact of<br>undertaking the project? What measures have<br>you taken to reduce the impact? Have you<br>quantified this reduction?              | What resources do you estimate will be used during<br>the useful life of the project? What will be the<br>environmental impact of these resources?                                                            | Could situations occur that could increase the project's ecological footprint?                     |  |

|               |                                                                                                        | If you carried out the project again, could you use fewer resources?                                                                                                                  | Will the project enable a reduction in the use of other<br>resources? Overall, does the use of the project<br>improve or worsen the ecological footprint?                                                     | the project's ecological lootprint?                                                                |  |

|               | I                                                                                                      | Have you estimated the cost of undertaking the<br>project (human and material resources)?                                                                                             | How is the problem that you wish to address<br>resolved currently (state of the art)? In what ways will<br>your solution economically improve existing<br>solutions?                                          |                                                                                                    |  |

| Economic      | F                                                                                                      | Have you quantified the cost (human and<br>material resources) of undertaking the project?<br>What decisions have you taken to reduce the<br>cost? Have you quantified these savings? | What cost do you estimate the project will have<br>during its useful life? Could this cost be reduced to<br>increase viability?                                                                               | Could situations occur that are detrimental                                                        |  |

|               |                                                                                                        | Is the expected cost similar to the final cost?<br>Have you justified any differences (lessons<br>learnt)?                                                                            | Have you considered the cost of<br>adaptations/updates/repairs during the useful life of<br>the project?                                                                                                      | to the project's viability?                                                                        |  |

| Social        | I                                                                                                      | What do you think undertaking the project has<br>contributed to you personally?                                                                                                       | How is the problem that you wish to address<br>resolved currently (state of the art)? In what ways will<br>your solution socially improve (quality of life) existing<br>is there a real need for the project? |                                                                                                    |  |

|               | Has undertaking this project led to meaningful<br>F reflections at the personal, professional or ethic |                                                                                                                                                                                       | Who will benefit from the use of the project? Could<br>any group be adversely affected by the project? To<br>what extent?                                                                                     | Could situations occur in which the project<br>adversely affects a specific population<br>segment? |  |

|               |                                                                                                        | level among the people involved?                                                                                                                                                      | To what extent does the project solve the problem that was established initially?                                                                                                                             | Could the project create any kind of<br>dependency that puts users in a weak<br>position?          |  |

Figure 8: sustainability matrix

### 10.2 Environmental perspective

What resources have you used during the lifespan of the project? What is the environmental impact of those resources? The main resource used is a personal computer, The main environmental impact is its electrical usage. Have you estimated the environmental impact of undertaking the project? Have you considered how to minimise the impact, for example by reusing resources?

I have not quantified the the environmental impact of the used resources, and neither have I taken measures to minimize them.

How is the problem that you wish to address resolved currently (state of the art)? In what ways will your solution environmentally improve existing solutions?

Different CPU vendors have their own hypervisor implementations, my solution, while not being directly an improvement could be made more environmentally friendly by any third party given that the project is open source.

#### What resources could reuse other projects?

Everything related to the project is open source and could be used by other RISC-V implementators either in the BSC or elsewhere.

## 10.3 Economic perspective

# Have you estimated the cost of undertaking the project (human and material resources)

This project includes a budget and the deviations of said project

How is the problem that you wish to address resolved currently (state of the art)? In what ways will your solution economically improve existing solutions?

This solution offers a free Hypervisor implementation, which would be an improvement over the closed source proprietary ones currently on the market.

### Is there a collaboration with another project?

While not an explicit collaboration, the project may be integrated the in the Lagarto project of the BSC.

# 10.4 Social perspective

# What do you think undertaking the project has contributed to you personally?

This project has given me experience in the hardware field, as well as a greater understanding on how to manage this kind of projects.

### Is there a real need for the project?

I think that having an open source hypervisor is important, as open source hardware is both really important and surprisingly scarce.

# 11 The RISCV

In this section we are going to discuss the ISA itself as well as some of its more relevant characteristics for our project.

The term RISC itself means Reduced Instruction Set Computer, a type of computer design that prioritizes a simple, small, fixed length instruction set, with explicit load and store instructions in contrast with a CISC (Complex Instruction Set Computer) that tends to have a large number of instructions of various word sizes, the most common desktop PC architecture x86 is a CISC. What distinguishes the RISC-V architecture among other RISCs and most ISAs in general, is that it is a royalty free, open and free ISA, allowing anyone to develop, and sell their own RISC-V implementations. This coupled with a large amount of existing support, makes it an attractive offer for hardware developers and researches alike.

The base design of the ISA is focused on small, low energy, general usage CPUs, however, the ISA has a number of extensions, that allow things such as: Integer multiplication and division, single and double precision floating point operations, atomic operations and more.

One of the extensions, and the one we will be focusing on, is the H extension -Standard Extension for Hypervisor, that allows for the implementation of both Type-1 and Type-2 Hypervisors.

# 12 RISC-V Privileged Instruction Set - Standard Extension for Hypervisor

As said before, virtualizing without hardware support is really slow and resource intensive. The Hypervisor Extension aims to improve virtualization performance, mainly by reducing amount of interrupts and exceptions that need to be handled by the Host OS.

The approach taken is to virtualize supervisor mode(S mode), changing the existing supervisor mode into an Hypervisor-extended supervisor mode (HS mode) and adding both virtual user mode (US mode) and virtual supervisor mode (VS mode), additionally, a second stage is added to the address translation mechanism, virtualizing the memory and memory mapped I/O devices for the guest OS.

## 12.1 Trap Handling

RISC-V features a trap delegation mechanism that allows different privilege levels to handle interrupts and exceptions instead of M-mode. this is done by selecting which exceptions are delegated to a lower privilege level, going from M to HS to VS. This allows the Guest OS to handle exceptions by itself.

### 12.2 Two-Stage Address Translation.

When virtualization is enabled, all memory accesses go through two stages, on the first one, the virtual address is translated into a *guest physical address* this stage is known as VS-stage, then these address is translated again to a supervisor physical address, this is known as the G-stage, when performing this step all accesses are considered U-mode accesses, even those preformed on VSmode data structures, a guest page-fault must be handled by either M or HS and cannot be delegated further.

# 12.3 Registers

The specifications details number of registers specific to the Extension, those registers and their functionality, are explained in figure 9.

| Register        | Description                                                                           |  |

|-----------------|---------------------------------------------------------------------------------------|--|

| hstatus         | Contains information for tracking and controlling exception behavior                  |  |

| hedeleg         | Configure exception delegation HS->VS.                                                |  |

| hideleg         | Configure interrupt delegation HS->VS.                                                |  |

| hvip            | Trigger virtual interrupt intended for VS.                                            |  |

| hip             | Shows pending VS or Hypervisor-specific interrupts.                                   |  |

| hie             | Shows enabled VS or Hypervisor-specific interrupts.                                   |  |

| hgeip&hgip      | &hgip         Control external interrupts directed to the guest OS f.e( passthrought) |  |

| hcounteren      | Controls the availability of specific hardware counters.                              |  |

| htimedelta(l/h) | Controls the $\Delta$ between the time read from the time register                    |  |

|                 | and the time displayed in VS-VU modes.                                                |  |

| htval           | additional information for trap handling.                                             |  |