# A Closed-loop Capacitance-to-Frequency Converter for Single-Element and Differential Capacitive Sensors

Lakshmi Areekath, Student Member, IEEE, Boby George, Senior Member, IEEE, and Ferran Reverter

Abstract—A novel closed-loop switched-capacitor (SC)capacitance-to-frequency converter (CFC) is presented in this paper. The proposed CFC is capable of measuring from either a single-element or a differential capacitive sensor, providing ratio and ratio-metric outputs, respectively. Most of the existing autobalancing schemes for capacitive sensors use the closed-loop approach but require precise sinusoidal AC excitation and provide an analog output that is sensitive to parasitic capacitances. Also, the use of voltage-controlled resistors (VCR) in many of these schemes limits the linearity and accuracy of their output. The SC-CFC presented in this paper, employs a simple DC reference for excitation, and gives a digital output that is insensitive to parasitic capacitances, by virtue of design. Additionally, the output is linear, irrespective of the sensor characteristic, and independent of the nominal value of the sensor. This feature, along with its compatibility with singleelement and differential capacitive sensors, facilitates its ease of integration with a wide range of capacitive sensors. The CFC has a one-time correction mechanism that significantly reduces the impact of component mismatch. The prototype of the proposed scheme exhibits a maximum non-linearity error (NLE) of 0.24%, a resolution of 12.59 effective number of bits (ENOB), and a rise time of 6 ms. In addition, the proffered design is fit for integrated circuit (IC) fabrication as it employs a switched-capacitor approach.

*Index Terms* — Capacitance-to-digital converter; Capacitanceto-frequency converter; Capacitive sensor; Closed-loop; Differential capacitive sensors; Single-element capacitive sensor; Interface circuit; Switched-capacitor.

## I. INTRODUCTION

CAPACITIVE sensors play a key role in myriad fields such as consumer electronics, automotive sensors, and industrial applications [1]. These sensors have an established record of providing sensor designers with an attractive option to realize non-contact measurement of various physical parameters. They exhibit high sensitivity, high resolution, broad bandwidth, low power dissipation, robustness, and are inexpensive [2].

Capacitive sensors with two electrodes as well as multiple electrodes have been reported, and are in use, for various applications. Two electrodes separated by a dielectric, or one electrode with the other being ground plane, are examples of single-element capacitive sensors. Single-element capacitive sensors with various electrode structures are used to sense touch [3], proximity [4], position [5], pressure [6], humidity [7], flow [8], and level [9]. Differential capacitive sensors (DCS) constitute another important category of capacitive sensors. They are used in a range of applications such as improved touch sensing [10], and determining position [11], displacement [12], acceleration [13], differential pressure [14], and permittivity distribution in the area of interest [15]. These sensors consist of two sensing capacitances, say,  $C_1$  and  $C_2$ , with a common electrode.  $C_1$  and  $C_2$  vary with the parameter being sensed.  $C_1 = C_2 = C_0$  when the measurand is zero. The change in  $C_1$  due to the measurand is opposite to that in  $C_2$ , causing these sensors to be popularly known as push-pull type capacitive sensors. The change in capacitance with respect to the measurand, x, can be linear or non-linear (inverse) as given in (1) and (2), respectively, where k is the sensor constant, and  $C_0$  is the nominal capacitance of the sensor [16]. The characteristic is linear, as in (1), in the case of the widely used parallel-plate arrangement of the electrodes which utilize the change in the area of overlap between the plates, or change in the dielectric constant, with respect to the measurand. It is an inverse characteristic, as in (2), if the change in capacitance is caused by the change in the distance between the plates. Similarly, the linear single-element sensors can be represented as  $C_1$  in (1), while the inverse ones can be represented using  $C_2$  given in (2).

$$C_1 = C_0(1 \pm kx) \text{ and } C_2 = C_0(1 \mp kx)$$

(1)

$$C_1 = \frac{C_0}{(1 \mp kx)} \text{ and } C_2 = \frac{C_0}{(1 \pm kx)}$$

(2)

The general approaches for output digitization in singleelement capacitive sensors begin with the conversion of capacitance to an equivalent voltage signal [17], [18]. This signal is then given to an analog-to-digital converter. Other approaches include obtaining number of transitions [19], frequency [20] - [22] or time period [23] as a function of the capacitance, following which a corresponding digital value is derived. Similar approaches are employed to get a digital output from differential capacitive sensors. For instance, [24] is a commercially available  $\Sigma$ - $\Delta$  based converter for capacitive sensors. This does not provide ratio-metric output directly. Also, it has limited ranges for the sensor and acceptable

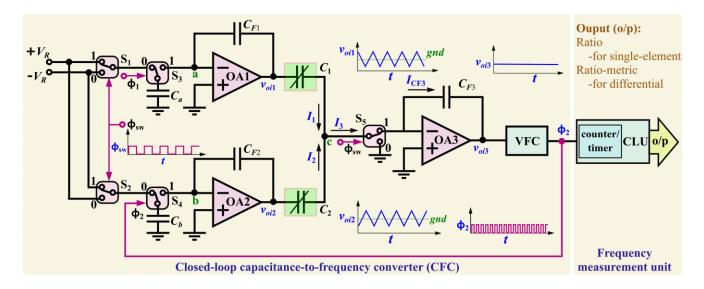

Fig. 1. Functional block diagram of the proposed SC-CFC. In the circuit,  $C_{F1} = C_{F2} = C_F$  and  $C_a = C_b = C$ . VFC represents a voltage-to-frequency converter, and CLU is a control and logic unit.

magnitude of parasitic capacitance. The circuit in [25] uses capacitance-to-pulse-width conversion. Its output is parasiticinsensitive but requires two capacitance-to-voltage converters, followed by a voltage-to-pulse-width converter, and operates in an open-loop configuration. In [26], a switched-capacitorbased dual-slope capacitance-to-digital converter (CDC) is presented, but the update rate is relatively low. A low power CDC using successive approximation register (SAR)-based conversion is reported in [27]. A ratio-metric output [26] is preferred for DCS instead of a difference output [27]. A synchronous demodulator-based scheme is presented in [28]. It needs AC excitation, and provides an analog output. In [29] a switch-bridge-based circuit is presented for the DCS. This design avoids the limitations of its diode counterpart, but requires an AC source and the output voltage is not ratiometric.

The measurement circuits given in [20], [30] and [31] adopt a closed-loop approach. The circuit in [20] is a closed-loop SC-CFC for a single-element capacitive sensor. Though it exhibits a high update rate, it is not suitable for interfacing differential capacitive sensors. The scheme proposed in [30] and [31] deals with differential capacitive sensors. It is an auto-balanced bridge circuit which requires a precise sinusoidal AC excitation and has a complex design involving a synchronous demodulator. It uses two multipliers in its feedback path, one of which is used to realize a voltagecontrolled resistor (VCR). The worst-case error of the analog multiplier employed is typically high, e.g. 2% in the case of AD633, used in [30], [31]. The use of such components in the design limits its linearity and accuracy. In addition, this circuit provides an analog output (while digital is preferred) which is sensitive to parasitic capacitances.

The proffered measurement scheme, for single-element and differential capacitive sensors, is a closed-loop switchedcapacitor capacitance-to-frequency converter (SC-CFC) circuit. It uses DC excitation, and achieves high accuracy and a relatively high update rate. In the case of differential capacitive sensors, the ratio-metric output from the scheme ensures a linear characteristic irrespective of the sensor characteristic being linear or inverse. Moreover, the final output does not depend on the nominal capacitance value of the sensor, enabling easy interfacing of the sensor to the measurement circuit. The same SC-CFC is suitable for singleelement capacitive sensors, possessing either linear or inverse characteristic, and gives a linear ratio output directly, independent of the nominal capacitance. The proposed CFC is simple and relatively inexpensive to realize. Since a switchedcapacitor approach has been employed in its implementation, this circuit is suitable for IC fabrication. The design and operation of this new closed-loop SC-CFC and its evaluation based on a hardware prototype are presented in the subsequent sections.

2

## II. CAPACITANCE-TO-FREQUENCY CONVERTER

The circuit diagram of the proposed SC-CFC is shown in Fig. 1. The scheme is presented first for differential capacitive sensor, followed by single-element capacitive sensor.

## A. Differential Capacitive Sensor

The variable capacitors  $C_1$  and  $C_2$  represent the differential capacitive sensor.  $V_R$  is a DC reference voltage, and it is connected to the single pole double throw (SPDT) switches  $S_1$ and  $S_2$ . When clock  $\phi_{sw}$  is high, the output of  $S_1$  is at  $+V_R$  and that of  $S_2$  is at  $-V_R$ . The outputs of these SPDT switches will be flipped when  $\phi_{sw}$  is low. The switch  $S_3$  controlled by the clock signal  $\phi_1$ , the operational amplifier OA1, and capacitors  $C_a$ ,  $C_{F1}$  constitute an SC integrator.  $\phi_1$  is a fixed clock whose frequency  $f_1$  is much higher than the frequency  $f_{sw}$  of  $\phi_{sw}$ . When  $\phi_{sw}$  is high, for every clock cycle of  $\phi_1$  the voltage  $v_{oi1}$ decreases by  $V_R C_a / C_{F1}$ . On the other hand, when  $\phi_{sw}$  is low,  $v_{oi1}$  increases by the same amount for each clock cycle of  $\phi_1$ . This process synthesizes a triangular voltage  $v_{oi1}$  as input to the capacitor  $C_1$ . This is illustrated in Fig. 2. Similarly, switch

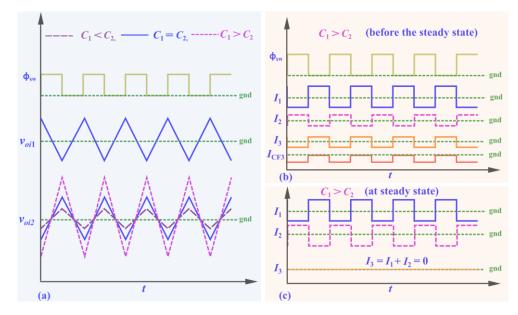

Fig. 2. (a) Important waveforms of the proposed CFC for different conditions of  $C_1$  and  $C_2$ .  $\phi_1$  and  $\phi_2$  are at a much higher frequency compared to  $\phi_{sw}$ .  $v_{ol1}$  and  $v_{ol2}$  increment and decrement, in steps, as they are outputs of SC integrators. The individual steps become less visible as they get smaller. (b) Pictorial representation of the waveforms of the currents for  $C_1 > C_2$ , before reaching the steady state of the circuit. The currents, once the circuit is in steady state, are given in (c).  $I_{CF3}$  is not shown in (c) as it is zero.

S<sub>4</sub>, capacitors  $C_b$ ,  $C_{F2}$ , and opamp OA2 forms another SC integrator with output  $v_{oi2}$ . The polarity of the slope of the triangular wave  $v_{oi2}$  will be opposite to that of  $v_{oi1}$  as, at any instant of time, the outputs of S<sub>1</sub> and S<sub>2</sub> have opposing signs. S<sub>4</sub> is operated using  $\phi_2$ , which is the output of the voltage to frequency converter (VFC).  $\phi_2$ , with a frequency  $f_2$  corresponding to the voltage fed into the VFC, is used together with switched-capacitor integrator to realize the autobalancing mechanism which forms the core of the proposed closed-loop circuit.

The currents  $I_1$  and  $I_2$ , indicated in Fig. 1, combine at node c, and the resultant current  $I_3$  flows into the SPDT switch  $S_5$ .  $S_5$  is controlled by  $\phi_{sw}$ , which is the same signal that controls  $S_1$  and  $S_2$ . In the absence of  $S_5$ , the output  $v_{oi3}$  of the integrator, consisting of feedback capacitor  $C_{F3}$ , and opamp OA3, would always tend to zero since  $I_3$  is a bipolar signal when  $C_1 \neq C_2$ , before the circuit reaches steady state, as shown in Fig. 2b. The presence of  $S_5$  ensures that the current  $I_{CF3}$  through  $C_{F3}$  is unidirectional (refer Fig. 2b), and hence  $v_{oi3}$  monotonously accumulates, and achieves auto-balancing at a different voltage for each set of values of  $C_1$  and  $C_2$ .

Let  $C_{F1} = C_{F2} = C_F$ , and  $C_a = C_b = C$ . In this case, the slopes of  $v_{oi1}$  and  $v_{oi2}$ , namely  $\frac{\partial v_{oi1}}{\partial t}$  and  $\frac{\partial v_{oi2}}{\partial t}$ , have the same magnitude but opposite polarity, as shown in Fig. 2. When  $\phi_{sw}$ is high the slope of  $v_{oi1}$  is negative, whereas that of  $v_{oi2}$  is positive. Thus,  $I_1$ ,  $I_2$  and  $I_3$  can be expressed by (3), (4) and (5) respectively. If  $C_1 = C_2$ ,  $I_1$  and  $I_2$  will be of equal magnitude and opposite polarity. Thus,  $I_3$  and  $I_{CF3}$  (=  $I_3/2$ ) are zero, producing an output  $v_{oi3} = 0$ . The expression for  $v_{oi3}$ is given in (6). The VFC is configured such that when  $v_{oi3}$  is zero, the frequency output,  $f_2$  will be the same as the fixed frequency  $f_1$ .

$$I_1 = -C_1 \frac{\partial v_{oi1}}{\partial t} = -C_1 \frac{v_R c}{c_F} f_1$$

(3)

$$I_2 = C_2 \frac{\partial v_{oi2}}{\partial t} = C_2 \frac{v_R C}{c_F} f_2 \tag{4}$$

$$I_3 = I_1 + I_2 = [C_2 f_2 - C_1 f_1] \frac{V_R C}{C_F}$$

(5)

$$v_{oi3} = -\frac{1}{C_{F3}} \int I_{CF3} dt = [C_1 f_1 - C_2 f_2] \frac{v_R c}{2C_F C_{F3}} t \qquad (6)$$

Now, when  $f_1 = f_2$ , let  $C_1$  and  $C_2$  be changed such that  $C_1 > C_2$ . Then,  $C_1 f_1 > C_2 f_2$ . This causes a non-zero  $I_3$  (actually,  $I_3 < 0$  since  $I_1$  is a negative quantity) to flow through  $C_{F3}$  increasing  $v_{oi3}$  as per (6). Thus, the VFC delivers an increased output frequency  $f_2$ , leading to an increase in  $\frac{\partial v_{oi2}}{\partial t}$ , as shown in Fig. 2. As  $f_1$ , and hence  $\frac{\partial v_{oi1}}{\partial t}$ , remain constant, the increase in  $\frac{\partial v_{oi2}}{\partial t}$  reduces  $|I_3|$ . This goes on until  $|I_1| = |I_2|$  following which  $v_{oi3}$  ceases to vary. In this condition, (7) can be obtained from (6).

$$C_1 f_1 = C_2 f_2 \tag{7}$$

or

$$C_1 / C_2 = f_2 / f_1$$

(8)

If instead  $C_1 < C_2$ , when  $f_1 = f_2$ , then  $|I_1| < |I_2|$ , and  $v_{oi3}$  decreases until  $f_2$  is sufficiently decreased such that  $|I_1| = |I_2|$ . The decrease in  $\frac{\partial v_{oi2}}{\partial t}$  due to the decreased  $f_2$  is also shown in Fig. 2.

The ratio of the capacitances  $C_1$  and  $C_2$  can be estimated using (8). However, if a ratio-metric computation of  $f_1$  and  $f_2$ , as in (9), is performed, the ratio-metric output due to  $C_1$  and  $C_2$  is obtained. In (9), the output follows a linear relation with the measurand x, where k is the sensor constant. Thus, the measurand can be linearly estimated for sensors possessing either linear or inverse characteristic. Polarity of x is taken as positive if  $f_1 < f_2$ , and negative for  $f_1 > f_2$ .

$$\frac{(f_2 - f_1)}{(f_2 + f_1)} = \frac{(C_1 - C_2)}{(C_1 + C_2)} = \pm kx \tag{9}$$

# B. Single-Element Capacitive Sensor

To interface a single-element capacitive sensor, either  $C_1$  or  $C_2$  (refer to Fig. 1) is set as the sensor capacitance, keeping the other as the reference capacitor. If the sensor  $C_x$  possesses a linear characteristic as  $C_x = C_0(1 \pm kx)$ , it is connected in place of  $C_1$ . Then,  $C_2$  is set as  $C_0$ . In this case, from (8), (10) is obtained.

$$\frac{(f_2 - f_1)}{f_1} = \frac{C_0(1 \pm kx)}{C_0} - 1 = \pm kx \tag{10}$$

To interface single-element sensor  $C_x$  that follows inverse characteristic, i.e.,  $C_x = C_0/(1 \pm kx)$ , it should be connected in place of  $C_2$  and  $C_1$  set as  $C_0$  in Fig. 1. In such case, a linear final output is obtained, i.e., (10) holds true for both types of single-element sensors.

#### C. Measurement of $f_2$

Since  $f_1$  is known and  $f_2$  can be measured using a frequency counter, the output estimated using (9) or (10) is available in digital domain. The frequency counter is part of the Control and Logic Unit (CLU) in Fig. 1. To measure  $f_2$ , it counts the number pulses  $n_t$  of  $\phi_2$  within a gate time  $T_G$ . The counter is set such that its output increments by one for every cycle of  $\phi_2$ . Then,  $f_2$  is computed as  $f_2 = (n_t/T_G)$ . For an update rate higher than the one achieved using the frequency counter, the measurement unit could be modified to measure the time period  $T_2$  of  $\phi_2$ . Then  $f_1$  can be replaced by  $1/T_1$ , where  $T_1$  is the time period of  $\phi_1$ , and  $f_2$  by  $1/T_2$  in (9) or (10), to obtain the ratio-metric or ratio outputs in terms of the respective time periods. However, due to limitations in the highest achievable frequency of the reference clock signal of the CLU, this approach has lower resolution and SNR than the frequency counter method. To improve these parameters the time-domain values can be averaged, for a given window size. Thus, the choice of output in the time-domain or frequency counter methods is essentially based on a tradeoff between update rate and resolution. In the prototype developed, the frequency counter has been used to perform the measurement.

# D. Effect of Mismatch and a Correction Method

In the derivation of (8), it is assumed that  $C_{F1} = C_{F2} = C_F$  and  $C_a = C_b = C$ . However, in practice there can be mismatch in the values of these components, which can impact the final output as explained below. Let,

$$C_{F1} = C_{F2}(1 + \epsilon_1) \text{ and } C_a = C_b(1 + \epsilon_2), \quad (11)$$

where  $\epsilon_1 = \Delta C_{F2}/C_{F2}$  and  $\epsilon_2 = \Delta C_b/C_b$ . Substituting (11) in (3) gives (12), while  $I_2 = C_2 \frac{V_R C_b}{C_{F_2}} f_2$ . Under this condition, (8) will get modified as in (13).

$$I_1 = -C_1 \frac{V_R C_b(1+\epsilon_2)}{C_{F2}(1+\epsilon_1)} f_1$$

(12)

$$f_2/f_1 = (C_1(1 + \epsilon_2))/(C_2(1 + \epsilon_1))$$

(13)

Defining the ratio  $(1 + \epsilon_2)/(1 + \epsilon_1) = k_{\epsilon}$ , (13) can be rewritten as in (14). This shows that the mismatch introduces a gain error in  $f_2$ .

$$f_2/f_1 = k_{\in}(C_1/C_2) \tag{14}$$

From (14), it is evident that  $(C_1/C_2)$  can be obtained by measuring  $k_{\in}$ , and taking the ratio of  $(f_2/k_{\in})$  and  $f_1$  as in (15).

$$(f_2/k_{\epsilon})/f_1 = (C_1/C_2)$$

(15)

The factor  $k_{\in}$  can be obtained by noting down  $f_2$  for x = 0, i.e., by setting  $C_1 = C_2$ . Under this condition,  $k_{\in} = f_2/f_1$ . This is a one-time measurement. From then onwards, for any new measurement, a corrected output frequency  $f_{2cal} = (f_2/k_{\epsilon})$  can be computed from the measured frequency  $f_2$ . Now, if  $f_2$  is replaced by  $f_{2cal}$  in (9), the ratio-metric output given by (16) will remain unaffected due to the mismatch, which is a major advantage. The same correction can be incorporated in (10), single-element sensor is interfaced. when a These computations can be realized using the CLU shown in Fig. 1.

$$\frac{(f_{2cal} - f_1)}{(f_{2cal} + f_1)} = \frac{(c_1 - c_2)}{(c_1 + c_2)} = kx$$

(16)

### E. Range of the Sensor Capacitance

The ranges of  $C_1$  and  $C_2$  for which (8) is applicable is limited by the operating ranges of the opamps and VFC used to realize the circuit given in Fig. 1. The maximum output current, Io1max, of OA1 will limit the maximum acceptable value,  $C_{1max}$ , of  $C_1$ , for a given  $C_a$  (=  $C_b$  = C),  $C_{F1}$ (=  $C_{F2}$  = C) and  $f_1$ , such that  $C_{1max} < I_{o1max} \frac{C_F}{V_R C f_1}$ . Similarly,  $C_{2max} < I_{o2max} \frac{C_F}{V_R C f_2}$ , where  $C_{2max}$  is the maximum value of  $C_2$  and  $I_{o2max}$  is the maximum output current of OA2. The maximum output frequency,  $f_{2max}$ , possible for the VFC corresponding to the maximum (less than saturation) output voltage  $v_{oi3max}$  of OA3 will introduce another limiting factor for the maximum change  $\Delta C_{max}$  possible for  $C_1$  and  $C_2$ , i. e.,  $\Delta C_{max} = 2C_0 (f_{2max} - f_1) / (f_{2max} + f_1).$  Considering the above factors, for sensors following (1),

$$C_{imax} < \min\left[I_{oimax}\frac{c_F}{v_R c_{f_i}}, \ C_0\left(1 + \frac{f_{2max} - f_1}{f_{2max} + f_1}\right)\right],$$

for those satisfying (2)

and for those satisfying (2),  $C_{imax} < \min \left[ I_{oimax} \frac{C_F}{V_R C f_i}, C_0 / \left( 1 - \frac{f_{2max} - f_1}{f_{2max} + f_1} \right) \right],$ where i = 1 or 2. For the prototype developed, for sensors with

linear characteristic, the  $C_{imax}$  works out to be 1.66  $C_0$  when  $f_{2max} = 500$  kHz and  $f_1 = 100$  kHz. In case of sensors satisfying (2),  $C_{imax} = 3C_0$ . For both cases, the resulting maximum kx is 0.66, which is sufficient for many applications of differential capacitive sensors [10], [15], [32]. To achieve a larger kx range,  $f_1$  can be reduced keeping the same  $f_{2max}$  or a more suitable VFC can be selected.

#### F. Sensitivity of the Interface

In the case of the differential capacitive sensor, when  $C_1 = C_2$ ,  $f_2 = f_1$ . When  $C_1 = C_0 + \Delta C$  and  $C_2 = C_0 - \Delta C$ , (8) becomes

$$\frac{C_0 + \Delta C}{C_0 - \Delta C} = \frac{f_1 + \Delta f}{f_1} \,. \tag{17}$$

or

$$\frac{1+\frac{\Delta c}{c_0}}{1-\frac{\Delta c}{c_0}} = 1 + \frac{\Delta f}{f_1}$$

(18)

For  $\frac{\Delta C}{c_0} \ll 1$ , (18) can be approximated as  $1 + 2\frac{\Delta C}{c_0} \approx 1 + \frac{\Delta f}{f_1}$ , or

$$\frac{\Delta f}{\Delta c} \approx \frac{2f_1}{c_0},\tag{19}$$

which gives the sensitivity of the proposed CFC. For the single-element, the right-hand side of (19) reduces to  $\frac{f_1}{c_1}$ .

#### **III. ERROR ANALYSIS**

The effect of important non-idealities in the output of the proposed SC-CFC is analyzed below. Here, let  $C_{F1} = C_{F2} = C_F$ , and  $C_a = C_b = C$ .

# A. Input Offset Voltage

Let  $V_{OS1}$ ,  $V_{OS2}$ , and  $V_{OS3}$  be the input offset voltages at the non-inverting terminals of OA1, OA2, and OA3, respectively. Since S<sub>5</sub> is used only to connect and disconnect node *c* to the input of OA<sub>3</sub>,  $v_{oi3}$ , due to  $V_{OS3}$ , will be  $V_{OS3}$  alone, with no other integrating components. Hence the effect of  $V_{OS3}$  at the output of OA3 can be compensated by appropriately designing the VFC. This is required to maintain  $f_1 = f_2$ , when  $C_1 = C_2$ .

$V_{OS1}$  and  $V_{OS2}$  contribute an additional voltage step in  $v_{oi1}$ and  $v_{oi2}$ , respectively. The impact of  $V_{OS1}$  in  $v_{oi1}$  and that of  $V_{OS2}$  in  $v_{oi2}$ , at any instant *n*, are given by (20) and (21), respectively, where m = 1 if  $\phi_{sw}$  is high and m = -1, otherwise. Also,  $v_{oi1}(n) = V_{OS1}$ , and  $v_{oi2}(n) = V_{OS2}$ , when n = 0.

$$v_{oi1}(n+1) = v_{oi1}(n) + V_{OS1}C/C_F - m V_R C/C_F$$

(20)

$$v_{oi2}(n+1) = v_{oi2}(n) + V_{OS2}C/C_F + m V_RC/C_F$$

(21)

Thus, for  $\phi_{sw} = high$ , when  $I_1 = -I_2$ ,

$$(C_1 (V_{OS1} - V_R) C/C_F) f_1 = (C_2 (V_{OS2} + V_R) C/C_F) f_2. (22)$$

Rearranging (22), gives

$$(C_1/C_2) = \left| \frac{(V_{OS2} + V_R)}{(V_{OS1} - V_R)} \right| (f_2/f_1)$$

(23)

Assuming  $V_{OS1}$ ,  $V_{OS2}$ ,  $V_R$  to be not time varying, (23) can

be re-written as

(

$$C_1/C_2) = k_{OS}(f_2/f_1).$$

(24)

5

In the case of the prototype of the proffered circuit, the maximum values of  $V_{OS1}$  and  $V_{OS2}$  is 75 µV. Substituting these in (23) shows that  $V_{OS1}$ ,  $V_{OS2} \ll V_R$  (= 2.5 V) and so, in the developed prototype, input offset voltage has a negligible impact. Thus, as long as the opamps used in the proposed circuit are chosen such that  $V_{OS1}$  and  $V_{OS2} \ll V_R$ , and the VFC designed to compensate for  $V_{OS3}$ , the impact of the input offset voltages in the final output is negligible.

#### B. Input Bias Current

Let  $I_{B1}$ ,  $I_{B2}$ , and  $I_{B3}$  be the input bias currents at the inverting terminals of OA1, OA2, and OA3 respectively. The presence of  $I_{B1}$  will change  $v_{oi1}$  by  $I_{B1}T_1/C_F$  in each cycle of  $\phi_1$ . However, in practice,  $\frac{I_{B1}T_1}{C_F} \ll V_R C/C_F$ . Hence the effect of  $I_{B1}$  in  $I_1$  is negligible. Similarly, the effect of  $I_{B2}$  in  $I_2$  is not significant. However, since the bias current is flowing continuously in the same direction,  $v_{oi1}$  and  $v_{oi2}$  will go into saturation. To prevent this, resistors of appropriate values (20 MΩ) are connected in parallel to  $C_{F1}$  and  $C_{F2}$ , respectively. Since this resistor is in the feedback-path of OA1 and OA2, it can be implemented using relatively low-value resistors, say the largest being in 100 k $\Omega$  range, connected in a T- network. It has been reported that the leakage resistance of on-chip capacitors is in the range of few mega ohms [33]. In such a case, the additional resistor in parallel, as in the prototype, may not be necessary. In case the above options are not feasible, keeping these resistors external to the IC can be considered, to save the chip area, when an IC is designed.

In the ideal condition, at steady state,  $I_3/2 = I_{CF3} = 0$ . Due to the presence of  $I_{B3}$ , at the input of OA3, at steady state

$$(I_3)/2 = I_{\rm CF3} = -I_{B3}.$$

(25)

Substituting (3) and (5) in (25) with  $f_2$  replaced with  $f'_2$ , to indicate the new condition  $I_{CF3} = -I_{B3}$ , and rearranging, (26) is obtained.

$$f_2' = \frac{(-I_{B3}C_F/V_RC)}{c_2} + \left(\frac{c_1}{c_2}\right)f_1$$

(26)

Substituting the values from the prototype of the proposed circuit ( $I_{B3} = 30$  pA,  $C_F = 2$  nF, C = 20 pF,  $V_R = 2.5$  V,  $f_1 = 100$  kHz, along with the smallest value of  $C_2$  used, 100 pF, and the corresponding  $C_1 = 400$  pF) in (26), the relative error in  $f'_2$ , with respect to  $f_2$ , obtained is -0.003%. Thus, as long as OA1, OA2, and OA3 are chosen such that  $\frac{I_{B1}T_1}{C_F}$ ,  $\frac{I_{B2}T_1}{C_F} \ll V_R C/C_F$  and  $\frac{(-I_{B3}C_F/V_R C)}{C_2} \ll (\frac{C_1}{C_2})f_1$ , in the proffered circuit, the impact of bias current in the final output is negligible.

#### *C. Mismatch between* $+V_R$ *and* $-V_R$

Let the positive DC excitation be  $+V_R$ , whereas the negative be  $-V_R(1 + \epsilon_V)$ , where  $\epsilon_V$  is the relative mismatch between the magnitudes of the  $V_R$  and  $-V_R$ .  $\epsilon_V = 0$ , in an ideal case. This voltage mismatch contributes to  $I_{CF3}$  when  $\phi_{sw} = 1$ . In this condition,  $I_2$  and  $I_3$  given in (4) and (5) will get modified as (27) and (28), respectively.

$$I_2 = +C_2 \frac{\partial v_{oi2}}{\partial t} = +C_2 \frac{V_R(1+\epsilon_V)C}{C_F} f_2$$

(27)

$$I_{3} = I_{1} + I_{2} = \frac{V_{R}C}{C_{F}} (C_{2}f_{2} - C_{1}f_{1}) + C_{2} \in_{V} \frac{V_{R}C}{C_{F}} f_{2}$$

(28)

In a balanced condition,  $I_{CF3} = I_3 = 0$ . Then, the condition (29) can be obtained from (28).

$$\frac{c_1}{c_2} = k_V \frac{f_2}{f_1}$$

(29)

Comparing (29) with (8), it can be seen that the mismatch in reference voltages results in a multiplication factor  $k_V = (1 + \epsilon_V)$ . The value of  $k_V$  can be calculated, to correct the measurement, by setting  $C_1 = C_2$  and comparing the  $f_{2meas}$  measured to the expected  $f_2 (= f_1)$ , i.e.  $k_V = \frac{f_1}{f_{2meas}}$ . If there is a drift in  $\epsilon_V$ , a periodic calibration/correction will be required.

#### D. Variations in the Switch Control Signals $\phi_{sw}$ and $\phi_1$

A change in the frequency  $f_{sw}$  of  $\phi_{sw}$ , will change the duration for which  $\phi_{sw}$  is high. During the operation, the step change in  $v_{oi2}$  is  $V_R C/C_F$ . The maximum number of such steps, expected, when  $\phi_{sw}$  is high is  $(f_{2max})/(2f_{sw})$ . Let us say that the maximum output voltage swing of OA2 is  $2(V_{SAT} - 1)$ , where  $V_{SAT}$  is the saturation voltage of opamp. This means  $[(f_{2max})/(2f_{sw})] < [2(V_{SAT} - 1)/(V_R C/C_F)]$ , or the design should satisfy the condition

$$\frac{(f_{2max}V_RC)}{4(V_{SAT}-1)C_F} < f_{sw(min)},$$

where  $f_{sw(min)}$  in the minimum value of  $f_{sw}$  expected.

Any change in the frequency of  $\phi_1$  will impact the accuracy of the measurement. In the proposed CFC, the value of  $f_1$  was found to be stable and accurate during the measurement time. However, it is advisable to measure  $f_1$  periodically, using the same counter/timer, and use in (9) or (10), to ensure that the accuracy of the measurement of kx is not affected.

#### E. Non-idealities of the Switches

The effects of charge injection and ON resistance of the switches on the final output of the CFC are discussed below.

## 1. Charge Injection

To analyze the effect of charge injection, each SPDT switch in Fig. 1 can be replaced by the charge injection model given in [34]. The charge injected at the output of each switch is a combination of charges generated during breaking of a contact, say position '1', and making of the next, say position '0'. S<sub>3</sub>, S<sub>4</sub>, and S<sub>5</sub> inject charges into  $C_{F1}$ ,  $C_{F2}$ , and  $C_{F3}$ , respectively, changing  $v_{oi1}$ ,  $v_{oi2}$ , and  $v_{oi3}$ , respectively, thereby affecting the final output of the proposed CFC. To realize the switches, IC MAX4709 from Maxim Integrated has

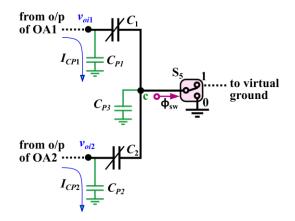

Fig. 3. The parasitic capacitances  $C_{P1}$ ,  $C_{P2}$  and  $C_{P3}$ , associated with the differential capacitive sensor consisting of  $C_1$  and  $C_2$ , are indicated.

been used. This IC is so designed that the switches inject zero charges during the making and breaking of the input-output connections. The functional diagram can be found in [34], [35]. The implementation of these ICs on the silicon substrate is done using the CMOS process [34]. As this is a zero-charge injection switch, the associated error will be negligible.

2. ON Resistance

The impact of the switch ON-resistances can be analyzed by replacing the switches S<sub>1</sub>-S<sub>4</sub> by the corresponding resistances  $R_{ON1}$ ,  $R_{ON2}$ ,  $R_{ON3}$ , and  $R_{ON4}$ , respectively. Consider first that  $\phi_{sw} =$  high. If for  $\phi_1 = 0$ ,  $\phi_2 = 0$ , as long as  $(R_{ON1} + R_{ON3})C_a << (1/f_1)$  and  $(R_{ON2} + R_{ON4})C_b << (1/f_2)$ ,  $C_a$  and  $C_b$  get fully charged to  $+V_R$  and  $-V_R$ , respectively, and vice-versa for  $\phi_{sw} =$  low. For  $\phi_1 = 1$ ,  $\phi_2 = 1$ , the outputs of OA1 and OA2 will be negligibly affected by the ON-resistances while  $R_{ON3}C_a << (1/f_1)$  and  $R_{ON4}C_b << (1/f_2)$  holds true.

# F. Parasitic Capacitances

Parasitic capacitance to ground will be present when shielded cables, with shield connected to ground, are used to connect the capacitive sensor to the interface circuit. Similarly, there will be parasitic capacitance between the ground plane and traces of the printed circuit board or lines of the bread-board. The equivalent lumped model of the parasitic capacitances is shown as  $C_{P1}$ ,  $C_{P2}$ , and  $C_{P3}$  in Fig. 3.  $C_{P1}$  and  $C_{P2}$  do not impact the performance of the proposed circuit as long as the outputs of the opamps OA1 and OA2 are not overloaded by them.  $C_{P3}$  is inactive as one end of it is connected to the virtual ground or ground while the other is always at ground. Hence, it has no impact on the final output.

#### IV. EXPERIMENTAL SETUP AND RESULTS

#### A. Prototype

The hardware prototype of the proposed closed-loop SC-CFC, given in Fig. 1, was realized using the components and ICs listed in Table I. In the prototype, the clock signals  $\phi_{sw}$  and  $\phi_1$  were set using a function generator to  $f_{sw} = 1$  kHz and  $f_1 = 100$  kHz, respectively. Since these are generated from the same dual-channel function generator, they are in synchronization. Alternatively, the synchronization can be maintained by generating  $\phi_{sw}$  and  $\phi_1$  using the timer/counter

| Component                                     | Part/Value      | Component        | Part/Value     |  |  |

|-----------------------------------------------|-----------------|------------------|----------------|--|--|

| $V_R$                                         | Using LM385-2.5 | $C_a, C_b$       | 20 pF          |  |  |

| <i>S</i> <sub>1</sub> - <i>S</i> <sub>5</sub> | MAX4709         | $C_{F1}, C_{F2}$ | 2 nF           |  |  |

| VFC                                           | ADVFC32         | $C_{F3}$         | 2 nF           |  |  |

| OA1, OA2                                      | OPA227          | $\Delta C$       | $\pm 150 \ pF$ |  |  |

| OA3                                           | LF357           | $f_{\sf sw}$     | 1 kHz          |  |  |

| CLU                                           | ATSAM3X8E       | $f_1$            | 100 kHz        |  |  |

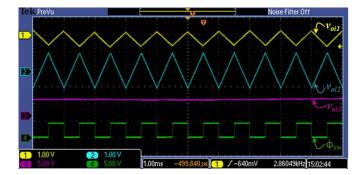

Fig. 4. A snapshot of the integrator waveforms, from the prototype, for  $C_1 > C_2$ .

unit of a microcontroller, with appropriate pre-scaler.

The linearity of the VFC limits the linearity of the overall system. In the protype, ADVFC32 was employed. It has high linearity, e.g., 0.05% in the 100 kHz range and 0.2% in the 500 kHz range. The VFC was set to output  $f_2 = f_1$ , for x = 0, by selecting the values of the resistors and capacitors in accordance with the design calculations given in [36]. Also, the VFC was configured to handle both positive and negative values of  $v_{oi3}$ .

Frequency  $f_2$  corresponding to  $C_1 = C_2$ , was used to determine the mismatch correction factor,  $k_{\epsilon}$  as in (14). The prototype was then tested using two identical standard variable capacitance boxes, with high leakage resistances, representing  $C_1$  and  $C_2$ , set to the nominal capacitance value,  $C_0 = 250$  pF. The final ratio-metric output, as per (16), was obtained after applying the corrections for mismatch discussed in section-II.A. The counter in the CLU was programmed to measure  $f_2$  for a gate time of 10 ms. This was used in the CLU to compute the final output applying (15). The important waveforms from the prototype were observed using MSO 2014, Mixed Signal Oscilloscope, during the test. A snapshot of the waveforms, from the oscilloscope, for  $C_1 > C_2$  is given in Fig. 4.

#### B. Power Consumption

As a proof-of-concept, the prototype was implemented with discrete components and ICs and, hence, it was not optimised for low power consumption. In this prototype, the power consumption of the opamps, VFC, switches and  $V_R$  were,

$P_{OA} = 110 \text{ mW}, P_{VFC} = 80 \text{ mW}, P_{SW} = 6 \text{ mW} \text{ and } P_{VR} = 50 \text{ }\mu\text{W},$ respectively. The clock is generated in the prototype by a function generator, but in practice it can be generated by the microcontroller. When the microcontroller is used to generate  $\phi_{SW}$  and  $\phi_1$ , in addition to measuring  $f_2$ , the power  $P_{\mu C}$  taken was about  $P_{\mu C} \cong 3 \text{ mW}$ . Thus the total power =  $P_{OA} + P_{VFC} + P_{SW} + P_{VR} + P_{\mu C} \cong 200 \text{ mW}$ . If the entire unit is designed and fabricated as a single chip, the overall power consumption could be reduced to as low as that of a dual-slope ADC ( $\cong 10 \text{ mW}$  [37]).

# C. Testing the Effectiveness of the Mismatch Correction

To test the effectiveness of the correction mechanism against component mismatch, discussed in section-II.A, a test was conducted by intentionally introducing a mismatch between  $C_a$  and  $C_b$  by setting  $C_b = C_a/2$ . The error percentage in the VFC output before and after correction for different values of  $\Delta C$  (deviation of  $C_1$  from the nominal capacitance) is given in Table II. As can be seen, the correction mechanism almost completely removes the effect of the mismatch. The same test was conducted by similarly introducing a mismatch between the  $C_{F1}$  and  $C_{F2}$ , and the correction was also found to be effective.

TABLE II EFFECTIVENESS OF THE MISMATCH CORRECTION

| $\Delta C (pF)$             | -10   | -5    | 0     | +5    | +10   |

|-----------------------------|-------|-------|-------|-------|-------|

| % Error before correction   | 48.39 | 48.32 | 48.40 | 48.00 | 48.48 |

| % Error after<br>correction | 0.01  | 0.15  | 0.00  | 0.17  | 0.15  |

# D. Linearity and Sensitivity

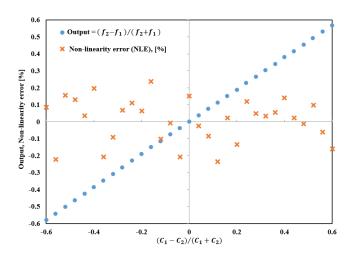

In this test, the values of  $C_1$  and  $C_2$  were first set to nominal capacitance  $C_0 = 250$  pF. Then they were varied in steps of 10 pF in opposing directions, for 15 steps in either direction. This process emulates a differential capacitive sensor with a linear characteristic as in (1), with a full-scale change kx<sup>FS</sup> = 0.6. The CLU provided the output as per (15), for each step. In this manner, the output was recorded for a range of capacitance,  $\Delta C = \pm 150$  pF, from nominal value. The results are presented in Fig. 5. This corresponds to a full-scale  $kx = \pm 0.6$ . This tested range covers the range of measurement in several applications, e.g., 0.35 [10], 0.536 [15] and 0.6 [32]. This is within the possible range discussed in section-II.D.

To obtain the maximum non-linearity error (NLE), the recorded output-data was first plotted. A trend-line of the same was then obtained using the Least Squares Algorithm. Subsequently, the values of the y-axis were determined by substituting the corresponding x-axis data in the trend-line equation. These values are taken as the expected output values, had the system been linear. Each measured value was subtracted from the corresponding expected value, for the full measurement range. This gives the NLE in each measurement. The % with respect to the full-scale ( $kx^{FS} = 0.6$ ) gave the % NLE. The maximum NLE observed was 0.24%.

In addition, the linearity was tested for the single-element capacitive sensor. For this test the same value of  $C_0$  was used and the value of  $C_1$  alone varied in steps of 10 pF from 100 pF

Fig. 5. Results from the prototype by varying  $C_1$  and  $C_2$ . The output and the percentage non-linearity error obtained are shown.

to 400 pF. The worst-case %NLE found in this test was 0.19 %. The linearity of the prototype circuit has also been verified for single-element and differential capacitive sensors that follow inverse characteristic as in (2).

The sensitivity of the frequency output  $f_2$  with respect to  $\Delta C$  was computed using (19). For the prototype developed  $f_1 = 100$  kHz and  $C_0 = 250$  pF. The resulting sensitivity is  $\frac{\Delta f}{\Delta c} \approx 0.8$  kHz/pF. The same has been verified practically from the prototype. For the single-element capacitive sensor, this was found to be  $\approx 0.4$  kHz/pF.

# E. Resolution, Signal-to-Noise Ratio (SNR) and Repeatability

To determine the resolution and repeatability, the prototype CFC was operated for  $\Delta C = 5$  pF, and the ratio-metric output,  $(f_2 - f_1)/(f_2 + f_1)$ , was recorded 30 times and tabulated. The formulae given in Table III, based on the approach given in [38], were used to determine the resolution and repeatability parameters, given in the same table. The proffered circuit shows a resolution of 12.59 bits (ENOB), signal-to-noise ratio (SNR) of 77.56 dB and repeatability error of 0.01%.

## F. Rise Time

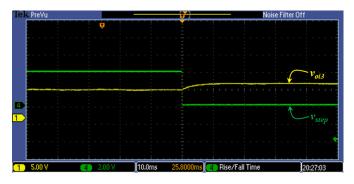

To ascertain the rise time of the proffered CFC, initially, the sensor capacitance was set to its mid-scale and then a sudden change in capacitance was introduced, in parallel, using a switching arrangement controlled by the signal  $v_{step}$ . When  $v_{step} = 0$ , an additional capacitance of 10 pF was introduced in parallel to  $C_1$ , using a capacitance box, with negligible leakage conductance, from Rohde and Schwarz. The rise time was 6 ms for  $f_{sw} = 1$  kHz and  $f_1 = 100$  kHz. A snapshot of the waveforms, in this case, is given in Fig. 6. As mentioned in section-II. B,  $f_2$  is measured using a counter. In the prototype, a change in the measurand will be correctly reflected in the output, at steady state, after about 16 ms, considering the rise time of 6 ms, and the gate time of 10 ms.

To verify the impact of the values of the operating frequencies in the rise time of the prototype SC-CFC, both  $f_{sw}$  and  $f_1$  were decreased to 100 Hz and 10 kHz, respectively.

TABLE III

REPEATABILITY STUDY

| Parameter                        | Formula                                                                             | Value                 |  |  |  |

|----------------------------------|-------------------------------------------------------------------------------------|-----------------------|--|--|--|

| Signal-to-noise<br>ratio (SNR)   | $SNR = 10 \log \frac{\sum_{i=1}^{M} X(i)^{2}}{\sum_{i=1}^{M} [X(i) - \bar{X}]^{2}}$ | 77.56 dB              |  |  |  |

| Standard Deviation, $\sigma$     | $\sigma = \sqrt{\frac{\sum_{i=1}^{M} [X(i) - \bar{X}]^2}{M - 1}}$                   | $4.33 \times 10^{-5}$ |  |  |  |

| Resolution (ENOB), <i>n</i> bits | $n = \frac{(SNR - 1.76)}{6.02}$                                                     | 12.59 bits            |  |  |  |

| Repeatability, d                 | $d = \frac{\Delta_{rmax}}{x_u - x_l} \times 100\%$                                  | 0.01%                 |  |  |  |

$X(i) = i^{\text{th}}$  measurement;  $\overline{X}$  = average value of the measured data

M =total number of measurements

$X_u, X_l$  = upper and lower limits of CFC

$\Delta_{rmax}$  = maximum difference between repeated measurements

Fig. 6. Rise time of the CFC for  $f_{sw} = 1$  kHz,  $f_1 = 100$  kHz.

Then, the rise time was 65 ms. The results in both cases show that the rise time improved by approximately ten times when the operating frequencies  $f_{sw}$  and  $f_1$  were increased tenfold.

#### V. DISCUSSION

The main features of the new scheme have been analyzed in comparison with the best ten of the existing schemes, and presented in Table IV. The proposed scheme is suitable for single-element and differential capacitive sensors (DCS), which is a main difference as can be seen in Table IV. The CFCs [20] - [22] presented in Table IV are suitable only for single-element capacitive sensor. The presented approach provides a linear output, without any additional computation or correction, even for single-element sensor that follows an inverse characteristic which is another specialty.

Other important factors of the proposed approach are: (a) It uses a closed-loop approach. Differential capacitance-tofrequency converter with this feature has not been sufficiently explored before. Closed-loop approach has been used to realize self-balancing bridges in [30], [31]. However, the outputs of these bridge schemes are sensitive to parasitic capacitance. In addition, they need a precise sinusoidal AC excitation. These designs have limited linearity and accuracy due to the use of analog multipliers, with high error (as large

| Methods                                                      | Capacitance-to-digital/time |                    | Current-           | Auto-                      | μC-                               | Capacitance-to-frequency |                     |                      |      |                    |

|--------------------------------------------------------------|-----------------------------|--------------------|--------------------|----------------------------|-----------------------------------|--------------------------|---------------------|----------------------|------|--------------------|

|                                                              | SAR<br>[27]                 | Σ-Δ<br>[24]        | Time<br>[25]       | -mode<br>interface<br>[39] | balancing<br>bridge [28]-<br>[31] | based                    | [20]                | [21]                 | [22] | This work          |

| Suitable for differential capacitive sensor (DCS)            | Yes                         | Yes                | Yes                | Yes                        | Yes                               | Yes                      | No                  | No                   | No   | Yes                |

| Suitable for single-element and DCS                          | No                          | Yes <sup>(a)</sup> | No                 | No                         | No                                | No                       | No                  | No                   | No   | Yes                |

| OL / CL                                                      | CL                          | OL                 | OL                 | OL                         | CL                                | OL                       | CL                  | OL                   | OL   | CL                 |

| Excitation (AC/DC)                                           | DC                          | AC                 | DC                 | DC                         | AC                                | DC                       | DC                  | AC                   | DC   | DC                 |

| Ease of IC fabrication                                       | High                        | High               | High               | Yes                        | Low                               |                          | High                | Low                  | High | High               |

| Resolution                                                   | 150 aF                      | 20 aF              | 160 aF             | 800 aF <sup>(b)</sup>      | NS                                | 7 bits                   | 17.5 fF             | 20 zF <sup>(c)</sup> | NS   | 12.5 ENOB(d)       |

| %NLE<br>Sensitivity                                          |                             | 0.01               |                    | 1.5                        |                                   | 1                        | 0.1                 | 0.1                  | 0.13 | 0.24               |

| Sensitivity                                                  |                             |                    | 127 ns/fF          | 5 nA/fF                    |                                   |                          |                     | 12 kHz/pF            |      | 0.8 kHz/pF         |

| Insensitivity to parasitic capacitance                       | Yes                         | Limited            | Yes                | Limited                    | No                                | No                       | Yes                 | No                   | Yes  | Yes                |

| Insensitivity to component mismatch                          | NS                          |                    | No                 | NS                         | No                                | Yes                      |                     | No                   |      | Yes <sup>(e)</sup> |

| Digital/quasi-digital output                                 | Yes                         | Yes                | Yes <sup>(f)</sup> | No                         | No                                | Yes                      | Yes                 | Yes                  | Yes  | Yes                |

| Ratio-metric output<br>(Ease of integration <sup>(g)</sup> ) | No                          | No                 | Yes                | Yes                        | No                                | Yes                      | No                  | No                   | No   | Yes                |

| Power consumption (mW)                                       | 1.59×10-3                   | 3.94               | 0.720              | 0.22                       |                                   |                          | 3645 <sup>(h)</sup> |                      |      | 200 <sup>(h)</sup> |

| Conversion time (ms)                                         | 0.81                        | 124                | 0.5                |                            |                                   |                          | 0.45                |                      |      | 16                 |

TABLE IV

COMPARISON STUDY

OL - open-loop, CL - closed-loop, NS - not studied, NLE - non-linearity error, --- not available or not applicable. <sup>(a)</sup> Unlike the proposed scheme, this converter in [24] is not designed to provide ratio-metric output, for differential capacitive sensors. In addition, it will not automatically give a linear output for single-element sensor with inverse characteristic. <sup>(b)</sup> Simulated, not measured. <sup>(c)</sup> theoretical. <sup>(d)</sup> Resolution of the ratio-metric output in Effective Number of Bits. 12.59 corresponds to 80 fF in terms of absolute capacitance. <sup>(e)</sup> Needs one-time correction. <sup>(f)</sup> changes the pulse-width. <sup>(g)</sup>Easy to interface to new sensor as the output is not sensitive to  $C_0$ . <sup>(h)</sup> Will be much less once designed as a single IC.

as 2%), in them. (b) Excitation is derived from a simple DC reference source. (c) Since it uses switched-capacitor circuit, it is relatively easy to design and fabricate its IC. (d) Insensitive to parasitic capacitance and mismatch in values of components used. (e) Ratio-metric output for DCS and ratio output for single-element capacitive sensor. Hence a linear output is obtained independent of the sensor characteristic, and nominal capacitance. Some of the existing schemes have only some of the features of the proposed scheme as can be seen in Table IV.

The proposed design does not rely on voltage-controlled resistors to realize auto-balancing [30], [31]. Instead, a VFC, together with a switched-capacitor mechanism, effectively realizes the auto-balancing. It is important to select a VFC with sufficient linearity. VFCs with very high linearity, as the one used in the prototype, are available [36].

## VI. CONCLUSION

The design, development, and realization of a new closedloop switched-capacitor capacitance-to-frequency converter (CFC) have been presented in this paper. The developed CFC is suitable for single-element and differential capacitive sensors. The scheme provides a linear output, irrespective of the sensor characteristic being linear or inverse. The output is independent of the value of the nominal capacitance, and insensitive to the parasitic capacitances, which enhance the ease of interfacing. Thus, the presented circuit is compatible for integration with a wide variety of single and differential capacitive sensors. It uses a simple DC excitation source, as opposed to complex AC sinusoidal excitation which needs precise amplitude stabilization and very low total harmonic distortion. As the scheme is realized using switched-capacitor circuit, the presented CFC is suitable for IC fabrication. The prototype of the proposed CFC possesses desirable features such as a low maximum non-linearity error (NLE) of 0.24%, a resolution of 12.59 bits (ENOB), signal-to-noise ratio (SNR) of 77.56 dB, and rise time of 6 ms. The range of the prototype CFC developed is  $\pm 60\%$  of the nominal capacitance of the sensor. The range and measurement time can be modified by suitably selecting the frequency of clock signals, components, and ICs. The design presented specifies criteria to minimize the impact of circuit non-idealities such as input offset voltage and input bias current of opamp, and mismatch between the magnitudes of the DC reference voltages.

#### ACKNOWLEDGMENT

The authors would like to thank the Department of Science and Technology (DST), Govt. of India, for its financial assistance (Grant Number SERB/F/4573/2016-17) in carrying out the research activities presented in this paper.

#### REFERENCES

- [1] L. K. Baxter, *Capacitive Sensors. Design and Applications*. NewYork: IEEE Press, 1997.

- [2] Du, Winncy Y., Resistive, Capacitive, Inductive, and Magnetic Sensor Technologies, CRC Press, 2014.

- [3] D. Zhou, S. K. Sharma, A. Lüttgen and C. D. Sarris, "Systematic Design Optimization of Capacitive Touch Sensor Electrode Patterns," IEEE Sens. J., vol. 20, no. 4, pp. 1962-1970, 15 Feb., 2020.

- [4] A. Braun, R. Wichert, A. Kuijper, D. W. Fellner, "Capacitive proximity sensing in smart environments", Journal of Ambient Intelligence and Smart Environments, vol. 7, no. 4, pp. 483-510, 2015.

- [5] B. George, Z. Tan and S. Nihtianov, "Advances in Capacitive, Eddy Current, and Magnetic Displacement Sensors and Corresponding Interfaces," IEEE Trans. Ind. Electron., vol. 64, no. 12, pp. 9595-9607, Dec. 2017.

- [6] Y. Zhang, Z. Lin, X. Huang, X. You, J. Ye, and H. Wu, "Highly sensitive capacitive pressure sensor with elastic metallized sponge", Smart Materials and Structures, 2019 Sep 4;28(10):105023.

- [7] J. Pelegri-Sebastia, E. Garcia-Breijo, J. Ibanez, T. Sogorb, N. Laguarda-Miro and J. Garrigues, "Low-Cost Capacitive Humidity Sensor for Application Within Flexible RFID Labels Based on Microcontroller Systems," IEEE Trans. Instrum. Meas., vol. 61, no. 2, pp. 545-553, Feb. 2012.

- [8] H. Mandal, S. K. Bera, P. K. Sadhu and S. C. Bera, "Further Study of the Sensing Ring Position on the Orifice-Type Capacitive Flow Sensor," IEEE Trans. Instrum. Meas., vol. 69, no. 4, pp. 1812-1820, April 2020.

- [9] C. A. Gong, H. K. Chiu, L. R. Huang, C. H. Lin, Z. D. Hsu and P. Tu, "Low-Cost Comb-Electrode Capacitive Sensing Device for Liquid-Level Measurement," IEEE Sens. J., vol. 16, no. 9, pp. 2896-2897, May, 2016.

- [10] Y. Ik-Seok, and K. Oh-Kyong, "A touch controller using differential sensing method for on-cell capacitive touch screen panel systems." IEEE Trans. Consum. Electron. 57.3 (2011): 1027-1032.

- [11] F. Han, Z. Gao, and Y. Wang, "A differential capacitance to voltage converter for electrostatic levitation applications," *Sens. Actuators A*, *Phys.*, vol. 99, no. 3, pp. 249–255, Jun. 2002.

- [12] K. Mochizuki, T. Masuda, and K. Watanabe, "An interface circuit for high-accuracy signal processing of differential-capacitance transducers," *IEEE Trans. Instrum. Meas.*, vol. 47, no. 4, pp. 823–827, Aug. 1998.

- [13] W. Bracke, P. Merken, R. Puers, and C. Van Hoof, "Ultra-low-power interface chip for autonomous capacitive sensor systems," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 54, no. 1, pp. 130–140, Jan. 2007.

- [14] "Data sheet, Model 115C, Metal Capacitive Differential Pressures", BCM Sensor Technologies, BVBA, BELGIUM. [Online]. Available: https://www.bcmsensor.com/wp-content/uploads/2 014/12/190725\_115C\_Metal\_Capacitive\_Differential\_Pressure\_Sensor s.pdf

- [15] C. Ziqiang, H. Wang, and W. Yin, "Electrical capacitance tomography with differential sensor." IEEE Sens. J. 15.9 (2015): 5087-5094.

- [16] F. Reverter and O. Casas, "Interfacing Differential Capacitive Sensors to Microcontrollers: A Direct Approach," *IEEE Trans. Instrum. Meas*, vol. 59, no. 10, pp. 2763-2769, Oct. 2010.

- [17] S. Wang and C. Dehollain, "Design and Implementation of a Rail-to-Rail 460-kS/s 10-bit SAR ADC for the Power-Efficient Capacitance Measurement," *IEEE Trans. Instrum. Meas.*, vol. 64, no. 4, pp. 888-901, April 2015.

- [18] H. Attarzadeh and T. Ytterdal, "Low power OTA-less I-V-converter with single-ended to differential conversion for capacitive sensor interfaces," *proc. of 2013 European Conference on Circuit Theory and Design (ECCTD)*, Dresden, 2013, pp. 1-4.

- [19] L. Areekath, B. George and F. Reverter, "An Extended Study on an Interference-Insensitive Switched Capacitor CDC," *IEEE Sensors J.*, vol. 19, no. 18, pp. 8283-8292, Sept.15, 2019.

- [20] V. Sreenath and B. George, "An Improved Closed-Loop Switched Capacitor Capacitance-to-Frequency Converter and Its Evaluation," *IEEE Trans. Instrum. Meas.*, vol. 67, no. 5, pp. 1028-1035, May 2018.

- [21] V. Matko, M. Milanović, "Temperature-compensated capacitance– frequency converter with high resolution," *Sensors and Actuators A: Physical*, vol. 220, pp. 262-269, Dec. 2014.

- [22] D. Shin, H. Lee and S. Kim, "Improving the Accuracy of Capacitanceto-Frequency Converter by Accumulating Residual Charges," *IEEE Trans. Instrum. Meas.*, vol. 60, no. 12, pp. 3950-3955, Dec. 2011.

- [23] S. Malik, K. Kishore, T. Islam, Z. H. Zargar, and S. Akbar, "A time domain bridge-based impedance measurement technique for widerange lossy capacitive sensors," *Sens. Actuators A, Phys.*, vol. 234, pp. 248–262, Oct. 2015.

- [24] "Data Sheet, AD7747 24-bit capacitance-to-digital converter with temperature sensor", Analog Devices, USA, 2007.

- [25] F. Aezinia and B. Bahreyni, "Low-power, parasitic-insensitive interface circuit for capacitive microsensors," *IET Circuits, Devices & Systems*, vol. 10, no. 2, pp. 104-110, 2016.

- [26] B. George and V. J. Kumar, "Analysis of the Switched-Capacitor Dual-Slope Capacitance-to-Digital Converter," *IEEE Trans. Instrum. Meas.*, vol. 59, no. 5, pp. 997-1006, May 2010.

- [27] A. Alhoshany and K. N. Salama, "A Precision, Energy-Efficient, Oversampling, Noise-Shaping Differential SAR Capacitance-to-Digital Converter," *IEEE Trans. Instrum. Meas.*, vol. 68, no. 2, pp. 392-401, Feb. 2019.

- [28] F. Aezinia and B. Bahreyni, "An Interface Circuit With Wide Dynamic Range for Differential Capacitive Sensing Applications," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 60, no. 11, pp. 766-770, Nov. 2013.

- [29] X. Ding, K. Zhu and H. Li, "A Switch-Bridge-Based Readout Circuit for Differential Capacitance Measurement in MEMS Resonators," *IEEE Sensors J.*, vol. 17, no. 21, pp. 6978-6985, Nov.1, 2017.

- [30] A. Depari, E. Sisinni, A. Flammini, G. Ferri, V. Stornelli, G. Barile, and F. R. Parente, "Autobalancing Analog Front End for Full-Range Differential Capacitive Sensing," *IEEE Trans. Instrum. Meas.*, vol. 67, no. 4, pp. 885-893, April 2018.

- [31] G. Ferri, V. Stornelli, F. R. Parente, and G. Barile, "Full range analog Wheatstone bridge-based automatic circuit for differential capacitance sensor evaluation," *Int. J. Circuit Theory Appl.*, vol. 45, no. 12, pp. 2149–2156, 2016

- [32] K. Mochizuki, T. Masuda, and K. Watanabe, "A high-accuracy high speed signal processing circuit of differential-capacitance transducers," IEEE Trans. Instrum. Meas., vol. 47, no. 5, pp. 1244–1247, Oct. 1998.

- [33] T. Charania, A. Opal and M. Sachdev, "Analysis and Design of On-Chip Decoupling Capacitors," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 21, no. 4, pp. 648-658, April 2013.

- [34] W. Kester, "Analog switches and multiplexers," in *The Data Conversion Handbook*. New York, NY, USA: Elsevier, 2005, pp. 493–517.

- [35] "Data sheet, MAX4708/MAX4709, Fault-protected, single 8-to-1/Dual 4-to-1 multiplexers", Maxim Integr. Product Sunnyvale, CA, Dec. 2008. [Online]. Available: https://datasheets.maximintegrated.com/en/d s/MAX4708-MAX4709.pdf

- [36] "Datasheet, ADVFC32, Voltage-to-Frequency and Frequency-to-Voltage Converter", Norwood, MA: Analog Devices, Inc. [Online]. Available: https://www.analog.com/media/en/technicaldocumentation/data-sheets/ADVFC32.pdf

- [37] "Datasheet, The integrating A/D converter (ICL 7135)," Intersil Americas Inc., Milpitas, CA, USA, Appl. Note AN017, 2002. [Online]. Available: http://www.intersil.com/data/an/an017.pdf.

- [38] L. Xu, S. Sun, Z. Cao, W. Yang, "Performance analysis of a digital capacitance measuring circuit", Review of Scientific Instruments. 2015 May 15;86(5):054703.

- [39] G. Scotti, S. Pennisi, P. Monsurrò and A. Trifiletti, "88µA 1-MHz Stray-Insensitive CMOS Current-Mode Interface IC for Differential Capacitive Sensors," IEEE Trans. Circuits Syst. I: Reg. Papers, vol. 61, no. 7, pp. 1905-1916, July 2014.