# Multi-port Interline Current Flow Controller for Meshed HVDC Grids

Joan Sau-Bassols, *Student Member, IEEE*, Ricard Ferrer-San-José, *Student Member, IEEE*, Eduardo Prieto-Araujo, *Member, IEEE*, and Oriol Gomis-Bellmunt, *Senior Member, IEEE*

Abstract-In meshed High Voltage Direct Current (HVDC) grids, the current of each line cannot be controlled independently, since it depends on the resistances between nodes. Additional devices, such as Current Flow Controllers (CFCs), may be needed to avoid bottlenecks or line overloads. This work presents a multi-port DC/DC based CFC topology to be connected to n lines with unidirectional current flows. The device is able to control the DC lines' currents to the desired value by inserting variable voltage sources in series. First, the modelling of the generic *n*-port topology is presented and then, its modulation and control strategy are described. In the first case study, the concept is validated considering a 5-port CFC by means of dynamic simulations using different control methods. Finally, in the second case study, a 3-port CFC prototype is built and tested in an experimental platform in the laboratory considering different control modes.

*Index Terms*—Multi-port, Current Flow Controller, Meshed HVDC grid, Power Flow Control, DC/DC converter, CFC prototype.

### I. INTRODUCTION

**I** N the last years, many Voltage Source Converter based High Voltage Direct Current links (VSC-HVDC) have been installed as a means of transmitting large amounts of power over long distances [1]. Their advantages lie in the possibility to control active and reactive power independently, the black-start capability and a reduced footprint compared to Line Commutated Converter (LCC) based HVDC [2]. Among VSC, Modular Multilevel Converters (MMCs) are seen as the key technology due to their modularity and reduced filter requirements [3], [4], [5]. Interconnecting the already built HVDC links and forming a Multi-terminal or Meshed HVDC grid can increase the flexibility and redundancy of the system [6], [7]. Nevertheless, this comes at a cost, since in meshed grids, the power flows cannot be controlled independently for each line, but are determined passively by the resistances between nodes. This may lead to uncontrolled power flows that can create overloads or bottlenecks in the lines, thus restricting the overall operation of the HVDC network. In order to overcome this challenge, additional devices might be installed on the HVDC grid to regulate the power flows [6]. Those devices based on power electronics are named Power Flow Controllers (PFC) or Current Flow Controllers (CFC) and are the equivalent to Flexible Alternating Current Transmission Systems (FACTS) for HVDC grids [8], [9].

The operation of the CFCs is based on inserting variable voltage sources in series with the lines that modify their effective impedance, and by doing so, they can regulate the currents that are circulating through them [9]. The number of CFC topologies that can be found in the literature is increasing,

and they can be gathered in three major groups: Variable resistances, AC/DC converters and DC/DC converters. Variable resistances are a simple solution but they have the disadvantage of increasing the losses of the system [10]. AC/DC converters apply voltages on the DC lines by exchanging power with the AC grid, which requires an insulation transformer that can augment the cost of the device [11], [12]. DC/DC converter based CFCs are connected between DC lines and they can regulate the current flows by exchanging power inside the DC grid [13]-[25]. The behaviour of the DC/DC based CFCs during faults in the HVDC grid is investigated in [17], [26] providing some countermeasures to protect the devices. Also, the integration of the CFC capabilities into the DC Circuit Breakers (DCCB) [27] is analysed in [28], [29] in order to have two functionalities in a single device, thus, reducing the total cost. Finally, some research has been done trying to identify multi-port DC/DC topologies to be connected to any number of lines [24], [25]. The experimental validation of some CFC topologies has been presented in [17], [19], [25].

This paper presents a *n*-port DC/DC based CFC topology for unidirectional current flows, which represents the generalisation of the converter introduced in [20], [21] for *n* lines. The concept brings the advantage of a simplified circuit compared to other topologies, especially attractive for distributed approaches [23] where more than one simple CFC is installed and are selectively operated according to the overload location, at the expense of being able to operate only with unidirectional current flows. The modelling of the converter is provided and its average model derived for a generic number n of lines. Then, the modulation and control strategy of the converter are also described, presenting different control methods to operate the CFC. After, Case Study 1 presents the dynamic simulation results of two 5-port CFCs based on the presented topology, one located on the positive pole and the other on the negative pole of a symmetric monopole 5-terminal meshed HVDC grid. Considerations regarding CFC losses, AC voltage ripples and bypass and protection are also included. Finally, in Case Study 2, an experimental prototype of a 3-port CFC is built and tested in an experimental platform in the laboratory, which represents a scaled down symmetrical monopole HVDC grid with three terminals. For the experimental validation, different control modes of the CFC are also tested.

# II. MULTI-PORT CURRENT FLOW CONTROLLER

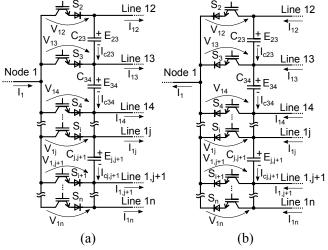

This work presents a multi-port CFC topology, which is able to control the DC current through the lines where it is connected. The topology is meant for unidirectional current flows and it is based on the 3-port concept introduced in [20], [21] but extended to n lines. The two CFC structures are presented in Fig. 1, depending on the direction of the currents. In Fig. 1(a), it is assumed that the total current goes into the CFC from Node 1 and then it is distributed between the other lines. On the other hand, Fig. 1(b) considers that the currents through the lines enter into the the CFC and the total amount goes out to Node 1.

Fig. 1. Scheme of the multi-port CFC topology located in Node 1 and connected to n-1 lines. (a) DC currents circulating from Node 1 to the other lines. (b) DC currents circulating to Node 1 coming from the other lines.

As shown in Fig. 1, taking n as the number of lines where the converter is connected to, its structure is made of n-1 switches and n-2 capacitors. The switches require reverse blocking voltage capability and the capacitors must allow positive and negative voltage polarity for the adequate operation of the converter. For this work, Insulated Gate Bipolar Transistors (IGBTs) with a diode connected in series are assumed to obtain the reverse blocking voltage capability, though other options can be applicable [20].

#### **III. CONVERTER MODELLING**

For simplicity, the following work derives the model of the converter based on the structure of Fig. 1(a), however, the derivation is analogous for the structure in Fig. 1(b). The procedure is the same as the one applied in [15], [20] but for a generic *n*-port CFC.

### A. Operating Principle

In order to allow a path for the current, there must be always a switch in ON state and it is assumed that only one of them is in ON state at a time. Based on this, the following equation is obtained: n

$$\sum_{i=2}^{n} t_{Si} = T \tag{1}$$

where  $t_{Si}$  is the time that switch *i* is in ON state and *T* is the period of the switching frequency of the converter. Transforming the previous expression to duty cycles, yields to: *n*

$$\sum_{i=2}^{n} D_i = 1 \tag{2}$$

where  $D_i$  is the duty cycle of switch *i*.

For instance,  $D_i = 1$  implies that switch *i* remains in ON state all the period. Analysing Fig. 1(a) under this situation, initially the current from Node 1 flows through the switch *i* and then is distributed through all the lines. The current finds no obstacle through the line connected to switch  $S_i$ , but regarding the other lines, the current charges the capacitors and increases their voltage. Whenever the voltages of the capacitors are high enough to block the currents through the other lines, the steady-state is reached and  $I_1$  flows entirely through the line connected to switch  $S_i$ .

In order to bypass the device without using external switches, which are required for bypassing permanently the converter [20], the procedure consists on turning ON all the switches. By doing this, the voltage of the capacitors goes to zero and the converter is not applying any effect on the DC grid currents.

Assuming that the line currents remain constant for the following analysis, when one of the switches is in ON state, a voltage between Node 1 and the other lines is applied and it is dependent on the voltage of the capacitors at that time. The subscript i is used to identify the switch that is in ON state and the subscript j refers to the Node j that is connected to the CFC through line 1j. The following equations describe the voltage between Node 1 and line 1j, assuming no voltage drops on the switches:

$$V_{1j} = 0$$

,  $i = j$  (3)

$$V_{1j} = \sum_{k=i}^{j-1} E_{k,k+1} , \qquad i < j$$

(4)

$$V_{1j} = \sum_{k=j}^{i-1} -E_{k,k+1} , \qquad i > j$$

(5)

The current that circulates through each capacitor is given by (6) and (7). n

$$I_{c_{j,j+1}} = \sum_{k=j+1} I_{1k} , \qquad i \le j$$

(6)

$$I_{c_{j,j+1}} = \sum_{k=2}^{J} -I_{1k} , \qquad i > j$$

(7)

where, *i* defines the switch that is ON and and *j* is used to name the lines 1j and 1, j+1 where the capacitor is connected. In order to have each capacitor balanced, the equation that must be met for each capacitor between lines 1j and 1, j+1 is:

$$\sum_{i=2}^{n} \frac{t_{Si}}{T} I_{c_{j,j+1}} = 0 , \qquad \forall j \le n-1$$

(8)

and considering the duty cycles of the switches:

$$\sum_{i=2}^{n} D_i I_{c_{j,j+1}} = 0 , \qquad \forall j \le n-1$$

(9)

Then, by combining (6), (7) and (8), it is possible to obtain:

$$D_i = \frac{I_{1i}}{\sum_{i=2}^n I_{1i}} , \qquad \forall i \le n \tag{10}$$

Based on (10), imposing a duty cycle drives the system to achieve a certain current relation in order to have the CFC capacitors balanced, as it was also reported for the 3-port CFC topology presented in [20]. Then, when a certain duty cycle is applied, the capacitors will achieve the CFC voltage that provides the corresponding current relation.

From the previous analysis, the ripple of each CFC capacitor can be obtained and corresponds to:

$$\Delta E_{j,j+1} = \frac{\sum_{k=2}^{j} I_{1k} (I_1 - \sum_{k=2}^{j} I_{1k})}{f C_{j,j+1} I_1} , \qquad \forall j \le n-1 \quad (11)$$

The previous equation provides a criterion to select the switching frequency and the capacitance of the capacitors in the CFC.

The rated voltage value of the CFC capacitors depends on the required voltage to provide current changes. Then, if a higher voltage is allowed in the capacitor, the CFC will be able to apply higher voltages in series, which provides a further increase in the operational area of the system [15]. It is a trade-off between voltage rating of the equipment and CFC capability.

#### B. Modulation strategy

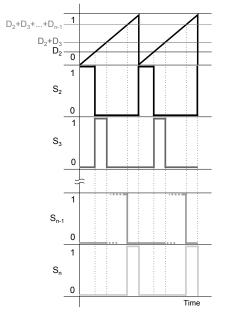

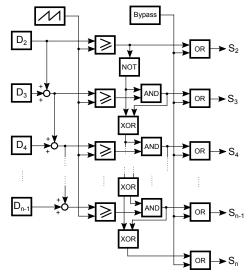

According to (10), imposing a duty cycle defines the current relation between the corresponding line and the total current from Node 1. Based on this, it is possible to control DC currents by assigning a duty cycle to each switch according to the desired current of that line. Fig. 2 presents the generalised modulation strategy for a *n*-port CFC. As shown in Fig. 2, the signals sent to each switch are time-consecutive in a way that always one of the switches is in ON state. The time that the signal has a value of 1 is proportional to the duty cycle of that switch. For the real implementation of the converter, negative dead-times are required so that there is always a path for the current through the converter [20]. The logic implemented to

Fig. 2. Modulation strategy applied to the *n*-port CFC.

obtain the desired signals according to Fig. 2 is illustrated in Fig. 3. Using this approach and according to (2), it is possible to see that the *n*-port CFC has n - 2 degrees of freedom since when  $D_2$  to  $D_{n-1}$  have been set,  $D_n$  achieves a certain value to guarantee a path for the current at any time. Other modulation and control strategies can be studied where more than one switch can be ON at the same time. Nevertheless,

Fig. 3. Modulation implemented with logic blocks for a *n*-port CFC.

this work presents the previous modulation in order to provide an intuitive control of the converter, where each duty cycle is directly related to the current value of a certain line.

### C. Average model

As illustrated in Section III-A, when one of the switches is in ON state, a certain voltage, which is dependent on the actual voltage values of the CFC capacitors, is applied on the lines. Then, knowing the time that each switch is conducting, given by the duty cycle, it is possible to obtain the average voltage applied to each line as a function of the CFC capacitor voltages and the duty cycles of the switches:

$$\overline{V}_{1j} = \sum_{i=2}^{n} D_i V_{1j} , \qquad 2 \le j \le n$$

(12)

And using (3)-(5) yields to:

$$\overline{V}_{1j} = \sum_{i=2}^{j-1} D_i \sum_{k=i}^{j-1} E_{k,k+1} - \sum_{i=j+1}^n D_i \sum_{k=j}^{i-1} E_{k,k+1} , \quad 2 \le j \le n$$

(13)

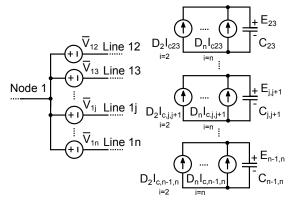

Fig. 4 illustrates the average model of the *n*-port CFC where a variable voltage source is placed between Node 1 and each line. An additional circuit is introduced for each capacitor in the CFC, which is composed of a capacitor and several current sources in parallel that represent the charging and discharging of the capacitors of the CFC due to the DC line currents. The analytic expression of  $\overline{V}_{1j}$  and  $I_{cj,j+1}$  can be obtained from (6), (7) or (13).

# D. Control methodology

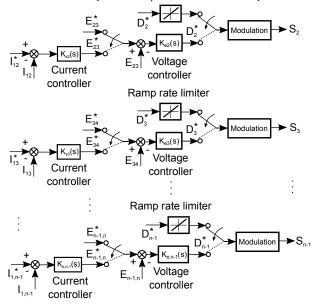

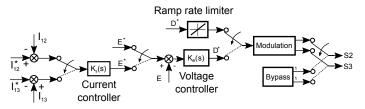

According Section III-A, the DC currents circulating through the *n*-port CFC can be controlled by imposing the corresponding duty cycle  $D_j$ . Nevertheless, in order to have a closed-loop control of the current and maintain the voltage of the capacitors under certain limits, the following control methodology is presented (see Fig. 5), which is based on the control scheme introduced in [20] for the 3-port CFC.

Based on the average model in Fig. 4, each voltage  $\overline{V}_{1j}$  depends on the voltage of the capacitors and the duty cycles

Fig. 4. Average model of the *n*-port CFC made of n-1 voltage sources and n-2 circuits with a capacitor **Reating rate: limite** sources in parallel.

Fig. 5. Control methodology for *n*-port CFC topology with n - 2 controller schemes.

applied to the switches. Each duty cycle  $D_j$  is associated to the current of line 1j and n-2 currents can be regulated independently, which correspond to the number of CFC capacitors and each of the controller schemes in Fig. 5.

Four control methods are included in the methodology as Fig. 5 shows: CFC bypass (included in the Modulation); direct control of the duty cycle through a ramp limiter; voltage control of each of the capacitors in the CFC; and a current controller in cascade with the voltage controller to regulate the line currents and at the same time maintaining the CFC voltages under the ratings.

By using the voltage control (left switch in the upper position and right switch in the lower position), it is possible to regulate the capacitor voltage to the desired value,  $E_{j,j+1}^*$ . However, by using this method, there is no control of the corresponding line current since the current controller of the corresponding control scheme is not used. If the left switch is in the lower position, the current controller is used and then, the voltage reference for the capacitor,  $E_{j,j+1}^*$ , cannot be freely chosen, as it achieves the value required to impose the desired line current. By introducing a saturation limit in the current controller it is possible to maintain the voltage of the capacitor below the threshold.

# IV. BYPASS AND PROTECTION CONSIDERATIONS

Due to the unidirectional nature of the *n*-port CFC considered in this work, additional protection equipment must be installed to allow bidirectional current flows through the CFC device and prevent overvoltages and overcurrents.

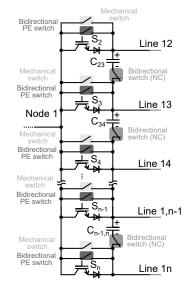

Based on the protection equipment for the 3-port CFC presented in [20], an extended protection scheme is outlined for the *n*-port CFC device, which is depicted in Fig. 6. Although this represents an increase in the number of switches

Fig. 6. Additional protection equipment for the unidirectional *n*-port CFC topology.

required for the implementation of the multi-port CFC, such protection equipment or a similar one may be also needed for bidirectional multi-port CFCs; since the normal operation switches may not be rated for the fault current, requiring then, another path to divert the current [26].

In parallel with each switch  $S_i$ , two switches are added: a Bidirectional switch based on Power Electronics (PE), to be able to switch ON fast, and a Mechanical switch that allows the bypassing of the CFC with low losses with slower turn ON. Also, in series with each capacitor, a Normally Closed (NC) switch is included to avoid the short-circuit of the capacitor when the aforementioned bidirectional switches are turned ON.

The procedure to bypass the CFC when abnormal situations happen is as follows: first, the NC switches should be opened in order to isolate the capacitors and must be coordinated with the CFC switches  $S_i$ , which should be turned ON to allow always a path for the current. Then, the first set of bidirectional PE switches can be activated without short-circuiting the capacitors. The second set of Mechanical switches (with slower turn ON time and lower losses) can be then closed to provide a path for the current with less losses. The previous switches can also be used to maintain the CFC in bypass mode if its operation is not required and allow any current flow in the HVDC grid.

Additionally, the possibility of integrating the CFC capability into DCCBs can be considered, as well for the multi-port CFC. This concept allows to have a single device that can interrupt both DC faults and also has CFC capability, which has been studied for a 3-port CFC in [28].

## V. CASE STUDY 1: SIMULATIONS OF A 5-PORT CFC

#### A. System description

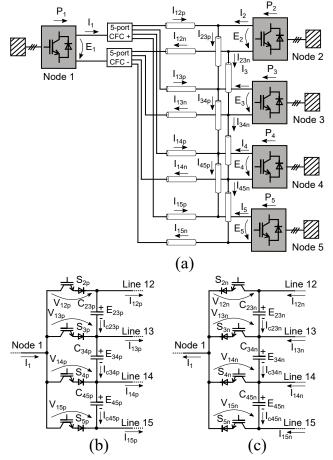

This case study considers a 5-terminal meshed HVDC grid as the one illustrated in Fig. 7(a). Two 5-port CFCs are installed in Node 1, one in the positive pole and the other in the negative pole. Both converters are shown, respectively, in Fig. 7(b) and 7(c), and their switching model is used for the simulations. Node 1 operates as a slack bus keeping constant the DC voltage and the remaining nodes perform power control. The cables of the DC grid are modelled using two sections of the parallel series branches model proposed in [30], whose parameters are obtained from [31], both model and parameters are the same ones as in [20]. Tables I and II depict the parameters of the HVDC grid and the 5-port CFC.

Based on (11), the capacitance of the capacitors in the 5-port CFC is selected imposing a maximum ripple in its voltage. The switching frequency is set at  $f_{sw} = 2$  kHz and the maximum ripple is defined to be 250 V, which represents 0.0625 pu of the nominal CFC voltage. Considering, then a capacitance of 1.1 mF for all the capacitors, the maximum expected ripple is 248.59 V, assuming the nominal value of  $I_1$  is 2187.5 A.

Fig. 7. Scheme of a 5-terminal meshed HVDC grid with two 5-port CFCs considered for the dynamic simulation. (a) 5-terminal HVDC grid (b) Scheme of the 5-port CFC of the positive pole. (c) Scheme of the 5-port CFC of the negative pole.

TABLE I HVDC grid parameters

| Parameters of the meshed HVDC grid            |        |     |     |      |       |       |      |

|-----------------------------------------------|--------|-----|-----|------|-------|-------|------|

| Cable <i>i j</i>                              | 12     | 13  | 14  | 15   | 23    | 34    | 45   |

| Distance d <sub>ij</sub> [km]                 | 100    | 150 | 150 | 150  | 100   | 200   | 150  |

|                                               | Node i |     | 1   | 2    | 3     | 4     | 5    |

| Power reference $P_i^*$ [MW]                  |        |     | -   | -500 | - 300 | - 500 | -100 |

| Voltage reference $E_1^*$ [kV]                |        |     | 320 | -    | -     | -     | -    |

| VSC time constant of power loop $\tau_i$ [ms] |        |     | ] - | 100  |       |       |      |

|                                               |        |     |     |      |       |       |      |

TABLE II CFC parameters

| Parameters of the CFCs              |    |     |    |

|-------------------------------------|----|-----|----|

| CFC between lines $ij$ (+ & – pole) | 23 | 34  | 45 |

| Rated voltage $E_{cfc}$ [kV]        | :  | ±4  |    |

| CFC capacitance $C_{ij}$ [mF]       |    | 1.1 |    |

| Switching frequency $f_{sw}$ [Hz]   |    | 000 |    |

The average voltages applied on the lines by the 5-port CFC in the positive pole, according to (13) are:

$$V_{12} = -D_3 E_{23} - D_4 (E_{23} + E_{34}) - D_5 (E_{23} + E_{34} + E_{45})$$

(14)

$$\overline{V}_{13} = D_2 E_{23} - D_4 E_{34} - D_5 (E_{34} + E_{45})$$

(15)

$$\overline{V}_{14} = D_2(E_{23} + E_{34}) + D_3 E_{34} - D_5 E_{45}$$

(16)

$$\overline{V}_{15} = D_2(E_{23} + E_{34} + E_{45}) + D_3(E_{34} + E_{45}) + D_4E_{45}$$

(17)

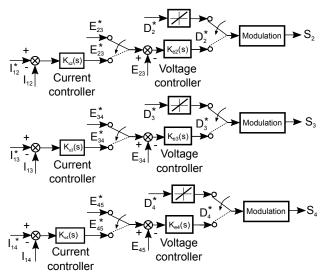

Fig 8 illustrates the controller schemes used to control the 5-port CFCs and the parameters of the controllers are shown in (18) and (19), which are obtained following the same methodology than in [20].

Fig. 8. Controller schemes applied to the 5-port CFCs of the positive and negative poles.

$$K_{ej}(s) = \left(\frac{0.004s + 0.4}{s}\right) \left(\frac{0.01s^2 + 0.08s + 0.85}{s^2 + 48.35s + 151.8}\right)$$

(18)

$$K_{sj}(s) = \left(\frac{2s+10}{s}\right) \tag{19}$$

# B. Simulation results

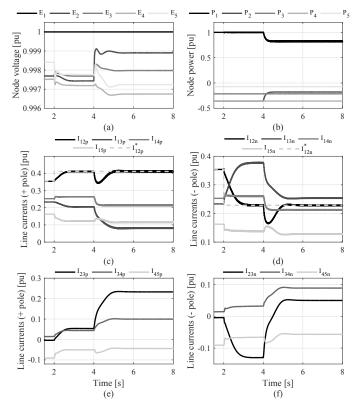

Figs. 9-13 show the simulation results of the 5-port CFCs in the meshed HVDC grid. For this case study, the controller schemes implemented are validated as explained below considering current control, voltage control and duty cycle setting.

The currents circulating through lines 12 in both poles are controlled in closed-loop using the current and voltage controller in cascade. The voltages of the capacitors  $E_{34p}$ and  $E_{34n}$  are regulated to show the capability of the CFC to directly control the voltage according to a reference value. Finally, regarding the currents of lines 14, their duty cycle  $D_4$  is imposed, which represents an open-loop control of the percentage of current that flows through both lines.

Initially, before instant t = 2 s, the CFCs are bypassed with all the switches in ON state. The duty cycle of the switches in those conditions, Neutral Duty Cycle (NDC), can be obtained from measuring the currents through each line and applying (10). Then, the NDCs are used to initialise the controllers to provide a smooth start-up of the converter [20].

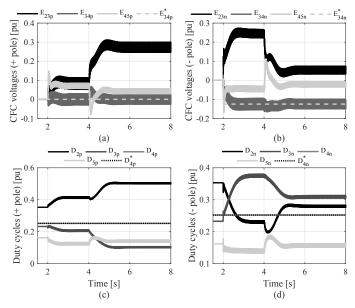

After t = 2 s, step changes in the current reference of  $I_{12p}$  and  $I_{12n}$ , and the voltage reference of  $E_{34p}$  and  $E_{34n}$ are introduced.  $D_{4p}$  and  $D_{4n}$  are kept at the same value. The CFCs start to control the current to the desired value (see Figs. 9(c) and 9(d)). The target values are achieved after a transient and the voltages of the capacitors are modified to provide such a change (see Figs. 10(a) and 10(b)). At the same time, the two voltage references  $E_{34p}$  and  $E_{34n}$  are achieved in a faster transient as shown in Figs. 10(a) and 10(b). Meanwhile, the same duty cycles,  $D_{4p}^*$  and  $D_{4n}^*$ , are sent to the switches maintaining approximately the same current through lines 14 in both poles, and the currents circulating through 15 are adapted accordingly to the remaining current of Node 1.

At instant t = 4 s, a reduction of the 50% of the power in Node 2 happens. Both CFCs are able to maintain the current value at the reference after a transient (see Figs. 9(c) and 9(d)) and the voltage controller also keeps the voltages  $E_{34p}$  and  $E_{34n}$  to the target value. In this case, the setting of  $D_{4p}$  and  $D_{4n}$  at the same value as before induces a current reduction in both lines since the total current in Node 1 has been reduced.

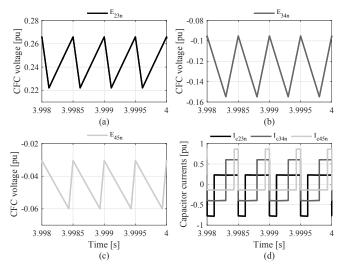

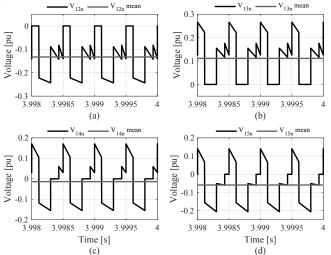

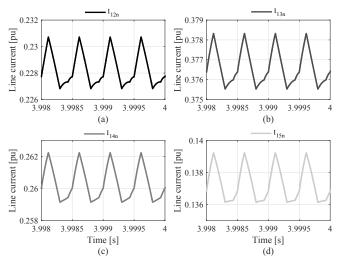

Finally, the detail of the capacitor voltages, the voltages applied on the lines by the CFCs and the line currents are shown in Figs. 11, 12 and 13, respectively.

*C. Losses calculation* In this Section, the losses of the 5-port CFC located at the negative pole at instant t = 4 s are calculated. According to the voltage rating of the CFC, six IGBTs in series with the corresponding diodes are used to obtain the switches of the converter. The parameters of the IGBTs and diodes used for the calculations are obtained from the ABB StakPack [32] and the switching frequency is f = 2 kHz. Besides, the losses due to the resistances in the lines of the negative pole assuming no AC ripple in the current and with the ripple occasioned by the CFC operation are calculated. Table III illustrates the previous results. The losses of the CFC are in the order kW and the conduction losses are higher than the switching losses for the given instant. It can be seen that the AC ripple in the line currents have low effect on the line losses.

Fig. 9. Simulation results. (a) Node voltages. (b) Node powers. (c) First set of line currents in the positive pole. (d) First set of line currents in the negative pole. (e) Second set of line currents in the positive pole. (f) Second set of the line currents in the negative pole.

Fig. 10. Simulation results. (a) Voltages of the capacitors in the CFC on the positive pole. (b) Voltages of the capacitors in the CFC on the negative pole. (c) Duty cycles of the CFC in the positive pole. (d) Duty cycles of the CFC in the negative pole.

#### D. AC ripple consideration

From the previous results, it is possible to see that the operation of the 5-port CFC introduces an AC voltage in series with the lines, with a certain mean value that allows the current control. This AC voltage produces an AC ripple in the currents circulating through the lines where the CFC is

Fig. 11. Detail of the voltages of the capacitors in the CFC on the negative nole

Fig. 12. Detail of the voltages applied by the CFC on the negative pole (actual and mean value) in each line.

Fig. 13. Detail of the currents circulating through lines 12, 13, 14 and 15 in the negative pole.

connected. In the previous results (see Fig. 13), the AC current ripple corresponds to a maximum value around 0.004 pu.

Nevertheless, if the number n is increased, more capacitors

TABLE III LOSSES CALCULATION

|                  |       | Line losses    |         | Line losses   |         |  |

|------------------|-------|----------------|---------|---------------|---------|--|

| CFC losses       |       | No ripple      |         | AC ripple     |         |  |

| $P_{sw}$ [kW]    | 6.04  | $P'_{12}$ [kW] | 238.877 | $P_{12}$ [kW] | 238.922 |  |

| $P_{cond}$ [kW]  | 67.67 | $P'_{13}$ [kW] | 975.106 | $P_{13}$ [kW] | 975.140 |  |

| $P_{total}$ [kW] | 73.71 | $P'_{14}$ [kW] | 465.888 | $P_{14}$ [kW] | 465.937 |  |

|                  |       | $P'_{15}$ [kW] | 129.558 | $P_{15}$ [kW] | 129.611 |  |

are included in the *n*-port CFC. In such a situation, and specially if the capacitors are charged close to the nominal voltage, the instant voltage applied in series with the lines can be the sum of all capacitor voltages plus the ripple in each capacitor, in the worst case scenario.

In those conditions the *n*-port may require additional filters, such as inductors in series with the lines in order to reduce the impact of the AC ripple. Assuming that the CFC is located in a meshed HVDC grid where DCCBs are expected to be installed, the inductors used in the DCCBs can be used as well to provide the inductance in series.

Another strategy to reduce the impact of this issue can be the modification of the modulation strategy for large n values. For this work, a modulation approach based on a single switch in ON state at any time is applied. Nonetheless, other strategies where more than one switch is in ON state can be considered to deal with this effect, preventing the sum of the voltage of all capacitors to be applied in series with the lines.

# VI. CASE STUDY 2:

#### EXPERIMENTAL VALIDATION OF A 3-PORT CFC

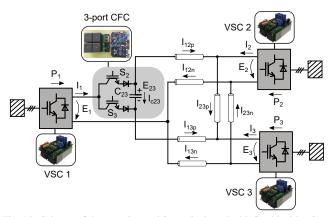

## A. System description

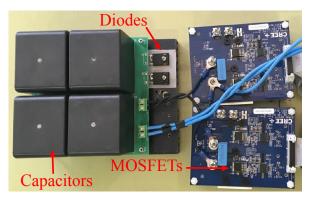

A 3-port CFC prototype for low voltage is built to provide a validation of the simulation models and is tested in an experimental platform illustrated in Fig. 14. The platform represents a DC grid composed of three terminals connected via the DC side forming a meshed DC grid. Each terminal consists of a cabinet as shown in Fig. 15, which contains an AC transformer, a two-level three-phase VSC with its control board and several measuring boards and data acquisition systems. The cables of the DC grid are physically emulated using a resistance and an inductance. The 3-port CFC is installed at the positive pole in Node 1, at the DC output of the cabinet and is depicted in Fig. 16. The device is made of two SiC MOSFETS included in two evaluation boards from CREE. The two SiC MOSFETs are then connected to the the PCB that contains the diodes and the capacitors of the CFC.

Table IV, V and VI show the parameters of the VSC, the DC lines and the CFC, respectively.

TABLE IV VSC parameters

| Parameter           | Value | Unit |

|---------------------|-------|------|

| DC voltage          | ±250  | V    |

| Nominal power       | 5.7   | kW   |

| AC voltage (1-1)    | 230   | Vrms |

| AC inductors        | 1.6   | mH   |

| DC capacitance      | 1020  | μF   |

| Switching frequency | 20    | kHz  |

Fig. 14. Scheme of the experimental 3-terminal meshed DC grid with a 3-port CFC in the laboratory.

Fig. 15. Image of the experimental platform, including the CFC and the three VSCs. TABLE V

DC LINE PARAMETERS

| Parameter                                  | Value | Unit |

|--------------------------------------------|-------|------|

| Resistance lines 12: $R_{12p}$ , $R_{12n}$ | 3.2   | Ω    |

| Resistance lines 13: $R_{13p}$ , $R_{13n}$ | 0.4   | Ω    |

| Resistance lines 23: $R_{23p}$ , $R_{23n}$ | 0.7   | Ω    |

| Inductance lines 12: $L_{12p}$ , $L_{12n}$ | 2.5   | mH   |

| Inductance lines 13: $L_{13p}$ , $L_{13n}$ | 1.22  | mH   |

| Inductance lines 23: $L_{23p}$ , $L_{23n}$ | 1.5   | mH   |

TABLE VI CFC parameters

| Parameter                 | Value | Unit |

|---------------------------|-------|------|

| Rated CFC voltage         | ±20   | V    |

| Rated DC current          | 11.4  | А    |

| CFC capacitance: $C_{23}$ | 1000  | μF   |

| Switching frequency       | 2     | kHz  |

Fig. 16. Detail of the CFC converter.

A monitoring system based in National Instruments (NI) Labview is also implemented in the experimental platform that acquires data regarding the DC voltages and currents of the DC grid. A NI cRIO 9024 controller is used to collect the data and send it to the monitoring PC.

#### B. Control of the converters

Each of the VSCs of the scaled laboratory set up is controlled using a Digital Signal Processor (DSP) F28M35 of Texas Instruments (TI). Each VSC operates in voltage *droop* control [33], and uses the classic vector control in the dq reference frame for the current loop [33].

The control of the CFC is implemented in the same control board as VSC 1 and its scheme is illustrated in Fig. 17, which is based on the one proposed in [20] for the 3-port CFC structure. As it can be seen in Fig. 17, the CFC has four control modes implemented: It can be bypassed, with both  $S_2$  and  $S_3$  in ON state; the duty cycle of both switches can be controlled directly using a ramp limiter; the CFC can also perform voltage control, by regulating the voltage of its capacitor; and finally, a current control of the DC lines is also implemented with an outer current controller and an inner voltage controller to limit the voltage that the CFC is applying.

Fig. 17. Control scheme of the experimental 3-port CFC.

# C. Experimental results

For all the tests performed in this section, the power that is being injected into the DC grid by VSC 1 is 4.7 kW and the powers extracted from the DC grid by VSC 2 and 3 are 2.1 kW and 2.3 kW, respectively.

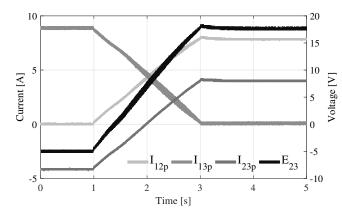

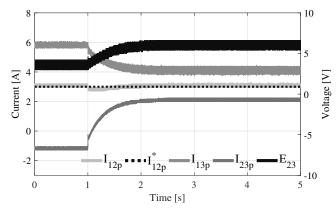

1) Open-loop control: Fig. 18 and 19 depict the results considering the open-loop control of the CFC where the duty cycle reference is given to the switches through a ramp rate limiter to avoid voltage and current transients.

At the beginning of the test, the duty cycle  $D_2$  is zero, which implies that  $S_2$  is OFF and  $S_3$  is ON. All the current  $I_1$ circulates through  $S_3$  and line 13, and the capacitor is charged negatively. Then, the duty cycle reference changes from 0 to 1. This variation is applied through a ramp, and at the end the capacitor gets charged at 18 V and the current of line 13 is totally diverted into line 12.

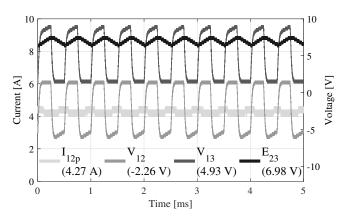

Fig. 19 depicts current  $I_{12p}$  and the voltages that the CFC is applying on the grid for a constant duty cycle of  $D_2 = 0.5$ . It can be seen that the voltage across the CFC capacitor,  $E_{23}$ , is a triangular waveform, showing the charge and discharge of the capacitor when the CFC is switching. The voltages applied on the lines are illustrated also in Fig. 19, showing that whenever the corresponding switch of the line is in ON state, the voltage is almost zero and when it is OFF, the voltage applied is the the voltage of the CFC capacitor (in positive or negative polarity depending on the switch). For such a low

Fig. 18. Experimental results considering a ramped change of the duty cycle of the CFC in open-loop: Line currents and CFC voltage.

scale platform, the voltage drops across the switches play an important role as their value is considerable, around 1.5 V, as it was also reported in [17]. The average values of  $V_{12}$  and  $V_{13}$  correspond to the expressions  $(1 - D_2)E_{23}$  and  $-D_2E_{23}$ , respectively, where its value is highly affected by the voltage drop. The mean values of the variables on the graphic are depicted below the legend.

Fig. 19. Experimental results considering a constant duty cycle of  $D_2 = 0.5$  in open-loop: Current  $I_{12p}$  and voltages applied by the CFC on the lines.

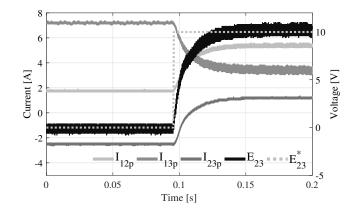

2) *Closed-loop with voltage control:* Fig. 20 illustrates the results using the voltage controller to regulate directly the voltage across the capacitor of the CFC.

Fig. 20 shows the results considering a closed-loop control for the CFC, where the voltage reference,  $E_{23}^*$  is given to the voltage controller whose output is the duty cycle of the switches. Initially, the voltage reference is zero, which means that the CFC is operating with the NDC [20], so that, it does not apply any change in the currents. Then, the voltage reference is changed to 10 V and the CFC achieves this value after 40 ms following a first order system response. Due to the charging of the capacitor, voltages are applied in series with the lines, which provokes a certain change in the line currents.

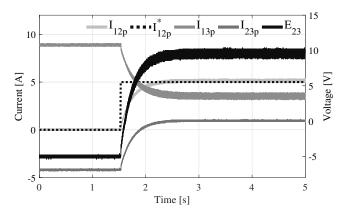

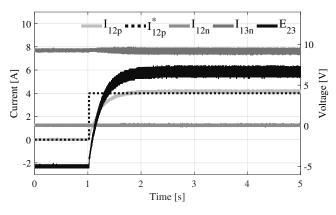

3) Closed-loop with current control: Finally, the closed-loop current control of the CFC is tested and the results can be seen in Figs. 21, 22 and 23. This control scheme includes an outer current controller and an inner voltage controller as it is shown in Fig. 17.

Fig. 20. Experimental results considering a voltage step change in closed-loop using the voltage controller: Line currents and CFC voltage.

Fig. 21 shows a current step change in current  $I_{12}$ , where initially, the current through line 12 is zero, and then achieves a value of 5 A. The CFC voltage also changes its value and is charged up to 10 V.

Fig. 21. Experimental results considering a current step change in closed-loop using the voltage and current controllers: Line currents and CFC voltage.

In Fig. 22, the current of line 12 is being controlled to 3 A, when, the power reference of VSC 2 goes from 2.5 kW to zero. The *droop* control implemented in each VSC compensates the unbalance in power, so that the powers from VSC 1, VSC 2 and VSC 3, end up being -3.9 kW, 0.5 kW and 3.1 kW, respectively. The line currents change their values according the new power flow, yet the CFC is able to maintain the current regulation of line 12 to 3 A, after the transient. It is possible to see in Fig. 22, that the voltage of the capacitor achieves a higher value to keep the current to the same level.

Fig. 23 is meant to illustrate the effect that the CFC located on the positive pole exerts on the negative pole of the grid.

The current  $I_{12p}$  is regulated at 4 A, and the capacitor charges up to 7.5 V to provide such change. The currents through the negative pole,  $I_{12n}$  and  $I_{13n}$  are not affected while the CFC is changing the currents in the positive pole. Only a small increase in the ripple of current  $I_{13n}$  can be observed due to the CFC operation.

#### VII. CONCLUSION

This paper has presented a multi-port CFC for unidirectional current flows that can be connected to n lines. It can regulate

Fig. 22. Experimental results with current control and changes in the power of the nodes: Line currents and CFC voltage.

Fig. 23. Experimental results considering a current step change in closedloop using the voltage and current controllers: Line currents of the positive and negative pole and the CFC voltage.

the current through those lines in order to prevent overloads by charging and discharging the CFC capacitors. The modulation and control strategy for a n-port CFC have been presented and a 5-port CFC is validated using dynamic simulations considering different control mehtods. The simulations show how the CFCs located on the positive and negative poles can regulate the currents, independently, according to the references and under power changes in the nodes of the HVDC grid. Considerations regarding the protection and the effect of the AC voltages generated by the device if n is high have also been introduced. A scaled down 3-port CFC has been built and tested in a experimental platform in the laboratory. The tests shown that the CFC can be bypassed, operated in open-loop, performing voltage control and current control. It can also keep the current control during power changes in the nodes of the DC grid and if installed in the positive pole can only affect the currents of the positive pole.

#### REFERENCES

- D. Van Hertem, O. Gomis-Bellmunt and J. Liang, *HVDC Grids: For Offshore and Supergrid of the Future*, IEEE Press Series on Power Engineering, Ed. John Wiley & Sons, 2016.

- [2] D. Jovcic and K. Ahmed, High Voltage Direct Current Transmission: Converters, Systems and DC Grids, University of Aberdeen, UK, Wiley 2015.

- [3] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, BinWu, J. Rodríguez, M. A. Pérez and J I. Leon, "Recent Advances and Industrial Applications of Multilevel Converters", *IEEE Trans. on Indust. Electron. vol.* 57 no. 8, pp. 2553-2580, Aug. 2010.

- [4] S. Rohner, S. Bernet, M. Hiller and R. Sommer,"Modulation, Losses, and Semiconductor Requirements of Modular Multilevel Converters", *IEEE Trans. on Indust. Electron. vol.* 57 no. 8, pp. 2633-2642, Aug. 2010.

- [5] L. Harnefors, A. Antonopoulos, S. Norrga, L. Ängquist and H. P. Nee,"Dynamic Analysis of Modular Multilevel Converters", *IEEE Trans.* on Indust. Electron. vol. 60 no. 7, pp. 2526-2537, Jul. 2013.

- [6] D. Van Hertem and M. Ghandhari, "Multi-terminal VSC HVDC for the European supergrid: Obstacles", *Renewable and Sustainable Energy Reviews, vol. 14, issue 9*, pp. 3156-3163, Dec. 2010.

- [7] A. Egea-Álvarez, F. Bianchi, A. Junyent-Ferré, G. Gross, O. Gomis-Bellmunt,"Voltage control of multiterminal VSC-HVDC transmission systems for offshore wind power plants: Design and implementation in a scaled platform", *IEEE Trans. on Indust. Electron. vol. 60* no. 6, pp. 2381-2391, June 2013.

- [8] K. Rouzbehi, A. Miranian, A. Luna and P. Rodriguez, "Towards fully controllable multi-terminal DC grids using flexible DC transmission systems," in *Conversion Congress and Expo. (ECCE)*, 2014, pp. 1-5.

- [9] E. Veilleux and B. Ooi, "Power flow analysis in multi-terminal HVDC grid," in *Power Systems Conf. and Expo. (PSCE)*, 2011, pp. 1-7.

- [10] Q. Mu, J. Liang, Y. Li and X. Zhou, "Power flow control devices in DC grids," in *Power and Energy Society General Meeting IEEE*, 2012, pp. 1-7.

- [11] E. Veilleux and B. Ooi. "Multi-terminal HVDC with thyristor powerflow controller," *IEEE Trans. Power Del.*, vol. 27, no. 3, pp. 1205-1212, Jul. 2012.

- [12] S. Balasubramaniam, J. Liang and C.E. Ugalde-Loo, "An IGBT based series power flow controller for multi-terminal HVDC transmission," in 49th Int UPEC, Cluj-Napoca, 2014, pp. 1-6.

- [13] C. Barker and R. Whitehouse, "A current flow controller for use in HVDC grids," in *IET Int. Conf. on AC and DC Power Trans. (ACDC)*, 2012, pp. 1-5.

- [14] S. Balasubramaniam, J. Liang and C.E. Ugalde-Loo, "Control, dynamics and operation of a dual H-bridge current flow controller," in *IEEE Energy Conversion Congress and Exposition (ECCE), Montreal*, 2015, pp. 1-8.

- [15] J. Sau-Bassols, E. Prieto-Araujo and O. Gomis-Bellmunt, "Modelling and control of an interline Current Flow Controller for meshed HVDC grids," *IEEE Trans. Power Del. vol. 32*, issue 1, pp. 11-22, Feb. 2017.

- [16] F. Hassan, R. King, R. Whitehouse and C. Barker, "Double modulation control (DMC) for dual H-bridge current flow controller (2B-CFC)," in 17th European Conf. on Power Electron. and Applications (EPE'15 ECCE-Europe), Geneva 2015, pp. 1-9.

- [17] S. Balasubramaniam, C. Ugalde-Loo, J. Liang, T. Joseph, R. King and A. Adamczyk, "Experimental Validation of Dual H-Bridge Current Flow Controllers for Meshed HVdc Grids," *IEEE Trans. Power Del. vol. 33*, issue 1, pp. 381-392, Sep. 2017.

- [18] W. Chen, X. Zhu, L. Yao, X. Ruan, Z. Wang and Y. Cao, "An Interline DC Power Flow Controller (IDCPFC) for Multi-terminal HVDC System," *IEEE Trans. Power Del. vol. 30*, issue 4, pp. 2027-2036, Aug. 2015.

- [19] W. Chen, X. Zhu, L. Yao, G. Ning, Y. Li, Z. Wang, W. Gu and X. Qu, "A Novel Interline DC Power-Flow Controller (IDCPFC) for Meshed HVDC Grids," *IEEE Trans. Power Del. vol.* 31, issue 4, pp. 1719-1727, Aug. 2016.

- [20] J. Sau-Bassols, E. Prieto-Araujo, O. Gomis-Bellmunt and F. Hassan, "Series interline DC/DC Current Flow Controller for meshed HVDC grids," *IEEE Trans. Power Del. vol. 33*, issue 2, pp. 881-891, Apr 2017.

- [21] F. Hassan, J. Sau-Bassols, E. Prieto-Araujo and O. Gomis-Bellmunt, "Current flow controller," WO/2016/055580, Apr. 14, 2016.

- [22] F. Hassan, J. Sau-Bassols, E. Prieto-Araujo and O. Gomis-Bellmunt, "Current flow control assembly," WO/2016/071522, May 12, 2016.

- [23] J. Sau-Bassols, E. Prieto-Araujo, O. Gomis-Bellmunt and F. Hassan, "Selective Operation of Distributed Current Flow Controller Devices for Meshed HVDC Grids", *IEEE Trans. Power Del. vol.* 34, issue 1, pp. 107-118, Feb. 2019.

- [24] H. Y. Diab, M. I. Marei and S. B. Tennakoon, "Operation and control of an insulated gate bipolar transistor-based current controlling device for power flow applications in multiterminal high-voltage direct current grids," *IET Power Electron. vol. 9*, issue 2, pp. 305-315, Feb. 2016.

- [25] M. Ranjram and P. W. Lehn, "A Multiport Power-Flow Controller for DC Transmission Grids," *IEEE Trans. Power Del. vol. 31*, issue 1, pp. 389-396, Feb. 2016.

- [26] A. Mokhberdoran, J. Sau-Bassols, E. Prieto-Araujo, O. Gomis-Bellmunt, N. Silva, A. Carvalho, "Fault mode operation strategies for dual H-bridge current flow controller in meshed HVDC grid," *Electric Power Systems Research. vol. 160*, pp. 163-172, Mar. 2018.

- [27] A. Mokhberdoran, D. Van Hertem, N. Silva, H. Leite and A. Carvalho,"Multiport Hybrid HVDC Circuit Breaker", *IEEE Trans. on Indust. Electron. vol.* 65 no. 1, pp. 309-320, Jan. 2018.

- [28] O. Cwikowski, J. Sau-Bassols, B. Chang, E. Prieto-Araujo, M. Barnes, O. Gomis-Bellmunt and R. Shuttleworth, "Integrated HVDC Circuit Breakers with Current Flow Control Capability," *IEEE Trans. Power Del. vol. 33*, issue 1, pp. 371-380, Feb. 2018.

- [29] A. Mokhberdoran, O. Gomis-Bellmunt, N. Silva and A. Carvalho, "Current Flow Controlling Hybrid DC Circuit Breaker," *IEEE Trans. Power Electro. vol. 33*, issue 2, pp. 1323-1334, Feb. 2018.

- [30] J. Beerten, S. DArco, J. A. Suul, "Cable Model Order Reduction for HVDC Systems Interoperability Analysis", in 11th Int. Conf. on AC and DC Power Trans. (ACDC), Birmingham 2015, pp. 1-10.

- [31] J. Freytes, S. Akkari, J. Dai, F. Gruson, P. Rault and X. Guillaud, "Small signal state-space modeling of an HVDC link with modular multilevel converters", in 17th IEEE Workshop on Control and Modeling for Power Electron. (COMPEL), Trondheim 2016, pp. 1-8.

- [32] StakPak IGBT Module. Data Sheet, Doc. No. 5SYA 1450-00 10-2016, Accessed Feb. 2018.

- [33] T. K. Vrana, S. Dennetiere, J. Jardini, Y. Yang, and H. Saad, "The CIGRE B4 DC grid test system version 2013," in *Electra*, Mar. 2013.