A forming-free ReRAM cell with low operating voltage

Binbin Yang<sup>1</sup>, Nuo Xu<sup>2</sup>, Cheng Li<sup>1</sup>, Chenglong Huang<sup>1</sup>, Desheng Ma<sup>1</sup>, Jiahao Liu<sup>1</sup>, Daniel Arumí<sup>3</sup>, and Liang Fang<sup>1, a)</sup>

Abstract The unwanted electro-forming process is unavoidable for the practical application of most resistive random access memory (ReRAM) devices, which is always being one of the obstacles for the massive commercialization of this novel electronic device. In this letter, a forming-free Pt/Ti/(TiO<sub>2-x</sub>)/Ta<sub>2</sub>O<sub>5</sub>/Pt based ReRAM device is demonstrated with an additional feature of the low operation voltage. The fitting result of the measured I-V curves reveals that resistive switching of the fabricated device is conducted by the electrons trapping/de-trapping process in deep-level electron traps of the  $TiO_{2-x}$  layer, which is formed through the spontaneous "oxygen grabbing" reaction in the interface of Ti and Ta<sub>2</sub>O<sub>5</sub> during the film deposition. The plentiful oxygen vacancy defects and the thin resistive switching zone  $(TiO_{2-x})$  ensure the forming-free and low operating voltage characteristics. Using "oxygen grabbing" to pre-produce abundant electron trapping centers for the resistive switching provides a simple way for the fabrication of the forming-free ReRAM device with low operating voltage, aiming to the high-density and low-power memory applications.

Keywords: ReRAM, resistive switching, forming-free, low operation voltage

**Classification:** Electron devices, circuits and modules (silicon, compound semiconductor, organic and novel materials)

# 1. Introduction

In the coming era of the Internet of Things (IoT) and big data, as the most promising successor of the next-generation nonvolatile memory [1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15], ReRAM still meets some practical problems that need to be solved. First, in most cases, an electro-forming process is a prerequisite for the repeatable resistive switching, in which a large voltage is applied to the pristinely insulating ReRAM device to generate sufficient oxygen vacancy defects or metal ions to construct a conducting path [1]. However, this electro-forming step is generally companied with some undesired side effects [16], such as device variations and failures, and would undoubtedly increase the complexity of the peripheral circuit. Second, most of this kind of filamentconducted resistive switching could not meet the low power consumption requirements [16, 17, 18, 19, 20], which is concerned in the IoT or mobile application scenarios.

In this study, a forming-free ReRAM device with the sim-

DOI: 10.1587/elex.17.20200343 Received October 13, 2020 Accepted October 26, 2020 Publicized November 10, 2020 Copyedited November 25, 2020 ple structure of  $Pt/Ti/(TiO_{2-x})/Ta_2O_5/Pt$  is achieved by several conventional film deposition processes. The  $TiO_{2-x}$  is formed by the interface reaction between the top electrode (TE, Ti) and the oxide layer  $(Ta_2O_5)$  during the deposition process, acting as the switching zone in the resistive switching process. The electrical measurement results of the device manifest the typical resistive switching behavior, which is ascribed to the electrons trapping/de-trapping process in the deep-level trap sites. And the space-charge-limited current (SCLC) mechanism [21] takes control of the conduction in high resistance state (HRS) and low resistance state (LRS), evidenced by the *I-V* curves fitting result. Moreover, as plenty of electron trap centers are pre-generated in the thin switching zone  $(TiO_{2-x})$  during the interface reaction, the fabricated ReRAM device is forming-free and can be switched under low voltages, holding great potential in low power applications.

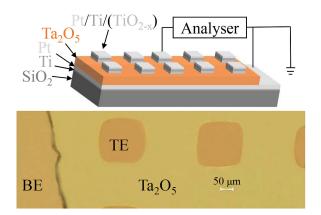

Fig. 1 Top view optical microscope image of the device with an inset of the  $Pt/Ti/(TiO_{2-x})/Ta_2O_5/Pt$  structure schematic.

# 2. Experimental

Fig. 1 shows the top view optical microscope image of the fabricated device, with the device structure schematic as an inset. First, the SiO<sub>2</sub> substrate was sequentially cleaned by the acetone, isopropyl alcohol, and deionized (DI) water in an ultrasonic oscillator. Then, the films were deposited on the chemically cleaned SiO<sub>2</sub> substrate through electron beam evaporation in a vacuum chamber with the pressure of  $1.5 \times 10^{-4}$  Pa, having a stacking sequence of 10-nm Ti (the adhesion layer), 40-nm Pt (the bottom electrode, BE), 80-nm Ta<sub>2</sub>O<sub>5</sub> (the oxide layer), 40-nm Ti (TE) and 10-nm Pt (the protection layer). A copper grid shadow mask with the arrayed opening window of 200  $\mu$ m × 200  $\mu$ m was used to shape the device during the deposition of the TE and protec-

<sup>&</sup>lt;sup>1</sup> Institute for Quantum Information & State Key Laboratory of High Performance Computing, College of Computer, National University of Defense Technology, Changsha 410073, China

<sup>&</sup>lt;sup>2</sup> College of Computer, National University of Defense Technology, Changsha 410073, China

<sup>&</sup>lt;sup>3</sup> Dept. d'Enginyeria Electrònica, Universitat Politècnica de Catalunya, 08028 Barcelona, Spain

a) lfang@nudt.edu.cn

tion layer. A TiO<sub>2-x</sub> layer was formed between the Ta<sub>2</sub>O<sub>5</sub> and Ti by the spontaneous "oxygen grabbing" reaction during the deposition process, as shown in the inset of Fig. 1. The detailed mechanism will be explained later. The optical microscopy image of the device was obtained by an Optical Microscope (Nikon ECLIPSE LV150NL) in 100X. And, a semiconductor characterization system (Keithley 4200 SCS) combined with a probe station was utilized to the electrical measurement of the ReRAM cell at room temperature, during which a bias voltage was applied to the TE and the BE was grounded.

# 3. Results and discussion

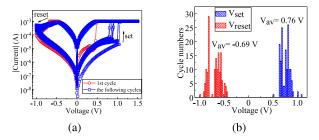

Fig. 2(a) reflects the bipolar resistive switching behavior of the fabricated ReRAM device by showing the DC voltage sweep results of the first 10 cycles in the semi-log scale. The voltage is swept in a sequence of  $0\rightarrow 1.5 \text{ V}\rightarrow 0\rightarrow -1.0$  $\text{V}\rightarrow 0$  with the step of 0.02 V and compliant current of 1 mA. The set switching, in which the resistance of the device is changed from HRS to LRS, occurs in positive voltage direction whereas the reset switching, in which the resistance of the device is changed from LRS to HRS, happens in the negative voltage direction. A more detailed resistive switching behavior analysis of this ReRAM cell could be found in our previous work [22].

**Fig. 2** Electrical characteristics of the ReRAM device under DC sweep. (a) Resistive switching behavior with forming-free performance. (b) Distribution of switching voltages from 150 continuous DC sweeps.

Notably, the first cycle has a smaller set voltage (near 0.5 V) than the following cycles, which evidences that the fabricated ReRAM device is free from the electro-forming step. Fig. 2(b) shows the distribution of the switching voltages from 150 continuous DC sweep cycles. Most of the switching voltages are below 1.0 V (in the form of absolute value), showing the low operating voltage attribute (0.76 and -0.69 V are the average values of Vset and Vreset, respectively). The switching voltages of recently reported representative forming-free bipolar ReRAM devices are summarized in Table I [16, 17, 18, 19, 20, 23, 24, 25, 26]. The device in this article achieves the forming-free and superiorly low operating voltage characteristics without using any special processes, such as solution-process and ions implantation, which equips the device with a great advantage in terms of the CMOS-compatibility. All of these attributes facilitate its application in the low-power consumption memory with a simple peripheral circuit.

Table I

Summary of recently reported material systems showing forming-free resistive switching characteristics

| Ref.         | Material system                                                                                | Special process                                | Vset/Vreset (V)            |

|--------------|------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------|

| [16]         | Pt/a-MoO <sub>3</sub> /Nb-SrTiO <sub>3</sub>                                                   | Proton injection                               | 1.5/-2.2                   |

| [17]         | Al/HfO <sub>2</sub> /P <sup>++</sup> -Si                                                       | Doping with Sm<br>or Dy                        | ~ 3.5/~ -3.8               |

| [18]         | Al/nc-Si:H/a-SiN <sub>x</sub> :H/P <sup>+</sup> -Si                                            | Hydrogen<br>plasma treatment                   | ~ 3.2/~ -1.5               |

| [19]         | Al/a-SiN <sub>0.73</sub> O <sub>0.83</sub> :H/P <sup>+</sup> -Si                               | Oxygen plasma<br>treatment                     | ~ 2.4/~ -2.0               |

| [20]         | $Pd/HfO_2/WO_x/W$                                                                              | -                                              | 1.0/-3.0                   |

| [23]         | Al/BP:PS/Al                                                                                    | Solution-Process                               | ~ 1.75/~ -1.25             |

| [24]         | TiN/AlO <sub>x</sub> /Pt                                                                       | Solution-Process<br>and annealing at<br>200 °C | 0.9 to 3.7/-0.3 to<br>-1.2 |

| [25]         | Al <sub>2</sub> O <sub>3</sub> /La <sub>2</sub> O <sub>3</sub> /Al <sub>2</sub> O <sub>3</sub> | Al <sup>+</sup> implantation                   | 1.5/-1.0                   |

| [26]         | Ag/r-TiO <sub>2</sub> /FTO                                                                     | Solution-Process                               | 0.7/-0.8                   |

| This<br>work | $Pt/Ti/(TiO_{2-x})/Ta_2O_5/Pt$                                                                 | -                                              | 0.76/-0.69                 |

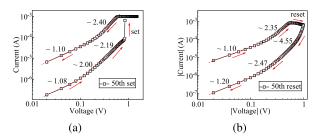

**Fig. 3** *I-V* curves fitting result in double-log scales (a) for set switching and (b) for reset switching.

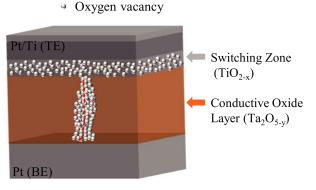

fabricated ReRAM device, as shown in Fig. 3. The fitting result shows that the carrier transports in both HRS and LRS follow the SCLC model, which has three different conductive stages with the increase of the applied voltage: (1)  $I \propto V$ ; (2)  $I \propto V^n$  (1<n≤2); (3)  $I \propto V^n$  (n>2) [21]. Moreover, it reveals the existence of substantial deep-level electron traps in the matrix of the device. Emptying of these traps contributes to the HRS of the device, whereas their filled states lead to the LRS. The electron traps come from the film deposition process in the electron-beam evaporation system with high reaction temperature. When depositing the TE (Ti) on to the oxide layer  $(Ta_2O_5)$  in the high-temperature chamber, the active metal titanium automatically reacts with the oxygen atoms from the Ta<sub>2</sub>O<sub>5</sub> layer, which conducts to form a thin  $TiO_{2-x}$  layer with a high concentration of oxygen vacancies in the interface of Ti and Ta2O5. These oxygen vacancy defects occupy the deep energy levels (from  $\sim 0.8$  eV to  $\sim$ 1 eV) in the bandgap and act as the electron trap centers to trap/de-trap electrons during the resistive switching process [12, 27]. Although this chemical reaction also leaves abundant oxygen vacancies in the oxide layer, these defects occupy shallower energy levels (from  $\sim 0.25$  eV to  $\sim 0.57$ eV) and trend to construct a conductive filament acting as a virtual electrode [28, 29, 30]. Therefore, resistive switching only happens in the thin  $TiO_{2-x}$  zone in this study, as shown in Fig. 4. Furthermore, compared with the previously reported resistive switching behavior in the tantalum oxide with similar electrode systems [31, 32], none of them claiming any forming-free attribute, we could conclude that the spontaneously formed thin  $TiO_{2-x}$  switching zone is responsible for the forming-free operation in our device.

Fig. 4 Schematic of the device in the stable state.

During the fabrication process, this automatic "oxygen grabbing" process pre-produces sufficient oxygen vacancy defects in the switching zone  $(\text{TiO}_{2-x})$  for the successful switching events, so an initial electro-forming step is not required for the workable ReRAM cell in this work. During the first switching cycle, the reset operation releases many trapped electrons, which results in a higher HRS (than the pristine state). Therefore, the subsequent switches require a larger set voltage than the first cycle. This can be concluded by the smaller current of the following cycles in the near-zero voltage region (0 to 0.3 V) in HRS (See Fig. 2(a)). Besides, the thin switching zone could also account for the characteristic of low operating voltage.

# 4. Conclusion

In summary, a forming-free Pt/Ti/(TiO<sub>2-x</sub>)/Ta<sub>2</sub>O<sub>5</sub>/Pt-based ReRAM cell with low switching voltages is achieved in this study. The disappearance of the bothersome electroforming step is ascribed to the presence of substantial deeplevel electron-traps pre-produced by the spontaneous "oxygen grabbing" reaction in the active metal/oxide interface during the film deposition process. The I-V curves fitting result demonstrates that the electron trapping/de-trapping process governs the switching between the HRS and LRS. The thin resistive switching zone results in the forming-free and the low operation voltage attributes, making the device have great potential in some high-density and low-power consumption memory applications. The adopted "oxygen grabbing" method does not need any special process or improvement in the fabrication process, providing a simple way for achieving the forming-free and low switching voltage ReRAM device.

# Acknowledgments

This work is supported in part by the HGJ (Grant No. 2017ZX01028-103-002), National Key Research and Development Program of China (Grant No. 2018YFB1003304), National Natural Science Foundation of China (Grant No. 61832007) and the research foundation from NUDT under Grant ZK20-02.

#### References

- R. Waser, *et al.*: "Redox-based resistive switching memoriesnanoionic mechanisms, prospects, and challenges," Adv. Mater. 21 (2009) 2632 (DOI: 10.1002/adma.200900375).

- [2] C.S. Hwang : "Prospective of semiconductor memory devices: from memory system to materials," Adv. Electron. Mater. 1 (2015) 1400056 (DOI: 10.1002/aelm.201400056).

- [3] L. Chua : "Memristor: the missing circuit element," IEEE Trans. Circuit Theory 18 (1971) 507 (DOI: 10.1109/TCT.1971.1083337).

- [4] D.B. Strukov, *et al.*: "The missing memristor found," Nature 453 (2008) 80 (DOI: 10.1038/nature06932).

- [5] R. Waser and M. Aono: "Nanoionics-based resistive switching memories," Nanoscience and Technology: A Collection of Reviews from Nature Journals 1 (2010) 158 (DOI: 10.1142/9789814287005\_0016).

- [6] M. Prezioso, *et al.*: "Training and operation of an integrated neuromorphic network based on metal-oxide memristors," Nature **521** (2015) 61 (DOI: 10.1038/nature14441).

- [7] E.R. Zhou, *et al.*: "Memristive spiking neural networks trained with unsupervised STDP," Electronics 7 (2018) 396 (DOI: 10.3390/ electronics7120396).

- [8] L. Liu, *et al.*: "Designing high-performance storage in HfO<sub>2</sub>/BiFeO<sub>3</sub> memristor for artificial synapse applications," Adv. Electron. Mater. 6 (2020) 1901012 (DOI: 10.1002/aelm.201901012).

- [9] N. Xu, et al.: "Fully functional logic-in-memory operations based on a reconfigurable finite-state machine using a single memristor," Adv. Electron. Mater. 4 (2018) 1800189 (DOI: 10.1002/aelm.201800189).

- [10] N. Xu, et al.: "Time-efficient stateful dual-bit-memristor logic," physica status solidi (RRL)-Rapid Research Letters 13 (2019) 1900033 (DOI: 10.1002/pssr.201900033).

- [11] E.R. Zhou, *et al.*: "An improved memristor model for brain-inspired computing," Chinese Phys. B **26** (2017) 118502 (DOI: 10.1088/ 1674-1056/26/11/118502).

- [12] S. Jia, *et al.*: "Ultrahigh drive current and large selectivity in GeS selector," Nat. Commun. **11** (2020) 4636 (DOI: 10.1038/ s41467-020-18382-z).

- [13] X. Zhu, et al.: "Performing stateful logic on memristor memory," IEEE Trans. Circuits Syst. II, Exp. Briefs 60 (2013) 682 (DOI: 0.1109/TCSII.2013.2273837).

- [14] J. Zhou, *et al.*: "A memristor-based architecture combining memory and image processing," Sci. China Inf. Sci. **57** (2014) 1 (DOI: 10.1007/s11432-013-4887-5).

- [15] T. Liu, *et al.*: "A 130.7mm<sup>2</sup> 2-layer 32Gb ReRAM memory device in 24nm technology," ISSCC Dig. Tech. Papers (2013) 210 (DOI: 10.1109/ISSCC.2013.6487703).

- [16] Z. Wang, *et al.*: "Electroforming-free artificial synapses based on proton conduction in  $\alpha$ -MoO<sub>3</sub> films," Adv. Electron. Mater. **6** (2020) 1901290 (DOI: 10.1002/aelm.201901290).

- [17] S. Kumar and C. Rath : "Oxygen vacancy mediated stabilization of cubic phase at room temperature and resistive switching effect in Smand Dy-Doped HfO<sub>2</sub> thin film," physica status solidi (a) **217** (2020) 1900756 (DOI: 10.1002/pssa.201900756).

- [18] Y. Sun, *et al.*: "Hybrid channel induced forming-free performance in nanocrystalline-Si:H/a-SiNx:H resistive switching memory," Nanotechnology **30** (2019) 365701 (DOI: 10.1088/1361-6528/ab2507).

- [19] X. Zhang, et al.: "Forming-free performance of a-SiNx:Hbased resistive switching memory obtained by oxygen plasma treatment," Nanotechnology 29 (2018) 245701 (DOI: 10.1088/ 1361-6528/aab9e1).

- [20] Q. Luo, *et al.*: "Self-rectifying and forming-free resistive-switching device for embedded memory application," IEEE Electron Device Lett. **39** (2018) 664 (DOI: 10.1109/LED.2018.2821162).

- [21] K.C. Kao, et al.: Electrical Transport in Solids (Pergamon Press, Oxford, 1981) 1st ed. 150.

- [22] B.B. Yang, *et al.*: "A method of generating random bits by using an electronic bipolar memristor," Chinese Phys. B **29** (2020) 048505 (DOI: 10.1088/1674-1056/ab77fd).

- [23] Y.L. Hsieh, *et al.*: "Solution-processed black phosphorus nanoflakes for integrating nonvolatile resistive random access memory and the mechanism unveiled," Nanotechnology **30** (2019) 445702 (DOI:

10.1088/1361-6528/ab3606).

- [24] Y.F. Qi, et al.: "Enhanced resistive switching performance of aluminum oxide dielectric with a low temperature solutionprocessed method," Solid-State Electronics 158 (2019) 28 (DOI: 10.1016/j.sse.2019.05.007).

- [25] X. Wang, *et al.*: "Improved resistive switching characteristics of atomic layer deposited Al<sub>2</sub>O<sub>3</sub>/La<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub> multi-stacked films with Al<sup>+</sup> implantation," J Mater. Sci.: Mater. Electron **30** (2019) 12577 (DOI: 10.1007/s10854-019-01618-0).

- [26] Y. Abbas, *et al.*: "Tailored nanoplateau and nanochannel structures using solution-processed rutile TiO<sub>2</sub> thin films for complementary and bipolar switching characteristics," Nanoscale **11** (2019) 13815 (DOI: 10.1039/C9NR03465J).

- [27] K.M. Kim, *et al.*: "A detailed understanding of the electronic bipolar resistance switching behavior in Pt/TiO<sub>2</sub>/Pt structure," Nanotechnology 22 (2011) 254010 (DOI: 10.1088/0957-4484/22/25/254010).

- [28] X.M. Wu, *et al.*: "Dielectric constant dependence of Poole-Frenkel potential in tantalum oxide thin films," Mater. Chem. Phys. **38** (1994) 297 (DOI: 10.1016/0254-0584(94)90205-4).

- [29] A. Prakash, *et al.*: "Improvement of uniformity of resistive switching parameters by selecting the electroformation polarity in IrO<sub>x</sub>/TaO<sub>x</sub>/WO<sub>x</sub>/W structure," Jpn. J. Appl. Phys. **51** (2012) 04DD06 (DOI: 10.1143/JJAP.51.04DD06).

- [30] C. Chen, *et al.*: "Oxygen migration induced resistive switching effect and its thermal stability in W/TaO<sub>x</sub>/Pt structure," Appl. Phys. Lett. **100** (2012) 253509 (DOI: 10.1063/1.4730601).

- [31] M. Terai, et al.: "Resistance controllability of Ta<sub>2</sub>O<sub>5</sub>/TiO<sub>2</sub> stack ReRAM for low-voltage and multilevel operation," IEEE Electron Device Lett. **31** (2010) 204 (DOI: 10.1109/LED.2009.2039021).

- [32] Z. Wei, *et al.*: "Highly reliable TaO<sub>x</sub> ReRAM and direct evidence of redox reaction mechanism," IEEE International Electron Devices Meeting Papers (2008) 1 (DOI: 10.1109/IEDM.2008.4796676).