### POLITECNICO DI TORINO

Master's Degree in Electronic Engineering

### Master's Thesis

# Functional and Formal Verification on submodules of a Vector Processing Unit based on RISC-V V-extension

Supervisor:

Prof. LAVAGNO Luciano (PoliTo)

Cosupervisors:

Prof. Moll Echeto Francesc (UPC)

Dr. Palomar Oscar (BSC)

Candidate:

Guglielmi Vito Luca

ID: s265044

SEPTEMBER 2020

## Abstract

This thesis was developed while working at Barcelona Supercomputing Center, a research center specialized in High Performance Computing and investigation in many fields, such as cloud computing, bioinformatics, material science and more.

Taking part to European Processor Initiative (EPI) project, the whole thesis aims to perform the verification process on a Vector Processing Unit (VPU). The implemented Vector Processing Unit is based on the RISC-V V-Extension, which is a set of specifications defining the Instructions Set Architecture (ISA) of a vector core. The V-Extension is currently on develop by the RISC-V foundation. This manuscript will refer to the versions 0.7.1.

The first chapter consist of an introduction of the needed concepts and of the context in which this thesis is been developed.

Then, in the second chapter, all the techniques used to verify functionally and formally this VPU are discussed.

All the results, such as found bugs or created material, are displayed in the third chapter. Moreover, analysing these results, the efficacy of the techniques used is evaluated. It is shown how formal and functional tools can be used to find bugs or to better define specification.

In the last chapter, it is possible to conclude that the techniques adopted produced the expected results showing significant improvements in the verification effort.

# Contents

| 1 | Intr | Introduction 6                                 |  |  |  |  |  |  |  |  |  |  |  |

|---|------|------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

|   | 1.1  | Concepts                                       |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.1.1 RISC-V                                   |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.1.2 Parallelism, Vectors and the V-Extension |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.1.3 Verification                             |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.2  | Context                                        |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.2.1 The VPU                                  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.2.2 The UVM                                  |  |  |  |  |  |  |  |  |  |  |  |

| 2 | Cor  | tributions 32                                  |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.1  | Submodules and Specifications                  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.1.1 Load Management Unit                     |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.1.2 Load Buffer                              |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.2  | Verification Plan                              |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.1 Test Plan                                |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.3  | Verification Process                           |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.3.1 Scoreboard                               |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.3.2 Checkers                                 |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.3.3 Drivers                                  |  |  |  |  |  |  |  |  |  |  |  |

| 3 | Res  | Results and Considerations 61                  |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.1  | Found Bugs                                     |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.2  | Material Created                               |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.3  | Considerations                                 |  |  |  |  |  |  |  |  |  |  |  |

| 4  | Con   | iclusions                  | 69 |

|----|-------|----------------------------|----|

|    | 4.1   | Conclusions                | 69 |

|    | 4.2   | Future developments        | 70 |

| Li | st of | Figures                    | 71 |

| Li | st of | Tables                     | 73 |

| Bi | bliog | graphy                     | 74 |

| A  | App   | pendix                     | 76 |

|    | A.1   | Checkers                   | 76 |

|    |       | A.1.1 Load Buffer          | 76 |

|    |       | A.1.2 Load Management Unit | 92 |

# Chapter 1

# Introduction

In this Chapter the RISC-V and V-Extension concepts relevant for this thesis are presented and discussed together with the verification notions. Furthermore, an overview on the context of this project is given, explaining the Vector Processing Unit (VPU) implemented and then showing the Universal Verification Methodologies (UVM) adopted.

Firstly, the RISC-V Instruction Set Architecture (ISA) is briefly illustrated, proceeding with an overview on all the major extensions provided by the RISC-V foundation. The Concepts section is then closed with some knowledge about the Verification process and its main tools.

Finally the theory is contextualized by the implemented VPU and on the used UVM structure. Those allow to better understand the contributions done in this thesis, contributions that are then explained into the next Chapter.

### 1.1 Concepts

#### 1.1.1 RISC-V

RISC-V is an open, extensible and free ISA. It was initially only designed to support computer architecture research and education [1]. The project, began at the Berkeley University of California in 2010, published the first ISA User Manual in 2011.

The RISC-V ISA is implemented as a base integer ISA, but it is modular and

so supports many instruction encodings. This ISA is provided under open source licenses, and it is gaining a lot of popularity due to its open nature. Mainly there are two primary base integer variants, RV32I and RV64I, which provide 32-bit or 64-bit user-level address spaces respectively.

#### Extensions

RISC-V is designed to have a good customization which is the reason why it is provided with the possibility to be extended, but the base integer instructions cannot be redefined. There are two kinds of extensions: *standard* and *non-standard*.

- The *standard* ones need to be compatible with all the other standards and they should also aim to be generally useful.

- The *non-standard* ones can be highly specialized in some task and therefore they may conflict with other extensions.

For general development, as defined in the specification document [1], some of the standard extensions are predefined:

- "I" is the base integer extension and contains integer computational instructions, integer loads, integer stores, and control-flow instructions. It is mandatory for all RISC-V implementations.

- "M" is the standard integer multiplication and division extension, it allows to multiply and divide the values held in the integer registers.

- "A" is the standard atomic instruction extension. It is useful to have atomic instructions for inter-processor synchronization. In fact, with this extension is possible to read, modify, and write memory atomically.

- "F" is the standard single-precision floating-point extension. It adds floating-point registers, single-precision computational instructions, and single-precision loads and stores.

- "D" is the standard double-precision floating-point extension. Advantageous when the F extension is not enough, it expands the extension and adds double-precision computational instructions, loads, and stores.

- "G" is the denotation for an integer base plus these four standard extensions ("IMAFD").

- "V" is the standard Vector Extension. It is designed to add the possibility to perform vector operations, allowing performance and efficiency. The thesis will focus only on this extension.

The design philosophy of the RISC-V projects is based on modularity: the base ISA will not change over time, but new extensions will be available and new feature will be added. Which is a major feature because of the difficulty in finding general useful extension beyond the ones already existing. Therefore, it would not be convenient to constantly add new features to the base ISA and then have to keep track of that at a later time.

#### Base instructions

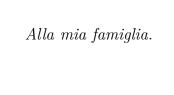

In Figure 1.1 it is possible to see how the base instruction are composed.

| 31 | 25        | 24  | 20 | 19  | 15 | 14    | 12 | 11       | 7 | 6      |        | 0      |        |

|----|-----------|-----|----|-----|----|-------|----|----------|---|--------|--------|--------|--------|

|    | funct7    | rs2 |    | rs1 |    | funct | 3  | rd       |   |        | opcode |        | R-type |

|    |           |     |    |     |    |       |    |          |   |        |        |        |        |

|    | imm[11:0  | ]   |    | rs1 |    | funct | 3  | rd       |   |        | opcode |        | I-type |

|    |           |     |    |     |    |       |    |          |   |        |        |        |        |

|    | imm[11:5] | rs2 |    | rs1 |    | funct | 3  | imm[4:0] |   |        | opcode |        | S-type |

|    |           |     |    |     |    |       |    |          |   |        |        |        |        |

|    |           | 12] |    |     |    |       | rd |          |   | opcode |        | U-type |        |

Figure 1.1. RISC-V base instruction formats [1]

It is important to notice that RISC-V is a load-store architecture, which means that only load and store operations can have access to the memory. It is a very convenient organization, because it reduces the average time-per-operation and guarantees a good functioning of the pipelined structure.

The instruction also supports signed byte and half word loads, which is very advantageous when working with signed byte and half word data types.

In Figure 1.2 it is possible to see how the load-store instructions are composed, and that the LOAD is an I-type op and the STORE is an S-type op.

Figure 1.2. RISC-V load/store instruction formats [1]

### 1.1.2 Parallelism, Vectors and the V-Extension

During the last years, the parallel architecture is gaining inertia on the processors field. This is happening because the real world has parallel behaviour and so the hardware we use to compute simulations and calculus needs to be likewise [2].

Also, most of the paradigms that led to the decision of using a single core, are now changing quickly as the technology changes its needs. In fact, as the technology scales down to the nanometers, the power and the energy consumptions are becoming a problem. Also, the cost of a single transistor is significantly lower.

A solution to the efficiency problem are the VPU (Vector Processing Units) working with single instruction multiple data (SIMD), in this way it possible to maintain the binaries easy to program, but very powerful in term of data computation..

A famous example of a vector architecture is the Cray-1, presented in 1975. The Cray-1, a load/store architecture, was designed for Supercomputing and its major feature was to have a scalar mode along the vector one. This was advantageous because high performances are not always useful.

#### Time efficiency

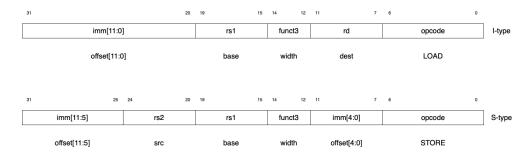

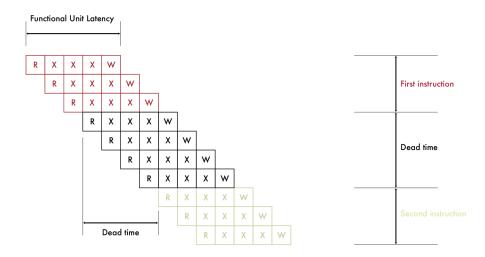

As shown in Figure 1.3, with standard multithreading there will often be some empty thread along with the running ones, causing a loss in the efficiency.

Figure 1.3. Multithreading Processor Clock Time usage [3]

Indeed the major advantage with the vector computation is the condensation of the processor usage. So that the usage will not be distributed as for standard multithreading processors, but it will have full usage for some cycles and none usage for others [3].

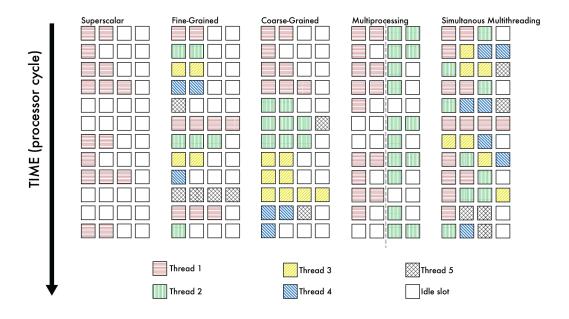

Figure 1.4. Vector Processor Processor Time usage [3]

It is shown in Figure 1.4 how the processor usage is condensed in some cycles and then empty for others. That happens because the vector operations need some clock cycles to start up. So based on the length of the pipeline, there will be some dead cycles. This means the latency increases, because each operation adds some dead cycles that need to be waited before a new operation can start.

But, this drawback can be used to increase the efficiency with modern low-power techniques. In fact, it was shown [4] that the Vector Accelerators, while improving performances up to 10X, can also improve energy efficiency of 40-50% on loop kernels and 10-20% on larger program segments. In Figure 1.5 it is possible to see how a vector needs to wait the previous one to be completed before starting, and so why the latency increases.

Figure 1.5. Latency penalty on vector processing units [3]

The design implementation that is been used for the EPI project and so in this thesis is the V-Extension (V stands for Vector), and it is in current development. The reference is the V-Extension 0.7.1.

The vector extension adds 32 vector registers, and 5 unprivileged CSRs (*vstart*, *vxsat*, *vxrm*, *vtype*, *vl*) to the base scalar RISC-V ISA [5]. There are also 8 vector predicate registers (vp0-vp7). The CSRs vectors define the configurations.

| Privilege | Name   | Description               |

|-----------|--------|---------------------------|

| URW       | vstart | Vector start position     |

| URW       | vxsat  | Fixed-point Saturate Flag |

| URW       | vxrm   | Fixed-Point Rounding Mode |

| URO       | vl     | Vector length             |

| URO       | vtype  | Vector data type register |

Table 1.1. RISC-V's CSRs

The datatypes and operations supported by the V-extension change based on the base scalar ISA [5].

The vector unit must be configured before being used. I.e. the active vector

length is held in the CSR vl, which can only hold values between 0 and MVL (Maximum Vector Length parameter) inclusive. The active vector length is usually written with the setvl instruction.

#### Vector instructions

Beside the base instructions that we can expect from a Vector Architecture (such as a move, add, xor and so on) it is also possible to find some useful operations related to the nature of the vector calculus [5]:

• vectorial load/store: are used to copy data between vector registers and memory. These instructions can be strided or indexed. The strided ones index the vector elements referring to a starting element and then adding (or subtracting) a certain stride to the base address. This kind of load/store is very fast, in particular in some special cases (as unit-strided or some optimized power of 2).

The vector elements into the indexed ones are basically pointed with a vector of indexes, added to a base address. This process does really slows down the operation but allows to directly select the elements.

- widening/narrowing: these operation are used to increase or decrease the size of the vector's contents. In fact, they are very useful when performing operations that need to increase the result size (as example a multiplication between to integer at 32 bit needs to have 64 bit to not loose information). There are also few operations that require the inverse resizing, as for the narrowing.

- rgather: those are very particular operations which are very advantageous when manipulating vectors. They allow to index a vector using another vector as index. Therefore, various patterns are possible. The pseudo code representing this operation is the following:

```

for (i=0; i<N; ++i)

x[i] = y[idx[i]];</pre>

```

where y is the starting vector, idx is the index vector and x is the result vector.

• reduction: finally, the reduction can perform an operation between a scalar and a vector and give a scalar as result (an easy example could be to calculate the maximum value between all the value contained in a vector and one scalar, the result would either be one of the element of the vector or the scalar).

Finally, all those operations can be *masked*. The masking is a common operation when there is branching or when complex patterns emerge. Normally one bit of the mask represent a whole word or byte into the vector. This bit indicates if the operation of the instruction should be performed for that specific element of the vector.

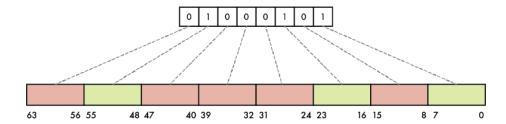

Figure 1.6. 8 bit mask, masking a 64 bit vector

In Figure 1.6 there is an example of an 8-bit vector masking a 64-bit vector. Each bit of the mask corresponds to 8 bit of the vector.

#### 1.1.3 Verification

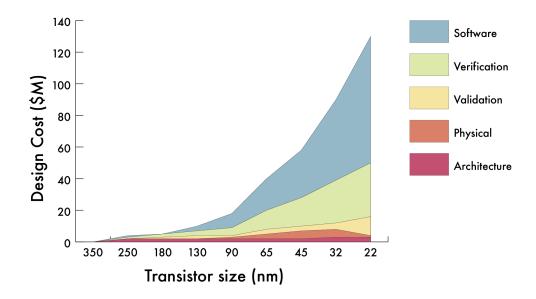

As the technology scales down, conflicting requirements for high performance, low-power and area arise. This lead to a complex design and to elevate the costs.

It is possible to see in Figure 1.7 how the cost for verification increases drastically with the shrinking of the technology node.

Figure 1.7. The design cost vs the technology node [6]

Verification is responsible to make sure that the design is in track with the specification. So, if the design complexity increases, the same does its verification process.

This is of course an issue for the time-to-market. In particular functional design verification takes 40-50% of the project resources. In other words, increasing the productivity of functional design verification and shorten the design / simulate / debug / cover loop is an essential task [6].

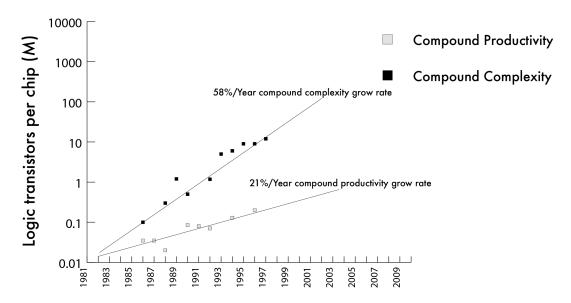

Moreover, the compounded complexity grows faster then the compounded productivity. This gap only means the verification needs to be faster and hence needs to implement more techniques. It is possible to see a study on the complexity/productivity gap in Figure 1.8

Figure 1.8. The gap between the complexity and the productivity [6]

This graph shows how the complexity rate is higher than the productivity rate during the years. This means that it is not possible to reach an equity only by increasing the number of tests or by adding some more checkers. More advanced techniques are needed to cope with the growing complexity.

In order to verify an RTL design, its specifications need to be stated as code. In this thesis all the tools implemented for the verification process are wrote in *SystemVerilog*. SystemVerilog is an hardware description language, born as an evolution of the Verilog language. Some extensions such as Objective-Oriented Programming elements and specific keywords for verification tools were added to it. The functionalities of a design can be stated by using the *checkers*.

#### Checkers

They are mainly composed by assertions and assumptions, some really powerful statements used to define the constraints of the DUT's behaviour.

Assertions and assumptions are syntactically identical, but the first one refers to the output signals while the second one to the input signals. They are mainly composed by two parts which are both conditions, even though they act differently. The first part is a condition to "fire", this means that when the condition is true the assertion, or assumption, starts checking for the second part [7].

The second part is another check on some condition, and can reveal the result of the check. At this point the possible results are *True* or *False*.

Both of them can be time consuming, and conditions on the edge are possible. It is also possible to create *properties* and *sequences* and then embed them into the assertions, in this way it is possible to reuse those parts.

Let's now see the basic structure of an assertion.

```

property property_1;

@(posedge clk_i)

a |-> b;

endproperty : property_1

assertion_1 : assert property ( disable_iff(rst) property_1) else $error("")

```

Basically if a is HIGH('1') then b is also expected to be HIGH('1').

The functionality is expressed into the property, then it is asserted into the assertion. It could be possible to recall tasks or processes, in this way it is possible to have more computational capabilities. It can also provide an error message to better identify the problem during simulations. When the signals into the <code>disable\_iff</code> function are asserted (in the example above it is the <code>rst</code> signal) the assertion is disabled. This means that the assertion does now need to be re-fired with a new starting condition.

#### Functional verification

The functional verification needs to verify whether the functionalities described into the specifications are met into the design. In order to verify functionally, the functionalities need to be defined. This is a very important part of the process, as this translation is never perfect and often highlights some critical points into the specs, such as omissions or inaccuracies. The functional verification is performed using simulations, this means that time is required to simulate the design behaviour and to check it against its specifications.

In functional verification the assertions and the assumptions are implemented in the simulation process to verify to correctness of the RTL design.

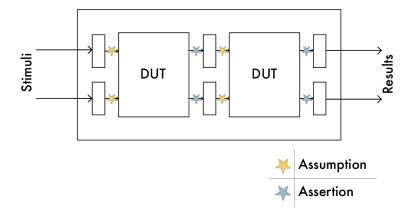

Figure 1.9. Assertions and assumptions into an RTL design

In Figure 1.9 it is possible to visualize how assertions and assumptions are used to verify functionally the RTL design. The assumptions are mainly checking the inputs and the assertions are mainly checking the outputs. It is possible to notice that the assertions for a DUT can be considered as assumptions for another one.

#### Formal verification

The formal verification can be done in different ways: theorem proving, that tries to prove the equivalence between specifications and design by using mathematical reasoning; equivalence checking, useful when performing optimization to the design, trying to demonstrate that the various versions are mathematically equivalent; and model checking, which try to find counter example on the behaviour of the design, and, if a counterexample exists, the Formal tool provides an example of the specific case to demonstrate the falsity. It is performed using assumptions to assume the design behaviour and then using assertions to test it.

As already mentioned, the assertions and the assumptions in simulations are treated equally. This is not true in the formal verification [8]. In order to be performed, the formal assertions verification only needs to instantiate the RTL file and the checkers file. Then it uses the assumptions as drivers for the RTL, and finally it tries to prove wrong the assertions using mathematical simplifications. Hence, here it is possible to see how the assumptions work differently. If a property is assumed it can never be proved wrong. Only assertions need to

be checked. The formal tool, in this project, was only used to perform model checking. The tool used is provided by Mentor, and it is called Questa Propcheck. There are different possible outcomes occurring while verifying:

- vacuous proof: the case is vacuously proven when the assertion is always true given the assumptions. This means probably there is some mistake into the assumptions or the assertions;

- **proof**: starting at the initial state, no legal stimulus exists that causes in the assertion to be violated. It is normally proven in the first 10-100 cycles;

- **firing**: a counterexample to the assertion exist, this means that there is a bug in design, or the specifications are not well defined;

- firing with warnings: a counterexample to the assertion exist, but it does not use primary inputs. This means that there are uncontrolled internal values that cause a fail;

- **inconclusive**: the formal analysis timed out before demonstrating the assertion. This could be also meaning the complexity is too high to be elaborated with math tools;

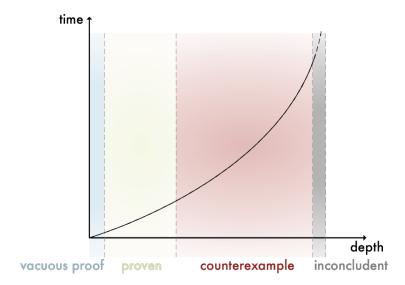

In Figure 1.10 are graphically summarized all the possible outcomes previously exposed. It is shown how the time required to prove an assertion grows exponentially with the depth of the analysis. There are also illustrated the various "zones" in which the result is produced.

Figure 1.10. Growing complexity and expected results in formal verification.

#### Coverage

The whole process of verification does also need to have a direction. Coverage is employed to do it.

Coverage is very useful and can be performed on functionalities or code:

- functionality: it measures the cover of all the functionalities stated by the specifications. This approach makes it possible to assure that all the requirements are met. But this also means that there is no information about unused RTL.

- code: it measures the cover of the RTL code. This means that it is possible to acknowledge whether there is unused logic and possibly some branch of the flow. Although, this implies that there is no check about the functionalities implemented.

The main goal is to take the coverage to 100%. But at the same time it is easy to fool the coverage, because it depends on how the cases are taken into account.

In order to use all of these techniques there is the need of a structure to contain and control them. This structure is designed following the *Universal Verification Methodology* (UVM). The UVM is thought to verify circuits

designs, and it is provided of Object-Oriented Programming elements, in order to enhance reusability. Later on this Chapter the particular case of this work is discussed.

### 1.2 Context

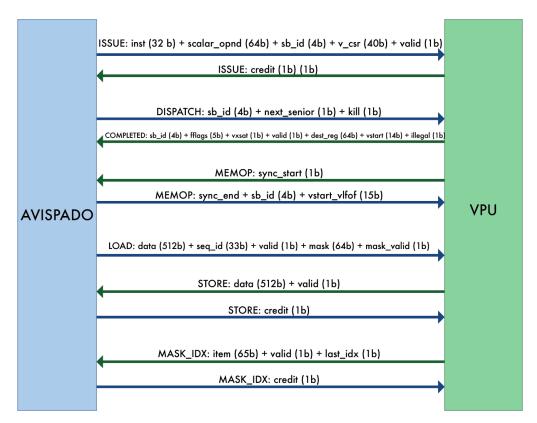

Prior to start, it is important to highlight that the VPU is designed to be the co-processor of a scalar core named Avispado. This core is under development by SemiDynamics, which works together with the BSC at the EPI project. In order to implement and test the VPU a simulator of the Avispado core was used, it is called Spike. It was initially developed to simulate RISC-V core, but for this project it was extended to simulate also the Vector-Extension. So, Spike is simulating both the core and the VPU, to use it as a scoreboard. In Figure 1.11 it is possible to see the interface between Avispado and the VPU for all the instructions.

Figure 1.11. Avispado-VPU interface

The instructions are issued with a credit system, whose number corresponds to the depth of the issue queue of the VPU. All the informations about the interface are reported into the paper published by SemiDynamics [9]

#### 1.2.1 The VPU

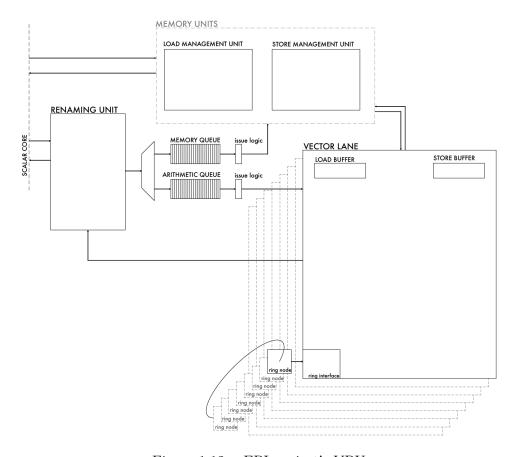

In Figure 1.12 it is possible to find a simplified scheme of the implemented VPU.

Figure 1.12. EPI project's VPU

It is important to notice that the VPU implemented is a decoupled architecture, this means that two operations can be executed at once only in case they are not both memory operations nor arithmetic ones.

The main elements composing the VPU are:

• Renaming Unit: the scope of this unit is to remove false dependencies due to the naming of the registers. This is possible because of the virtual

memory. The processor only uses logical registers, which in this component they are mapped to physical registers using the Free Register List (FRL). Write-to-write dependencies are removed if possible, in order to avoid Data Hazards.

- Queues: the VPU is a decoupled vector architecture, this means that the arithmetic instructions and the memory instructions are buffered in different queues. In Figure 1.12 it is possible to see how the two queues are independent in the issue stage. The vector lane is capable of performing only one arithmetic instruction at time, so the issue queue must wait until the previous instruction finishes its execution, but simultaneously a memory instruction can be performed. The whole issue stage is composed by the queue and the issue logic. The number of entries in the issue queues is parameterized.

- Memory Units: as mentioned before, the only instructions that can access memory are the load and the store operations. There are different units working on memory instructions: The load management unit, the store management unit and the index and mask unit. As the name suggest their core task is respectively to load operations, to store operations and to mask the operations and provide the indexes. The possible addressing modes are strided or indexed.

- Vector Lane: the Vector Lane is the core of the VPU. It is composed by different vector processing lanes. This is a very common technique that allows to improve performance and scalability. In an ideal multi-lane vector architecture all the lanes are working simultaneously and thus efficiently, with the cost of more hardware to control the synchronization.

One of the most important submodules of the Vector Lane is the Vector Register File (VRF). This is designed with only one read/write port, this because it is important to limit the area usage, and so to increase the operating frequency. It is necessary to have a buffer in order to avoid streaming problems and bubbles inside the pipe.

This solution implies the existence of some cost in terms of latency, due to the starting of a new instruction. Inside the Vector Lane the Write-Back Buffer (WB) and the Load Buffer (LB) are important as well. Those buffers store the data until the VRF line is complete. There is also the Store Buffer (SB) which holds the data read from the register file and then sends it to the Store Unit. Eventually when an instruction is completed the physical register are freed.

The VPU can be configured with different numbers of lanes from 1 up to 8, the default value is 8.

• Lane Interconnection: due to the range of the Lanes, which can be any value between 1 and 8, it is important to have a system capable of synchronizing all of them. There are also some operations which require to use multiple lanes at once to perform the execution, so an unidirectional ring intercommunication is implemented between the lanes.

It is also important to point out how the memory is organized in order to understand how some operations work.

The vectors are distributed into the different lanes. Indeed it is possible to say the Vector are sliced into the lanes, this means that an efficient organization is needed in order to understand where to put the right data.

According to the RISC-V V-extension, vector elements can have different sizes. The parameter that describes the size of an element is the Standard Element Width (SEW). This is determined by the Control and Status Register (CSR) named *vsew*. The maximum supported SEW into the EPI project is 64 bit. Also the maximum VLEN is equal to 16384 bit, so 2kB.

The number of elements a vector registers holds is given by VLEN/SEW, according to the Table 1.2.1:

| SEW | ELEMENTS |

|-----|----------|

| 64  | 256      |

| 32  | 512      |

| 16  | 1024     |

| 8   | 2048     |

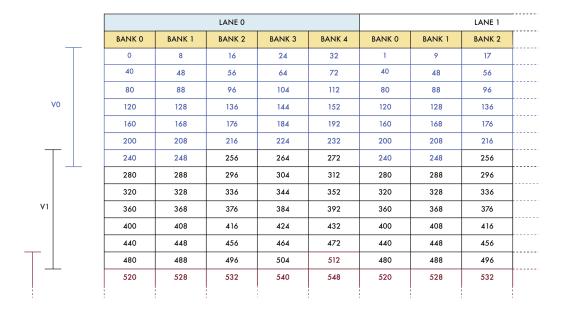

In Figure 1.13 it is possible to see the structure used for SEW = 64 bit as examples.

Figure 1.13. VRF with SEW = 64

Notice that the sub-banks are more than 1 only when the SEW is not equal to 64.

In Figure 1.14 it is possible to identify the sub-banks as subdivision of a bank.

| LANE 0     |            |     |      |      |      |       |      |        |      |

|------------|------------|-----|------|------|------|-------|------|--------|------|

| BANK 0     |            | BAN | 1K 1 | BAN  | √K 2 | BAN   | 1K 3 | BAN    | 1K 4 |

| 0          | 1          | 16  | 17   | 32   | 33   | 48    | 49   | 64     | 65   |

| SUB-BANK 0 | SUB-BANK 1 |     |      |      |      | 1     |      |        |      |

|            |            |     |      | <br> |      | 1<br> |      | !<br>! |      |

Figure 1.14. VRF with SEW = 32

#### 1.2.2 The UVM

As mentioned before, the UVM is the solution to the standardization problem of the verification. In fact, it is a transaction-level methodology (TLM) designed for testbench development. It is a class library that facilitates writing configurable and reusable code [6].

The testbenches created are designed to be reusable, as a result less code and more production is achieved.

This is mainly obtained with the polymorphism. It means an object can be used to define a reusable class. Operating with this technique an object can be used as a super-class and other sub-classes can be created.

It works following an hierarchy method, and every component can only operate with the components above it. In this way multiple sub-components can be instantiated.

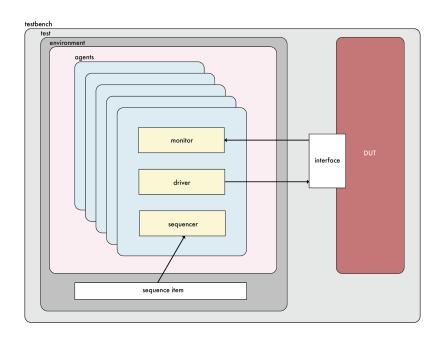

#### Generic UVM

In Figure 1.15 it is possible to see an example of a standard UVM.

Figure 1.15. A generic UVM

Let's proceed analyzing some elements of a standard UVM and its implementations in the EPI project.

- **Testbench**: typically, it instantiates the DUT (Design Under Test) and the UVM Test Class. Also it is responsible to configure the connections between them. There are different ways to communicate into an UVM and in this module is possible to choose them. It is also important to say that the Testbench instantiates the Test dynamically at run-time, enabling to compile it once and run many Tests.

- **Test**: this is the top-level component into an UVM testbench. Typically a base test class is defined to instantiate the top-level environment and then it is extended to the specific case.

- Environment: it is a component that defines the environment of a test. It aims to define all the agents and the scoreboards. The top-level environment instantiates and configures the reusable verification IP and defines its default configurations based on the application of the test.

Typically there is a different environment for each interface of the DUT.

- Sequence Item: it is the fundamental lowest denominator object in the UVM hierarchy. It can also be defined as a transaction and it is the smallest data transfer that can exist in a UVM. It can include variables and constraints.

- Sequence: it is generated by the environment using the sequence item. It is an ordered collection of transactions. Mostly it can impose some constraint to the variables generated into the sequence item.

- Agent: it is one of the most important components of the UVM. It groups together all the components that are dealing with the DUT and so a specific DUT interface. Normally there is a different agent for every interface or DUT. This allows specific sequencers for specific stimulus. It can also be active or passive depending on its action on the DUT: if it sends signals to stimulate the DUT it is considered active, and otherwise passive.

It contains:

- Driver: it is the component responsible for the communication between the UVM and the DUT at pinlevel. It receives the sequences from the sequencer and then converts them into signals, following the interface protocol. This action is observed by another component, the (command) monitor.

It can be turned off when the agent is defined as passive. In this way there is no other component sending signals to the DUT.

- Sequencer: it controls the requests and the responses between the driver and the sequence item. So it is a controller.

- Monitor: it observes the outputs of the DUT at pinlevel. Then transforms those signals into transactions for the analysis. On a larger stage, those transactions are very likely then compared with the expected outputs. This is normally done in the scoreboard. It can perform internally also some processing. The signals the monitor is observing could be monitored into the driver, but this would mean violating the modularity choices for the UVM.

- Scoreboard: it is a checker for the outputs of the DUT. It compares the transactions obtained by the monitors against a predicted result. There are different ways to generate a predicted result and so a scoreboard, it often uses a C/C++ model, but it is possible to use also other languages as well.

It is important to point the UVM works in different phases. It is possible to macro-divide the process in 3 phases: the *build phase*: here the components are constructed from the top, in this phase an important sub-phase is present, the *connect sub-phase*: here all the components are connected upwards; the *run phase*: in this phase the simulation is ran, and finally the *cleanup phase*: here all the results are checked and reported.

In Figure 1.16 it is illustrated a simple scheme representing all the phases.

Figure 1.16. UVM phases

In the EPI project two different UVM structures were implemented. One to test all the VPU (and its interface with the scalar core) and another one to test the submodules. This approach was chosen because it is not always possible to test all the corner cases with an UVM testing the whole VPU.

Let's proceed with a brief analysis of those two structures.

#### Main UVM

The main UVM is interfaced with Avispado and it is composed following the standard structure. It was mainly used to support the use of a scoreboard (Spike) and then to implement then some checkers and some coverage controls.

The majority of the automatic tests are made with this structure, and they are scripted to run all the night and to produce a valid dataset to then find and fix the bugs. Those tests are created using random RISC-V vector instructions, with some constraints that allow the tests to be valid.

Using a simulator for Avispado as input, the driver is a little bit different from a standard one. Indeed, the input are not controlled at pinlevel but vector instructions are sent to the core, which will then produce a correct input for the VPU.

Those instructions are ultimately compared with with the scoreboard and a result is produced.

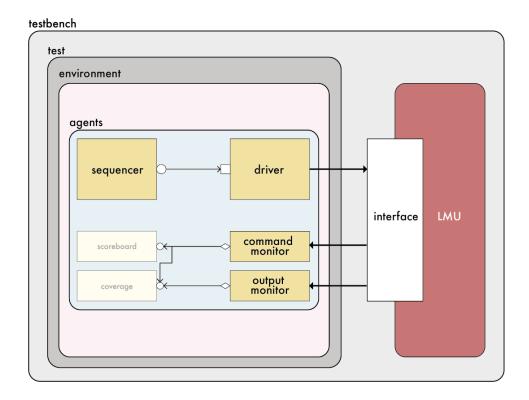

#### Submodules UVM

Another structure was necessary due to the different interface, and so to different drivers. It is not always trivial to create a driver for a submodule, because the handshake processes can be very complex, thus it would be possible to introduce some error in the verification structure.

As an UVM structure is useful when driving an monitoring all the signals of a module, this technique was used for the Load Management Unit but not for the Load Buffer. This because the handshake process for the Load Buffer is complex, and so would have been the UVM, with the possibility to introduce some errors. The structure of the LMU's UVM is represented in figure 1.17.

Figure 1.17. A small UVM for the submodules

It is possible to observe the scoreboard and the coverage are disabled in this application. In reality a scoreboard was implemented for each of them, but was handles with a different methodology discussed later on the next Chapter.

# Chapter 2

# Contributions

### 2.1 Submodules and Specifications

The main focus of this thesis will be on two important submodules in charge of the load instructions:

Load Management Unit and Load Buffer.

### 2.1.1 Load Management Unit

This module is in charge of handling the load operations. It receives cache lines from Avispado containing the data for the load. Then, the LMU rearranges the data to distribute it to the vector lanes. The load operation can be strided or indexed. Since the VPU is able to work out-of-order and with two loads in parallel, an ID system is necessary, so each instruction comes with an ID. In particular the load operation comes with the signal  $seq_id_i$ . This signal identifies the load and contains all the determinant informations about it.

The main elements of this submodules are:

- **Shifter**: it is useful to have the first bit in other position than the MSB or the LSB position;

- **Compactor**: it is useful to compact all the valid elements. When the stride is equal to one the compactor is not used;

• Aligner: it is in charge to align correctly the elements for the output (lane, bank and sub-bank).

The main parameters defining this submodule are:

- MEM\_DATA\_WIDTH: width of the chunk of data received from Avispado. The standard value is 512.

- **SEQ\_ID\_WIDTH**: width of the *seq\_id\_i* that identifies the data coming from Avispado. The standard value is *33*.

- MAX\_NUMBER\_ELEMENTS: maximum number of elements that can be encoded in the chunk of data received (64 when SEW = 8 bit). The standard value is 64.

- MAVISPADO\_LOAD\_MASK\_WIDTH: Indicates the maximum number of mask bit that are received with the data. Every bit of the mask represents a byte into the data. The standard value is 64.

- NUM\_LANES: number of lanes. The standard value is 8.

#### Interface

| Signal                 | Description                                       |

|------------------------|---------------------------------------------------|

| load_granted_i         | a load is granted,                                |

|                        | it will have a certain sew_i and stride_i         |

| load_granted_sb_id_i   | the id for the issued load,                       |

|                        | can be issued up to 2 loads                       |

| indexed_load_granted_i | the granted load is indexed                       |

| load_sync_end_i        | indicates if the load is ended                    |

| load_sync_end_sb_id_i  | indicates the load id of the ended load           |

| load_data_valid_i      | indicates if the data in load_data_i bus is valid |

| load_data_i            | data received from Avispado                       |

| seq_id_i               | the sequence id (described below)                 |

| mask_valid_i           | validity of mask_i signal                         |

| mask_i                 | mask bit to mask load_data_i                      |

| sew_i                  | identifies the size of each vector element        |

| stride_i               | stride indicated in bytes                         |

Table 2.1. Input signals to the LMU

| Signal               | Description                                       |

|----------------------|---------------------------------------------------|

| load_data_o          | output data sent to the lanes                     |

| load_dvalid_o        | indicates if the data in load_data_o bus is valid |

| mask_o               | mask bit to mask load_data_o                      |

|                      | it is needed also for not masked inst.            |

| element_ids_o        | identifies each element sent in load_data_o       |

| sb_id_o              | identifies the instruction                        |

| vstart_self_o        | identifies the first valid element                |

|                      | in the chunk of data received in load_data_i      |

| vstart_next_o        | identifies the last valid element                 |

|                      | in the chunk of data received in load_data_i      |

| min_element_id_idx_o | index of the first valid                          |

|                      | element in elements_ids_o of each lane.           |

Table 2.2. Output signals to the LMU

In the Tables 2.1 and 2.2 are reported respectively the input and the output signals of the LMU, together with their description.

#### Sequence ID

The sequence id ID is necessary as the memory system does not guarantee the inorder arrival of elements. Hence, this signal contains all the informations needed to correctly elaborate the data.

The  $seq_id_i$  is composed by:

- **seq\_id\_i[4:0**] = *v\_reg*, identifies the logical vector register in which the data should be written;

- seq\_id\_i[15:5] = el\_id, identifies the lowest valid element id contained in the chunk of data being transmitted;

- seq\_id\_i[21:16] = el\_off, identifies the offset in the chunk of data being transmitted;

- seq\_id\_i[28:22] = el\_count, identifies the number of valid elements being transmitted. Masked elements are valid elements;

- $seq_id_i[32:29] = sb_id$ , scoreboard id of the load instruction that requested the data.

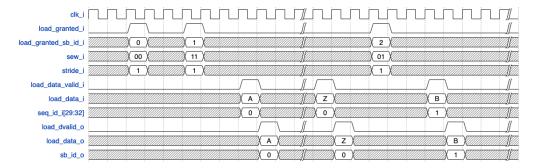

#### Handshake

The handshake protocol with the different components is as important as the data manipulation. Following, there is a simple example with the stride value equal to 1 and offset equal to 0 (meaning that there is no manipulation on the input data). The procedure for the handshake is the following:

- 1. Up to 2 load are granted by memory queue with the *load\_granted\_i* signal. The SEW and stride information of the relative instruction are passed;

- 2. Avispado sends the data and the seq\_id\_i with its seq\_id\_i;

- 3. The next clock cycle, the data is at the output of the LMU towards the Vector Lane:

- 4. When a load is finished, another load can be granted.

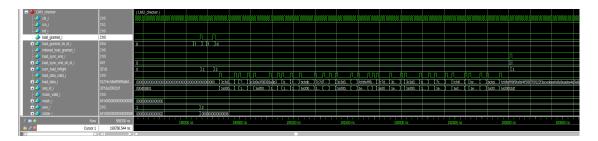

Figure 2.1. Timing Diagram unit-strided load for the LMU

In Figure 2.1 it is possible to see an example of an unit-strided load. This is a simple load, and its behaviour is discussed in the following section.

#### Strided Load

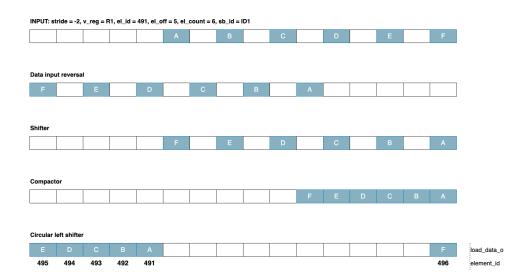

In this case all the valid elements are separated by a constant stride. If the stride is equal to 1, then it is called unit-strided load. Figure 2.2 shows how the LMU works in this case. The parameters (defined in the  $seq\_id\_i$ ) are defining the elements to consider.

Figure 2.2. Strided load handled by the LMU

#### **Indexed Load**

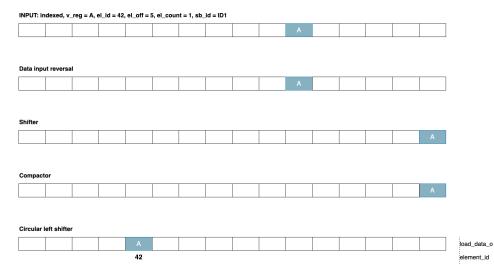

It is also possible to load values in an indexed way. By design, it was chosen that only one valid element at time can be sent, and so *el\_count* needs to be equal to 1. If the indexed load is requested with many valid elements, the cache line is sent multiple times with only one valid element each time. In Figure 2.3 it is possible to see an example of a simple indexed load.

Figure 2.3. Indexed load handled by the LMU

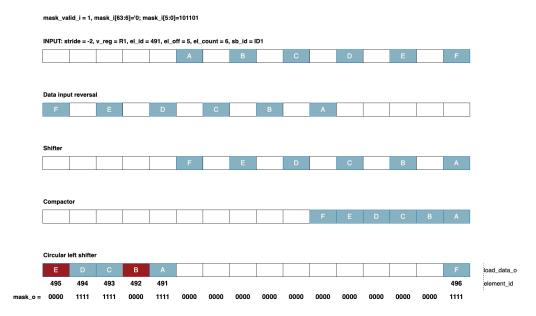

# Masked Load

All the load operations can be masked. This operation does not change the number of valid elements, but if an elements is masked, at the end of the process it will not be sent. In Figure 2.4 it is possible to see an example of the simple strided-load shown before, but this time, with a mask.

Figure 2.4. Strided load, with mask, handled by the LMU

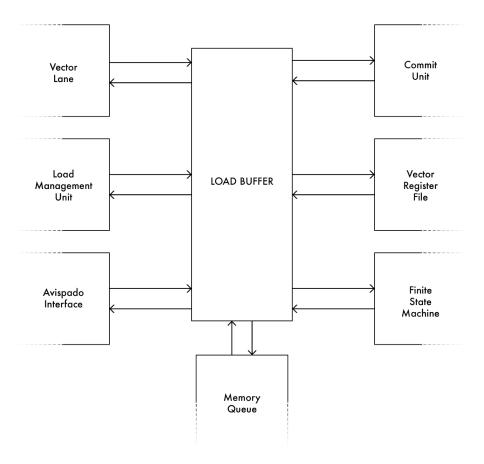

# 2.1.2 Load Buffer

The second submodule that is mainly in charge of the load operation is the Load Buffer. Its function is writing the data sent by Avispado to the Vector Register File. The data can come from different instructions inflight, and the Buffer will always try to optimize and group the data to write.

The LMU receives full cache lines of 512 bit from Avispado and forwards them to the corresponding Load Buffer for each lane (64 bit max per lane), depending on the  $seq\_id\_i$ . The position of the data into the LB will be determined by the element ID. Up to two loads can be inflight, but their associated cache lines can arrive out-of-order, although the implementation will be parameterized to accept N loads in flight.

# Interface

The Load Buffer is connected with a lot of modules. From the *Vector Lane* it receives the clock and the reset and communicates if there is a load inflight; with the *LMU* it exchanges all the data; from *Avispado* it knows if the operation has terminated; the requested handshake is handled with the *Memory Queue*; the data goes to the *Vector Register File*, synchronizing with the internal *Finite State Machine*; finally it can commit the result with the *Commit Unit*.

A simple connection structure is represented in Figure 2.5.

Figure 2.5. Load Buffer's interfaces

# Structure

There is a Load Buffer of each lane and there are three layers to buffer the elements. The layers are divided by the concept of Element Group. In fact, the

elements cannot be disposed in every combination, but every element, based on its element ID, has an exact location (based also on the SEW). The position of the elements follows the structure of the VRF explained in the first Chapter.

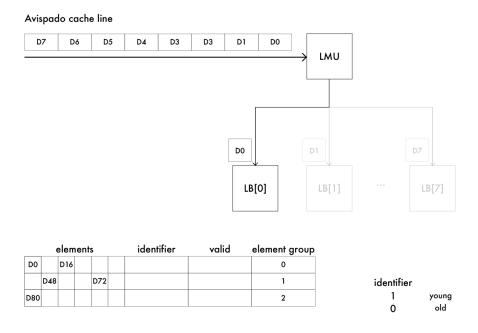

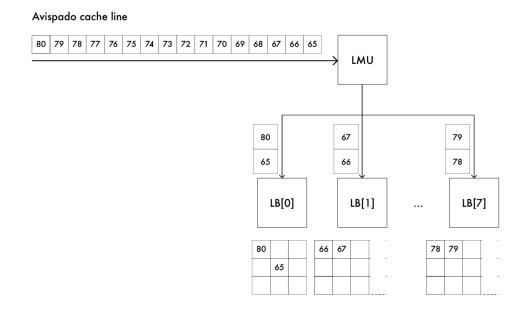

In Figure 2.6 it is possible to see a general connection between the LMU and the various Load Buffers.

Avispado cache line

# D7 D6 D5 D4 D3 D3 D1 D0 LMU D0 D1 D7 LB[0] LB[1] .... LB[7]

Figure 2.6. Data through the LB

In Figure 2.7 there is an example of the disposition of the elements of 64 bit. It is also important to say that the number of bits for each element group stays the same, this means that the number of elements depends on the SEW.

Figure 2.7. General case for the LB

The Load Buffers are mainly composed of 4 parts:

- *Elements*: are the values stored into the buffer. The elements are always 512 bit long, so there are 5 elements with SEW = 64, 10 elements with SEW = 32 and so on;

- *Identifier*: identifies the elements coming from the young or the old load;

- Valid: identifies if the elements are valid;

- *Element Group*: identifies the group of elements into the Vector Register File.

# Retry

There are cases in which three buffers are not enough to store all the elements. It is possible that more than three elements try to occupy the same position and thus causing a problem. This case is handled with a retry mechanism: one of

the elements is discarded and a new request is made to Avispado, to notify the retry. It is important to identify the element to discard when there is a retry, whether it is a new or an old one.

There are 4 possible cases:

- 1. if the incoming data comes from the *young load* and the buffer does only contain *data from the same load*, the data with the highest element group will be discarded;

- 2. if the incoming data comes from the young load and the buffer contains data from both the oldest and youngest loads, the incoming data will be discarded;

- 3. if the incoming data comes from the *old load* and the buffer only contains data from the same load, the data with the highest element group will be discarded;

- 4. if the incoming data comes from the *old load* and the buffer contain *data* from both the oldest and youngest loads, the data inside the buffer, the one from the young load will be discarded.

# Flow

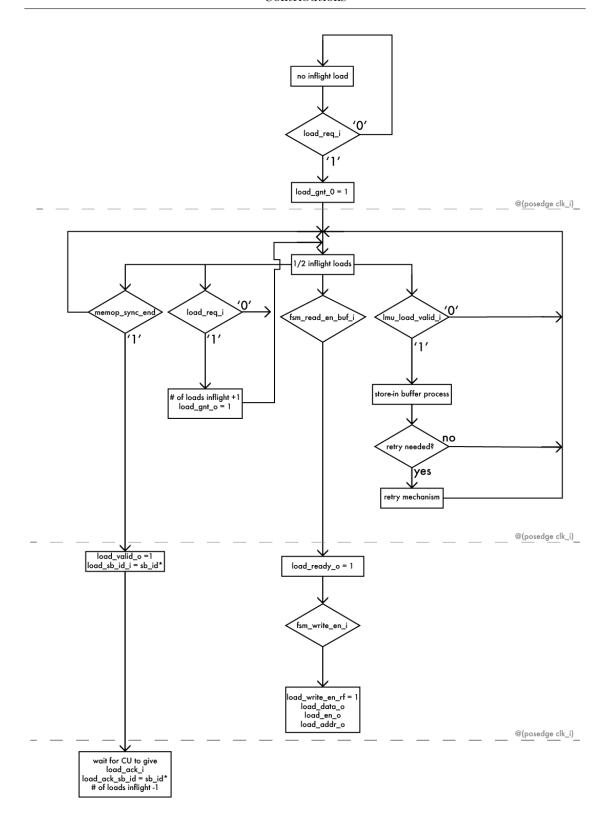

In Figure 2.8 it is possible to see a simple scheme of the LB's behaviour.

Figure 2.8. Working flow of the Load Buffer

Following the scheme it is possible to understand the main working flow of the Load Buffer. When the Load Buffer receives a request, it is granted if the number of loads inflight is less than two. For each request the LB can receive the data, activating the retry mechanism if necessary, or it can receive a  $memop\_sync\_end$  and then continue the process to finish the load. During this process it is possible that  $fsm\_read\_en\_buf\_i$  is asserted by the internal Finite State Machine of the Vector Lane, thus the LB can write the data in output.

# 2.2 Verification Plan

In order to have a better approach with the verification of a design, it is important to define a Verification Plan. There are many ways to write it. In this specific case, the Verification Team was working along with the Design Team to produce better specifications and not only to test the completed design. This means that the Verification Plan is done following the general rules to have a good value in future, but it is not entirely defined a priori.

Defining the approach to have does also mean defining the tools that will be used, in fact, many different of them were created, such as a *Test Plan*, an *UVM* and the *checkers*.

# 2.2.1 Test Plan

In order to have a good coverage of the cases, and good simulations to find bugs, it is very important to have a test plan.

The test plan defines all the different cases to test for a submodule or for the entire VPU. This means trying to find all the different corner cases stimulating the DUT. Whenever possible, a good test plan only includes different sets of stimulus, in this way an easy implementation is possible. But this situation does not cover all the possible cases. For instance, not every case could be tested in a submodule of the VPU only modifying the inputs from the scalar core. Which means that sometimes it is necessary to create some modified settings, to create the correct environment for the test.

It was created a test plan to stress the load operations. Those are affecting a lot of submodules of the VPU, but the focus will be on the Load Buffer and on

the LMU, mainly. Let's now analyze some of the created tests.

# Test on consecutive elements

Avispado cache line

The first test planned was a simple test about consecutive elements, this means that all the elements are sent in order. Of course this is a simple case, and it is thought to test if all the chain to the effective load are working. In fact, it is a regression test.

The only constraint meant to be in this test is the sequentiality of the elements. An example is the one reported in Figure 2.9.

# 15 14 13 12 11 10 9 8 LMU 8 9 15 LB[0] LB[1] ... LB[7]

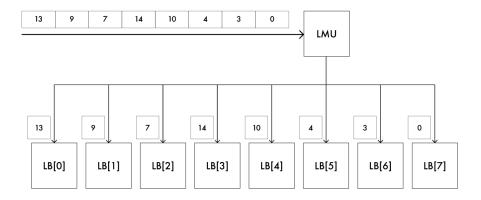

Figure 2.9. Sequential inputs from Avispado

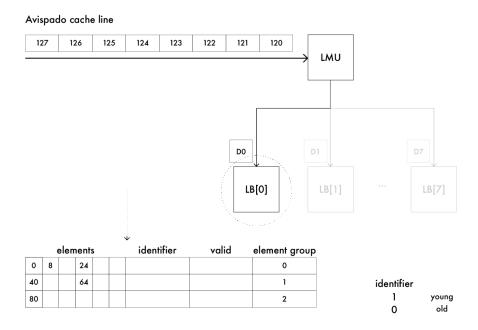

### Test on random values

The second kind of test to implement is the random test. This will stress the ability to use different elements ID and different loads at the same time. In this way all the handling for the positions, calculated based on the load and on the element ID, is stressed. It was created a special modality to constrain the randomness to the possible values. This was implemented in the UVM using the configurations for the sequence.

An example of random inputs from the same load is the one represented in Figure 2.10.

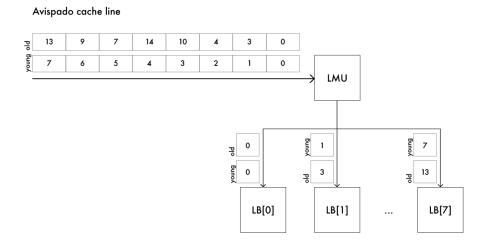

# Avispado cache line

Figure 2.10. Random inputs from Avispado

It is also possible to have inputs from two loads, as reported in Figure 2.11.

Figure 2.11. Random inputs from two loads

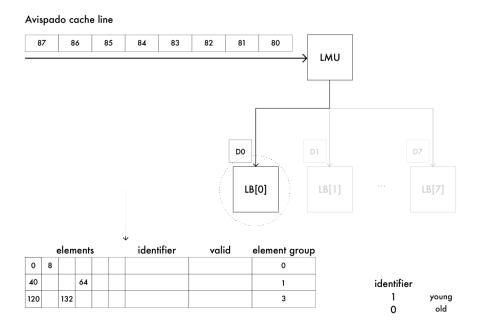

# Test on splitted elements

A very interesting case is revealed when studying the positions. Let's take into account a line of elements sent by the LMU to the Load Buffer. In this case the SEW needs to be different from 64, so the case will use SEW = 32. The data sent will be sequential, starting from 65 to 80. In this way it is possible to test if the output is disposed correctly and so if the Load Buffer for the Lane[0] stores 80-65 as values, in this order.

The situation explained is the one reported in Figure 2.12. It does also show how the input is splitted in the LB.

Figure 2.12. Input splitted into the LB

For reference let's analyze the binary used for this specific case.

```

#define __riscv_xlen 32

1

#include "test_macros.h"

2

3

4

.globl _start

.section .text

5

6

INIT_TEST(e32, 512)

7

8

9

la x1, init_region

10

addi x1, x1, 0x3c

vle.v v0, 0(x1)

11

12

13

END_TEST

14

15

# Initializes 4 registers (256 elements of 64 bit each one)

# TODO Do a macro that allocates N registers...

17

18

RVTEST_DATA (

.dword 0x0000000200000001, 0x0000000400000003; \

19

.dword 0x0000000600000005, 0x0000000800000007; \

20

.dword \texttt{0x00000000A00000009} , \texttt{0x0000000000000000} ; \texttt{\chi}

21

.dword 0x000000E0000000D, 0x00000010000000F;

22

.dword 0x0000001200000011, 0x0000001400000013;

23

.dword 0x0000001600000015, 0x0000001800000017; \

.dword 0x...

25

26

```

The test is initialized with a macro, defining the SEW = 32 and the size in bit = 512. Then the data (the one that follows the instructions) is loaded into a register as address, and is summed an offset of  $\theta x 3c$ , equal to 60 in decimal. This is the exact value needed to have the first sent element id = 65. As the number of elements will be 512/32 = 16 the element ids will go from 65 to 80.

### Test on retries

The last test typology is about the retry mechanism. This occurs when all the three lines are filled with an element in the same position, and then a fourth elements arrives, this means that the Load Buffer does not have another position for one of the elements, thus one of the elements needs to go back to the sender and a new request is made.

Considering SEW = 64, there are different versions about this test: it can be a simple in-order retry with elements 0-40-80-120-... as inputs, it can be out-of-order as 0-40-120-80-..., or it can be with two different loads.

The easier example is represented in Figure 2.13. 0-40-80 are already filling the spots where 120 will try to fit. So a retry is needed, discarding 120.

Figure 2.13. Stimulated retry

The out-of-order example is represented in Figure 2.14. 0-40-120 are already filling the spots where 80 will try to fit. So a retry is needed, discarding 120, and taking 80.

Figure 2.14. Stimulated retry with out-of-order values

# 2.3 Verification Process

The test executed are just the base for the verification. The tests can only define some functionalities, but a complete functional verification is required to test all of them. The normal approach starts with defining some functionalities and then comparing them to the design. This of course is the crucial part, because it is not always obvious how a specific case works. Also, there are different ways to test these functionalities.

# 2.3.1 Scoreboard

As seen into the test plan, an easy way to test the results is the scoreboard, thus to have a predicted value and then to compare it against the calculated one. Before the work of this thesis started, the UVM for the Avispado interface and a scoreboard for the VPU results were already implemented by the BSC

verification team. Let's briefly analyze how the scoreboard works and why it was useful to develop other tests.

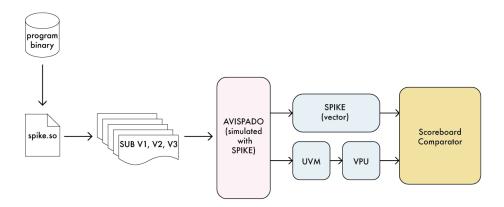

# Spike

Spike is a RISC-V ISA Simulator. For this specific project it was extended to support the vector extension. Spike has two functions, the first one is to simulate the Avispado core, producing stream of vector instructions and memory addresses. Those are feed to the VPU using the UVM. The second function is to produce a result to be compared with the one produced by the VPU. A simple scheme is represented in Figure 2.15.

Figure 2.15. Simulation path

This kind of tool is very useful because it can give an idea of the general result and at the same time can give hints about the working condition of the VPU. Of course it is just a first step, because often it is hard to find a bug only using the comparison with the final result.

# Load Management Unit's scoreboard

The aim of this thesis was principally based on testing the load operations, so a scoreboard for the LMU was created.

Recalling the LMU working model, the module first takes into account the stride, reversing the data in case of negative stride, then the data is positioned correctly again, then it is compacted considering the stride, and finally it is aligned to match with correct ID. In high level it was done using vectors, and a couple of steps were merged together. It is possible to see below the pseudo code representing the implementation in this way.

```

x = new[N_ELEMENTS][SEW];

y=new[N_ELEMENTS][SEW];

2

3

//first assignment

4

x[N_ELEMETS][SEW] = load_data_i[N_ELEEMTS*SEW]

5

6

//consider the stride

if(stride<0 && !is indexed)

8

9

y[i] = x[-i];

10

y[i] = x[i];

11

12

13

//from # of bytes to # of elements

14

local_stride = mod(local_stride * 8 / SEW);

15

16

17

//concatenate the data according to stride

x[N_ELEMENTS-1-i] = y[(N_ELEMENTS-1-i*local_stride-OFFSET)%N_ELEMENTS];

18

19

//shift the data according to EL_ID

20

k = EL_ID % N_ELEMENTS;

21

22

y[(N_ELEMENTS-1-(k+i))%N_ELEMENTS] = x[(N_ELEMENTS-1-i)]

23

```

Also the mask was predicted in a similar way, thus the masking step was then implemented with a simple check on the mask to have the correct result. In this way it is possible to have an exact result for the LMU, so when a test fails, it is always possible to check if the LMU performed correctly with the data it received in input.

# Load Buffer's scoreboard

For the Load Buffer the behaviour was really complicated, so a simplified version of a scoreboard was implemented. Hence, it does not work on the correct result operation-per-operation, because the LB has three layer of deepness and does always try to optimize the output. So, to implementing all the rules about the output would mean to create a similar structure with an high risk to create a bug in the verification model.

The idea was that the data observed as input would eventually become the

output data, placing in the correct position. This of course is not conflicting with the concept of retry. In fact, the retry mechanism only delays the data. It was implemented as an assertion to take advantage of the time correlation.

A pseudo version of this checker is represented below.

```

// Pseudo checker

if( lmu_dvalid_load_i) {

2

3

load_data_o[get_el_bank(el_id_i, sew_i)*SEW + SEW-1 -: SEW] == data_i;

4

}

5

6

7

// This function computes the bank of an element

function [BANK_IDX_SZ-1:0] get_el_bank([EL_ID_WIDTH-1:0] el_id,

9

10

[SEW_WIDTH-1:0] sew);

11

case (sew[1:0])

12

SEW64: get_el_bank=((el_id/N_LANES)%N_BANKS);

13

SEW32: get_el_bank=(((el_id>>1)/N_LANES)%N_BANKS);

14

SEW16: get_el_bank=(((el_id>>2)/N_LANES)%N_BANKS);

15

16

get_el_bank=(((el_id>>3)/N_LANES)%N_BANKS);

endcase

17

endfunction

```

Using the *element\_id* and the corresponding bank (based on the SEW), it is possible to predict the result for a specific location and compare it with the calculated one. In this pseudo code the time handling is not very visible, but the *if* statement will wait until the result goes as output.

# 2.3.2 Checkers

In order to connect the checkers to the whole structure the binding method was used: basically, when a file containing the checker is created, it is compiled with a bind option to connect it to an RTL file. In this way the files can be kept separate and the Design Team and the Verification Team can work together on different files [10].

```

vlog $PATH_LB/LoadBuffer.sv -mfcu -cuname $PATH_LBC/LoadBuffer_checker.svh

```

In the code above the compiling line for the LoadBuffer RTL is reported, with the binding option recalling the checker, in order to compile it as well. Then, as the following code illustrates, the bind statement is written into the checker file. This statement will connect all the in/out ports between the DUT and the checker.

```

| bind LoadBuffer LoadBuffer_checker bind_LoadBuffer_checker (.*);

```

# Load Management Unit's assertions

The main focus was on the calculated result and on the handshake with the other components. All the functionalities to be checked were define in the verification plan, then a list of assertions was used to produce a good checker. The list of all the checkers can be found in Appendix.

| name                   | functionality                                                                           |

|------------------------|-----------------------------------------------------------------------------------------|

| a_el_count             | when load_data_valid_i                                                                  |

|                        | then $seq\_id[28:22](el\_count) \le \frac{(n\_elements-el\_offset)}{(stride*8/sew)}$    |

| a_stride _i            | $  stride \cdot 8 $ can be one of the following $\pm (sew, 2 \cdot sew, 4 \cdot sew)  $ |

|                        | with SEW = $2^{(3+sew)}$ and not indexed load                                           |

| a_load_granted_i_known | when load_granted_i,                                                                    |

|                        | not unknown the following : SEW, granted_sb_id                                          |

| a_load_data_i_known    | when data_valid_i,                                                                      |

|                        | not unknown seq_id_i, load_data_i                                                       |

| a_sb_id_o              | when load_data_valid_i ,                                                                |

|                        | next clock cycle $sb_id_o(t) = seq_id_i[29:32](t-1)$                                    |

| a_load_dvalid_o_known  | when load_dvalid_o, outputs known                                                       |

| a_dvalid_o             | after load_data_valid_i,                                                                |

|                        | next clock cycle, load_dvalid_o                                                         |

| a_vstart_o             | correct v_start_next_o v_start_self_o,                                                  |

|                        | according to load_data_o                                                                |

| a_granted_ids          | can not be granted 2 loads with the same id at once                                     |

| a_indexed_instr        | when the load is an indexed load,                                                       |

|                        | el_count=1 and mask_valid_i = 0                                                         |

| a_load_sync_end_i      | for every load_granted_i                                                                |

|                        | there is eventually the corresponding load_sync_end_i                                   |

| a_load_grant_beh       | when $num\_load\_inflight = 2$ , $load\_grant\_i = 0$                                   |

| a_load_sync_end_beh    | when $num\_load\_inflight = 0$ , $load\_sync\_end\_i = 0$                               |

| a_load_req_sync_end    | load_sync_end_i cannot be simultanous with load_granted_i                               |

| a_el_count_sew_i       | when $stride\_i \neq (1, 2, 4) \cdot sew\_i$ (in bytes),                                |

|                        | $el_{count}$ has to $be = 1$                                                            |

| a_sb_correct           | when load_dvalid_i,                                                                     |

|                        | if it is given a sb_id not present in the fifo,                                         |

|                        | load_dvalid_o will be 0                                                                 |

| a_data_o               | correct load_data_o,                                                                    |

|                        | clk cycle after load_dvalid_i (stride/mask/indx)                                        |

| a_mask_o               | correct mask_o, according to load_data_o                                                |

| a_el_ids_o             | correct element_ids_o                                                                   |

| a_min_el_id_idx_o      | correct min_el_id_idx_o                                                                 |

| a_rsn_o                | when rsn_i load_dvalid_o = 0 and mask_o = '0                                            |

| a_rsn_i                | when rsn_i load_data_valid_i = 0                                                        |

|                        | and load_granted_ $i = 0$                                                               |

Table 2.3. Assertions on LMU

As it is possible to see in Table 2.3, there are different assertions possible for a single submodule. Here they are separated by colour distinguishing the different "categories". Indeed, the red ones are checking the basic signals behaviour and the handshakes. An example is **a\_dvalid\_o**:

```

property p_dvalid_o;

@(posedge clk_i)

load_data_valid_i && sb_correct |-> ##1 load_dvalid_o;

endproperty : p_dvalid_o

a_dvalid_o : assert property( disable iff(!rsn_i || kill_i) p_dvalid_o)

else $error('LMU did not compute any output');

```

- load\_data\_valid\_i is the input necessary to fire the assertion;

- **sb\_correct** is the result of a task, that calculates if the *scoreboard\_id* is a valid one;

- |-> is the separation between the firing condition and the checking one. It is not time consuming (the time consuming version would be |=>), so the check for the second condition starts immediately;

- ##1 command refers to 1 clock cycle(s) delay;

- load\_dvalid\_o asserted is the expected output.

The light blue ones are scoreboard-like assertions, indeed are checking the scoreboard\_id, the data in output and also the masks. They use the results of the tasks to check the values, it is possible to see an example in **a\_el\_ids\_o**where it shown how an assertion uses the result of a task.

```

//task

1

task compute_ids(int unsigned SEW, int unsigned EL_COUNT,

2

int unsigned EL_ID, int unsigned N_ELEMENTS);

3

4

int unsigned f_v_e, i, j;

5

6

// f_v_e is the index of the first 11-bit-element

7

// of computed_el_id_o where we have to put an EL_ID

8

9

f_v_e = EL_ID % N_ELEMENTS; // find the first valid element

f_v_e = f_v_e * SEW / 8 ; // multiply it by the number of bytes per el

10

11

12

// initialize to 0

for(j=0;j<MAX_NUMBER_ELEMENTS;j++) begin</pre>

13

14

computed_el_id_o[j] = '0;

15

for(j=0;j<EL_COUNT;j++) begin</pre>

17

18

for(i=0;i<SEW/8;i++) begin

computed_el_id_o[(f_v_e+i+(j*SEW/8))%MAX_NUMBER_ELEMENTS]

19

= EL_ID+j;

20

21

end

22

end

23

endtask : compute_ids

24

25

// property

26

27

property p_el_ids_o;

bit [MAX_NUMBER_ELEMENTS-1:0][EL_ID_WIDTH-1:0] buffer_ids;

28

29

@(posedge clk_i)

(load_data_valid_i && sb_correct, buffer_ids = computed_el_id_o) | ->

30

##1 element_ids_o == buffer_ids;

31

32

endproperty : p_el_ids_o

33

//assertion

34

a_el_ids_o : assert property( disable iff(!rsn_i || kill_i) p_el_ids_o )

35

else $error('mismatch in element_ids_o');

36

```

It is possible to see that the property uses the value <code>computed\_el\_id\_o</code>, a global variable. It is important to say that the task <code>compute\_ids</code> is not called by the property but from another external process not displayed here. Finally, the yellow ones are just checking the conditions for the reset and the expected output.

It is also important to notice that some of those are not assertions, but assumptions. This means that they are conditions on the input and not on the outputs. There is no difference for the Functional Verification, unlike with Formal Verification.

# Load Buffer's assertions

A similar approach was adopted for the Load Buffer. Having a lot of interfaces the LB has also a lot of handshakes, and so assertions. For this reason, in the Table 2.4 are only reported some categories containing all the assertions for an interface.

| name                   | functionality                                              |

|------------------------|------------------------------------------------------------|

| AVISPADO IF            | this is the interface with the scalar core                 |

| a_mem_sync_end_i       | if mem_sync_end_i is high,                                 |

|                        | memop_sb_id_i must be a known value                        |

| a_valid_after_sync_end | for every memop_sync_end_i (with a valid memop_sb_id_i)    |

|                        | there will be a load_valid_o (with correct load_sb_id_o)   |

| a_memop_sync_end_num   | if num of memop_sync_end_i = num of load_ack_i $+2$ ,      |

|                        | then only memop_sync_end with                              |

|                        | a sb_id different from the ones stored                     |

| a_load_ack_i_num       | if the num of load_ack_i is in excess,                     |

|                        | we assume this ack is for a different operation            |

| a_unique_request       | there can not be a request with the same sb_id             |

|                        | of an inflight load                                        |

| LMU INTERFACE          | from this interface the LB receive the cache lines         |

| MQ INTERFACE           | from this interface the load are requested/granted         |

| FSM INTERFACE          | from this interface comes the enable to write on the VRF   |

| CU INTERFACE           | to this interface the ids for and ended load are sent      |

| VRF INTERFACE          | this is the interface to load the data                     |

| a_load_inflight        | load_inflight_o is checked,                                |

|                        | it can be 1 when the number of load inflight is 1 or 2 and |

|                        | it can be 0 otherwise                                      |

| a_load_ready_o         | when load_inflight_o = 1 and $lmu_dvalid_load_i = 1$ ,     |

|                        | if there is fsm_read_en_lbuf_i,                            |

|                        | the next clock cycle there is load_ready_ $o = 1$          |

| a_data_corruption      | check that each element that enter                         |

|                        | will eventually exit in correct position                   |

| VL INTERFACE           | from this interface the clk and the rst are recived        |

Table 2.4. Assertions on LB

A good example for the handshake is  $a\_mem\_sync\_end\_i$ . This is an assumption on the inputs, but will be treated as an assertion.

```

property p_mem_sync_end_i;

@(posedge clk_i)

memop_sync_end_i |-> !$isunknown(memop_sb_id_i);

endproperty : p_mem_sync_end_i

a_mem_sync_end_i: assume property(disable iff(!rsn_i||kill_i) p_mem_sync_end_i)

else $error('unknown memop sd id on memop_sync_end_i asserted');

```

The property is using the system function  $\pmb{sisunknown}$ , this function returns if the value passed is unknown ('X' or 'Z'). So basically when  $memop\_sync\_end\_i$  is asserted, the value of its scoreboard id must be known.

Then  $a\_data\_corruption$  is the scoreboard like discussed before, and finally there are the reset's ones. The assertions are reported into the Appendix.

# 2.3.3 Drivers

The other tool used to test the submodules is the Driver. It is a file that defines the stimuli and their order. A very specific order of signals defines an operation. It is then possible to create the situation in which the DUT will work as expected. It is important to notice that the driver is enabled only when the UVM is configured as ACTIVE.

# Load Management Unit

This is the only submodule on which was developed a driver, due to the reduced complexity. In fact, the driver can be very complex when different handshakes are present.

In the next page it is possible to see one of the operations implemented into the driver, as example.

```

if(command.op == gnt_op) begin

1

// randomizations

2

3

SEW = command.sew_i;

SEW = (2**(3+SEW))/8; // in number of bytes , for the stride in bytes

4

randomize(command.stride_i)

5

with {command.stride_i inside{1*SEW,2*SEW,4*SEW,-1*SEW,-2*SEW,-4*SEW,

6

7

command.n*SEW};};

8

9

randomize(command.load_granted_sb_id_i)

10

with{!(command.load_granted_sb_id_i inside

{fifo[0].sb_id, fifo[1].sb_id});};

11

12

// check how many inflight load

13

14

if (!fifo[0].done && !fifo[1].done ) begin

@(posedge lmu_if.clk_i);

15

lmu_if.load_data_valid_i = 0;

16

lmu_if.load_sync_end_i=1;

17

18

lmu_if.load_sync_end_sb_id_i=fifo[command.which_load].sb_id;

fifo[command.which_load].done = 1;

19

end

20

21

// driving

22

@(posedge lmu_if.clk_i);

23

lmu_if.load_sync_end_i=0;

24

lmu_if.load_sync_end_sb_id_i='0;

25

26

@(posedge lmu_if.clk_i);

lmu_if.load_sync_end_i=0;

27

lmu_if.load_sync_end_sb_id_i='0;

28

29

lmu_if.op = gnt_op;

lmu_if.rsn_i = 1'b1;

30

lmu_if.kill_i = 1'b0;

31

32

lmu_if.load_granted_i = 1;

33

lmu_if.indexed_load_granted_i = command.indexed_load_granted_i;

lmu_if.load_granted_sb_id_i = command.load_granted_sb_id_i;

34

35

lmu_if.load_data_valid_i = 0;

lmu_if.load_data_i = '0;

36

37

lmu_if.seq_id_i = '0;

lmu_if.mask_valid_i = 1'b0;

38

39

lmu_if.mask_i = '0;

lmu_if.sew_i = command.sew_i;

40

41

lmu_if.stride_i = command.stride_i;

42

// update the fifo

43

if (fifo[1].done ) begin

fifo[1].SEW = command.sew_i;

44

fifo[1].STRIDE = command.stride_i;

45

fifo[1].sb_id = command.load_granted_sb_id_i ;

46

fifo[1].is_indexed = command.indexed_load_granted_i;

47

fifo[1].done = 0;

48

49

else if( fifo[0].done ) begin

50

51

fifo[0].SEW = command.sew_i;

fifo[0].STRIDE = command.stride_i;

52

fifo[0].sb_id = command.load_granted_sb_id_i;

53

54

fifo[0].is_indexed = command.indexed_load_granted_i;

fifo[0].done = 0;

55

56

@(posedge lmu_if.clk_i);

57

58

lmu_if.load_granted_i = 0;

-> lmu_if.new_input;

59

end

60

```

The operation implemented is the granting of a load request. The code is mainly divided in three parts:

- the *first* one makes some randomization for the data while it checks if the driver is following the assumptions about the inputs (in this case on the loads inflight);