# Active Gate Drivers for High-Frequency Application of SiC MOSFETs

By

#### Alejandro Paredes Camacho

Thesis submitted in partial fulfilment of the requirement for the PhD degree issued by the Universitat Politècnica de Catalunya, in its Electronic Engineering Program.

Supervisors: Dr. Jose Luis Romeral Martínez Dr. Vicent M. Sala Caselles

Terrassa, Barcelona December 2019

A mi madre,

María Luisa Camacho Ramos

### Abstract

The trend in the development of power converters is focused on efficient systems with high power density, reliability and low cost. The challenges to cover the new power converters requirements are mainly concentered on the use of new switching-device technologies such as silicon carbide MOSFETs (SiC). SiC MOSFETs have better characteristics than their silicon counterparts; they have low conduction resistance, can work at higher switching speeds and can operate at higher temperature and voltage levels. Despite the advantages of SiC transistors, operating at high switching frequencies, with these devices, reveal new challenges. The fast switching speeds of SiC MOSFETs can cause over-voltages and over-currents that lead to electromagnetic interference (EMI) problems.

For this reason, gate drivers (GD) development is a fundamental stage in SiC MOSFETs circuitry design. The reduction of the problems at high switching frequencies, thus increasing their performance, will allow to take advantage of these devices and achieve more efficient and high power density systems.

This Thesis consists of a study, design and development of active gate drivers (AGDs) aimed to improve the switching performance of SiC MOSFETs applied to high-frequency power converters. Every developed stage regarding the GDs is validated through tests and experimental studies. In addition, the developed GDs are applied to converters for wireless charging systems of electric vehicle batteries. The results show the effectiveness of the proposed GDs and their viability in power converters based on SiC MOSFET devices.

#### Keywords

Electromagnetic interference High frequency converters Gate drivers Silicon carbide SiC MOSFETs Wide-bandgap devices

#### Resumen

La tendencia en el diseño y desarrollo de convertidores de potencia está enfocada en realizar sistemas eficientes con alta densidad de potencia, fiabilidad y bajo costo. Los retos para cubrir esta tendencia están centrados principalmente en el uso de nuevas tecnologías de dispositivos de conmutación tales como, MOSFETs de carburo de silicio (SiC). Los MOSFETs de SiC presentan mejores características que sus homólogos de silicio; tienen baja resistencia de conducción, pueden trabajar a mayores velocidades de conmutación y pueden operar a mayores niveles de temperatura y tensión. A pesar de las ventajas de los transistores de SiC, existen problemas que se manifiestan cuando estos dispositivos operan a altas frecuencias de conmutación. Las rápidas velocidades de conmutación de los MOSFETs de SiC pueden provocar sobre-voltajes y sobre-corrientes que conllevan a problemas de interferencia electromagnética (EMI).

Por tal motivo, el desarrollo de controladores de puertas es una etapa fundamental en los MOSFETs de SiC para eliminar los problemas a altas frecuencias de conmutación y aumentar su rendimiento. En consecuencia, aprovechar las ventajas de estos dispositivos y lograr sistemas más eficientes y con alta densidad de potencia.

En esta tesis, se realiza un estudio, diseño y desarrollo de controladores activos de puerta para mejorar el rendimiento de conmutación de los MOSFETs de SiC aplicados a convertidores de potencia de alta frecuencia. Los controladores son validados a través de pruebas y estudios experimentales. Además, los controladores de puerta desarrollados son aplicados en convertidores para sistemas de carga inalámbrica de baterías de vehículos eléctricos. Los resultados muestran la importancia de los controladores de compuerta propuestos y su viabilidad en convertidores de potencia basados en carburo de silicio.

#### **Palabras clave**

Controladores de puerta Convertidores de alta frecuencia Carburo de silicio Interferencia electromagnética Dispositivos de banda ancha prohibida SiC MOSFETs

# Acknowledgement

Quiero dar mi especial agradecimiento al concejo nacional de ciencia y tecnología de México (CONACyT) por la beca otorgada durante mis estudios de doctorado.

Agradezco también a la secretaría de educación pública de México (SEP), por la beca otorgada al inicio del doctorado en la modalidad "Becas complemento"

También mi profundo agradecimiento al centro de investigación Motion Control And Industrial Applications por los apoyos económicos y material de laboratorio para realizar todas las pruebas de esta tesis.

Quiero agradecer también a mis directores de tesis, al Dr. Luis Romeral por la paciencia y por todo el apoyo otorgado para desarrollar esta tesis. Mi agradecimiento al Dr. Vicent Sala por la confianza, el soporte en las ideas fundamentales de esta tesis y por facilitarme la instrumentación y material para desarrollar la parte experimental de esta tesis.

Mi especial agradecimiento a Toni, Carles, Carlos, Efrén y Quique por compartir experiencias y consejos. Doy gracias a todos mis compañeros del grupo MCIA por la convivencia y compañerismo.

Finalmente doy gracias a mi familia, a cada uno de mis hermanos y en especial a mi madre por estar siempre en los mejores y peores momentos.

¡Gracias!

# Content of the document

| Abstract         |                                                                                    | v    |

|------------------|------------------------------------------------------------------------------------|------|

| Resumen          |                                                                                    | vii  |

| Acknowledg       | ement                                                                              | ix   |

| List of figure   | 25                                                                                 | XV   |

| List of tables   | 3                                                                                  | xvii |

| Acronyms         |                                                                                    | xix  |

| Nomenclatu       | re                                                                                 | XX   |

| 1. Introduct     | ion                                                                                | 1    |

| 1.1 Resear       | ch topic                                                                           | 2    |

| 1.2 Resear       | ch problem                                                                         | 3    |

| 1.3 Hypoth       | neses                                                                              | 4    |

| 1.4 Aim ar       | nd objectives                                                                      | 5    |

| 1.5 Thesis       | outline                                                                            | 6    |

| 2. Character     | ristics and gate drivers of SiC MOSFET devices                                     | 7    |

| 2.1 A brief      | analysis of SiC Power Semiconductors Devices                                       | 8    |

| 2.1.1            | Comparison and status of power semiconductor devices                               | 8    |

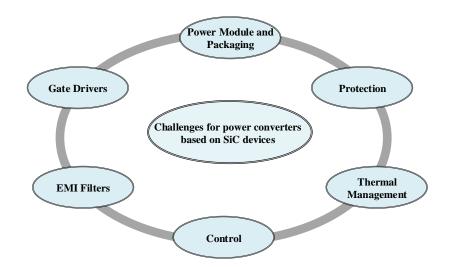

| 2.1.2            | Challenges for SiC-based power conversion system                                   | 9    |

| 2.2 SiC M        | OSFET power devices                                                                | 11   |

| 2.2.1            | Static characteristics of the SiC MOSFETs                                          | 11   |

| 2.2.2<br>problem | SiC MOSFETs dynamic characteristics and basic technics for reducing switching s 14 |      |

| 2.2.3            | Gate resistances optimization method                                               | 17   |

| 2.2.4            | Switching and conduction losses of the SiC MOSFETs                                 | 19   |

| 2.3 Gate di      | rivers for SiC MOSFET devices                                                      | 21   |

| 2.3.1            | State-of-the-art of GDs for SiC MOSFETs                                            | 22   |

| 2.3.2            | Commercial gate drivers                                                            | 24   |

| 2.4 Conclu       | isions                                                                             | 26   |

| 3. An active     | gate driver for improving the switching performance of SiC MOSFET                  | 27   |

| 3.1 Descrij      | ption and operation principle of the proposed gate driver                          | 28   |

| 3.1.1            | Operating at turn-on transition                                                    | 29   |

| 3.1.2            | Operating at turn-off transition                                                   | 30   |

| 3.2 An An        | alysis of AGD by using simulations                                                 | 31   |

| 3.3 AGD e        | xperimental validation                                                             | 36   |

| 3.3.1       | AGD design and parameter calculation for experimental studio                 |               |

|-------------|------------------------------------------------------------------------------|---------------|

| 3.3.2       | Time intervals calculation                                                   |               |

| 3.3.3       | Optimal values for reference voltage $V_{1,low}$ and optimal delay $t_{d,2}$ |               |

| 3.4 AGD     | evaluation                                                                   |               |

| 3.4.1       | Experimental validation analysis of the AGD                                  | 39            |

| 3.4.2       | Experimental studio of the AGD with different SiC MOSFET models              | 40            |

| 3.5 AGD     | viability study                                                              |               |

| 3.5.1       | SiC MOSFET performance analysis with AGD                                     | 41            |

| 3.5.2       | Electromagnetic interference analysis                                        |               |

| 3.5.3       | Cost study                                                                   | 43            |

| 3.6 Concl   | usions                                                                       | 44            |

| 4. Advance  | d gate driver for SiC MOSFET based on feedback circuits                      | 45            |

| 4.1 Conce   | ept and operating principle of the AGD                                       | 46            |

| 4.1.1       | Operating principle                                                          |               |

| 4.1.2       | Operating principle at turn-on                                               | 47            |

| 4.1.3       | Operating principle at turn-off                                              |               |

| 4.2 AGD     | design                                                                       |               |

| 4.2.1       | General consideration for the gate driver                                    |               |

| 4.2.2       | Gate driver parameters design                                                | 49            |

| 4.2.3       | Current and voltage sensors                                                  | 49            |

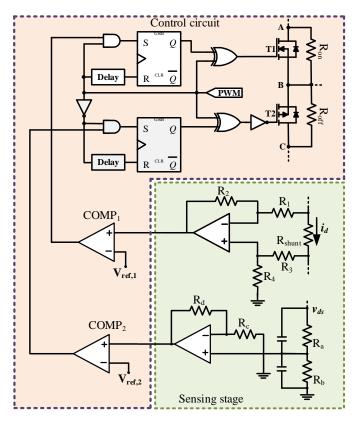

| 4.2.4       | Coupling stage and control circuit architecture                              | 50            |

| 4.3 Active  | e gate driver development and experimental validation                        | 51            |

| 4.3.1       | Time transition and voltage reference optimization                           | 53            |

| 4.3.2       | Study of the AGD under hard switching conditions                             | 54            |

| 4.3.3       | Results discussion                                                           | 57            |

| 4.1 Concl   | usions                                                                       | 57            |

| 5. Analysis | of the AGD applied on power inverter for Wireless EV charging systems ap     | pplications59 |

| 5.1 A brie  | ef analysis of Wireless EV charging systems                                  | 60            |

| 5.1.1       | Converter topologies for wireless charging systems                           | 60            |

| 5.1.2       | Power devices and technologies for WCS                                       | 61            |

| 5.1.3       | Power losses and the importance for using AGDs                               | 62            |

| 5.2 Power   | r inverter development                                                       | 62            |

| 5.3 Exper   | imental analysis of the wireless charging system by using AGD                | 63            |

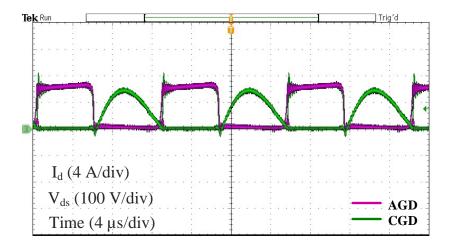

| 5.3.1       | General study of the behaviour of the system                                 | 64            |

| 5.3.2       | Power losses analysis                                                        | 66            |

| 5.4 Concl   | usions                                                                       | 67            |

| 6. Overall  | conclusions and future works                                                 | 69            |

| 6.1 Thesis  | s conclusions                                                                | 70            |

| 6.2 Future    | works                                                                | 71 |

|---------------|----------------------------------------------------------------------|----|

| 7. Thesis res | ults disseminations                                                  | 73 |

| 7.1 Derived   | l publications from this thesis work                                 | 74 |

| 7.1.1         | Journal papers                                                       | 74 |

| 7.1.2         | Conference papers                                                    | 74 |

| 7.2 Resultin  | ng publications from additional collaboration related with this work | 75 |

| 7.2.1         | Journal papers                                                       | 75 |

| 7.2.2         | Conference papers                                                    | 75 |

| References    |                                                                      | 77 |

# List of figures

| Figure 2.1. Challenges for developing power converters based on SiC devices                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

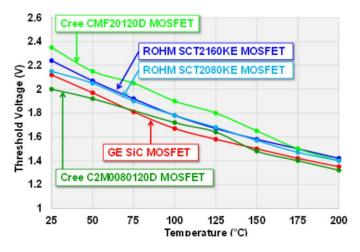

| Figure 2.2. Threshold voltage comparison by [66]       12                                                                                                    |

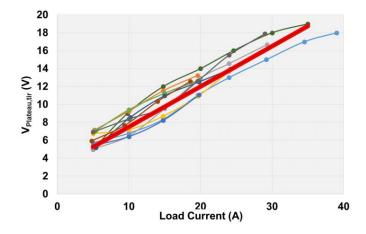

| <b>Figure 2.3.</b> Plateau voltage versus load current for different SiC MOSFETs with different gate resistances for the current rise transition [66]        |

|                                                                                                                                                              |

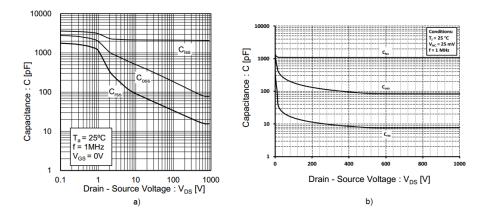

| <b>Figure 2.4.</b> Capacitance versus drain-source voltage variation. a) SiC MOSFET SCT2080KE by Rohm semiconductor and b) SiC MOSFET C2M0080120D by Cree    |

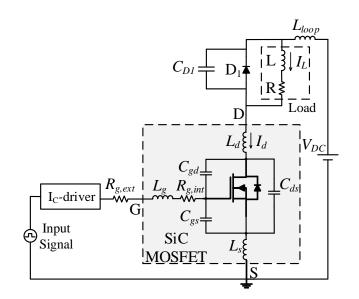

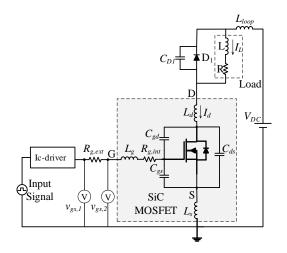

| <b>Figure 2.5.</b> Equivalent testing circuit to evaluate and represent parasitic elements                                                                   |

| representation of the SiC MOSFET in turn-on conditions                                                                                                       |

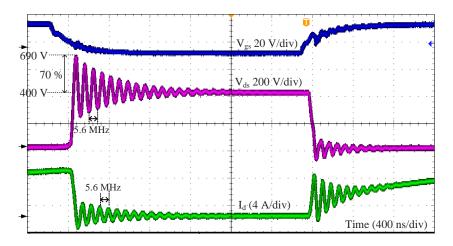

| <b>Figure 2.6.</b> Current and voltages of a discrete SiC MOSFET by ROHM semiconductors applied                                                              |

| on the power converter of Fig. 2.5 and working at 100 kHz of switching frequency, $R_g$ =6.3 $\Omega$ and                                                    |

| 400 V of DC-bus                                                                                                                                              |

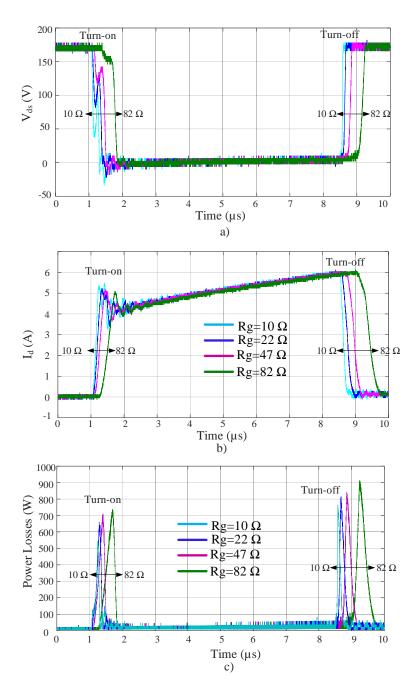

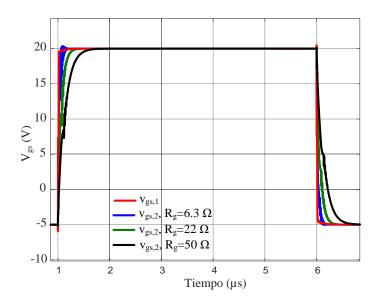

| <b>Figure 2.7.</b> Gate resistance comparison of a discrete SiC MOSFET by ROHM semiconductors                                                                |

| applied on a power converter of Fig. 2.4 at 100 kHz of switching frequency, $R_g$ =6.3 $\Omega$ and 200 V                                                    |

| of DC-bus                                                                                                                                                    |

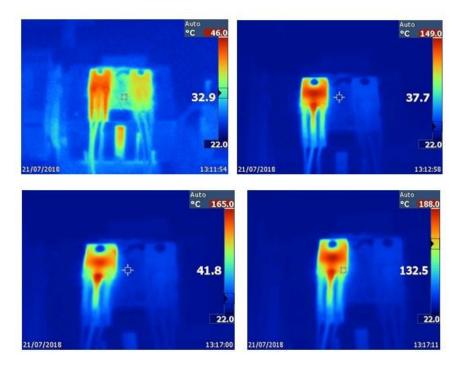

| Figure 2.8. Temperature of the SiC MOSFET when the R <sub>g</sub> increases                                                                                  |

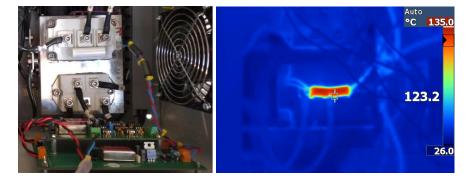

| Figure 2.9. Snubber circuit example applied to SiC MOSFET module working at 100 kHz of                                                                       |

| switching frequency and 400 V of the DC-bus. Maximum temperature measured on the snubber                                                                     |

| component was 135 °C                                                                                                                                         |

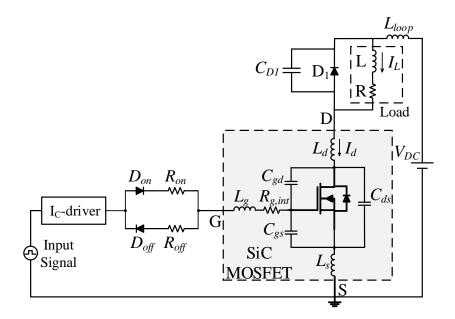

| Figure 2.10. Gate driver for SiC MOSFET with different turn-on and turn-off gate resistances. 17                                                             |

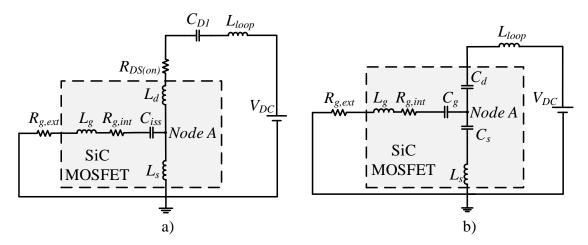

| Figure 2.11. Parasitic elements representation of the SiC MOSFET in turn-on and turn-off                                                                     |

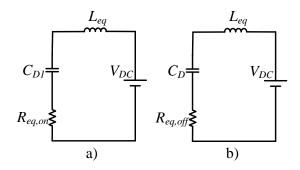

| transition conditions. a) Turn-on circuit, b) turn-off circuit                                                                                               |

| Figure 2.12. Final equivalent circuit of SiC MOSFET with parasitic elements. a) Turn-on                                                                      |

| equivalent circuit and, b) Turn-off equivalent circuit                                                                                                       |

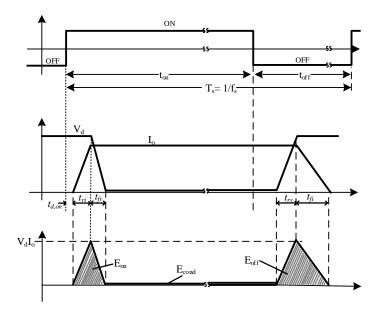

| Figure 2.13. Representation of power losses of the SiC MOSFET 19                                                                                             |

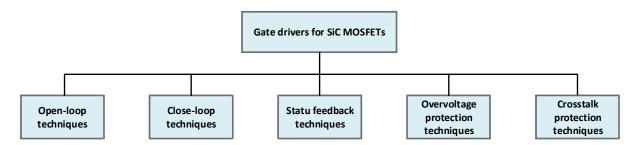

| Figure 2.14. A classification of the GD circuits for SiC MOSFET devices                                                                                      |

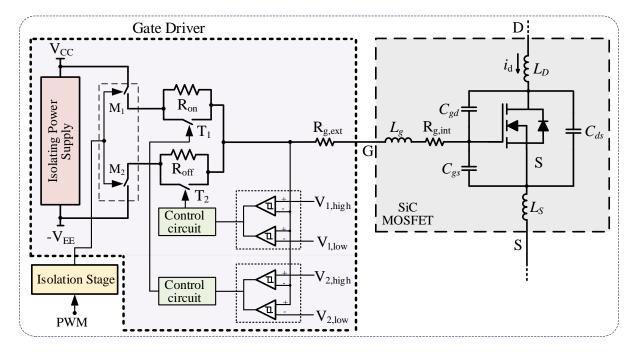

| Figure 3.1. General scheme of the proposed AGD                                                                                                               |

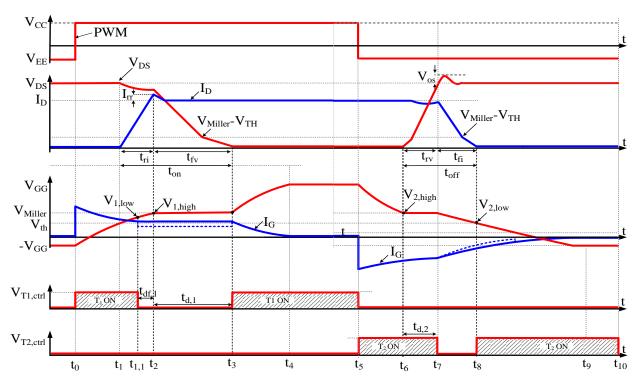

| <b>Figure 3.2.</b> Turn-on and Turn-off SiC MOSFET waveforms and control signals for $T_1$ and $T_2$ of                                                      |

| the AGD                                                                                                                                                      |

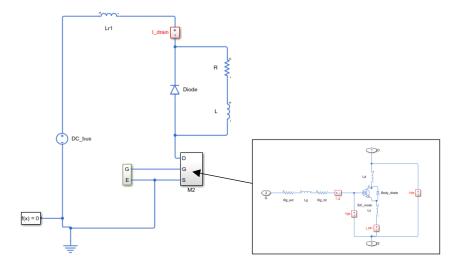

| Figure 3.3. MOSFETs models used for simulations                                                                                                              |

| Figure 3.4. Test circuit representation for measuring $v_{gs}$ voltage on both side of $R_{g\_ext}$                                                          |

| Figure 3.5. Test circuit representation for measuring $V_{gs}$ voltage on both side of $R_{g_{ext}}$                                                         |

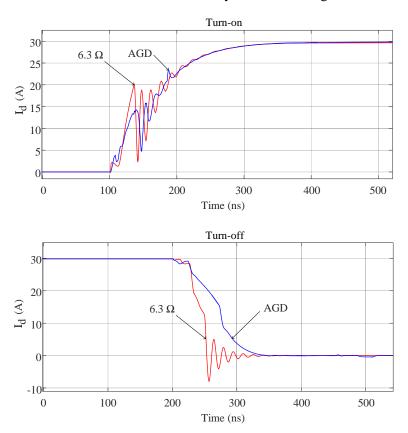

| <b>Figure 3.6.</b> Turn-on and turn-off I <sub>d</sub> with $R_g = 6.3 \Omega$ and AGD. $V_{1,high} = 15 V$ and $V_{1,low} = 10 V$ , and                     |

| $V_{2,hihg} = 10 \text{ V and } V_{2,low} = 0 \text{ V for AGD}33$                                                                                           |

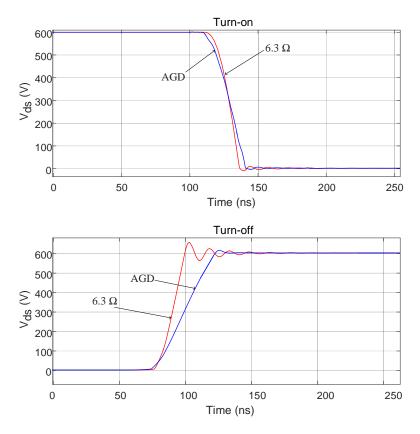

| <b>Figure 3.7.</b> Turn-on and turn-off V <sub>ds</sub> with $R_g = 6.3 \Omega$ and AGD. $V_{1,high} = 15 V$ and $V_{1,low} = 10 V$ ,                        |

| and $V_{2,high} = 10$ V and $V_{2,low} = 0$ V for AGD.                                                                                                       |

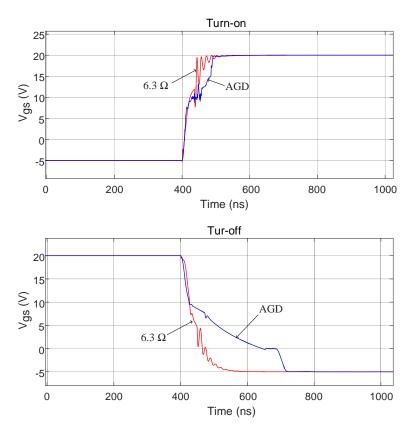

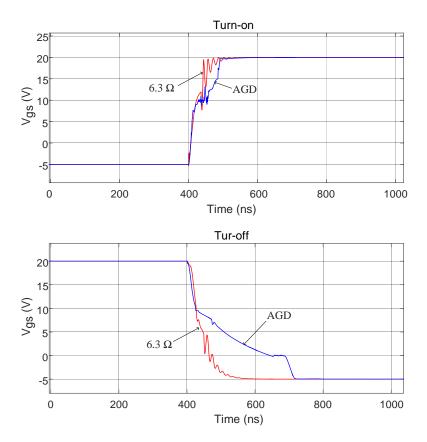

| <b>Figure 3.8.</b> Turn-on and turn-off V <sub>gs</sub> with R <sub>g</sub> = 6.3 $\Omega$ and AGD. V <sub>1,high</sub> =15 V and V <sub>1,low</sub> = 10 V, |

| and $V_{2,high} = 10$ V and $V_{2,low} = 0$ V for AGD                                                                                                        |

| <b>Figure 3.9.</b> Turn-on and Turn-off I <sub>g</sub> with $R_g = 6.3 \Omega$ and AGD. $V_{1,high} = 15 V$ and $V_{1,low} = 10 V$ , and                     |

| $V_{2,high} = 10 \text{ V}$ and $V_{2,low} = 0 \text{ V}$ for AGD                                                                                            |

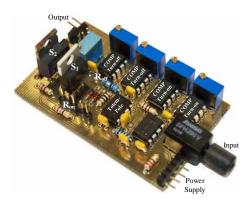

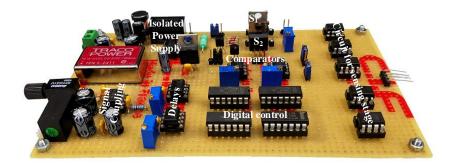

| Figure 3.10. Prototype of the open loop AGD for one device                                                                                                   |

| Figure 3.11. Prototype of the open loop AGD for one device                                                                                                   |

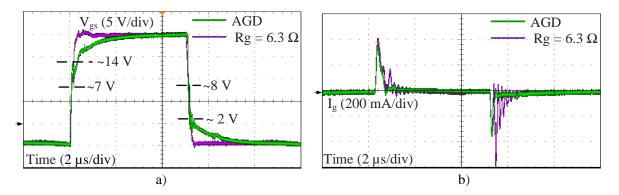

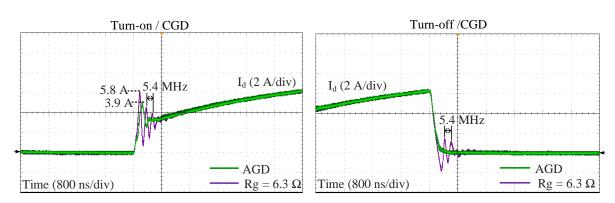

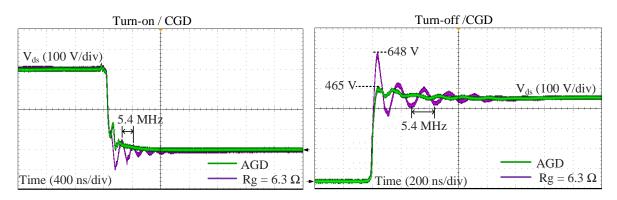

| <b>Figure 3.12.</b> Experimental results for voltage V <sub>gs</sub> transitions. R <sub>g</sub> = 6.3 $\Omega$ and AGD with V <sub>1,high</sub> V and V <sub>1,low</sub> =7 V and V <sub>2,high</sub> =8 V and V <sub>2,low</sub> = 2 V. a) voltage-source voltage, b) gate current<br><b>Figure 3.13.</b> Experimental results of I <sub>d</sub> for tur-on and turn-off transition. R <sub>g</sub> = 6.3 $\Omega$ and AGD with V <sub>1,high</sub> = 14 V and V <sub>1,low</sub> = 7 V and V <sub>2,high</sub> =8 V and V <sub>2,low</sub> = 2 V<br><b>Figure 3.14.</b> Experimental results of V <sub>ds</sub> for tur-on and turn-off transition. R <sub>g</sub> = 6.3 $\Omega$ and AGD with V <sub>1,high</sub> = 14 V and V <sub>1,low</sub> = 7 V and V <sub>2,high</sub> =8 V and V <sub>2,low</sub> = 2 V | 39<br>40<br>D |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

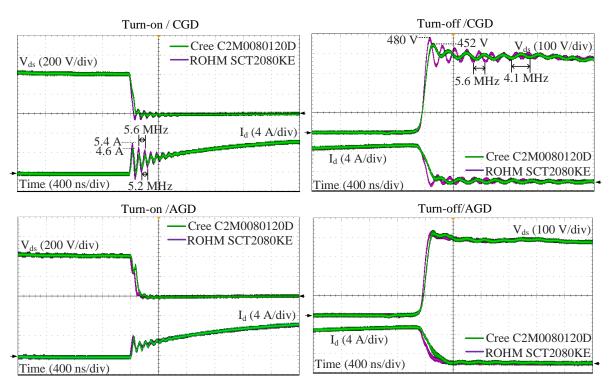

| Figure 3.15. Experimental results of $I_d$ and $V_{ds}$ for turn-on transition between two SiC MOSFETS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 41            |

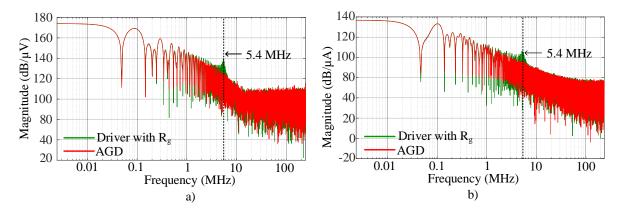

| Figure 3.16. Spectrum comparison between CGD with $R_g$ =6.3 $\Omega$ and AGD for $I_d$ and $V_{ds}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

| experimental results. a) Spectrum approximation of $V_{ds}$ and b) spectrum approximation of $I_d$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 43            |

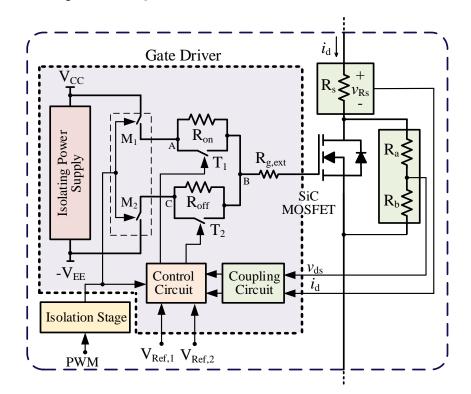

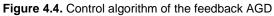

| Figure 4.1. General scheme of the proposed gate driver based on feedback circuits for one device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16            |

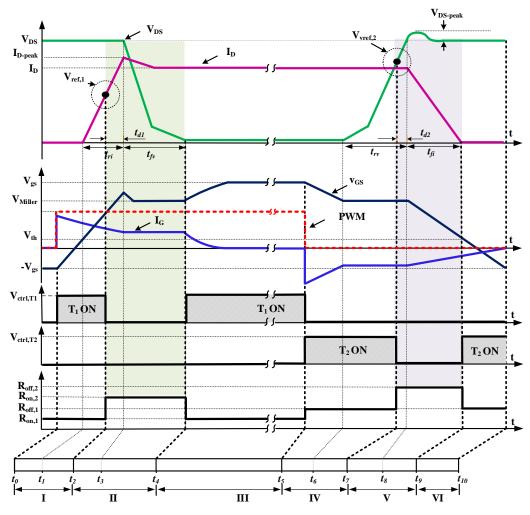

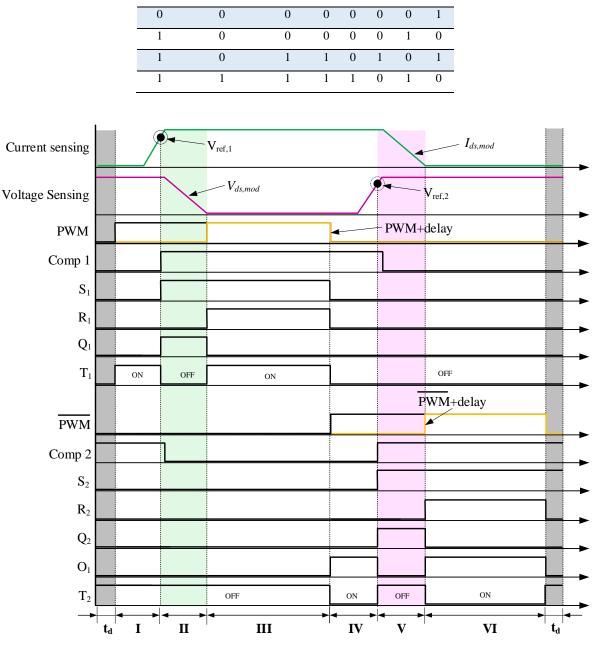

| Figure 4.2. Turn-on and turn-off SiC MOSFET waveforms and control signals for S1 of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |

| AGD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

| Figure 4.3. Circuit control of the feedback AGD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |

| Figure 4.4. Control algorithm of the feedback AGD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |

| Figure 4.5. Power converter representation to evaluate the AGD<br>Figure 4.6. Active Gate driver prototype based on feedback control for one device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |

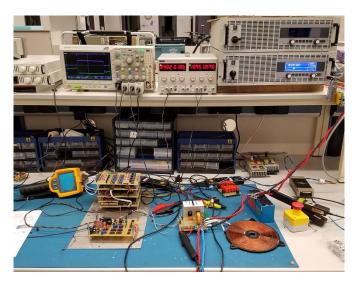

| Figure 4.7. Experimental workbench for AGD evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |

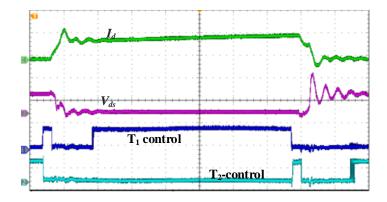

| <b>Figure 4.8.</b> Control signals of r $T_1$ and $T_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |

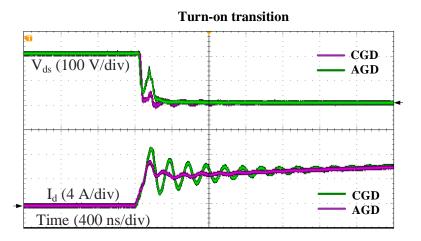

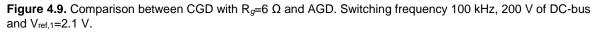

| <b>Figure 4.9.</b> Comparison between CGD with $R_q=6 \Omega$ and AGD. Switching frequency 100 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |

| 200 V of DC-bus and $V_{ref,1}$ =2.1 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |

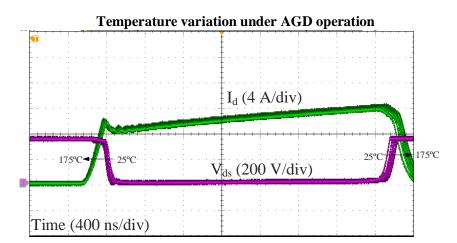

| <b>Figure 4.10.</b> Comparison between CGD with $R_g=6 \Omega$ and AGD. Switching frequency 100 kH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |

| 200 V of DC-busand V <sub>ref.2</sub> =2.5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |

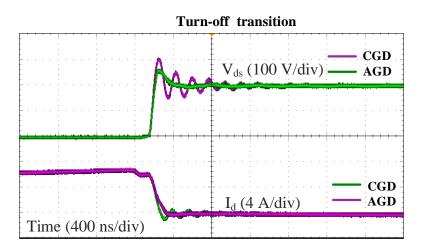

| Figure 4.11. Behavior of the current and voltage with the temperature variation applying AG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |

| 100 kHz of switching frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |

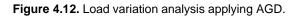

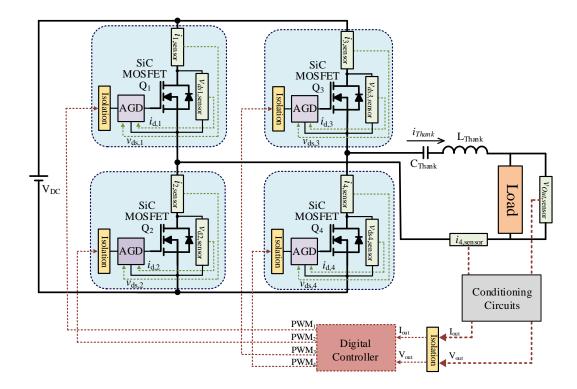

| Figure 4.12. Load variation analysis applying AGD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |

| <b>Figure 4.13.</b> Power losses comparison between CGD and proposed AGD under different loa current. Switching frequency 100 kHz, 200 V dc-bus, 27 $\Omega$ and 22 $\Omega$ for turn-on and turn-off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |

| respectively for the CGD resistances.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |

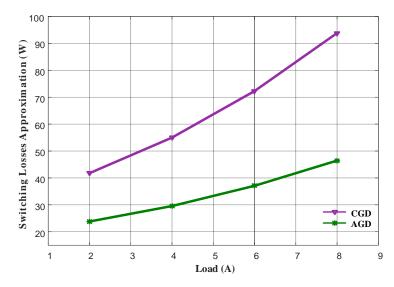

| Figure 5.1. Power electronics devices comparison applied in wireless EV charging system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |

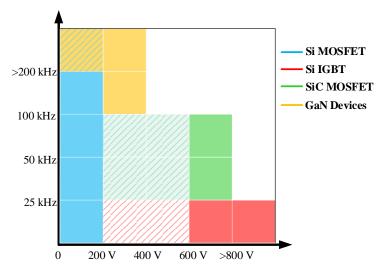

| Figure 5.2. Schematic representation of power inverter used to evaluate the AGD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

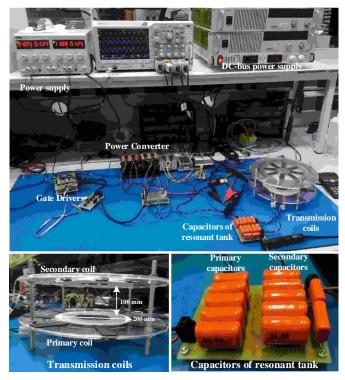

| Figure 5.3. Test bench and prototypes, only primary coil was used in this evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

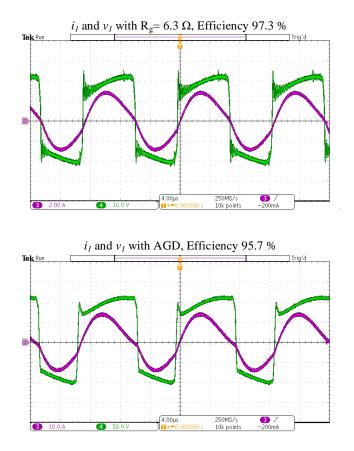

| <b>Figure 5.4.</b> Current and voltage output waveforms of the resonant inverter with $R_g$ =6.3 $\Omega$ and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |

| $R_g$ =33 $\Omega$ at 85 kHz, 200 V of DC-bus and power 2 kW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |

| <b>Figure 5.5.</b> Current and voltage output waveforms of the resonant inverter with AGD and CG with $R_{q}$ =6 $\Omega$ at 85 kHz, 200 V of DC-bus and power 2 kW. Resonant converter working for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ۶D            |

| above of the resonant frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 65          |

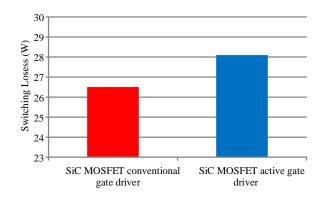

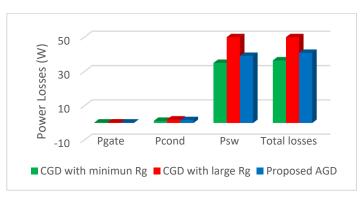

| Figure 5.6. A comparison example of power losses for one SiC MOSFETs by using AGD and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |

| conventional GD with large gate resistance of 33 $\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |

| Figure 5.7. Power losses comparison of the SiC MOSFETS between AGD and conventional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -             |

| gate driver applied in the resonant power inverter 2 kW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 66            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |

# List of tables

| Table 2.1. A comparison of power-semiconductors electrical properties [2] [17], [57], [46  | ],8 |

|--------------------------------------------------------------------------------------------|-----|

| Table 2.2. Comparison of characteristics, availability and costs of switching power device | es9 |

| Table 2.3. Comparison of the AGDs found in state-of-the-art                                |     |

| Table 2.4. Gate driver for SiC MOSFETs available in the market                             |     |

| Table 3.1. Parameters for AGD evaluation.                                                  |     |

| Table 3.2. Turn-on energy losses and current peaks                                         |     |

| Table 3.3. Turn-on energy losses and voltage overshoots.                                   | 38  |

| Table 3.4. Comparison of characteristics, availability and cost of devices for WCS         | 39  |

| Table 3.5. Numerical comparison of power losses.                                           |     |

| Table 3.6. Comparison of characteristics, availability and cost of devices for WCS         | 44  |

| Table 4.1. Logic states for turn-on                                                        | 50  |

| Table 4.2. Logic states for turn-off                                                       | 51  |

| Table 4.3. Devices and elements used for the AGD                                           | 53  |

| Table 4.4. Parameters for experimental validation of the feedback AGD                      | 53  |

| Table 5.1. Main equation for the resonant inverter used to the evaluation of the AGD       | 62  |

| Table 5.2. General parameter of the system for evaluations                                 | 64  |

# Acronyms

| AMP1Amplifier number 1AMP2Amplifier number 2BJTBipolar Junction TransistorCGDConventional Gate DriverCMCommon modeCOMP1Comparator 1COMP2Comparator 2EMIElectromagnetic InterferenceEVElectric VehicleFTTFast Fourier TransformGaNGallium NitrideGIRGate impedance regulationGVCGate voltage controlGDGate DriverHFHigh FrequencyIGBTIsolated Gate Bipolar TransistorI_C-driverIntegrated circuit - driverJFETJunction Field-Effect TransistorLVLow-voltageMOSFETMetal-oxide-semiconductor Field-effect transistorMVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap | AGD                    | Active Gate Driver                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------------|

| AMP2Amplifier number 2BJTBipolar Junction TransistorCGDConventional Gate DriverCMCommon modeCOMP1Comparator 1COMP2Comparator 2EMIElectromagnetic InterferenceEVElectric VehicleFFTFast Fourier TransformGaNGallium NitrideGIRGate impedance regulationGVCGate voltage controlGDGate DriverHFHigh FrequencyIGBTIsolated Gate Bipolar TransistorI_c-driverIntegrated circuit - driverJFETJunction Field-Effect TransistorLVLow-voltageMOSFETMetal-oxide-semiconductor Field-effect transistorMVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                       | $AMP_1$                | Amplifier number 1                                |

| BJTBipolar Junction TransistorCGDConventional Gate DriverCMCommon modeCOMP1Comparator 1COMP2Comparator 2EMIElectromagnetic InterferenceEVElectric VehicleFFTFast Fourier TransformGaNGallium NitrideGIRGate impedance regulationGVCGate voltage controlGDGate DriverHFHigh FrequencyIGBTIsolated Gate Bipolar TransistorI_c-driverIntegrated circuit - driverJFETJunction Field-Effect TransistorLVLow-voltageMOSFETMetal-oxide-semiconductor Field-effect transistorMVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                             | AMP <sub>2</sub>       |                                                   |

| CGDConventional Gate DriverCMCommon modeCOMP1Comparator 1COMP2Comparator 2EMIElectromagnetic InterferenceEVElectric VehicleFTTFast Fourier TransformGaNGallium NitrideGIRGate impedance regulationGVCGate voltage controlGDGate DriverHFHigh FrequencyIGBTIsolated Gate Bipolar TransistorIc-driverIntegrated circuit - driverJFETJunction Field-Effect TransistorLVLow-voltageMOSFETMetal-oxide-semiconductor Field-effect transistorMVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                            | BJT                    |                                                   |

| COMP1Comparator 1COMP2Comparator 2EMIElectromagnetic InterferenceEVElectric VehicleFFTFast Fourier TransformGaNGallium NitrideGIRGate impedance regulationGVCGate voltage controlGDGate DriverHFHigh FrequencyIGBTIsolated Gate Bipolar TransistorIc-driverIntegrated circuit - driverJFETJunction Field-Effect TransistorLVLow-voltageMOSFETMetal-oxide-semiconductor Field-effect transistorMVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                    | CGD                    |                                                   |

| COMP2Conprator 2EMIElectromagnetic InterferenceEVElectric VehicleFTFast Fourier TransformGaNGallium NitrideGIRGate impedance regulationGVCGate voltage controlGDGate DriverHFHigh FrequencyIGBTIsolated Gate Bipolar TransistorIc-driverIntegrated circuit - driverJFETJunction Field-Effect TransistorLVLow-voltageMOSFETMetal-oxide-semiconductor Field-effect transistorMVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                       | СМ                     | Common mode                                       |

| COMP2Comparator 2EMIElectromagnetic InterferenceEVElectric VehicleFTTFast Fourier TransformGaNGallium NitrideGIRGate impedance regulationGVCGate voltage controlGDGate DriverHFHigh FrequencyIGBTIsolated Gate Bipolar TransistorIc-driverIntegrated circuit - driverJFETJunction Field-Effect TransistorLVLow-voltageMOSFETMetal-oxide-semiconductor Field-effect transistorMVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                     | COMP <sub>1</sub>      | Comparator 1                                      |

| EMIElectromagnetic InterferenceEVElectric VehicleFTFast Fourier TransformGaNGallium NitrideGIRGate impedance regulationGVCGate voltage controlGDGate DriverHFHigh FrequencyIGBTIsolated Gate Bipolar TransistorI_c-driverIntegrated circuit - driverJFETJunction Field-Effect TransistorLVLow-voltageMOSFETMetal-oxide-semiconductor Field-effect transistorMVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                      | COMP <sub>2</sub>      |                                                   |

| FFTFast Fourier TransformGaNGallium NitrideGIRGate impedance regulationGVCGate voltage controlGDGate DriverHFHigh FrequencyIGBTIsolated Gate Bipolar TransistorIc-driverIntegrated circuit - driverJFETJunction Field-Effect TransistorLVLow-voltageMOSFETMetal-oxide-semiconductor Field-effect transistorMVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                       | EMI                    |                                                   |

| GaNGallium NitrideGIRGate impedance regulationGVCGate voltage controlGDGate DriverHFHigh FrequencyIGBTIsolated Gate Bipolar TransistorIc-driverIntegrated circuit - driverJFETJunction Field-Effect TransistorLVLow-voltageMOSFETMetal-oxide-semiconductor Field-effect transistorMVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                                                          | EV                     | Electric Vehicle                                  |

| GIRGate impedance regulationGVCGate voltage controlGDGate DriverHFHigh FrequencyIGBTIsolated Gate Bipolar TransistorI_c-driverIntegrated circuit - driverJFETJunction Field-Effect TransistorLVLow-voltageMOSFETMetal-oxide-semiconductor Field-effect transistorMVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                                                                 | FFT                    | Fast Fourier Transform                            |

| GVCGate voltage controlGDGate DriverHFHigh FrequencyIGBTIsolated Gate Bipolar TransistorI_c-driverIntegrated circuit - driverJFETJunction Field-Effect TransistorLVLow-voltageMOSFETMetal-oxide-semiconductor Field-effect transistorMVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                                                                                             | GaN                    | Gallium Nitride                                   |

| GDGate DriverHFHigh FrequencyIGBTIsolated Gate Bipolar TransistorI_c-driverIntegrated circuit - driverJFETJunction Field-Effect TransistorLVLow-voltageMOSFETMetal-oxide-semiconductor Field-effect transistorMVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                                                                                                                    | GIR                    | Gate impedance regulation                         |

| HFHigh FrequencyIGBTIsolated Gate Bipolar TransistorIc-driverIntegrated circuit - driverJFETJunction Field-Effect TransistorLVLow-voltageMOSFETMetal-oxide-semiconductor Field-effect transistorMVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                                                                                                                                            | GVC                    |                                                   |

| IGBTIsolated Gate Bipolar TransistorIc-driverIntegrated circuit - driverJFETJunction Field-Effect TransistorLVLow-voltageMOSFETMetal-oxide-semiconductor Field-effect transistorMVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                                                                                                                                                  | GD                     | Gate Driver                                       |

| Ic-driverIntegrated circuit - driverJFETJunction Field-Effect TransistorLVLow-voltageMOSFETMetal-oxide-semiconductor Field-effect transistorMVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                                                                                                                                                                                      | HF                     | High Frequency                                    |

| JFETJunction Field-Effect TransistorLVLow-voltageMOSFETMetal-oxide-semiconductor Field-effect transistorMVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                                                                                                                                                                                                                          | IGBT                   | Isolated Gate Bipolar Transistor                  |

| LVLow-voltageMOSFETMetal-oxide-semiconductor Field-effect transistorMVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                                                                                                                                                                                                                                                              | I <sub>C</sub> -driver | Integrated circuit - driver                       |

| MOSFETMetal-oxide-semiconductor Field-effect transistorMVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                                                                                                                                                                                                                                                                           | JFET                   | Junction Field-Effect Transistor                  |

| MVMedium-voltagePCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LV                     | Low-voltage                                       |

| PCBPrinted Circuit BoardPHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MOSFET                 | Metal-oxide-semiconductor Field-effect transistor |

| PHEVPlug-in Hybrid Electric VehiclePWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MV                     | Medium-voltage                                    |

| PWMPulse-Width ModulationSAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PCB                    | Printed Circuit Board                             |

| SAESociety of Automotive EngineersSiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PHEV                   | Plug-in Hybrid Electric Vehicle                   |

| SiSiliconSiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PWM                    | Pulse-Width Modulation                            |

| SiCSilicon CarbideSOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SAE                    | Society of Automotive Engineers                   |

| SOASafe Operation AreaUVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Si                     | Silicon                                           |

| UVLOUnder voltageWBGWide-Bandgap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SiC                    | Silicon Carbide                                   |

| WBG Wide-Bandgap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SOA                    | Safe Operation Area                               |

| 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | UVLO                   | Under voltage                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | WBG                    |                                                   |

| C C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ZCS                    | Zero Current Switching                            |

| <b>ZVS</b> Zero Voltage Switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ZVS                    | Zero Voltage Switching                            |

# Nomenclature

| C <sub>D1</sub>                | Equivalent capacitance of the model SiC circuit              | pF  |

|--------------------------------|--------------------------------------------------------------|-----|

| Ciss                           | Small-signal input capacitance                               | pF  |

| Coss                           | Small-signal output capacitance                              | pF  |

| Crss                           | Small-signal reverse transfer capacitance                    | pF  |

| di/dt                          | Current slope                                                | A/s |

| dv/dt                          | Voltage slope                                                | V/s |

| $\mathbf{g}_{fs}$              | Transconductance                                             | S   |

| Id                             | Drain current                                                | А   |

| I <sub>d,mod</sub>             | Modified drain current                                       | А   |

| I <sub>d,peak</sub>            | Peak drain current                                           | А   |

| L                              | Inductance load                                              | μH  |