# DESIGN OF AN AXI-SDRAM INTERFACE IP IN A RISC-V PROCESSOR

A Master's Thesis Submitted to the Faculty of the Escola Tècnica d'Enginyeria de Telecomunicació de Barcelona Universitat Politècnica de Catalunya by Joan Marimon Illana

> In partial fulfilment of the requirements for the degree of MASTER IN ELECTRONIC ENGINEERING

> > **Advisor: Francesc Moll Echeto**

Barcelona, May 2020

# Abstract

PreDRAC is a RISC-V based SoC developed with the collaboration of the BSC, CIC-IPN, IMB-CNM (CSIC) and UPC. On its first version, sent to fabricate on May 2019, it used a custom interface to access main memory through an FPGA. Access to memory is critical to the performance of a processor and a AXI-SDRAM interface IP to be integrated into a future revision of the chip has been designed.

No specific area, power or performance constraints are defined for AXI-SDRAM interface as the first step is to obtain a functional design with the required verification setup to ensure its proper operation once fabricated on silicon. The design of the IP covers different aspects in the ASIC design flow: the initial RTL implementation, synthesis, verification at RTL and gate-level simulations and a final power analysis. Final results show that this IP can successfully be integrated with the preDRAC SoC, replacing the custom interface, and obtaining better performance. However, the AXI-SDRAM interface IP can be further improved both in terms of performance and power.

# Acknowledgements

I would like to express my gratitude to my master thesis advisor Francesc Moll for his support and to give me the opportunity to participate in this project.

I would like to make my gratiture extensive to all people from BSC, CNM and UPC who collaborated in the preDRAC tapeout with who I had the pleasure to work with.

Last but not least, I want to thank my family who have supported and motivated me the whole time.

# Contents

| Li | st of | Figures | S                   | 5    |

|----|-------|---------|---------------------|------|

| Li | st of | Tables  |                     | 7    |

| 1  | Intro | oductio | on                  | 8    |

|    | 1.1   | Motiva  | ation               | . 8  |

|    | 1.2   | Projec  | t organization      | . 9  |

| 2  | Bac   | kgroun  | nd                  | 10   |

|    | 2.1   | RISC-   | ν                   | . 10 |

|    |       | 2.1.1   | PreDRAC processor   | . 10 |

|    | 2.2   | Memo    | pry                 | . 12 |

|    |       | 2.2.1   | Memory hierarchy    | . 12 |

|    |       | 2.2.2   | DRAM                | . 13 |

|    |       | 2.2.3   | SDR SDRAM           | . 15 |

|    | 2.3   | AMBA    | Α ΑΧΙ               | . 20 |

|    |       | 2.3.1   | Signals description | . 20 |

|    |       | 2.3.2   | AXI architecture    | . 23 |

|    |       | 2.3.3   | Operation           | . 24 |

|    | 2.4   | ASIC    | design flow         | . 26 |

|    |       | 2.4.1   | Synthesis           | . 26 |

|    |       | 2.4.2   | Place&Route         | . 27 |

|    |       | 2.4.3   | Verification        | . 27 |

|    |       | 2.4.4   | Power analysis      | . 30 |

| 3  | Met   | hodolo  | ρgγ                 | 33   |

|    | 3.1   | Impler  | mentation           | . 33 |

|    |       | 3.1.1   | SDRAM controller    | . 34 |

|    |       | 3.1.2   | AXI interface       | . 41 |

| Bi | Bibliography 66                  |         |                           |    |  |  |  |

|----|----------------------------------|---------|---------------------------|----|--|--|--|

| 5  | 5 Conclusions and future work 64 |         |                           |    |  |  |  |

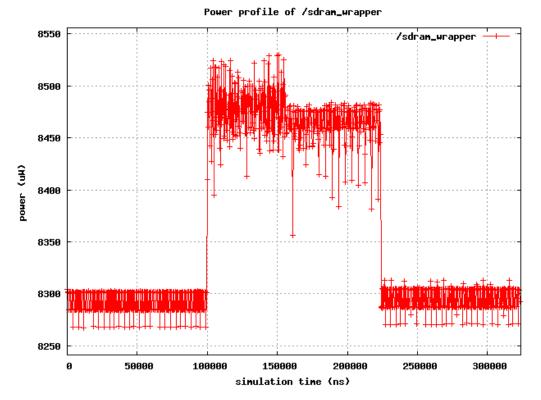

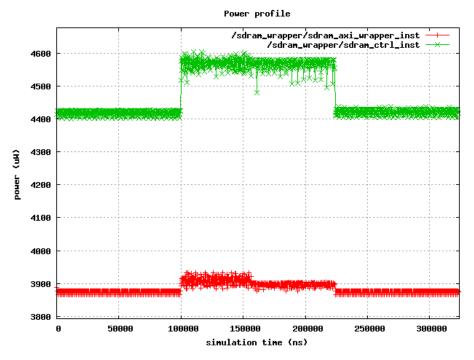

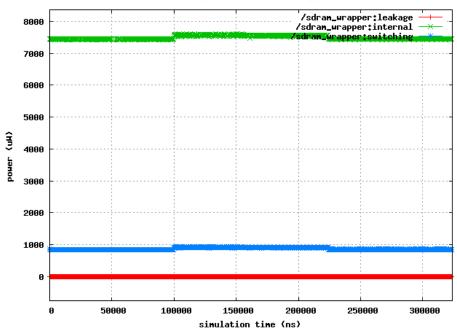

|    | 4.3                              | Power   | analysis                  | 62 |  |  |  |

|    | 4.2                              | Synthe  | esis                      | 62 |  |  |  |

|    | 4.1                              | Simula  | ation                     | 61 |  |  |  |

| 4  | Res                              | ults    |                           | 61 |  |  |  |

|    |                                  | 3.4.2   | Joules power analysis     | 57 |  |  |  |

|    |                                  | 3.4.1   | Extracting activity data  | 56 |  |  |  |

|    | 3.4                              | Power   | analysis                  | 56 |  |  |  |

|    | 3.3                              | Synthe  | esis                      | 55 |  |  |  |

|    |                                  | 3.2.3   | Gate-level simulation     | 53 |  |  |  |

|    |                                  | 3.2.2   | FPGA implementation       | 52 |  |  |  |

|    |                                  | 3.2.1   | Behavioral RTL simulation | 46 |  |  |  |

|    | 3.2                              | Verific | ation                     | 45 |  |  |  |

|    |                                  | 3.1.3   | Synchronization           | 45 |  |  |  |

# **List of Figures**

| 2.1  | PreDRAC processor block diagram.                                                                    | 11 |

|------|-----------------------------------------------------------------------------------------------------|----|

| 2.2  | Schematic of a 1T1C memory cell                                                                     | 13 |

| 2.3  | Functional block diagram of a SDR SDRAM.                                                            | 14 |

| 2.4  | Timing diagram of a write operation in a SDRAM                                                      | 18 |

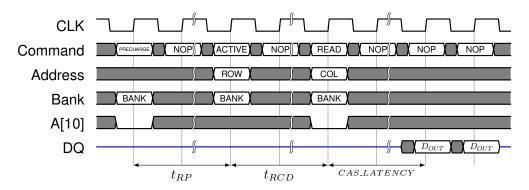

| 2.5  | Timing diagram of a read operation in a SDRAM                                                       | 19 |

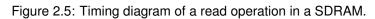

| 2.6  | Timing diagram of an AXI write transaction.                                                         | 25 |

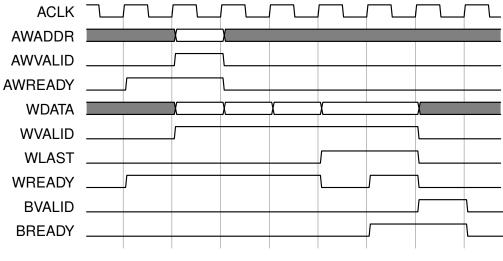

| 2.7  | Timing diagram of an AXI read transaction.                                                          | 25 |

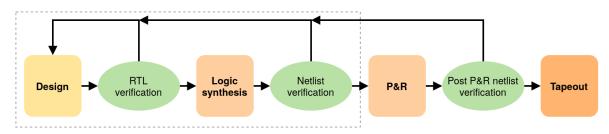

| 2.8  | Different steps in the ASIC design flow                                                             | 26 |

| 3.1  | Organization of the design modules.                                                                 | 33 |

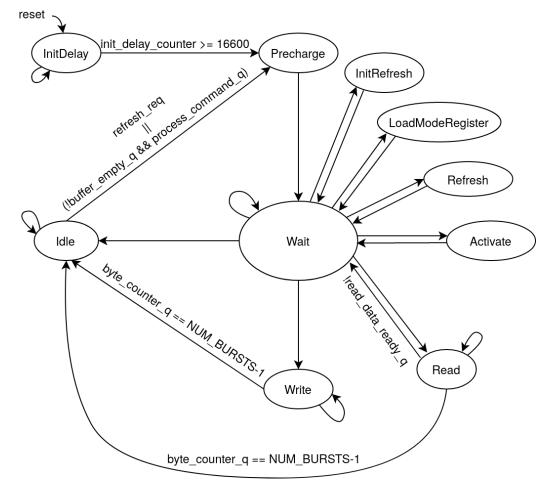

| 3.2  | Diragram of the FSM in the SDRAM controller.                                                        | 37 |

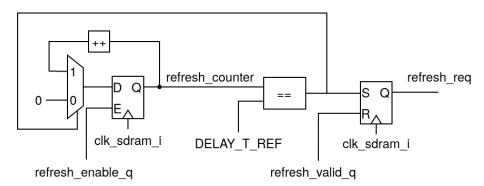

| 3.3  | Schematic of the refresh control logic in the SDRAM controller                                      | 38 |

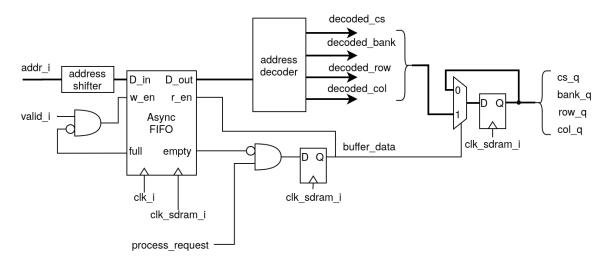

| 3.4  | Schematic of the address processing logic in the SDRAM controller                                   | 39 |

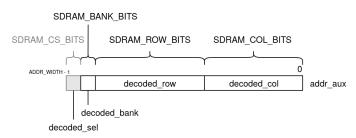

| 3.5  | Address decoding in the SDRAM controller                                                            | 39 |

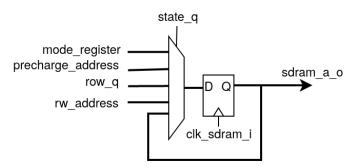

| 3.6  | Schematic of the output address logic the SDRAM controller                                          | 39 |

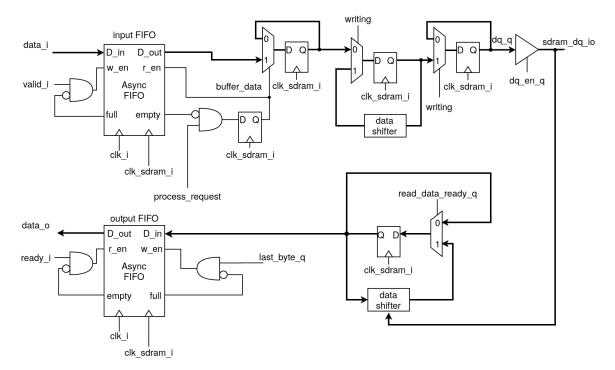

| 3.7  | Data reading and writting control logic in SDRAM controller                                         | 40 |

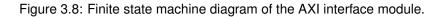

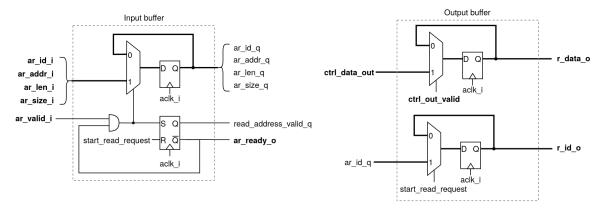

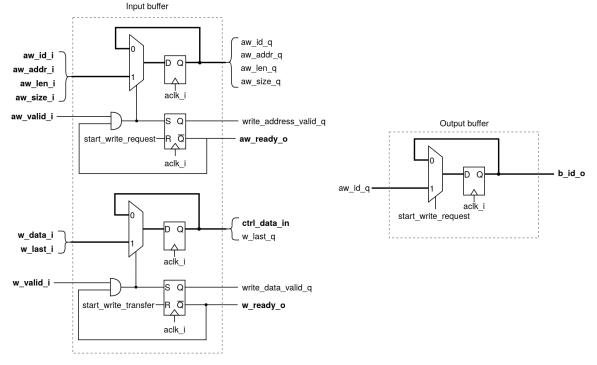

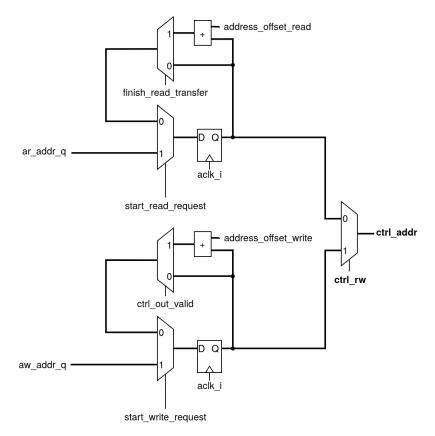

| 3.8  | Finite state machine diagram of the AXI interface module                                            | 42 |

| 3.9  | Schematic of input and output registers for a read operation in the AXI interface.                  | 43 |

| 3.10 | Schematic of input and output registers for a write operation in the AXI interface.                 | 44 |

| 3.11 | Schematic of address generation logic in the AXI interface                                          | 44 |

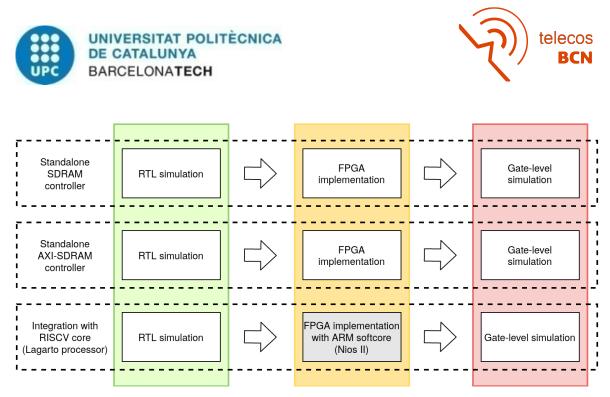

| 3.12 | Stages of the verification flow.                                                                    | 46 |

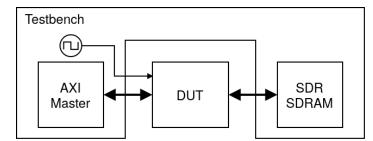

| 3.13 | Testbench compnents in the AXI-SDRAM controller verification                                        | 48 |

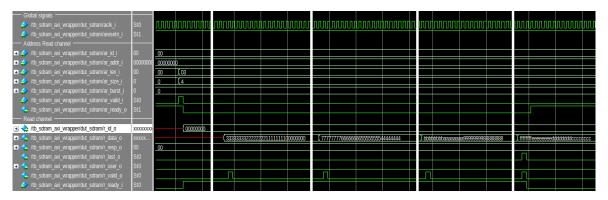

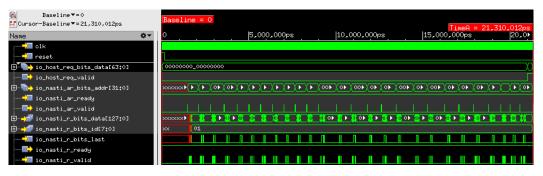

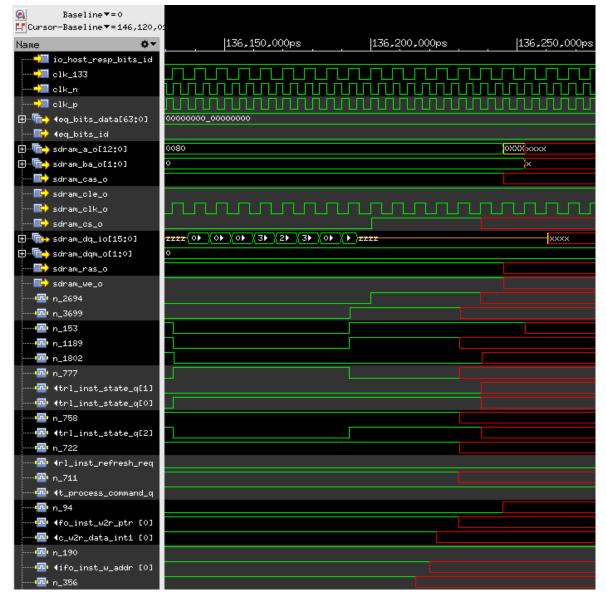

| 3.14 | Capture of an AXI read transaction obtained by simulation.                                          | 48 |

| 3.15 | Capture of an AXI write transaction obtained by simulation                                          | 49 |

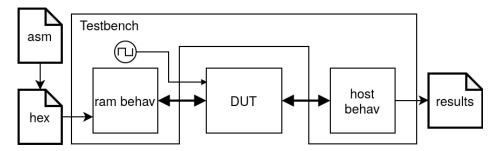

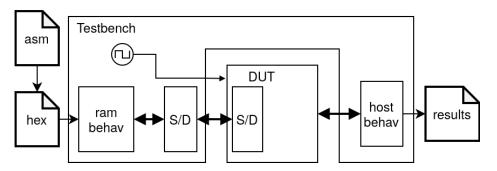

| 3.16 | Initial testbench setup used to verify the preDRAC SoC                                              | 49 |

| 3.17 | Final testbench setup used to verify the preDRAC SoC.                                               | 50 |

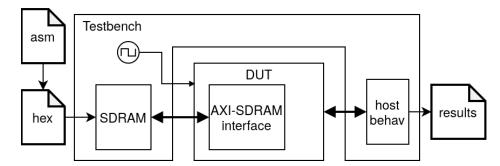

| 3.18 | Testbench setup used to verify the intergration of the AXI-SDRAM interface IP with the preDRAC SoC. | 51 |

| . 51      |

|-----------|

| t<br>. 52 |

| e<br>. 52 |

| ı         |

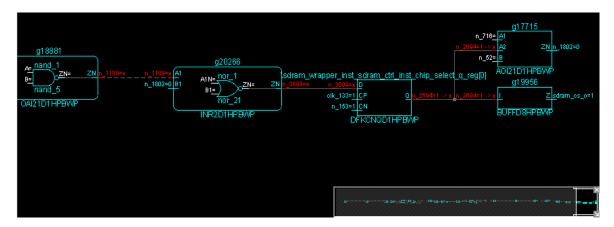

| . 54      |

| . 55      |

| . 58      |

| . 59      |

| . 60      |

| . 60      |

|           |

# **List of Tables**

| 2.1 | SDR SDRAM interface signals                               | 15 |

|-----|-----------------------------------------------------------|----|

| 2.2 | SDRAM commands summary.                                   | 16 |

| 2.3 | Summary of SDRAM timing parameters                        | 19 |

| 2.4 | AXI global signals.                                       | 20 |

| 2.5 | AXI Address Write channel signals                         | 21 |

| 2.6 | AXI Write Data channel signals                            | 21 |

| 2.7 | AXI Response channel signals                              | 22 |

| 2.8 | AXI Read Address channel signals.                         | 22 |

| 2.9 | AXI Read channel signals                                  | 23 |

| 3.1 | SDRAM controller interface.                               | 35 |

| 3.2 | Parameters of the SDRAM controller                        | 36 |

| 3.3 | Configurable parameters of the AXI interface              | 41 |

| 3.4 | Parameters of the SDRAM controller for the DE0-Nano board | 53 |

| 3.5 | Summary of standard cell corner conditions.               | 56 |

| 3.6 | Annotation report generated by Joules.                    | 59 |

| 4.1 | Measured throughput of the SDRAM controller.              | 61 |

| 4.2 | Average simulation time of all the ISA-tests.             | 61 |

| 4.3 | Summary of the area report obtained by Genus.             | 62 |

| 4.4 | Summary of the gates area report obtained by Genus.       | 62 |

| 4.5 | Power report results.                                     | 63 |

## **Chapter 1**

## Introduction

In May 2019, a RISC-V based processor, the preDRAC, was sent to tapeout [1]. PreDRAC is the first RISC-V processor from a Spanish academic institution. It was developed with the collaboration of Barcelona Supercomputing Center (BSC), Centro de Investigación en Computación del Instituto Politécnico Nacional de México (CIC-IPN), Institut de Microelectrònica de Barcelona (IMB-CNM(CSIC)) and Universitat Politècnica de Catalunya (UPC). This was a first step in the development of the DRAC project (Designing RISC-V based Accelerators for the next generation Computers).

The preDRAC includes a single RISC-V core as well as different levels of cache hierarchy and additional peripherals such as UART, JTAG, or an SD card controller. During initial tests, the preDRAC was implemented on an FPGA board, the Xilink Kintex KC705, and used the on-board DDR3 memory as the main memory. Memory was connected to the core through an AXI bus.

Memories such as DDR, DDR2, DDR3, and above work at high frequencies (>200 MHz). At these frequencies, wires can not be considered ideal and some conditioning is needed to ensure data is transmitted correctly. A physical interface with the right pin terminations is needed to ensure such conditioning. This physical interface was not available so it was not possible to include the main memory interface within the chip.

The solution in the preDRAC was making the AXI interface available outside the chip. From there, connect it to the FPGA to access the KC705 on-board DDR3 memory. Since the AXI interface had too many signals and there were not enough available pins, a custom interface was designed to split the AXI signals into multiple packets and send them to the FPGA. Then, inside the FPGA, reconstruct the original AXI request and send it to memory.

## 1.1 Motivation

Access to the main memory has a significant impact on the performance of a processor. The current setup, while it is functional, has several limitations in terms of performance. For the next chip, the custom interface will be replaced with an SDR SDRAM controller that will be integrated into the chip. Then, the main memory will be an SDR SDRAM placed on the same board as the chip and and the auxiliary FPGA board will not be required anymore.

SDR SDRAM work at lower frequencies than DDR, typically the maximum frequency ranges from 100 MHz to 166 MHz depending on the memory chip, with some recent models

reaching up to 200 MHz. In this case, it does not require a specific memory interface as it uses standard CMOS digital output buffers.

The purpose of this project is to design and implement an AXI-SDRAM interface IP that will be used in a future DRAC chip. The main goal is to obtain a functional design and provide the setup required for the verification to ensure everything will work once built on silicon. The project involves different steps in the ASIC design flow, starting from the design of the RTL itself, the synthesis, and verifications both at an initial RTL level and after synthesis. Additionally, even if power consumption is not a major concern for this particular project, a power analysis is included since it should be taken into consideration as part of the verification process.

## 1.2 Project organization

This work is divided into several parts. Chapter 2 gives an overview of the relevant concepts involved in this project. First, section 2.1 gives a brief introduction to RISC-V that is followed with a description of the preDRAC chip. Section 2.2 starts with the basics of memory organization. Then, the main operation of an SDRAM is described to have a better understanding of which are the tasks that should be performed by a memory controller. After that, section 2.3 gives an introduction to the AXI protocol. Finally, chapter 2 ends with an overview of the different steps involved in the ASIC design required to go from an initial RTL to the final layout that can be tapeout.

Chapter 3 contains the actual implementation of the design. It starts with a description of the main blocks in the design and how they work. Then, section 3.2 explains the methodology used for the verification of the design, and section 3.4 describes the steps that have been done to perform a power estimation of the design.

Results are presented in chapter 4, which include the area and power results obtained after synthesis and power analysis as well as some performance evaluation.

Finally, the project concludes with chapter 5, which includes some conclusions and an overview of the future work to be done.

## **Chapter 2**

# Background

## 2.1 RISC-V

RISC-V is an instruction set architecture (ISA) created in 2010 at UC Berkeley [2], initially designed to support research and educational projects. It is defined as a base integer ISA with two main variants of 32 and 64 bits. Moreover, RISC-V is designed so the base ISA can be extended to provide support for additional instructions.

The main interest behind RISC-V is that it defines an open and free ISA standard, available for both academia and industry. Anyone can develop their hardware that supports this common standard to run the software that was ported or developed for it.

Many RISC-V based processors have been fabricated both in academic and industrial environments. A special focus will be put on the preDRAC processor.

### 2.1.1 PreDRAC processor

The preDRAC is a 64-bit single-core in-order processor that implements the 64-bit RV64IMA scalar RISC-V ISA. It is the first RISC-V based processor from an spanish academic institution developed in 2019 with the collaboration of the BSC, CIC-IPN, IMB-CNM and UPC. It is based on the 0.2 version of the lowRISC chip [3].

lowRISC is a non-profit organization with the goal to produce a fully open source SoC. The lowRISC chip is a SoC built on top of the Rocket Chip and adds support for additional peripherals in order to make a fully functional SoC that can be implemented on a FPGA and is able to boot Linux. Moreover, the lowRISC chip also provides the required setup to verify the basic functionality of the SoC with different simulation tools.

The Rocket Chip is built with the Rocket Chip generator, a tool developed by UC Berkeley to generate custom SoC based on RISC-V cores [4]. The generator has a collection of libraries that can be used to generate SoCs with different paramaters, for instance different number of cores or cache sizes.

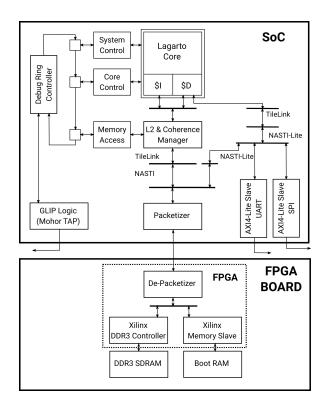

Then the preDRAC makes use of the lowRISC infrastructure but replaces the Rocket core with the Lagarto core, which is a custom core based on the RISC-V ISA. The main blocks of the design are shown in figure 2.1. The design is split into two parts: the preDRAC chip itself (SoC), and an auxiliary FPGA board.

Figure 2.1: PreDRAC processor block diagram.

The SoC contains the Lagarto core, two L1 caches of 16 KB, one for instructions and the other for data, and a single L2 cache of 64 KB, additional logic for debugging and peripherals to connect the processor with external devices like JTAG, UART or SPI.

Due to the lack of a physical interface, it was not possible to integrate a memory controller into the SoC. The memory controller was implemented in an external FPGA board, the Xilinx Kintex KC705, which had an on-board DDR3 memory that was used as the main memory of the preDRAC.

An AXI bus is used to interconnect the memory controller and the core. Due to the limited amount of I/O pins, it was not possible to make the whole AXI interface available at chip level. To solve that, and a custom interface, the packetizer, was used to send the AXI requests from the core to the memory controller in the FPGA. What is done inside the packetizer, is to serialize the AXI interface so a single AXI transfer is split into multiple transfers with less width. The FPGA board was connected to the main board, the one containing the preDRAC SoC, with an FMC connector.

This setup has some drawbacks. For one side, the FMC connector only supports signals up to 50 MHz. This made the clock speed of the transfers to be reduced from 200 MHz to 50 MHz. Moreover, since the AXI transfers were split in 4, it takes 4 times more to send each transfer.

The main performance bottleneck is the access to main memory due to the lack of a memory controller. To improve the performance of the system, a memory controller will be designed to provide an on-chip memory interface.

## 2.2 Memory

Memory is an essential part of any data processing system since it is where instructions and data are stored. Access to memory has an significant impact and limits the performance of the system.

This section provides an overview of how memory is organized in a processing system and why a memory controller is required. Then the principle of operation of DRAM (Dynamic Random Access Memory) is reviewed in order to get a better understanding of which are the tasks that should be performed by the controller.

After the DRAM overview, special focus will be put on SDRAM (Synchronous Dynamic Random Access Memory), in particular the SDR (Single Data Rate) SDRAM, which is the target of this project.

### 2.2.1 Memory hierarchy

As applications become more complex larger amounts of data need to be processed. To use more memory while keeping low the time required to access it processors are organized in multiple levels of memory hierarchy [5]: smaller but faster memories are placed close to the processor while larger but slower ones go to subsequent levels. While it is not the scope of this work to analyze the memory hierarchy, a brief overview is done to provide some context and have a better understanding of the final purpose of this project.

The main memory, where the program data and instructions are stored, is external to the processor since it is too big to be integrated on-chip. Inside the processor, a smaller memory, the cache memory, is used to buffer the data from the main memory so it can be accessed faster by the processor. Both the main and cache memories are volatile, which means they lose the data when they are powered off. Usually, there is a secondary nonvolatile memory in a more external level of the hierarchy that keeps the data even if powered off.

Different technologies are used to implement the memories in the different levels of the memory hierarchy. Secondary memories are made of non-volatile flash memories, or magnet disks when larger and cheaper storage is required. Higher levels in the hierarchy are implemented with volatile memories: the main memory is implemented with DRAM and the caches with SRAM (Static Random Access Memory).

SRAMs typically use six transistors to store each bit of data. They are made with standard CMOS technology, can be placed on the same silicon as the processor, and have faster access time compared to the other types of memories. This is why SRAMs are used to implement cache memories. On the other hand, DRAMs only require a single transistor plus an additional capacitor to store each bit of data, so they have higher memory density, but also higher latency. The higher density makes DRAM large enough to be used as main memory and store the program data. DRAMs are fabricated with a different process than standard CMOS and are typically used in an external chip.

A processor has to access the different layers of memory. It has direct access to the cache, which is made of SRAMs on the same silicon, but it does not has direct access to the main memory, which is typically made of DRAM and external to the chip.

A memory controller that acts as an interface between the processor and the main memory is needed. The controller has to manage the memory requests from the processor and

read or write data to the external DRAM while also control the refreshing of the DRAM to ensure data is not lost.

### 2.2.2 DRAM

As previously mentioned, DRAM is a volatile memory that use capactitors as storage elements [6]. Since capacitors are not ideal, the charge is progressively lost due to leakage currents. To prevent the loss of information, DRAM needs to be periodically refreshed. This is the reason why they are called dynamic.

In a reliable memory, not a single bit of data should be lost. Every single DRAM cell must be refreshed before it loses its stored charge. In a DRAM, all cells are typically refreshed every 32 or 64 ms.

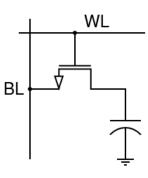

Figure 2.2 shows the basic structure of a DRAM cell, which is composed of one transistor and one capacitor (1T1C) and can store 1 bit of data.

Figure 2.2: Schematic of a 1T1C memory cell.

#### Principle of operation

The main operation of a DRAM is based on the 1T1C cell previously mentioned. First, to understand how DRAM works, the operation of the basic storage cell will be reviewed. As seen before, the structure of a basic DRAM memory cell is composed of one transistor and one capacitor. The capacitor is the storage element while the transistor is used to control the access to the data.

The gate of the transistor is connected to the word-line. The word-line enables or disables the access to data. When the word-line is enabled, the gate of the transistor is activated and the storage capacitor is connected to the bit-line so it can be accessed for reading or writing. Otherwise, if the word-line is disabled, the transistor is off and the capacitor is disconnected from the bitline, keeping its current value.

To write data into the capacitor then the bit-line must drive the value to be written. Then, when the word-line is enabled, the capacitor will be charged or discharged to the voltage of the bit-line. On the other hand, to read data from the capacitor the bit-line should be floating, that way when the word-line is enabled the bit-line will be charged with the curent value of the capacitor.

Since the capacitor is not ideal, the charge stored in the capacitor will eventually leak and it will be discharged even if it is not accessed. This means the value of the capacitor must be constantly read and written in order to keep the data. Additionally, in this kind of cell, the reading is destructive, which means that reading a stored value implies discharging the capacitor so, after a read, the value must be written again to not lose the data.

#### Internal Architecture

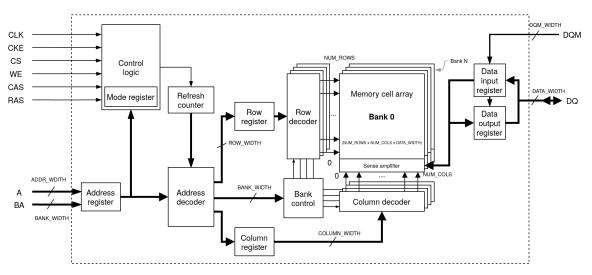

Figure 2.3: Functional block diagram of a SDR SDRAM.

Internally, DRAM is organized in memory arrays where each cell can be accessed by its row and column. DRAM does not operate with single bits, actually multiple memory arrays are put together and operate as a single unit, typically with word sizes of 4, 8, 16 or even 32 bits in modern memories. This defines the width of the data bus in the DRAM chips which is denoted as x4, x8, x16 or x32.

Additionally, memory arrays are grouped into banks. Each bank acts as an independent unit and it can be activated, precharged, read, or written while other operations are performed on other banks. There are some limitations, for example since the output data bus is shared for all banks, it is not possible to simultaneously read from two different banks at the same time.

Conventional DRAMs are asynchronous while SDR SDRAMs have a synchronous interface and all operations are controlled by a reference clock. Internally, the basic structure of a DRAM and a SDR SDRAM is the same. The main difference is that SDR SDRAMs add input and output registers and the control logic is different. Figure 2.3 shows the diagram of the main blocks in a SDR SDRAM chip. There is a control logic that decodes the input signals to determine which operation should be performed. Similarly, the input address is decoded to obtain the row, column, and bank to be accessed. Each bank has its own sense amplifier that is connected to the output data bus.

Sense amplifiers are used to detect the value stored in the capacitors [7]. The operation is performed as follow. First, bit-lines are initially precharged at VDD/2. Then, the storage capacitors are connected to the bitline through the access transistor and the capacitors charge or discharge the bit-lines producing a small variation on its voltage. The sense amplifier compares the voltage of the bit-line with a reference and the small differences are amplified to full VDD or GND.

The process to read from the DRAM requires to first precharge the bit-lines, read the values and then rewrite them since the read is destructive.

### 2.2.3 SDR SDRAM

After the overview of DRAM in the previous section, this section will give a a more specific review of the timing requirements and relevant commands involved in the operation of a DRAM. In this case, the focus will be specifically the SDR SDRAM. Table 2.1 shows the different signals in a SDR SDRAM chip.

| Name | Width        | Туре  | Description                                                                                                                                    |

|------|--------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK  | 1            | Input | Reference clock. All SDRAM input signals are sampled at the positive edge of the clock.                                                        |

| CKE  | 1            | Input | Clock enable, active high. When low, disables the CLK signal. It is used to control the low power operation modes of the SDRAM.                |

| CS   | 1            | Input | Chip select, active low. Enables or disables the command decoder.                                                                              |

| WE   | 1            | Input | Write enable. Command bit in the SDRAM, in a DRAM it was used to indicate the type of operation (read or write).                               |

| CAS  | 1            | Input | Column Address Strobe. Command bit in the SDRAM, in<br>a DRAM it was used to indicate the address was a valid<br>column address.               |

| RAS  | 1            | Input | Row column strobe. Command bit in the SDRAM, in DRAM it was used to indicate the address was a valid row address.                              |

| A    | <u>≥</u> 11  | Input | Address bits. Width depends on the size of the SDRAM, at least it has 11 bits. The 11th bit is used to control the operation of some commands. |

| BA   | 1, 2, 3      | Input | Bank selection bits. Width depends on the number of banks in the SDRAM. SDRAMs can have 2, 4 or 8 banks.                                       |

| DQ   | 4, 8, 16, 32 | Inout | Bidirectional data bus, it can have 4, 8, 16 or 32 bits.                                                                                       |

| DQM  | 1, 2, 4      | Input | Data mask. There is one mask bit for each byte in the data bus.                                                                                |

SDRAM modules are provided with different configurations of capacity, element size and maximum frequency [8] [9].

Internally the modules are configured as quad-bank DRAM with a synchronous interface: the accesses are synchronous to the reference clock and the data is registered at the positive edge of the clock. Accesses to the SDRAM are burst oriented: each request can be made up of multiple transfers. Read and write operations start at a given address and continue for a programmed number of locations, which can be of 1, 2, 4 and, 8 locations or without limit. In case of unlimited burst, refered to as a full-page burst, an additional command must be sent to terminate the operation.

The commands of the SDRAM will be described in more detail on the following lines, along with the main timing requirements. Additionally, some examples of the basic operations will be provided.

#### Commands

To control the operation of the SDRAM a set of commands are sent through the CS, RAS, CAS, and WE pins, then the mask (DQM) bank (BA) and address (A) bits provide additional configuration for some commands. Table 2.2 summarizes the commands used to operate with an SDRAM. Command names can differ from one vendor to another, but their functionality is the same. The 11th bit of the address (A[10]) is used to control the precharge of the SDRAM. Since it has a special functionality it is given a dedicated column separated from the rest of the address.

On the following lines, each command will be described with a bit more detail to have a better understanding of their functionality and how it relates to the internal operation of the SDRAM.

| Command            | CS | RAS | CAS | WE | DQM  | BA     | Α      | A[10]     |

|--------------------|----|-----|-----|----|------|--------|--------|-----------|

| No Operation       | L  | Н   | Н   | Н  | Х    | Х      | Х      | х         |

| Active             | L  | L   | Н   | Н  | Х    | Bank   | Row    | х         |

| Read               | L  | Н   | L   | Н  | Mask | Bank   | Col    | Precharge |

| Write              | L  | Н   | L   | L  | Mask | Bank   | Col    | Precharge |

| Burst Terminate    | L  | Н   | Н   | L  | Х    | Х      | Х      | х         |

| Precharge          | L  | L   | Н   | L  | Х    | Bank   | Х      | All banks |

| Auto refresh       | L  | L   | L   | Н  | Х    | Х      | Х      | Х         |

| Load Mode Register | L  | L   | L   | L  | Х    | Opcode | Opcode | Х         |

#### No operation

The *No Operation* is an auxiliary command that is used when no other command should be sent to the SDRAM, either because it is in idle or waiting for the completion of another command. It is equivalent to disabling the chip select.

#### Precharge

The *Precharge* command deactivates an active row, which is done by resetting the sense amplifiers and precharging the bit-lines to the reference voltage so they are ready for another row access. There is a minimum time,  $t_{RP}$ , between a *Precharge* command and the next *Active* command.

#### Auto Refresh

The *Auto Refresh* command must be sent during the normal operation of the SDRAM to refresh its contents. The SDRAM automatically generates the address that needs to be refreshed with an internal counter, the refresh counter shown in 2.3, which is updated each time the *Auto Refresh* command is sent. All the rows in the SDRAM must be refreshed within the refresh period,  $t_{REF}$ . Commands can be distributed along the period or sent all of them in a burst.

After a *Precharge* command a minimum time,  $t_{RP}$  must be respected before sending the *Auto Refresh* command. There is also a minimum time,  $t_{RFC}$ , between two consecutive *Auto Refresh* commands.

#### Load mode register

The *Load mode register* command is used to configure different parameters of the related to the operation of the SDRAM, such as the burst length or the CAS latency.

The *Load mode register* can only be sent when all banks are precharged. After sending it some time,  $t_{MRD}$ , must be waited for the SDRAM to be configured and no other commands can be sent.

#### Active

The *Active* command is used to open (activate) a row in a particular bank so it can be further accessed with a *Read* or *Write* command. When using the *Active* command, the bank bits select the bank while the address bits determine the row. Internally this operation moves the data from the memory cells of the selected row and bank in the SDRAM array to the sense amplifiers, then restores the values of the memory cells so data is not lost.

The whole row of data is moved into the sense amplifier. This means that multiple accesses to read or write data can be done on different columns of the same row without having to send the *Active* command each time.

There is a minimum time,  $t_{RCD}$ , before *Read* or *Write* commands can be sent after having sent an *Active* command. An *Active* command to another row of the same bank can only be sent after precharging the bank. The sense amplifiers of the bank have to be reset before reading new data. On the other hand, it is possible to send an *Active* command to a different bank, since each bank has its own set of sense amplifiers. There is a minimum time,  $t_{RRD}$ , between consecutive *Active* commands to different banks.

#### Read

The *Read* command is used to start a read access in a previously opened row. The bank bits select the bank while the address bits select the column to be read. Additionally, the 11th bit of the address determines if an auto precharge will be performed by the SDRAM after data has been read. Internally, this command moves the data from the sense amplifier of the given bank to the output data bus. Once the command is sent, the read data is available on the data bus after  $t_{CAS}$ . There is a minimum time,  $t_{CCD}$ , between two consecutive *Read* or *Write* commands.

#### Write

The *Write* command starts a write access to a previously opened row. As with the *Read* command, the bank bits select the bank and the address bits the column with the 11th bit enabling auto precharge. Internally the *Write* command copies the data from the data bus into the sense amplifiers of the given bank. There is a minimum time,  $t_{WR}$ , between a *Write* and a *Precharge* command to ensure the sense amplifiers are not precharged until data is written into memory.

#### Burst terminate

In an SDRAM, reads and writes are burst oriented, which means each *Read* or *Write* command performs several accesses to memory. The *Burst terminate* command is used to truncate the burst started with the last *Read* or *Write* command.

### Operation

#### Initialization

Before normal operation, the SDRAM must follow a set of initialization steps. Once power is applied and the clock is stable, SDRAM requires a delay of 100  $\mu$ s. During this period, only the *No Operation* command can be sent. Alternatively, the chip select can be disabled.

After the initial delay, the *Precharge* command must be sent to all banks to ensure there is not any open row. Then at least two refresh cycles must be performed by sending the *Auto Refresh* command. After that the SDRAM is ready.

Since the state of the mode register will be undetermined after power up, the last step previous to use the SDRAM is to load the mode register with the right configuration using the *Load Mode Register* command.

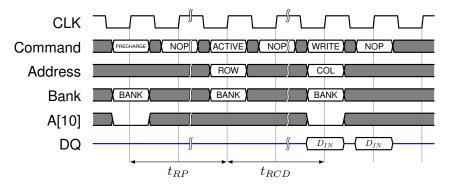

Write operation

Figure 2.4 shows an example of a basic write request to SDRAM memory with a burst size of 2. Initially, the bank is precharged. Since the 11th bit of the address (A[10]) is low, only the selected bank will be precharged. Then the *Active* command is sent to open the selected row in the selected bank.

After waiting for the required time, the *Write* command is sent to write the data into the specified column of the previously opened row in the selected bank. Since the 11th bit of the address is not enabled, the SDRAM will not do an automatic precharge after writting. In this example, a burst of 2 transfers is sent. The data of the first transfer is sent on the same cycle as the *Write* command, the data of the next transfer is sent on the following cycle.

Figure 2.4: Timing diagram of a write operation in a SDRAM.

#### Read operation

Read operation is similar as the write operation. In this case, as shown in figure 2.5, after the *Read* command the data will be ready after the number of cycles defined by the CAS latency. In case of a burst operation, subsequent data will be updated on next cycles.

### Timing parameters

| Parameter | Description                                                          |

|-----------|----------------------------------------------------------------------|

| $t_{RCD}$ | Row to Column Delay, it is the time it takes for the Active command  |

|           | to move the data from the SDRAM cell array to the sense amplifier.   |

| $t_{RRD}$ | Row activation to Row activation delay, it is the minimum time be-   |

|           | tween two Active commands.                                           |

| $t_{RAS}$ | Row Access Strobe latency, is the time it takes for the Active com-  |

|           | mand to discharge and restore the data from the row of SDRAM         |

|           | cells. After this time the sense amplifiers have completed teh re-   |

|           | sotarion of data to the SDRAM cells and the sense amplifiers can     |

|           | be precharged to access another row.                                 |

| $t_{CAS}$ | Column Access Strobe latency, it is the time it takes to the SDRAM   |

|           | to put the the data on the data bus after receiving the Read com-    |

|           | mand.                                                                |

| $t_{CCD}$ | Column to Column Delay, it corresponds to the minimum burst          |

|           | duration and it is determined by the internal prefetch length of the |

|           | SDRAM.                                                               |

| $t_{RP}$  | Time needed before the bitlines and sense amplifiers are properly    |

|           | precharged after a <i>Precharge</i> command.                         |

| $t_{WR}$  | Write recovery time, is the time needed for the write data to be     |

|           | written into the internal SDRAM arrays. It the minimum time be-      |

|           | tween a Write and a Precharge command.                               |

| $t_{RFC}$ | Required time between two consecutive Auto Refresh commands.         |

| $t_{MRD}$ | Required time between an Load Mode Register and the next Ac-         |

|           | tive or Auto Refresh command.                                        |

| $t_{REF}$ | Refresh period within all the rows of the SDRAM should be re-        |

|           | freshed.                                                             |

## 2.3 AMBA AXI

The ARM Advanced Microcontroller Bus Architecture (AMBA) is an open-standard, onchip interconnect specification for the connection and management of functional blocks in system-on-chip (SoC) designs [10]. AMBA specifications provides the interface standards that enable IP re-use and compatibility between different IPs, which is essential to reduce development costs. Additionally, AMBA provides a variety of interface specifications optimized for different requirements in terms of performance, power and area. Because of that, AMBA is flexible and widely used in multiple ASIC and SoC parts. AMBA provides a set of prototols that define how functional blocks communicate with each other, which has been constantly updated [11] [12]:

- The first generation of AMBA was introduced by ARM in 1997 and defined two specifications: the Advanced System Bus (ASB) and the Advanced Peripheral Bus (APB).

- The second generation, AMBA 2, appeared in 1999 and added the AMBA High-performance Bus (AHB).

- The third generation was introduced in 2003. AMBA 3 included the Advanced Trace Bus (ATB) and the Advanced eXtensbile Interface (AXI) targeted at high performance and high clock frequency designs and is designed to maximize bandwidth and reduce the latency of data transfers.

- In 2010 AMBA 4 specification added a revision of the AXI protocol, the AXI4, and included the AXI coherency Extensions (ACE) to provide system wide coherency which allows multiple processes to share the same memory resources.

Two metrics are used to determine the performance of a bus interface:

- Bandwidth: Rate of the data across the interface. In a syncrhonous system, the maximum bandwidth is limited by the product of the clock speed and the width of the data bus.

- Latency: Delay between the initiation and the end of the transfer. In a burst transfer, latency can also be defined as the delay between the start of the transaction and the end of the first transfer rather than the whole burst.

AXI is commonly used by many IP. It is the main interface to access the peripherals in the lowRISC SoC and therefore in the preDRAC SoC. AXI specification defines the interface between IP blocks. There are only two types of interfaces, master and slave, which are symmetrical. This section will give a summary of the main characteristics and signals of the AMBA AXI4 protocol [13].

### 2.3.1 Signals description

| Signal  | Required | Description                      |

|---------|----------|----------------------------------|

| ACLK    | Required | Global clock signal.             |

| ARESETn | Required | Global reset signal, active low. |

| Signal   | Source | Required | Description                                                                        |

|----------|--------|----------|------------------------------------------------------------------------------------|

| AWID     | Master | Required | Identification tag of the write transaction.                                       |

| AWADDR   | Master | Required | Address of the first transfer in the write transac-<br>tion.                       |

| AWLEN    | Master | Required | Number of data transfers in the write transac-<br>tion.                            |

| AWSIZE   | Master | Required | Number of bytes in each transfer in the write transaction.                         |

| AWBURST  | Master | Required | Burst type. Indicates how the address should be updated for after each transfer.   |

| AWLOCK   | Master | Optional | Provides additional information for atomic trans-<br>fers.                         |

| AWCACHE  | Master | Optional | Indicates how the transaction should progress through the system.                  |

| AWPROT   | Master | Optional | Additional protection attributes for different priv-<br>iledges and access levels. |

| AWQOS    | Master | Optional | Quality of Service identifier.                                                     |

| AWREGION | Master | Optional | Additional region indicator.                                                       |

| AWUSER   | Master | Optional | Additional user-defined extension.                                                 |

| AWVALID  | Master | Required | Indicates when the write address channel sig-<br>nals are valid.                   |

| AWREADY  | Slave  | Required | Indicates that a transfer on the write address channel can be accepted.            |

| Table 2.6: AXI Write Data channel signals. |

|--------------------------------------------|

|                                            |

| Signal | Source | Required | Description                                                               |

|--------|--------|----------|---------------------------------------------------------------------------|

| WDATA  | Master | Required | Write data                                                                |

| WSTRB  | Master | Required | Write strobes, indicate which bytes are valid.                            |

| WLAST  | Master | Optional | Indicates which is the last transfer in a write                           |

|        |        |          | transaction.                                                              |

| WUSER  | Master | Optional | Additional user-defined extension.                                        |

| WVALID | Master | Required | Indicates the write data channel signals are valid.                       |

| WREADY | Slave  | Required | Indicates that a transfer on the write data chan-<br>nel can be accepted. |

| Table 2.7: AXI Response channel signals. |

|------------------------------------------|

|------------------------------------------|

| Signal | Source | Required | Description                                                           |

|--------|--------|----------|-----------------------------------------------------------------------|

| BID    | Slave  | Required | Identification tag of a write response.                               |

| BRESP  | Slave  | Optional | Write response indicating the status of the write transaction.        |

| BUSER  | Slave  | Optional | Additional user-defined signals.                                      |

| BVALID | Slave  | Required | Indicates the write response channgel signals are valid.              |

| BREADY | Master | Required | Indicates the transfer of the write response channel can be accepted. |

Table 2.8: AXI Read Address channel signals.

| Signal   | Source | Required | Description                                                              |

|----------|--------|----------|--------------------------------------------------------------------------|

| ARID     | Master | Required | Identification tag for a read transaction.                               |

| ARADDR   | Master | Required | Address of the first data transfer in a read trans-<br>action.           |

| ARLEN    | Master | Required | Number of data transfers in a read transaction.                          |

| ARSIZE   | Master | Required | Number of bytes in each data transfer in a read transaction.             |

| ARBURST  | Master | Required | Burst type, indicates how address is updated after each transfer.        |

| ARLOCK   | Master | Optional | Additional signals for atomic transfers.                                 |

| ARCACHE  | Master | Optional | Additional signals to specify how signals progress through the system.   |

| ARPROT   | Master | Optional | Additional signal for different privilege and access type.               |

| ARQOS    | Master | Optional | Quality of Service additional signals.                                   |

| ARREGION | Master | Optional | Region indicator for a read transaction.                                 |

| ARUSER   | Master | Optional | Additional user-defined signals.                                         |

| ARVALID  | Master | Required | Indicates that read address channel signals are ready.                   |

| ARREADY  | Slave  | Required | Indicates that the transfer on the read address channel can be accepted. |

| Signal | Source | Required | Description                                                              |

|--------|--------|----------|--------------------------------------------------------------------------|

| RID    | Slave  | Required | Identification tag for read data.                                        |

| RDATA  | Slave  | Required | Read data.                                                               |

| RRESP  | Slave  | Optional | Read response indicating the status of the transfer.                     |

| RLAST  | Slave  | Required | Indicates the last transfer in a read transaction.                       |

| RUSER  | Slave  | Optional | Additional user-defined signals.                                         |

| RVALID | Slave  | Required | Indicates that the read data channel signals are valid.                  |

| RREADY | Master | Required | Indicates that a transfer on the read data chan-<br>nel can be accepted. |

|            |          | ا م در در م |          |

|------------|----------|-------------|----------|

| 12018 2.9. | AXI Read | Channel     | signals. |

#### 2.3.2 AXI architecture

#### Clock

Each AXI component uses a single clock signal. Input signals are sampled on the rising edge of the clock and all output signals changes must occur after the rising edge of the clock. Between master and slave devices there must not be any combinational logic between inputs and outputs.

#### Reset

The AXI protocol uses as single active low reset signal. It can be asserted asynchronously but it must be deasserted synchrously with the rising edge of the clock. During reset, the master must keep the signals ARVALID, AWVALID and WVALID low and the slave must keep RVALID and BVALID signals low. All the other signals can have any value. The master can assert ARVALID, AWVALID or WVALID at the rising edge of ACLK after ARESTETn is high.

#### **AXI channels**

AXI transactions are made of five independent channels:

- Read address channel (AR).

- Read data channel (R).

- Write address channel (AW).

- Write data channel (W).

- Write response channel (B).

The read address and read data channel are used in read transacions while the write address, write data and write response channels are used in write transactions. Since read

and write channels are independant from each ohter, read and write operations can happen at the same time.

Channels are unidirectional, which means they go from master to slave or the other way around. The address channels go from master to the slave and contain information about the transfer, including the address that will be accesses. On a read transfer, the read data channel contains the response from the slave, including the read data. In a write transfer, the write data channel contains the data that has to be written into the slave. The additional response channel is needed in write transfers so the slave can send a response to the master.

#### Handshake

The AXI protocol uses a hanshake mechanism so each channel has a pair of signals, VALID and READY. The source uses the VALID signal to indicate the channel contains valid data while the destination uses the READY signal to indicate it can accept new data. Once both VALID and READY of a given channel are asserted the handshake occurs at the rising edge of the clock signal and the transaction is completed. Additionally, write and data channels also have a LAST signal to indicate if the last item of the transaction is being transfered.

In the handshake process, the source must assert the VALID signal when it has valid data, it must not wait for the READY signal to be asserted. Once asserted the VALID signal must remain high until the handshake occurs. The destination can wait for the VALID signal before asserting the correspoding READY and if READY is asserted, it can be deasserted before VALID is asserted. To prevent a deadlock situation the VALID signal must not depend on the READY signal.

#### **AXI transactions**

AXI allows multiple outstanding addresses, which means a master can issue transactions without waiting previous transactions to complete. Each channel has a field used to send the identifier (ID) of the transfer. Transfers that have the same ID must be processed in order, but out-of-order transactions can be done by using different transaction IDs.

AXI is a burst-based protocol and each transaction can be made of multiple transfers. The address channel contains the information that defines the size and the number of transfers as well as the type of burst. The address is sent only once per transaction, then the slave has to generate subsequent addresses according to the type of transfer specified by the master.

### 2.3.3 Operation

#### Write transaction

Figure 2.6 shows an example of a write transaction. The transaction starts when both the write address channel and write data channel have done the handshake. In a burst transfer, the write data channel will be updated for each transfer. On the last transfer, the WLAST signal is enabled. Once all the data has been sent a response is returned. The transaction has completed after the handshake on the response channel.

Figure 2.6: Timing diagram of an AXI write transaction.

#### **Read transaction**

Figure 2.7 shows an AXI read transaction which is similar to the write transaction. In this case the transaction starts once the handshake of the read address channel is produced. The slave returns the read data and enables the RLAST signal on the last transfer.

Figure 2.7: Timing diagram of an AXI read transaction.

## 2.4 ASIC design flow

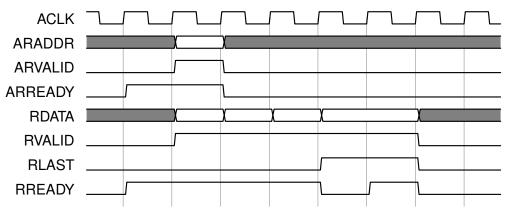

Figure 2.8: Different steps in the ASIC design flow

Before a design is ready to be put on a chip, several steps must be performed. ASIC design is a complex process which is summarized in figure 2.8.

The process starts with a set of specifications that define the functionality of the design, from there the initial RTL is developed. Additionally, a testbench is also developed in parallel with the RTL. At the end of the design phase, both an RTL and a testbench are obtained.

After the initial design stage the functionality of the RTL must be verified. If the verification is not successful, the design needs to be modified and then verified again. This is an iterative process that can take several iterations. The verification process is seen in more detail in section 2.4.3.

The next step is the logic synthesis. During this step, the high-level RTL description is mapped into a netlist made of logic gates. The gates are defined in a standard cell library, which contains area, power, and timing information. More about the synthesis process in section 2.4.1.

A post-synthesis verification is done to ensure the obtained netlist has the same behavior as the original RTL.

Finally, on the Place&Route (P&R) step the previous netlist is placed into the actual silicon area, the routing of the different cells is performed, and the clock tree is generated. In the end, another netlist and a physical layout are obtained.

A post-P&R verification is done to ensure this last netlist still behaves as expected. In this phase, there are additional checks to ensure the final layout meets the design rules so it can be manufactured, or that the design is within the power constraints.

Once the design is completed and verified, the obtained layout can be sent to tapeout.

This completes an overview of the full ASIC design flow. This project does not follow the full flow, but only the first steps of design and logic synthesis, with their respective verifications, are performed. The flow used in this project is the one within the dashed box in figure 2.8. In the following sections the main synthesis and verification steps are analyzed in more detail. Moreover, though it could be considered part of the verification, there is a separate section dedicated to power analysis.

### 2.4.1 Synthesis

To manufacture a chip what is needed is a layout that describes the shape and position of each transitor on the wafer. Since the number of transistors of digital designs is extremely high, it is not feasible to manually place all of them. Digital designers work at a higher level

of abstaction and use RTL descriptions to define the behavior of the design.

Foundries still require the layout to manufacture the chip so the original RTL desription has to be converted into the final layout. This is what is done by the synthesis and Place&Route processes.

Logic synthesis is the process of converting the RTL desription into a gate-level netlist. At the same time, this process has different steps [14]:

- Generic synthesis: During this initial step, the original RTL is converted into a set of registers and combinational logic made of generic gates.

- Mapping: This step maps the design from generic gates to a specific technology library.

- Optimization: The final step performs incremental optimizations on the mapped design in order to meet the given design contraints.

Additionally, physical synthesis is a similar process but uses information from a floorplan so it has more accurate timing information based on the actual placement of the different cells and can optimize the design taking such information into consideration.

### 2.4.2 Place&Route

Place&Route is composed of several steps to convert the netlist obtained from synthesis into the final layout that can be sent to the foundry. The main steps are:

- Floorplanning: this initial step consist in designing the layout and how the different elements of the design will be placed on silicon.

- Placement: after having the floorplan, this step consist on placing the cells or other macros into the actual silicon area according to the floorplan previosly designed, which is automatically performed by the tool.

- Routing: in this step the tool perform the connections of the different nets in the design.

- Parasitic Extraction: After routing the parasitic resistors and capacitors of the wires can be extracted. This information can be used later to verify the proper behavior of the system, both in terms of timing but also power, noise or IR drop.

- Clock Tree Synthesis: This step generates the routing of the clock and places the required buffers so the clock reaches all the the elements in the design minimizing the skew.

### 2.4.3 Verification

Verification is an essential step in the ASIC design process, as it is crucial to ensure the proper operation of the ASIC before sending the design to the foundry and manufacture the chip. Verification consist of checking the design meets timing, power, and other constraints as well as testing the functionality to make sure the design will behave as expected once implemented on silicon. It is an essential part of the ASIC design process, which can take from 40% to 70% of the total development efforts [15].

Different tools and methodologies are used in in the industry in order to both provide more accurate results, which increase the reliability of the verification, and to speed up the process and accelerate the design flow. Such methodologies can be divided into the following groups:

- **Simulation:** use a testbench to provide stimulus to the design and evaluate its behavior.

- Static verification: includes linting and static timing analysis. Lint checking revises the syntaxis of the code to find possible errors such as uninitialized variables, unsupported constructs or port mismatches, and static timing verification checks if the design meets the timing requirements. Unlike simulation, it does not require a test-bench.

- Formal verification: use of mathematical techniques to verify the correctness of the design. One type of formal verification is the equivalence check, which verifies the equivalence between two designs, for example between RTL and a netlist or between two netlists obtained at different stages, such as one after logical synthesis and the other after physical synthesis. It does not require testbench but only a functional reference design.

- **Physical verification:** check the integrity of the design to determine if it meets the design rules and other electrical or power requirements to ensure it can be manufactured.

Verification is not just a final step in the design flow, but a reiterative process that should be done at every stage. Previously, figure 2.8 showed here is a verification step after each development stage in the ASIC design flow. First, an initial verification of the RTL design, then another verification after the different synthesis to ensure both the netlist has the same functionality as the original design as well as timing requirements are met. In the following lines, the methodology and tools used to perform the verification of the design at the different stages of the ASIC design flow will be described in more detail.

#### **RTL verification**

The first step in the verification process is to simulate the RTL design to ensure it behaves accordingly to the desired functionality. At this stage both simulation and static analysis methods can be used to verify the design:

• Behavioral simulation: In RTL behavioral simulation a testbench is used to determine if the design under test (DUT) behaves as expeted or not [16]. The testbech can be seen as a wrapper around the DUT which generates the stimulus, applies such stimulus to the DUT, gets the response from the DUT and checks if the response coincides with the expected one. It is important to design an adequate testbench that applies the right stimulus to the DUT so the functionality is properly tested and a reliable verification is obtained. To generate the stimulus a testench use additional components, which can be non-synthetizatble modules used to emulate the behavior of external components and buses so the DUT can be properly tested.

In a real synchronous system, due to the propagation delay, signals changes slightly after the clock edge. This is not true with RTL simulation, since there are no delays all

signals change at the same simulation time. Depending on the simulator and how the different modules of the testbench are implemented, it can happen that some signals change before the clock edge and other signals after it but at end everything happens at the same simulation time. This problem is known as race condition. A possible workaround to avoid race condition is to add small delays so signals change after the clock edge like its expected from the real hardware. SystemVerilog offers more complex methodologies to prevent race condition which are out of the scope of this project, more information about this topic can be found on C. Spear [16].

• Static analysis: Linting tools can be used to check the design and detect both syntax as well as possible design errors such as mismatch between signals, unused signals, combinational loops or inferred latches.

It is not needed to wait until the design is completely finished to start with the simulations. Starting with simulations at an early stage in the design phase is a good way to identify and fix errors, which can save a significant amount of time in later phases of the design.

#### Post-synthesis verification

After synthesis, the RTL is mapped into a gate-level netlist. The obtained netlist is closer to the final desing that will be implemented on silicon, as it is made of gates from the standard cell library that was provided during synthesis.

Since the technology and cell libraries provide timing information it is now possible to perform timing analysis on the design. After the logic synthesis both a gate-level netlist and a SDF (Standard Delay Format) file are obtained. The SDF file contains the delay information of each net in the design.

Again, it's important to verify the design and check that after synthesis the obtained netlist still performs as expected. At this stage, there are different methods that can be used to perform such verification. The main methods are:

• Static timing analysis: As opposed to simulation, static timing analysis [17] is a method used to verify the timing of a design which doesn't require a testbench that provides stimulus to it. On the other hand, what it does require is the timing constrains of the system (such as the definition of the different clocks).

Static timing analysis performs an exhaustive verification, checking all the paths in the design, and validates if the design can operate at the desired speed. This is done with the same tool used for synthesis, Genus, which can generate detailed timing reports of the different paths in the design.

- Equivalence check: As previously mentioned, equivalence check is a way to verify that two different designs are functionally equivalent. This is a step that can be performed after synthesis to verify if the obtained netlist has the same functionality as the original RTL.

- **Gate-level simulation:** Verification methods such as static timing analysis and equivalence check can be used to verify the design but, for large and complex systems the combination of such methods might not be enough and another level of verification is required. Gate-Level simulation can help to find errors that static timing analysis

or an equivalence check are not able to detect. For example it can help to verify the initialization and reset sequence.

Gate-level simulation consist in the simulation of a netlist. As with the RTL simulation, a testbench is needed to provide stimulus to the DUT. The testbench can be the same as the used in the initial RTL behavioral simulation. Since after synthesis timing information for the design is obtained, this information can be used to do a simulation taking into account such delays. At this point, different simulations can be performed:

- Zero-Delay simulation: This simulation does not contain delay information but it is still useful to validate the functionality of the netlist and verify that the initialization and reset sequence work as expected. The advantage of this kind of simulations is that are much faster than simulations with timing. On the other hand, since no timing checks are done they can not be used to completely verify the netlist.

- SDF simulation: In this case the delays defined in an SDF file are annotated into the corresponding nets of the design. After successfully reading and annotating the SDF file, it can be seen in a waveform viewer that the signals do not longer change with the clock but have some delay. This kind of simulations can be much slower than zero-delay simulations, but they are crucial to verify the actual behaviour of the system and check if the timing requirements, such as hold and setup times, are met for the different cells in the design.

#### Post-P&R verification

After the place and route (P&R) a new netlist and more accurate delay information are obtained. With this new information another static timing analysis, equivalence check and gate-level simulation can be performed. The verification process followed in this step is the same as in the post-synthesis verification seen above.

After this step a layout is generated, which is what is sent to the foundry to manufacture the chip. In this case, additional checks are required, such as design rule check (DRC) to ensure the design meets the requirements of the foundry and to ensure the layout is functionally equivalent to the given netlist.

#### 2.4.4 Power analysis

For the last decades, following Moore's law, the number of transistors integrated on a single die has kept increasing. Technology scaling allowed a significant improvement of processors performance. At the same time with the increasing number of transistors as well as the operating frequency, power dissipation become a major concern in ASIC design.

Power dissipation depends on many factors such as the size of the design and how the architecture is implemented, the technology and cells used in the fabrication process, the operating frequency and the actual task being performed. Often there is a tradeoff between power, area and performance. It is becoming more important to perform power analysis, not only as a final signoff verification step but also at intermediate verification to ensure the design stays within the desired constraints.

Power dissipation of an ASIC can be divided into two components, the static and dynamic power [18]. The source of the static power is the leakage current in the transistors,

which depends for one side on the size and number of transistors in the design and also on the technology used to fabricate them:

$$P_{static} \propto I_{leakage} \cdot V_{DD}$$

(2.1)

On the other hand, the dynamic power depends mainly on activity of the ASIC:

$$P_{dynamic} = \alpha \cdot C_L \cdot V_{DD}^2 \cdot f \tag{2.2}$$

The final power is the combination of both:

$$P_{total} = P_{static} + P_{dynamic} \tag{2.3}$$

#### Static power

Static power is the power dissipated even when there is no activity, simply because the system is powered on.

Ideally, due to the complementary behavior of a CMOS cell there should not be any static power consumption since on steady state either the NMOS or the PMOS network are off and there is no direct path between  $V_{DD}$  and  $V_{SS}$ . With real transistors, there is some static power dissipation due to the leakage currents. The main source of static power disispation is the subthreshold leakage, which is the leakage current between drain and source because of the transistor not turning completely off when the gate voltage falls below the threshold voltage.

As mentioned, leakage depends on the actual technology and libraries used. This information is available on the cell libraries provided by the vendor, the same ones used during synthesis. In the tools used, Genus and Joules, the static power is reported as leakage power.

#### **Dynamic power**

Dynamic power is the power dissipited because of the activity of the design. It is produced when there is a transition in the state of the cells, eihter from high to low or low to high. The main source of dynamic power is the charging and discharging of load capacitances. An additional source of dynamic power is the short circuit that is produced during a transition where for an instant both NMOS and CMOS networks are on at the same time and the current flows from  $V_{DD}$  to  $V_{SS}$ .

To compute the dynamic power it's important to have an estimation of the activity of the design. Not every signal will change on every cycle so activity can bee seen as a factor ( $\alpha$  in formula 2.2) that determines the rate of change of the signals. For every node, the capacitance and activity should be considered and the total power will be the sum of the power of all nodes.

The activity factor depends on the task being performed and sometimes it could be difficult to estimate which factor use. As an alternative, its also possible to obtain the activity factor from the switching information obtained with an RTL or gate-level simulations. Additionally, to compute the dynamic power are also needed the technology and cell libraries since they contain the information needed to obtain the capacitances of each node.

In the tools used, Genus and Joules, the dynamic power of each cell is divided into two: internal and switching power. The internal power is the power dissipated internally the cell, which includes the short circuit currents and the charging and discharging of parasitic capacitances within the cell. On the other hand, the switching power is the power dissipated because of the load capacitance on the output of the cell, which include the output capacitance and also the parasitic capacitance of the wire.

## **Chapter 3**

# Methodology

The purpose of this project is to design a memory controller that acts as an interface between the SoC and the external memory. For one side, the controller has to communicate with the main processor using the AXI protocol, previously described in section 2.3. On the other side, the controller has to send the required request to the external SDR SDRAM, described in section 2.2.3.

The design has been designed in Verilog, then synthetized, verified and finally a power analysis has been done. This chapter describes the different steps and methodologies used involved in the the design of the AXI-SDRAM controller.

## 3.1 Implementation

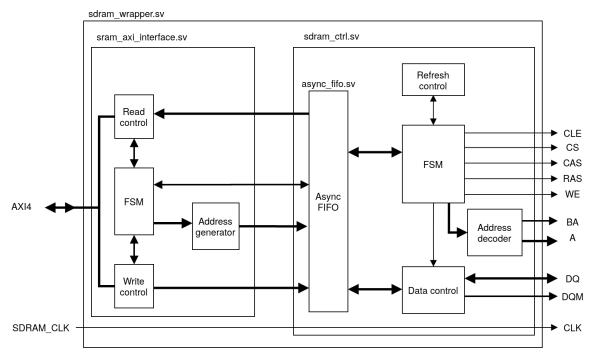

Figure 3.1: Organization of the design modules.

The purpose of the controller is to provide a simplied way to the accesses the memory. The proposed design is composed of two cascaded blocks as shown in figure 3.1:

- **AXI interface:** This module is used to adapt the previous SDRAM interface to the AXI4 specification, turning the design into an AXI4 slave that can communicate with the main processor through the AXI bus.

- **SDRAM controller:** This module interacts with the external SDRAM memory and provides a simple interface that makes the read and write operations transparent to the user. It contains the logic required to manage the accesses to the SDRAM, generate the appropriate commands and control the refresh sequence. Additionally it contains an asynchronous FIFO which is used to synchronoize the data between different clock domains, from the main clock to the SDRAM clock and the other way around.

Both blocks are wrapped together to provide the final AXI-SDRAM interface. On the following lines the actual implementation of the different modules in the design will be described.

### 3.1.1 SDRAM controller

As previoulsy seen in section 2.2.3, SDRAM has a standard interface composed of several control signals (CAS, RAS, WE and CS) and an address, bank, data and mask buses. The SDRAM controller is built on top of that and provides a simpler interface which consist of a an address, both input and ouput data buses, a RW signal and a set of valid and ready signals to control the transactions, in a similar way as the handhsake in the AXI bus works. The whole set of signals is described in table 3.1.

The suffix *sdram* is used for the signals that goes to the SDRAM, the prefix  $\_o$  indicates the signal is an output of the SDRAM controller, similarly the prefix  $\_i$  is used for inputs. An additional  $\_io$  prefix is used to denote bidirectional signals. Moreover the previous table shows to which interface belongs each signal as well as its size. Some of the sizes are not fixed but depend on a paramater than can be set set when instantiating the design. This adds some flexibility as it allows the controller to be configured according to the specific needs of the project. Table 3.2 contains the modifiable parameters in the SDRAM controller.

Some of the parameters depend on the internal configuration of the SDRAM chips or how many chips are used. For example, multiple chips could be used in parallel, commonly referred to as a rack, which will increase the memory data width. Similarly, multiple racks could be used, which would increase the number of chip selects. There are other parameters, such as the number of rows and columns, which depends on the internal organization of the SDRAM chip. Additionally, the timing configuration can vary from one chip to another, so some parameters related to the operation of the SDRAM can also be modified. Such parameters include the CAS latency or some critical delays that must be respected, in such case the parameter value refers to the number of cycles of delay.

From the user interface side, the parameters allow the modification of the data and address widths and also if the controller includes or not the asynchronous FIFO used for synchronization. If master operates at the same frequency as the SDRAM there is no need to synchronize between both domains, then by removing the overhead of the synchronization the latency can be reduced by some cycles.

Parameters can be modified to adapt the controller to different system requirements, but

| Port        | Interface | Size               | Description                                                                                                             |  |

|-------------|-----------|--------------------|-------------------------------------------------------------------------------------------------------------------------|--|

| clk₋i       | User      | 1                  | Main clock of the master system.                                                                                        |  |

| clk_sdram_i | User      | 1                  | Internal clock of the controller, at the same                                                                           |  |

|             |           |                    | frequency of operation as the SDRAM.                                                                                    |  |

| rstn₋i      | User      | 1                  | Asynchronoust active low reset.                                                                                         |  |

| addr₋i      | User      | ADDR_WIDTH         | Input address bus.                                                                                                      |  |

| rw₋i        | User      | 1                  | Read/Write enable signal, 0 for read and 1 for write.                                                                   |  |

| data₋i      | User      | DATA_WIDTH         | Data input bus. Contains the data to be writ-<br>ten into the SDRAM.                                                    |  |

| data_o      | User      | DATA_WIDTH         | Data output bus. Contains the data read from the SDRAM.                                                                 |  |

| busy_o      | User      | 1                  | Output busy signal. Indicates the controller is busy and can not accept more requests.                                  |  |