# Detection of hardware trojans and DFA attacks on cryptographic systems by applying residue checking

Ana Lasheras Mas

Date of defense: July 4th, 2019 Advisor: Ramon Canal Corretger (Departament d'Arquitectura de Computadors)

MASTER IN INNOVATION AND RESEARCH IN INFORMATICS Specialization in High Performance Computing Facultat d'Informàtica de Barcelona (FIB) Universitat Politècnica de Catalunya (UPC) – BarcelonaTech

#### Abstract

This thesis proposes the application of residue checking techniques on cryptographic accelerators to protect these circuits against malicious attacks. The focus is set in two different types of attacks. On one hand, the detection of hardware Trojans inserted during the design phase of a chip. On the other hand, finding errors injected during the execution of the system to avoid differential fault analysis attacks.

Hardware Trojans are malicious modifications of electronic circuits that can be introduced in any of their production phases and can affect the circuit in different ways. From all the different types of Trojans, we are addressing hardware Trojans introduced on the design or the fabrication phase of a chip focusing on the attacks where the variations affect the functionality of the circuit. For that reason, the evaluated systems are described in RTL using an HDL language. In this case, the proposed solution must be able to detect any change on the signals that the Trojan produces on the circuit and indicate somehow the system has been manipulated so it is not trustworthy.

Differential Fault Analysis (DFA) attacks try to obtain secret information from the execution of a cryptographic algorithm like other side channel attacks. The information is obtained by doing multiple executions for the same inputs where errors are injected during this execution. These executions generate a set of incorrect outputs through which sensitive information can be acquired. In this case, the proposal has to be able to perceive the alteration on the signals calculating the encrypted/decrypted value to repel the DFA attack by changing the output to a random value leaking no information to the attacker.

The technique used to detect these errors is called residue checking. Residue checking is a procedure initially defined to detect soft-errors in functional units. In this thesis, we propose to extend the usage of residue checking to security purposes and, specifically, to detect hardware Trojans and DFA attacks. To the best of our knowledge, this is the first time this combination is proposed.

In order to evaluate the proposal, three different cryptographic algorithms have been selected to apply residue checking (RSA, SHA and AES). These algorithms use distinct encryption schemes. We demonstrate how residue checking can be successfully applied in all of them with the aim of detecting hardware Trojans and repel DFA attacks.

First, we implemented the residue checker on the selected cryptographic circuits. Then, the protected circuit has been simulated to measure the error detection rate of the system with different configurations. Additionally, we have measured the overhead of the protection circuit in terms of operating frequency, power consumption and area. The goal of this assessment is to calculate how effective and costly is to apply the residue checking technique as a protection mechanism in cryptographic circuits.

## Acknowledgements

First, I would like to thank my supervisor Ramon Canal Corretger for giving me the opportunity to work on this project, and also for all his advise during this master thesis.

I also would like to thank Luca Cassano from the Politecnico di Milano for helping us to contextualise the proposal of the project in the hardware security areas.

Furthermore, I thank my family for supporting me always, and for giving me the opportunity to do this master at UPC.

# Contents

| 1        |      | / 8       | 1                                                                                                                                     |          |

|----------|------|-----------|---------------------------------------------------------------------------------------------------------------------------------------|----------|

|          | 1.1  |           | 0                                                                                                                                     | 2        |

|          | 1.2  |           |                                                                                                                                       | 3<br>1   |

|          | 1.3  | Objectiv  | ves of this thesis                                                                                                                    | 4        |

| <b>2</b> | Stat | te of the |                                                                                                                                       | 5        |

|          | 2.1  | -         |                                                                                                                                       | 5        |

|          |      |           |                                                                                                                                       | 5        |

|          |      |           |                                                                                                                                       | 6        |

|          |      |           |                                                                                                                                       | 7        |

|          |      | 2.1.4 l   | Detection applying formal verification methods                                                                                        | 7        |

|          | 2.2  | Techniq   | ues to protect against DFA attacks                                                                                                    | 7        |

|          |      | 2.2.1 l   | Protection based on external devices                                                                                                  | 8        |

|          |      | 2.2.2 ]   | Protection based on code modifications                                                                                                | 8        |

|          |      | 2.2.3     | Protection based on new protocols                                                                                                     | 8        |

|          | 2.3  | Residue   | checking                                                                                                                              | 8        |

|          |      | 2.3.1     | Application of residue checker in the last years                                                                                      | 9        |

|          | 2.4  |           |                                                                                                                                       | 9        |

| 3        | Met  | thodolog  | zv 10                                                                                                                                 | 0        |

| -        | 3.1  |           | $entation \dots \dots$          |          |

|          | 0.1  | -         | Initial decisions and stages of implementation                                                                                        |          |

|          |      |           | Development tools                                                                                                                     |          |

|          | 3.2  |           | ion                                                                                                                                   |          |

|          | 0.2  |           | Initial decisions and stages of evaluation                                                                                            |          |

|          |      |           | Evaluation tools                                                                                                                      |          |

| 4        | D    | 1         |                                                                                                                                       | <b>n</b> |

| 4        |      | -         | nt of the proposal 12                                                                                                                 |          |

|          | 4.1  |           | s and re-organisation of the cryptographic cores 12                                                                                   |          |

|          |      |           | Residue Checking and Rotary Residue Checking 13                                                                                       |          |

|          | 4.0  |           | Fault injector                                                                                                                        |          |

|          | 4.2  |           | on of RSA applying residue checking 10                                                                                                |          |

|          |      |           | Algorithm                                                                                                                             |          |

|          |      |           | RTL implementation of the original algorithm 1                                                                                        |          |

|          |      |           | Modifications to the design 19                                                                                                        |          |

|          | 4.3  |           | on of SHA applying residue checking                                                                                                   |          |

|          |      |           | Algorithm $\ldots \ldots 2$         |          |

|          |      |           | RTL implementation of the original algorithm $\ldots \ldots \ldots \ldots \ldots 22$                                                  | 2        |

|          |      | 4.3.3 I   | Modifications to the design $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 23$                                | 5        |

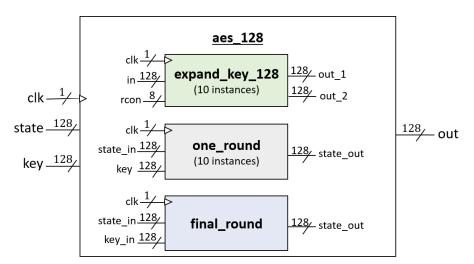

|          | 4.4  | Protecti  | on of AES applying residue checking                                                                                                   | 8        |

|          |      | 4.4.1     | Algorithm $\ldots \ldots 23$ | 8        |

|          |      | 4.4.2 l   | RTL implementation of the original algorithm                                                                                          | 0        |

|          |      | 4.4.3 I   | Modifications to the design                                                                                                           | 1        |

| <b>5</b> | Evaluation of the work |          |                                                       |    |  |  |  |  |  |

|----------|------------------------|----------|-------------------------------------------------------|----|--|--|--|--|--|

|          | 5.1                    | Defini   | tion of evaluation metrics                            | 34 |  |  |  |  |  |

|          | 5.2                    | Perfor   | mance results                                         | 35 |  |  |  |  |  |

|          |                        | 5.2.1    | Study of the detection rate                           | 35 |  |  |  |  |  |

|          |                        | 5.2.2    | Study of the overhead included to the original design | 40 |  |  |  |  |  |

| 6        | Pub                    | olicatio | ons and future work                                   | 46 |  |  |  |  |  |

|          | 6.1                    | Future   | e work                                                | 46 |  |  |  |  |  |

| 7        | Con                    | nclusio  | ns                                                    | 47 |  |  |  |  |  |

# List of Figures

| 1.1  | Estimated number of systems affected given a vulnerability per system level   | 1  |

|------|-------------------------------------------------------------------------------|----|

| 1.2  | ICs production cycle                                                          | 2  |

| 1.3  | Classification of hardware Trojans                                            | 2  |

| 1.4  | Example of a functional hardware Trojan[9]                                    | 3  |

| 1.5  | Example of a Differential Fault Analysis attack on AES                        | 4  |

| 4.1  | Modules inserted within the cryptographic module design                       | 12 |

| 4.2  | Explanation of the residue checker mechanism                                  | 13 |

| 4.3  | Explanation of the rotary residue checker mechanism                           | 14 |

| 4.4  | RTL schematic of the fault injector component                                 | 15 |

| 4.5  | Internal design based on logic gates of the fault injector component for      |    |

|      | an input of size 2 bits                                                       | 15 |

| 4.6  | Encryption/Decryption scheme in asymmetric cryptography                       | 16 |

| 4.7  | Digital signature scheme in asymmetric cryptography                           | 16 |

| 4.8  | RSA schema of the components from the original RTL                            | 17 |

| 4.9  | RSA schema of the modifications added to the original design                  | 19 |

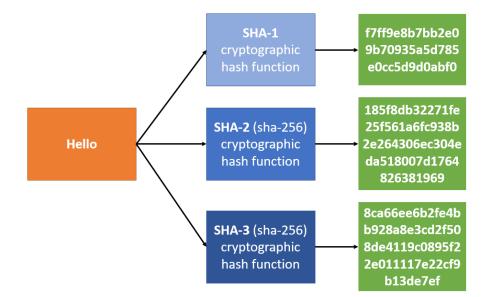

| 4.10 | Application cryptographic hash functions from the SHA family                  | 21 |

| 4.11 | SHA-1 schema of the components from the original RTL                          | 22 |

| 4.12 | $Pre-processor$ component instantiate within the $shacrypto$ component $\ $ . | 23 |

| 4.13 | Internal overview of the SHA-1 function based on the RTL design               | 24 |

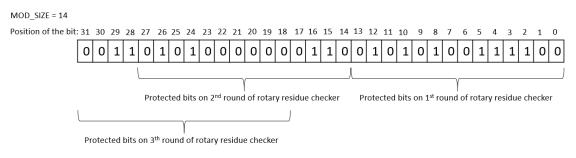

| 4.14 | Example of the rotary residue checker protecting 14 bits                      | 27 |

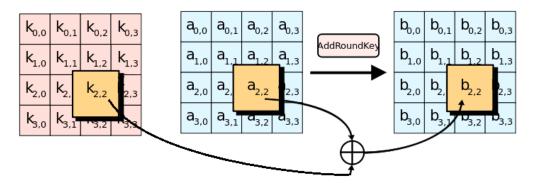

| 4.15 | Add round key operation[54]                                                   | 28 |

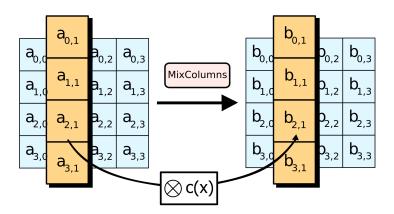

| 4.16 | Mix columns operation[54]                                                     | 29 |

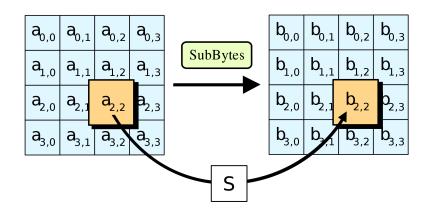

| 4.17 | Substitution of bytes operation[54]                                           | 29 |

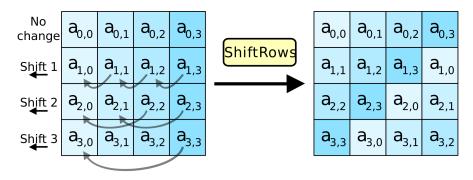

| 4.18 | Shift rows operation[54]                                                      | 29 |

| 4.19 | AES schema of the components from the original RTL                            | 30 |

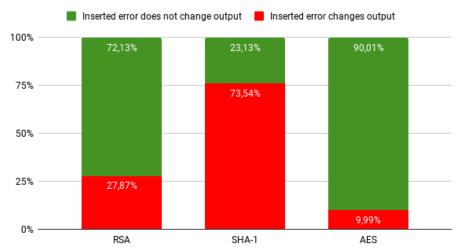

| 5.1  | Comparison of the inherent fault-tolerance represented by algorithms          | 36 |

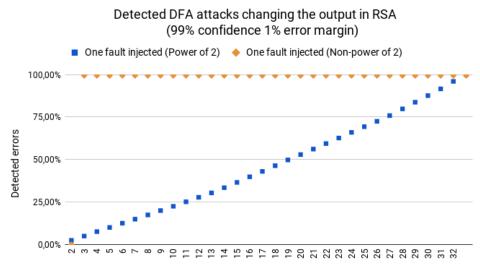

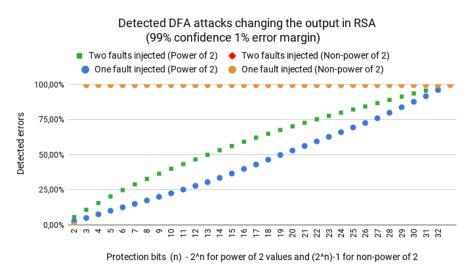

| 5.2  | Percentage of DFA attacks detection in RSA                                    | 37 |

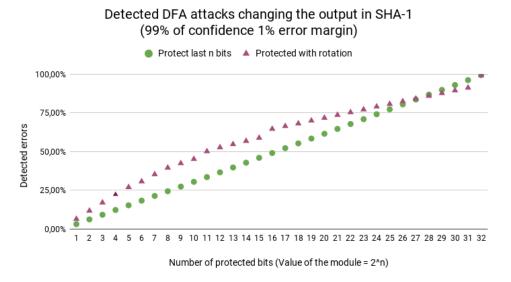

| 5.3  | Percentage of DFA attacks detection in SHA-1                                  | 38 |

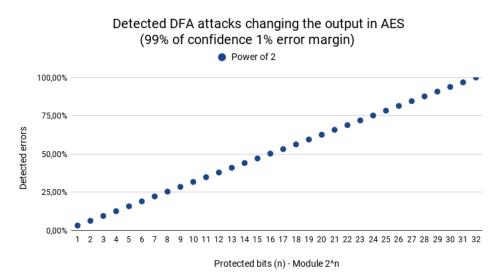

| 5.4  | Percentage of DFA attacks detection in AES                                    | 38 |

| 5.5  | Comparison of DFA attacks detection injecting consecutive faults in RSA       | 39 |

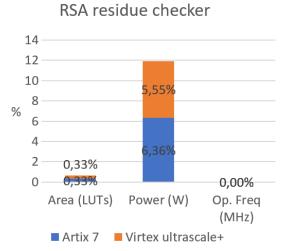

| 5.6  | Summary of the overhead because of adding residue checker                     | 45 |

# List of Tables

| 5.1 | Number of simulations for a certain confidence an error $margin[50]$ . |   | 35 |

|-----|------------------------------------------------------------------------|---|----|

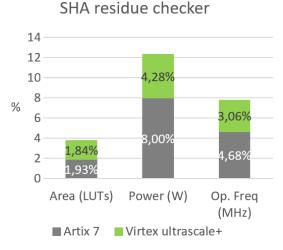

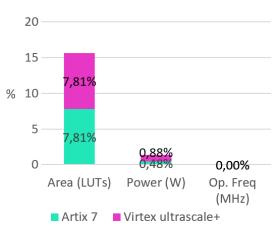

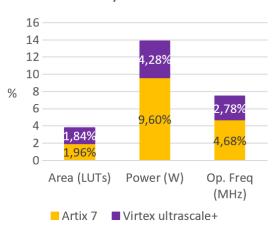

| 5.2 | Power consumption synthesising with Virtex UltraScale+                 | • | 41 |

| 5.3 | Power consumption synthesising with Artix 7                            |   | 42 |

| 5.4 | Area utilisation synthesising with Virtex Ultrascale+                  |   | 42 |

| 5.5 | Area utilisation synthesising with Artix 7                             |   | 43 |

| 5.6 | Restrictions to calculate the timing constraints of the designs        |   | 43 |

| 5.7 | Time constraints from synthesis with Virtex Ultrascale+                |   | 44 |

| 5.8 | Time constraints from synthesis with Artix 7                           |   | 44 |

# 1. Introduction, motivation and goals

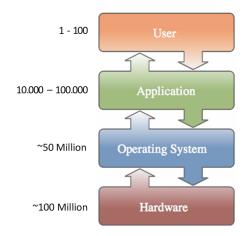

Nowadays, the number of computing devices is increasing and along with cyber-attacks are also rising [33]. These attacks can be set at different layers like in the application or operating system level, on the software layer, but also at the hardware level (Figure 1.1). One example of these attacks is the failure of a Syrian radar which microprocessors had a hidden *backdoor* inside that temporarily blocked the radar[1]. Another example of a hidden *backdoor* is the one in the chips used by Boeing 787 planes that could allow cyber-criminals to override and control the computer systems[4]. There are also examples of attacks on the field of security as the one on the random generator used for cryptography in Intel Ivy Bridge processors [36].

Figure 1.1: Estimated number of systems affected given a vulnerability per system level

Hardware has been always the target of reverse engineering for competitiveness between companies in the sector. However, in the last years, it has also become the target of malicious attacks in order to gain access to a computer or to extract information. Apart from the previous examples, there are much more critical vulnerabilities that have been discovered in modern processors like Spectre[29], Meltdown[32], RIDL[51] or Zombie Load[49]. These attacks can be prevented, once they had been discovered, through software patches. But, these patches are only a fix, not a solution. Using a patch can only be applied once the attack has been discovered implying that numerous system has been already compromised. Additionally, patches can degrade the performance of the system because to prevent the attack they have to change the initial behaviour of the system that it has been planned during the design phase. Therefore, new systems must tend to a secure by design approach where the security policies are embedded therein.

Hardware is the base of systems and all the layers built on top depends on it. For that reason, if the hardware is vulnerable, then the whole system is compromised that is why it should be protected.

Historically hardware has been a trusted source as all design and manufacturing were done by the same reliable company. Nevertheless, these days the high manufacturing costs have split the semiconductor industry into three kinds of companies: i) "Pure-play semiconductor foundries" which business is focus on the manufacturing process producing integrated circuits (ICs) for other companies (e.g TSMC, GlobalFoundries), ii) "fabless" companies that do the design but do not produce the chip (e.g. Qualcomm, ARM) and iii) "integrated device manufacturers" that both design and manufacture (e.g. Intel, Samsung). This fragmentation implies multiple companies into the ICs production cycle(Figure 1.2) breaking the trust chain from the design to the product manufacturing. Consequently, security principles need to be put in place at the design time to anticipate vulnerabilities in order to guarantee a trustful product.

Figure 1.2: ICs production cycle

In the vulnerable process of chip production, many modifications can be inserted like hardware Trojans during the design or fabrication phase. After fabrication, fault injection can be used to obtain information from non-protected chips as in DFA attacks.

Two complementary approaches can be used to make this process more trustworthy: i) white box approach when the design is completely made by the trusted company and ii) black box approach applied when the product contains multiple modules (IPs) designed by others. The white box approach is based on inserting the corresponding security functionalities during the design phase to guarantee the service once manufactured elsewhere. The black box approach extends the design based on third-party IPs with extra functionalities to ensure the trust in the non-trusted parts.

# 1.1 Hardware Trojans

Hardware Trojans are malicious circuits place on a trusted chip that can cause unexpected behaviours on the regular operation of the system.

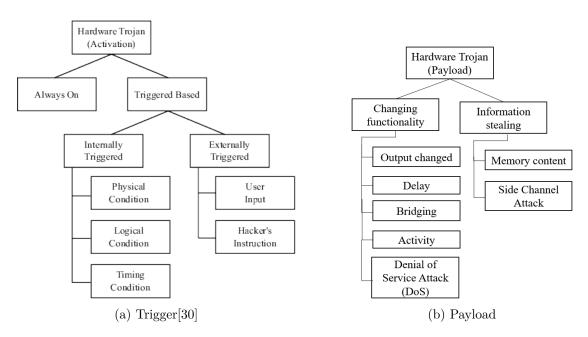

Figure 1.3: Classification of hardware Trojans

Hardware Trojans can be classified based on how they are triggered and their payload[10] (Figure 1.3). This malicious circuits can be triggered after i) a combination of conditions what is also called logical condition triggered or ii) a sequence of events during execution (Figure 1.3a). In case the Trojan is activated after a sequence of events, these occurrences can be based on i) a physical condition like the input of the user or a change on the activity of the circuit like rising the temperature of the system; or ii) time-based .

Based on how Trojans affect the execution of the system (Figure 1.3b), they can perform two different actions: i) change the intended functionality or ii) steal information . Changing the functionality of the circuit includes: i) returning a non-desire output, ii) including a delay on the system, iii) a bridging fault that connects two signals of a system to output the dominant signal, iv) changing the operational activity like consuming more power what could drain the battery of the device or v) denying the service (DoS) where the chip will stop running . Information-stealing attacks can be applied using a side channel attack to get through this external circuit relevant information without notifying the user or by reading *sensitive* content from memory.

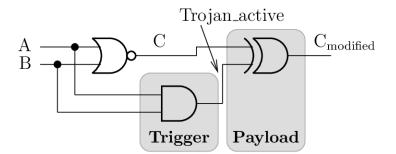

Figure 1.4 shows an example of a hardware Trojan characterise as a combinational triggered - after a combination on the inputs A and B that change the original output C.

Figure 1.4: Example of a functional hardware Trojan[9]

Hardware Trojans are usually difficult to detect as they hide in the circuit, they trigger on a specific unknown condition and they can affect the circuit in different ways. Moreover, as devices are becoming smaller and more complex, it is difficult to detect them. Additionally, millions of chips are fabricated and it is not possible to test all these chips one by one to ensure they do not include any hardware Trojan.

## 1.2 Differential Fault Analysis (DFA)

DFA attacks are applied to cryptography circuits as a type of side channel attacks to steal sensitive information such as the encryption key [27]. DFA is based on injecting maliciously erroneous values into a cryptographic circuit while it is in execution multiple times and then collecting all these incorrect outputs to analyse them and infer secret information like the internal state of the system or cryptographic keys. This attack is denoted as a white-box attack because the attacker has access to the target code and it can manipulate it to interfere on the execution using developer tools such as debuggers or emulators[56]. An example of how DFA works on the Advanced Encryption System (AES) algorithm is shown in figure 1.5. The attacker injects a fault in a certain bit and knowing which operations are done to calculate the output of the cryptographic algorithm it can determine which bits will change from the original output as it shows subfigure 1.5a. Additionally, from the output with faults, the correct output and knowing where the errors were injected, along with an analysis of the algorithm behaviour it can be determined some certain subkeys of the algorithm that will lead to discovering the cipher key (Subfigure 1.5b).

(a) Analysis of how the output changes based on the input in AES[15]

| Output with faults |    |    |    | Output without fault |    |    |    | Error |   |               |    |    |    |

|--------------------|----|----|----|----------------------|----|----|----|-------|---|---------------|----|----|----|

| DE                 | 02 | DC | 19 | ]                    | 39 | 02 | DC | 19    |   | $\mathbf{E7}$ | 00 | 00 | 00 |

| 25                 | DC | 11 | 3B | $\oplus$             | 25 | DC | 11 | 6A    | = | 00            | 00 | 00 | 51 |

| 84                 | 09 | C2 | 0B | ]                    | 84 | 09 | 85 | 0B    |   | 00            | 00 | 47 | 00 |

| 1D                 | 62 | 97 | 32 | ]                    | 1D | FB | 97 | 32    |   | 00            | 99 | 00 | 00 |

(b) Erroneous output based on a fault injection [13]

Figure 1.5: Example of a Differential Fault Analysis attack on AES

DFA has been demonstrated to be a very effective attack technique as it allows the attacker to choose which faults to inject and at which place in the circuit to insert them. Also, because it can attack several cryptographic algorithms like the symmetric key algorithms AES[15] or RSA[11]. The attacker just needs to know how the cryptography algorithm behaves to calculate the amount of insertion to do and the analysis to be done from the collected data to get the secret key. But, even if the cryptography algorithm is not known by the attacker doing multiple executions with different injections can help the attacker by analysing the output of how the algorithm behaves and steal secret information based on that[11].

## 1.3 Objectives of this thesis

The main objective of this thesis is to implement a method at the HDL level to detect hardware Trojans changing the system functionality and DFA attacks on cryptographic algorithms. The implemented residue checker should be able to detect security attacks extending the application of this technique to security from the original soft-error detection [37]. This method should be as general as possible to be applied to multiple types of cryptographic algorithms such as symmetric-key algorithm and hash functions.

Another goal of this project is to measure the coverage, cost, and impact of the method proposed. Consequently, it will be evaluated the overhead in area, energy consumption and performance impact on an FPGA substrate.

# 2. State of the art

This chapter shows an overview of the recent research done to detect hardware attacks. In concrete, it focuses on the two attacks this thesis faces that are hardware Trojans and DFA. There is also a synopsis about the work done related to residue checking and the fields in which residue checking was already applied.

This chapter concludes with the progress beyond the state of the art of this thesis.

## 2.1 Techniques to detect hardware Trojans

Over the last years, several kinds of techniques have been presented that detect a certain type of hardware Trojans. These proposals can be classified in four different techniques to detect Trojans: i) side channel analysis, ii) logic testing iii) machine learning and iv) formal methods. However, there are other proposals on the literature such as runtime methods, reverse engineering and Trojan activation methods[7].

Side channel analysis techniques measure non-functional properties of the manufactured chip in operation such as power consumption, leakage, temperature, delay or electromagnetic radiation and compare these values with the ones from the trusted design or manufactured chip. This technique is not good for small circuits as it is susceptible to experimental and process variation noise.

Logic testing is based on triggering a rare event on various internal nodes and propagate it to an output node to observe its effect. This method is not affected by process variation and noise effects but it has the difficulty to define correctly the test vector for that reason is a good option for small circuits.

Machine learning techniques study elements on the circuit such as netlists in order to detect Trojan features and then perform the detection task effectively based on the learned patterns during the circuit analysis phase.

Formal methods verify the design of a circuit to fulfil all the requirements specified. These methods are applied to the pre-synthesised hardware designs.

### 2.1.1 Side channel analysis techniques

Atieh Amelian and Shahram Etemadi Borujeni[3] present a method based on side-channel analysis to detect hardware Trojans measuring path delay. The method does not modify the target circuit and it can be applied to test the IC after its manufacturing. The method calculates the delay on a set of selected paths of the circuit and then comparing the expected delay of the Trojan-free design with the delay on the same paths of the manufactured IC it can decide if any hardware Trojan has been inserted during fabrication. This method detects more than 80% of Trojans using a configuration of 20 paths with an accuracy of 0.01 ns. Nguyen, Luong N., et al.[38] propose to use backscattering (i.e. the reflection of signals back to their original direction) for hardware Trojan detection as this signal can provide information about the ongoing state of a system. The goal of the paper is to can detect dormant Trojans (i.e not active Trojans) on circuits to determine possible malicious modifications on ICs without needing to identify the activation condition from the many possible triggers. The proposal is evaluated along with cross-training using the Trojan-free design three different Trojans from TrustHub[41] that leak information or do a DoS attack. Evaluation results show that all three cases have been correctly detected the Trojan.

Hossain, Fakir Sharif, et al. [22] specify three detection methods based on a side-channel analysing power consumption. One of the methods is a modification of scan segmentation methodology[23], previously proposed by the authors. Another method is Equal-Power Self-referencing (EP) that obtains gating points with EP from the design and then it applies the detected EP patterns and measures the generated currents individually. The third method proposed is Equal-Power Neighbouring self-referencing (EPN) and it tries to improve detection sensitivity on circuits with many process variations. The system is evaluated by inserting two different Trojans from TrustHub[41] into an AES without altering the original layout of the circuit. The results obtained differ from one circuit and another giving better results the EPN algorithm in all the tested cases.

## 2.1.2 Logic testing techniques

Amin Bazzazi et al.[7] define a way to localise hardware Trojans based on the logical values of nodes at runtime combining logic testing and runtime techniques for hardware Trojan detection. The method analyses the circuit and obtains a set of nodes with the greatest similarity on their logical values. Then, it compares the values of these nodes with the ones from the known non-manipulate circuit to detect if the evaluated circuit includes hardware Trojans. The proposal detects more than 80% of the Trojans on the evaluated circuits increasing the power consumption a 13% and the area a 15% from the initial value.

Huang, Yuanwen, Swarup Bhunia, and Prabhat Mishra[24] propose a method to generate efficient test vectors to detect hardware Trojans using side-channel analysis. The generated test vectors maximise the switching activity of the inserted Trojans while it minimises the switching activity in the rest of the circuit to make easy hardware Trojan detection applying side-channel analysis. Their proposals improve the Trojans detection with side channel analysis by more than 96%.

Salmani, Hassan, Mohammad Tehranipoor, and Jim Plusquellic[48] present a technique to raise the hardware Trojan activity inserted on a circuit and, consequently, decrease the activation time of these Trojans facilitating its detection. Hardware Trojan detection is improved based on an analysis of the circuit modelling the transitions on the system and the number of clock cycles with a geometric distribution. Additionally, they prove that the insertion of dummy flip-flops on the circuit can help on increasing transitions what also grows Trojan activation.

### 2.1.3 Detection applying machine learning techniques

Hasegawa, Kento, Masao Yanagisawa, and Nozomu Togawa[20] describe a machine learning based hardware Trojan classifier detecting Trojans nets inserted at gate-level during in ICs design. The system is tested on hardware Trojans from TrustHub[41]. All the Trojans evaluated produced a denial of service attack and are triggered based on timing or physical conditions. The evaluation shows that they are able to determine Trojan nets with 92.2% of precision and 74.6% of F-measure.

Yoon, Junghwan, et al.[58] introduce a technique to detect hardware Trojans in FPGAs doing a statistical analysis by applying machine learning. The analysis is done in a forward and backward direction. Forward analysis directly analyses the netlists at a synthesis phase while backward analysis checks the circuit reversely from bit streams. Multiple aspects are proposed to be considered in the synthesised design to detect hardware Trojans such as vectorized boolean equation of the LookUp Tables (LUTs), number of LUT's input pins, type of LUT's output pins, number of LUTs and nets from input and output pin to the Input/Output Blocks (IOB), number of LUT that affect the output. This technique is described to be promising based on other results applying their detection tool but there are no results given regarding hardware Trojan detection.

#### 2.1.4 Detection applying formal verification methods

J. Rajendran, A. Dhandayuthapany, V. Vedula and R. Karri[45] proposes a formal verification method to detect hardware Trojans inserted on third-party IPs and its trigger condition. This technique can detect hardware Trojans leaking sensitive information from the circuit by applying model checking techniques. In order to apply its proposal needs to have a temporal logic description of the design. This mechanism detects Trojans as long as the leakage of information is inside the number of clock cycles analysed.

Xiaolong Guo, Huifeng Zhu, Yier Jin and Xuan Zhang[18] describe a technique that it formally verifies a circuit to expose leakage paths at the circuit level. This technique uses information flow tracking methods to understand how the information in the circuit flows and allowing to successfully detect Trojans or other vulnerabilities in the system.

Jonathan Cruz, Farimah Farahmandi, Alif Ahmed and Prabhat Mishra[12] explains a technique that detects hardware Trojans by analysing the design based on combining automatic test pattern generation method and model checking.

## 2.2 Techniques to protect against DFA attacks

DFA attacks seem to be a very effective attack against ciphers. In the literature, several countermeasures have been proposed based on redundancy. These proposals can be categorised based on the where they are implemented that it can be i) a dedicated device detecting or blocking the attack, ii) modifications on the circuit computation, and iii) protocol level solutions that defining new algorithms in which there is a low probability of fault .

This section focuses on the last proposals shown in academia to protect circuits against DFA attacks.

#### 2.2.1 Protection based on external devices

He, Wei, Jakub Breier, and Shivam Bhasin describe a detection logic to protect systems against fault injection attacks using a laser to inject the faults. The proposal uses a high-frequency digital Ring-Oscillator watchdog and a disturbance sensor. Their results indicate that 94.20% of fault attacks tested on ciphers can be detected [21].

#### 2.2.2 Protection based on code modifications

Indrani Roy et al. define a framework to detect sensitive points of a block cipher design and fix these points based on the cipher specification and a set of security requirements. The implementation is based on the fact that cryptographic algorithms have different vulnerability depending on the point the faults are inserted and trying to protect these more critical locations. The evaluations is done on three cryptographic algorithms i) AES, ii) CAMELLIA and iii) CLEFIA giving a fault coverage between 50% and 100% depending on the online security margin chosen[47].

## 2.2.3 Protection based on new protocols

Christof Beierle et al. present a new lightweight cryptography algorithm secured against DFA attacks. Lightweight ciphers pretend to provide efficient cryptography algorithms with some of these algorithms are based on well-known symmetric algorithms. In concrete, this proposal follows the structure of AES to define its encryption and decryption scheme[8].

Baksi, Anubhab, et al. propose a protocol strategy that ensures faults are inserted into some part of the block cipher plain text instead of an intermedium cipher value increasing the difficulty to obtain information from a DFA attack. Additionally, this technique can be easily applied to standard ciphers such as AES[6].

## 2.3 Residue checking

Residue checking is based on the mathematical properties of integer modular arithmetic. Addition, subtraction and multiplication operations with integers follow this property (2.1).

$$((a+b) \mod N) \equiv (a \mod N) + (b \mod N) \tag{2.1}$$

This concept was originally applied to adder circuits[43] by W. W. Peterson in 1957 with the objective of detecting failures on components. Residue checker components allow to protect arithmetic circuits using a smaller quantity of additional hardware as the operations can be replicated with a smaller amount of bits than the original operation but getting the same protection results thanks to this property.

Since then, many other papers have been written following the original idea of protecting arithmetic modules such as adders or ALUs[39] but there are also other proposals focusing on other areas like soft-error detection[40].

### 2.3.1 Application of residue checker in the last years

Daniel Lipetz and Eric Schwarz propose the use of residue checker for decimal floating-point units protecting the two values representing the float one in base 10 and the other in base 2. They also give a discussion on the coverage obtain depending on the modules selected to protect the circuit[31].

Shugang Wei presents an improve version of residue checker for Multiply–accumulate operations with signed-digits. The calculation of the correction with residue checker is used using a tree structure. No concrete values on the coverage are given but they analyse a set of configurations indicate the best one based on coverage and area utilisation [53].

Stanisław J. Piestrak and Piotr Patronik explain their proposal to protect against faults digital finite input response (FIR) filters. FIRs are a kind of filters use for Digital Signal Processing. Their implementations show a 100% coverage of errors with only a 3% increase on area[44].

## 2.4 Novelty of this thesis

This thesis proposes a novel method to detect attacks on cryptographic systems. As far as we know, residue checking has never been used in the area of security to detect any kind of attack including the two attacks this thesis focus on that are hardware Trojan and DFA attacks.

Hardware Trojans are still an issue on real circuits as subsection 2.1 has detailed. Most of these articles based on the detection of any kind of hardware Trojans such as information stealing which is an objective of this thesis. The proposed detection technique varies from invasive and non-invasive methods so our proposal based on an invasive method is a valid approach at the moment. Even though the main objective in security area is protected, most of this methods not only centre its attention on giving a good detection result but also to minimise the area overhead. For that reason, our goal is to implement an attacks detection mechanism which overhead is as minimum as possible.

DFA attacks are one of the main threats to cryptographic circuits these days. Section 2.2 presents various techniques to detect them and protect the circuits against them, but there are recent papers describing new effective and efficient DFA attacks. Consequently, it is of utmost importance to contribute with new detection mechanism to this type of attack. Most of the papers reviewed in section 2.2 focus on AES unpatent cryptographic algorithm and other proprietary ciphers such as CAMELLIA from Mitsubishi electrics and NTT; or CLEFIA from Sony. However, there are many other standard cryptographic algorithms such as RSA and SHA mostly used nowadays[16] but which protection has not been investigated as much in the last years.

In conclusion, hardware Trojans and DFA attacks are still a threat to ICs so new techniques must be proposed to protect these systems against them. For that reason, the proposal of a novel method to detect them as this thesis can contribute to reduce the impact of hardware attacks on the security area.

# 3. Methodology

This chapter defines the method used to implement and evaluate the proposal of this thesis including how the target attacks were chosen, the tools used and the steps followed on the implementation and evaluation. It also includes theoretical values of the level of protection that the approach should give based on the attack and why.

# 3.1 Implementation

## 3.1.1 Initial decisions and stages of implementation

The first step on the implementation was to decide the attacks to target. We defined the initial target of this thesis was to detect hardware Trojans which payload changes somehow the functionality of the system. And, after that, it was extended to also detect other attacks affecting the values on the signals of the circuit, in concrete, DFA attacks.

Along with the attacks to detect, the cryptographic algorithm to protect were also selected. This decision was made based on the benchmarks provided by TrustHub[41] that had already some algorithms with Trojans. TrustHub provides benchmarks for two cryptographic algorithms AES and RSA. So, these two algorithms were chosen to protect them and also the hash function SHA-1 as we had already a design of a cryptographic accelerator implementing this algorithm and even though this algorithm is not secure anymore[5] it was chosen as it was still supported for digital signatures[2, 35] and also as its operation are quite similar to other versions of SHA so it can be used to probe the concept.

Once the target attacks and cryptographic algorithm were chosen, the residue checker mechanism and other modules needed were implemented and tested for the algorithms. Residue checker was not done straight forward as not all the algorithms use arithmetic operations supporting modular arithmetic but bitwise operations that do not follow these properties so some modifications to our residue checker were applied. More details on how the residue checker mechanism has been adapted to the algorithms, the defined modules and its insertion in the ciphers original design are described in the following section 4.

## 3.1.2 Development tools

The only tool used for the implementation was an Integrated Development Environment (IDE) from Xilinx called Vivado Design Suite[57]. This decision was taken from the many possible IDEs supporting HDL because we already know how to use it from previous projects and work. Another point why it was chosen is because it is a very complete tool that allows coding through the interface checking the syntax errors and simulation to can corroborate that the design is correct.

## 3.2 Evaluation

### 3.2.1 Initial decisions and stages of evaluation

The first step on the evaluation once the implementation was finished was to verify the system under hardware Trojans and DFA attacks.

Hardware Trojans to detect were taken from a set of TrustHub's benchmarks previously modified to include our residue checker. Our residue checker was not applied to all the available benchmarks as it has a limitation that it can only detect hardware Trojans that change the functionality. So, side channel attack Trojans could not be detected.

The detection of DFA attacks was done by simulating the detection of changes on the registers of the design. This was done by defining a testbench for each one of the evaluated systems and performing the simulations of them.

Then, other metrics were measure, in concrete, area, energy consumption, and the maximum frequency of operation. All these metrics were measured after performing the synthesis of the design on a certain FPGA model. Another measure done was to check if the integration of residue checker on the circuit affects the critical path of the original system to see if the performance, in terms of time, is degraded.

Evaluation details about how the simulations and the metrics have been executed are described on section 5 along with the results obtained for each one of the assess metrics.

#### 3.2.2 Evaluation tools

The tool used for the evaluation was the same one as for the implementation, Vivado Design Suite [57]. This tool includes a simulator, and it also allows to synthesise and implements a design on a certain FPGA. Additionally, it provides automatic metric's calculation of the design after its synthesis or implementation such as power consumption, area utilisation and timing constraints. One disadvantage of this tool is that the software is proprietary so some FPGAs and options are only available using the correspondent unlimited license or using a free trial license that gives you 30 days of free use.

# 4. Development of the proposal

This chapter explains in detail all the steps involved in the implementation of the proposal that was summarised on the previous section 3.1. These steps include how the modules for detection and insertion of faults has been implemented, the constraints and limitations that the proposal has, how these limitations affect the system, and how the proposal has been specifically applied to each of the cryptographic algorithms.

# 4.1 Analysis and re-organisation of the cryptographic cores

Once the cryptographic algorithms were selected, they had to be analysed to learn how each one of the algorithms behaves and which is the purpose of the different signals in the design to define which ones can be protected and how to apply the residue checker mechanism to them.

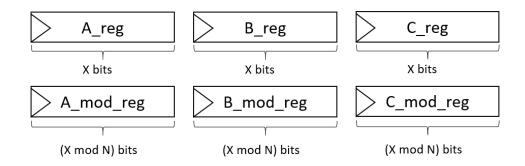

For each one of the algorithm, all the signals were classified between control signals and operational registers. Control signals indicate to the system how to perform and are usually composed of a small number of bits, mainly only one bit. For that reason, control signals were not our focus of protection as they had to be completely replicated and also because there are usually not a focus of attacks as they are commonly implemented as wires, not on storage element where faults can be captured. Operational registers are used to keep the partial calculation of the cipher algorithm. The value of registers is usually a set of bits, in the cases of the algorithms selected, most of the registers have a size of 32-bits or more. Additionally, faults can be visible and propagated through them over the calculations. Consequently, all the registers from the algorithm are a possible candidate for protection. Ideally, all registers of the systems should be protected but there were some issues, that is explained in subsection 4.1.1, forbidding.

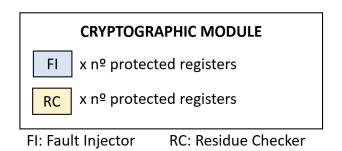

After the analysis, we inserted the extra modules needed to implement and evaluate the fault-detection mechanism. The two modules inserted are the proposed version of the residue checker mechanism to protect the circuit, and a fault-injector module to can verify the correct operation of the fault-detection mechanism that it is our implementation of the residue checker (Figure 4.1). Both modules are explained in detail on the following subsections 4.1.1 and 4.1.2.

Figure 4.1: Modules inserted within the cryptographic module design

#### 4.1.1 Residue Checking and Rotary Residue Checking

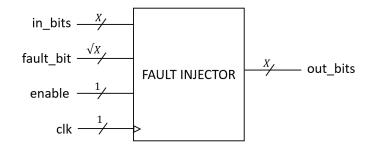

Residue checking is applied to each one of the operations with registers that can be protected. This technique is applied in two phases: i) protection and ii) check. The protection part is base on defining additional registers with the modulo value of each one of the registers, calculating in parallel the value of the original register and the modulo registers through the algorithm. The check part is based on checking the equality of modules (2.1). If there is an inequality detected this means that there could be a fault injected on that operation (Figure 4.2).

Protection phase: Calculate operations based on the module

A = B + C $A_mod = B_mod + C_mod$

# <u>Check phase</u>: Corroborate that the operations are not attacked if ((A mod N) $!= A_{mod} \rightarrow ERROR !$

Figure 4.2: Explanation of the residue checker mechanism

The explained residue checker is based on a property that can only be applied to certain arithmetic operations. For that reason, the operation types used in each one of the algorithms have to be taken into account because depending on the kind of operation residue checker cannot be directly applied as not all operations follow the same properties.

Two of the chosen algorithms, SHA-1 and AES, use bitwise operations and permutations while RSA is mostly based on additions and subtractions. Bitwise operations and permutations change the output in a way that the modular arithmetic property use in residue checker is not fulfilled. For that reason, it is not possible to apply straightforward the residue checker concept to those two algorithms. Therefore, residue checker for these SHA-1 and AES can only be applied to bitwise operations (4.1), not to permutations, with the limitation of only using power-of-two values for the module depicted as N in (4.1).

$(a \ AND \ b) \ mod \ N \equiv (c \ mod \ N) \equiv (a \ mod \ N) \ AND \ (b \ mod \ N) \ for all \ N \ in \ 2^n \ (4.1)$

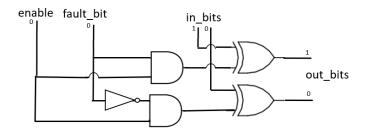

This limitation on residue checker reduces its performance as the use of power-of-two values for the module is like just protecting the N last bits of each register leaving the other most significant bits unprotected. This does not happen using odd values for the module as the remainder is calculated based on all the bits of the register. As a result of this limitation, an alternative version of residue checker has been proposed for these cases that we have called the rotary residue checker.

The Rotary residue checker is based on the same principle of the residue checker applied to power-of-two modules but including a rotation mechanism to change the bit that will be protected after a predefined number of cycles. Figure 4.3 shows visually how the rotary residue checker behaves by protecting a different set of bits depending on the execution cycle. The picture shows the simplest of the condition to update the bits to protect that is just adding N to the initial bit index and resetting these values when needed the more significant bits has already protected. This condition fits if the module value, N, is multiple of the total number of bits that the original register has, X. However, in case N is (X/2) + 1, one bit more than the original size of the register then the most significant will be always unprotected. This case has been taken into account on the implemented rotary residue checker, but it is not depicted to simplify the pseudo-code of the picture.

Protection phase: Calculate operations based on the module

A = B OR C A\_mod = B\_mod OR C\_mod If (timeToChangeBits == true) A\_mod = A((iniBit + N - 1)..iniBit) B\_mod = B((iniBit + N - 1)..iniBit) C\_mod = C((iniBit + N - 1)..iniBit) If ((iniBit + N) < X)  $\rightarrow$  iniBit = iniBit + N

Else  $\rightarrow$  iniBit = 0

<u>Check phase</u>: Corroborate that the operations are not attacked If (A((iniBit + N - 1)..iniBit) != A\_mod) → ERROR !

Figure 4.3: Explanation of the rotary residue checker mechanism

### 4.1.2 Fault injector

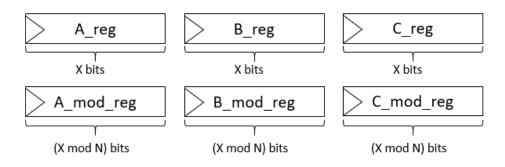

The fault injection module is designed to return an output value based on its input with a certain bit change on it. In concrete, the fault injection component defined is based on the following specification (Figure 4.4).

Figure 4.4: RTL schematic of the fault injector component

The control input signals are the clock to update the output only at the rising edge of the clock, and an enable signal that allows activating the fault injector or just let the input go by. The other two inputs are the input value to be attacked and an input position to know where to insert the fault. The output value of the module behaves differently based on the enable signal. If the enable signal is activated, the output is the input value with the bit on the indicated position flipped. In case it is deactivated, the output is the input value with no modifications. Figure 4.5 shows a simplified internal representation of the fault injector in case the input signals has a size of 2 bits.

Figure 4.5: Internal design based on logic gates of the fault injector component for an input of size 2 bits

This component is used to test that the fault-detection mechanism behaves as it was defined. This fault injector is instantiated multiple times on each design, specifically, there is one instance one for each of the values protected.

The injector has been designed on a parameterized way to enable its use for different input sizes. Additionally, it is as simple as possible and it can easily be extended or changed. For this reason, it only flips one of the bits in the input signal and it inserts the fault when it enables instead of having an extra signal indicating the time. This control of the time when the fault is inserted is done outside this component and it is further explained in the evaluation section 5.

# 4.2 Protection of RSA applying residue checking

## 4.2.1 Algorithm

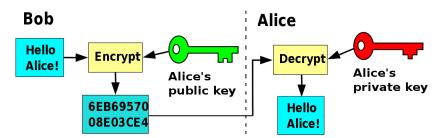

RSA is a cryptographic algorithm named after its designers Rivest, Shamir and Adleman. This cryptosystem was originally presented as one of the first asymmetric algorithms for cryptography in 1977[46]. Unlike symmetric cryptography algorithms, where the same secret key is used for encryption and decryption, asymmetric algorithms make use of two different types of keys i) a public-key and ii) a private key (Figure 4.6). The public key is used for encryption and it is shared between other users so messages are encrypted with the public key of the receiver. The private key is used for decryption and it is known only to the owner keeping the secret of the encrypted message to the receiver.

Figure 4.6: Encryption/Decryption scheme in asymmetric cryptography

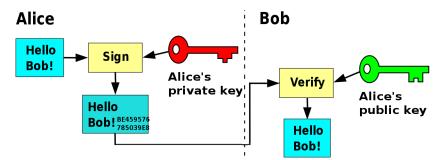

This kind of cryptographic algorithms can also be used for digital signatures (Figure 4.7) in which keys are applied the other way around, a message is signed with the private key of the sender and is verified with the public key of the sender.

Figure 4.7: Digital signature scheme in asymmetric cryptography

RSA encryption(4.3) and decryption(4.4) need to perform just two operations, but the operational complexity of these operations is as costly as the factoring problem. So the security of the algorithm remains unbroken until factoring problem could be rapidly solved for large numbers.

The operations applied in RSA involve three large positive integers: i) the encryption key e, ii) the decryption key d, and a number use as a part of the public or private key depending on the operation n. There is not restriction for e and d but n must be value such that  $0 \le m \le n$  where m is the value of the message to encrypt. Such that for all the previously described integers the following equation holds:

$$(m^e)^d \equiv m \bmod n \tag{4.1}$$

$$\left(m^d\right)^e \equiv m \bmod n \tag{4.2}$$

The previous values e, d and n involved in the computations cannot be any value but they have to be calculated based on the following rules.

- 1. n is obtained as the product of two very large randomly chosen prime numbers p and q

- 2. e can be chosen as any value following  $1 \leq e \leq \lambda(n)$  where  $\lambda$  represents the Carmichael's function[14].

- 3. d is computed based on n and d following this equation  $d = \frac{1 \mod \lambda(n)}{e}$

Encryption operation is calculated given a plaintext m as:

$$c = m^e \bmod n \tag{4.3}$$

Decryption operation does the same as (4.3) for the encryption but applying the power of the encrypted message to the decryption key:

$$m = c^d \bmod n \tag{4.4}$$

### 4.2.2 RTL implementation of the original algorithm

As the previous subsection 4.2.1 defines, RSA is based on a modular exponentiation operation. In order to compute efficiently, this operation square-and-multiply algorithm is used in the original RTL design of the RSA algorithm that we will protect with residue checker.

Square-and-multiply also called exponentiation by squaring or binary exponentiation, the method examines the bits of the exponent to determine which powers are computed and then it divides the operations in powers of two and multiplications (4.5).

$$x^{n} = \begin{cases} x \left(x^{2}\right)^{\frac{n-1}{2}}, & \text{if } n \text{ is odd} \\ \left(x^{2}\right)^{\frac{n}{2}}, & \text{if } n \text{ is even.} \end{cases}$$

(4.5)

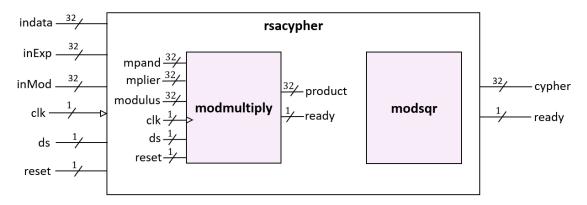

The RTL of the RSA algorithm to modified was taken from the Trojan benchmarks' code BasicRSA-Tx00 in TrustHub[41]. The design of this code is done in VHDL and follows the following scheme represented in figure 4.8. In the depicted schema from figure 4.8, each block represents a VHDL component and its instances are represented within a block. The input/output signals of the *modsqr* block are not drawn for simplicity, but it has the same inputs/outputs as the *modmultiply* block as they both instantiate the same component.

Figure 4.8: RSA schema of the components from the original RTL

The *rsacypher* is the main module receiving the plaintext or encrypted text in *indata*, the encryption or decryption key in *inExp*, the module in *inMod* along with some control signals. This module controls the modular multipliers across the value it pass them, and it collects the results they return.

The *modmultiply* and *modsqr* blocks instantiate the modular multiplier component and they use it to produce products and to take care of squaring operations, respectively. These blocks are the ones actually computing RSA. For that reason, most of the register protected in this design are included inside this component.

```

1 product = prodreg4

2 if (mpreg[0] == '1')

prodreg1 = prodreg + mcreg

3

4 else

prodreg1 = prodreg

5

6 // Subtract modulus and subtract modulus * 2

7 prodreg2 = prodreg1 - modreg1

8 prodreg3 = prodreg1 - modreg2

9 // Negative results mean that we subtracted too much

10 modstate = prodreg3(mpwid+1) & prodreg2(mpwid+1);

11 // Select the correct modular result and copy it

12 if (modstate == '11')

prodreg4 = prodreg1

13

14 else if (modstate == '10')

prodreg4 = prodreg2

15

16 else

prodreg4 = prodreg3

17

18 \ // \ Subtract the modulus from the shifted multiplicand

19 mcreg1 <= mcreg - modreg1;</pre>

20 // Select the correct modular value and copy it.

21 if (mcreg1(32) == '1')

22

mcreg2 = mcreg

23 else

24

mcreg2 = mcreg1

```

Listing 4.1: Main operations of RSA within the modular multiplier component

Listing 4.1 shows the internal signals use in the modular multiplier components and the main operations applied to calculate RSA. These signals are controlled by the bits of a multiplier and a multiplicand values based on the *indata* signal of the *rsacypher* that represents the message to encrypt/decrypt.

The modular multiplier operates under the Shift-and-Add algorithm to efficiently multiply integers as the square-and-multiply algorithm requires. The algorithm first shifts the multiplicand (i.e. *mpand*) value for each bit of the multiplier (i.e. *mplier*) storing these values in *mcreg*. Then for each bit of the multiplier which value is one, the shifted multiplicand is added to the product as operation in line 3 shows in listing 4.1. Subtractions are computed to make sure the product is always expressed as a remainder, lines 7 and 8 in listing 4.1. The most significant bits of these subtractions, line 10 in listing 4.1, are used to the value of the product, lines 12 to 17. The algorithm ends after going across all bits set to one in the multiplier.

## 4.2.3 Modifications to the design

RSA operations allow applying the original definition of residue checker to any module as explained in the previous subsection 4.1.1.

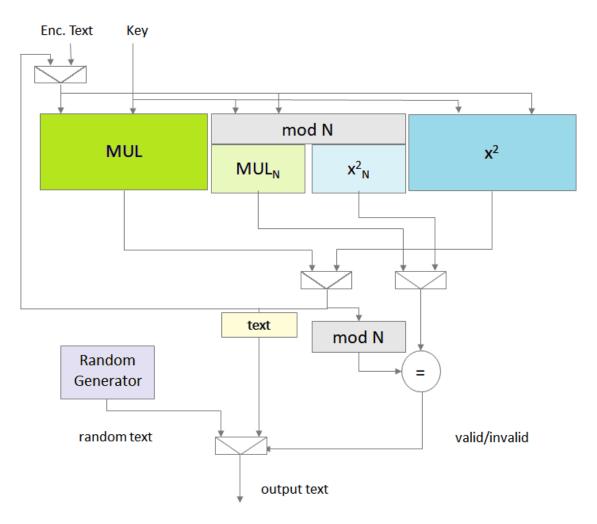

The protection mechanism of the operations is based on duplicating the signals of the original algorithm and applied the same operations based on the modules (Listing 4.2). These have been done by partially duplicating the functionality of the algorithm but with a much smaller amount of signals and bits per signal. A block representation of these changes on the design is shown in figure 4.9.

Figure 4.9: RSA schema of the modifications added to the original design

In spite of the operations following the modular-arithmetic properties, there are some issues to take into account when they have to be protected like the possible negative results of a subtraction solved like in lines 7 to 10. Additionally, there are some signals that can not be calculated from the replicated modules, lines 35 to 43. The module has been calculated based on the operations that VHDL provides for the modulo (mod) and the remainder (rem).

```

1 // ------ Protection of signals with residue checker ------

2 if (mpreg(0) == '1')

3 prodreg1_rc = (prodreg_rc + mcreg_rc) mod MOD_VALUE

4 else

5

prodreg1_rc = prodreg_rc

6

7 if (prodreg1_rc >= modreg1_rc)

8 prodreg2_rc = (prodreg1_rc - modreg1_rc) mod MOD_VALUE

9 else

10 prodreg2_rc = (MOD_VALUE + (prodreg1_rc - modreg1_rc))

11

12 if (prodreg1_rc >= modreg2_rc)

13 prodreg3_rc = (prodreg1_rc - modreg2_rc) mod MOD_VALUE

14 else

15

prodreg3_rc = (MOD_VALUE + (prodreg1_rc - modreg2_rc))

16

17 if (modstate == '11')

18 prodreg4_rc = prodreg1_rc

19 else if (modstate == '10')

20 prodreg4_rc = prodreg2_rc

21 else

22 prodreg4_rc = prodreg3_rc

23

24 if (mcreg_rc >= modreg1_rc)

25 mcreg1_rc = (mcreg_rc - modreg1_rc) mod MOD_VALUE

26 else

27

mcreg1_rc = (MOD_VALUE + (mcreg_rc - modreg1_rc));

28

29 if (mcreg1(32) == '1')

30 mcreg2_rc = mcreg_rc

31 else

32 mcreg2_rc = mcreg1_rc

33

34 // Copy values from the original algorithm for mcreg and mpreg as use division

35 if (signed(mcreg) >= 0)

36 mcreg_rc = (signed(mcreg) mod MOD_VALUE)

37 else

mcreg_rc = (((signed(mcreg) rem MOD_VALUE) + MOD_VALUE) mod MOD_VALUE)

38

39

40 if (signed(mpreg) >= 0)

41 mpreg_rc = (signed(mpreg) mod MOD_VALUE)

42 else

43

mpreg_rc = (((signed(mpreg) rem MOD_VALUE) + MOD_VALUE) mod MOD_VALUE);

```

Listing 4.2: Pseudo-code of the protected operations of RSA within the modular multiplier component

The verification of the signals values to corroborate that there is no change on the circuit operation is shown in listing 4.3. All signals can be verified to check if there is an error. However, as the algorithms iterates over all values and all the modifications pass through the last signal (i.e. *prodreg4*) the checks can be limited to that signal reducing the overhead in the hardware of this protection mechanism.

```

1 // ------ Verification of signals with residue checker ------

2 if(prodreg4_mod != prodreg4_rc) -> ERROR!

3 if(prodreg3_mod != prodreg3_rc) -> ERROR!

4 if(prodreg2_mod != prodreg2_rc) -> ERROR!

5 if(prodreg1_mod != prodreg1_rc) -> ERROR!

6 if(prodreg2_mod != prodreg2_rc) -> ERROR!

7 if(modreg2_mod != modreg2_rc) -> ERROR!

8 if(modreg1_mod != modreg1_rc) -> ERROR!

9 if(mcreg2_mod != mcreg2_rc) -> ERROR!

10 if(mcreg2_mod != mcreg2_rc) -> ERROR!

11 if(mcreg1_mod != mcreg1_rc) -> ERROR!

12 if(mcreg_mod != mcreg1_rc) -> ERROR!

13 if(mpreg_mod != mcreg2_rc) -> ERROR!

```

Listing 4.3: Pseudo-code of the verification of signals using residue checker in RSA within the modular multiplier component

The *rsacypher* module has been also protected even though most of its signals are one-bit signals used to control the flow of the algorithm. No code is shown as it follows the same mechanism shown in listing 4.2 and 4.3 for verification.

# 4.3 Protection of SHA applying residue checking

## 4.3.1 Algorithm

SHA is a cryptographic hash function which initials stands for Secure Hash Algorithm. SHA has multiple variants of the same algorithms changing the size of the keys to encrypt, the construction of the resulting hash and the number of construction rounds it uses making each specific algorithm more or less secure. It has been published by the National Institute of Standards and Technology (NIST) as a U.S. Federal Information Processing Standard (FIPS)[42].

Figure 4.10: Application cryptographic hash functions from the SHA family

SHA function are use for many applications like i) file and messages verification, ii) digital signatures like SSL certificates, iii) password verification or data identifier.

### 4.3.2 RTL implementation of the original algorithm

From all the SHA functions, the RTL design to apply our protection mechanism with residue checker uses SHA-1. SHA-1 generates a hash function with a length of 160-bit and it can be applied to messages with no length restriction. This algorithm has been discovered to be not secure anymore[5] so the standard was no longer approved for most cryptographic applications after that. However, it can be used to probe that residue checker can protect SHA functions against attack as it is explained in subsection 3.1.

SHA-1 algorithm divides the original plaintext into chunks of 512-bits, 64 characters, and iterates eighty times performing bitwise operations and permutations on this chunk. Then, if the initial message is bigger it takes the next chunks and does the same operations but applying the hash value obtained from the previous chunk to the next chunk and so on. The algorithm finish after going through all the chunks producing a single hash value that was a combination of all the iterations over the message.

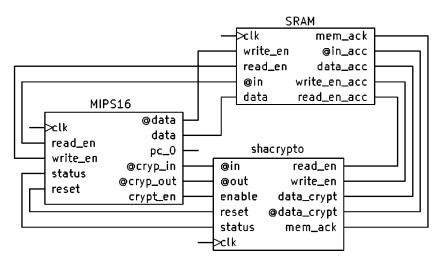

The RTL has been developed as a part of the project in the Processor Design subject from MIRI at UPC. The design of the *shacrypto* component has been based on a pseudo code of the SHA-1 algorithm[55]. The design used (Figure 4.11) is defined based on three main components: i) the cryptographic module called *shacrypto*, ii) a MIPS16 processor (i.e. *MIPS16*) and iii) a main data memory (i.e. *SRAM*). In spite of the three modules, the modifications to protect the design are only done within the *shacrypto* that is the one defining the SHA-1 function.

Figure 4.11: SHA-1 schema of the components from the original RTL

The *shacrypto* component has two input signals from *MIPS16*. There is a *enable* input signal to the module coming from the processor to indicate that the module has to start computing an SHA-1 operation. Another input entry, from the processor to the module, is the address in memory where the data to encrypt is located, *Qin*.

The outputs are the address in memory where the encoded data has been placed, called @*out* in the picture of figure 4.11. Also, there are two signals to indicate if the module wants to read or write from memory called *read\_en* and *write\_en*, respectively. Moreover, there is a one-bit output signal that indicates the end of the encoding process named *done*.

Additionally, the cryptography accelerator is connected with main memory (SROM) by the entries called *data* and @*data* that, respectively, indicate the data to encrypt and the address where this data is located in memory.

The *shacrypto* module instantiates a *pre-processor* that is in charge of applying the initial modifications to raw data received from memory, so as the SHA-1 algorithm can be applied. These modifications are:

These modifications are:

- Append a bit with value one to the raw message.

- Append k zeroes starting from that one bit so that the equation  $l + 1 + k \equiv 448 \mod 512$  is satisfied.

- Append a 64-bit block (l) containing the length of the original message.

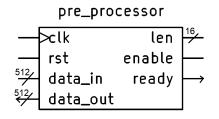

In figure 4.12 the definition of the pre-processing module can be seen. This module is fed with the clock, a reset signal, the length of the raw data, a 512-bit chunk containing the raw data, and finally an enable signal. After one cycle, the module produces the processed data, which is output through *data\_out* and a ready signal.

Figure 4.12: *Pre-processor* component instantiate within the *shacrypto* component

Listing 4.4 describes using a pseudo-code the operations done on the RTL of the *shacrypto* component to perform SHA-1 function.

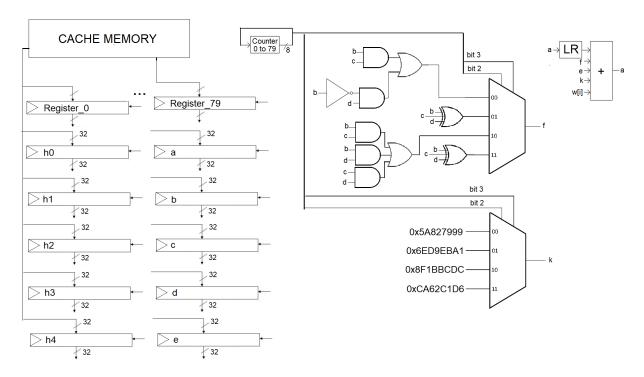

Figure 4.13 shows the components inside the *shacryp* component. This cryptographic component has a cache memory to store the data to be encoded and the hash key. It also has multiple registers, in this case, ninety registers have been defined. The registers contain the data to perform the cryptography encoding and the hash key.

Then, there is a counter to perform the eighty rounds needed by the SHA-1 algorithm. There are four sets of rounds that operate over the values applying different logic functions. For that reason, there are two multiplexers to compute all possible values in parallel and then obtain the correct computed value based on the current round. Finally, the values obtained by the multiplexer and other values from the registers are added to obtain a new value needed on next rounds. In the end, the values of the registers storing a,b,c,d and e are updated as the algorithm indicates. This final storing is not represented in figure 4.13 to reduce the number of connections on the draw.

```

1 for chunk 0 to NUM_CHUNKS

2

for counter_val in 0 to 79

if (counter_val >= 0 AND counter_val <= 19)</pre>

3

4

f = (b and c) or ((not b) and d)

5

k = 0x5A827999

else if (counter_val >= 20 AND counter_val <= 39)</pre>

6

7

f = b xor c xor d

k = 0x6ED9EBA1

8

else if (counter_val >= 40 AND counter_val <= 59)</pre>

9

10

f = (b and c) or (b and d) or (c and d)

k = 0x8F1BBCDC

11

12

else if (counter_val >= 60 AND counter_val <= 79)</pre>

13

f = b xor c xor d

k = 0xCA62C1D6

14

15

16

temp = (a leftrotate 5) + f + e + k + w[i]

e = d

17

d = c

18

c = b leftrotate 30

19

b = a

20

21

a = temp

22

23

if (counter_val == 79) // Save this chunk to the result

24

h0 = h0 + a

h1 = h1 + b

25

26

h2 = h2 + c

h3 = h3 + d

27

28

h4 = h4 + e

29

30 hh = \{a, b, c, d, e\} //Produce the final hash as a 160-bit number

```

Listing 4.4: Pseudo-code of the operations performed by the SHA-1 function

Figure 4.13: Internal overview of the SHA-1 function based on the RTL design

#### 4.3.3 Modifications to the design

The SHA-1 algorithm is mostly composed by bitwise operations (e.g. AND, OR, XOR, NOT) so residue checker cannot be directly applied as this operations do not follow the modular arithmetic properties to can use residue checker for any module. For that reason, as it is explained in subsection 4.1.1 residue checker has been applied using power-of-two modules that it is basically to protect the last n bytes when the module  $2^n$  is used.

Listing 4.5 shows a pseudo-code of the protected operations for SHA-1 where the replicated signals are denoted as the name of the original signals concatenate with the suffix rc. But, these replicated signals has a size of n bits where 0 < n < 32 as the original size of the protected signal is 32 bits.

```

1 for counter_val in 0 to 79

if (counter_val >= 0 AND counter_val <= 19)</pre>

2

f_rc = (b_rc \text{ and } c_rc) \text{ or } ((not b_rc) \text{ and } d_rc)

3

k_rc = 0x5A827999 // Take last n bits of this constant

4

else if (counter_val >= 20 AND counter_val <= 39)</pre>

5

f_rc = b_rc xor c_rc xor d_rc

6

k_rc = 0x6ED9EBA1 // Take last n bits of this constant

7

else if (counter_val >= 40 AND counter_val <= 59)</pre>

8

9

f_rc = (b_rc and c_rc) or (b_rc and d_rc) or (c_rc and d_rc)

10

k_rc = 0x8F1BBCDC // Take last n bits of this constant

11

else if (counter_val >= 60 AND counter_val <= 79)</pre>

12

f_rc = b_rc xor c_rc xor d_rc

13

k_rc = 0xCA62C1D6 // Take last n bits of this constant

14

temp_rc = (a \ leftrotate \ 5) + f_rc + e_rc + k_rc + w[i]

15

16

e_rc = d_rc

d_rc = c_rc

17

18

c_rc = b leftrotate 30

19

b_rc = a_rc

20

a rc = temp

```

Listing 4.5: Pseudo-code of the protected operations executed in SHA-1 function

The code verifying that these signals are correctly protected is shown in listing 4.6. This code is quite similar to the one for the protecting the other cryptographic algorithms (listing 4.3 and 4.12) as it only checks if the protected signals are equal to the protected part from the original signals and if throws an error in case the condition is not satisfied.

| 1 if(a_rc != | a[(MOD_SIZE - 1)0])            | -> ERROR!      |

|--------------|--------------------------------|----------------|

| 2 if(b_rc !: | <pre>b[(MOD_SIZE - 1)0])</pre> | -> ERROR!      |

| 3 if(c_rc !: | c[(MOD_SIZE - 1)0])            | -> ERROR!      |

| 4 if(d_rc !: | = d[(MOD_SIZE - 1)0])          | -> ERROR!      |

| 5 if(e_rc !: | e[(MOD_SIZE - 1)0])            | -> ERROR!      |

| 6 if(f_rc !: | f[(MOD_SIZE - 1)0])            | -> ERROR!      |

| 7 if(k_rc !: | <pre>k[(MOD_SIZE - 1)0])</pre> | -> ERROR!      |

| 8 if(temp_ro | : != temp[(MOD_SIZE - 1        | )0]) -> ERROR! |

Listing 4.6: Pseudo-code of the verification operations executed in SHA-1 function

Additionally, it has also been applied to the design of SHA-1 the rotary residue checker defined in subsection 4.1.1 with the objective of improving the detection rate on this algorithm as the limitation of only using power-of-two in residue checker always keep some unprotected bits and this fact detriments our protection system for cases in which the number of protected bits is very low. The pseudo-code of the rotary residue checker application to protect the operations of SHA-1 function is shown in listing 4.7. The rotary residue checker replicates the operation mostly in the same way it was done without the rotation mechanism that we show in listing 4.5. However, after n rounds the protected bits are changed and due to that, the protected bits must be copied from the original signals before using them.

```

1 K_HASH_ROUND_1_19 = 0x5A827999

2 K_HASH_ROUND_20_39 = 0x6ED9EBA1

3 K_HASH_ROUND_40_59 = 0x8F1BBCDC

4 \text{ K}_HASH_ROUND_60_79 = 0xCA62C1D6

6 for counter_val in 0 to 79

if (counter_val >= 0 AND counter_val <= 19)</pre>

7

8

f_rc = (b_rc and c_rc) or ((not b_rc) and d_rc)

k_rc = K_HASH_ROUND_1_19[(iniBit + MOD_SIZE - 1..)iniBit]

9

else if (counter_val >= 20 AND counter_val <= 39)</pre>

10

f_rc = b_rc xor c_rc xor d_rc

11

12

k_rc = K_HASH_ROUND_20_39[(iniBit + MOD_SIZE - 1..)iniBit]

else if (counter_val >= 40 AND counter_val <= 59)</pre>

13

14

f_rc = (b_rc and c_rc) or (b_rc and d_rc) or (c_rc and d_rc)

k_rc = K_HASH_ROUND_40_59[(iniBit + MOD_SIZE - 1..)iniBit]

15

16

else if (counter_val >= 60 AND counter_val <= 79)</pre>

17

f_rc = b_rc xor c_rc xor d_rc

18

k_rc = K_HASH_ROUND_60_79[(iniBit + MOD_SIZE - 1..)iniBit]

19

temp_rc = (a leftrotate 5) + f_rc + e_rc + k_rc + w[i]

20

21

e_rc = d_rc

22

d_rc = c_rc

c_rc = (b leftrotate 30)[(iniBit + MOD_SIZE - 1..)iniBit]

23

24

b_rc = a_rc

25

a_rc = temp[(iniBit + MOD_SIZE - 1..)iniBit]

26

27

// Copy values when protected bits are rotated after 3 iterations

28

if((counter_val mod 3 == 0) AND (counter_val >= 3) AND (REG_WIDTH > MOD_SIZE))

29

if (rst == 1)

30

new_iniBit = 0

31

else

32

// Take next n bits there are still n or more most significant bits to protect

33

if ((iniBit + MOD_SIZE) < (REG_WIDTH - MOD_SIZE))</pre>

34

new_iniBit = iniBit + MOD_SIZE

35

else // Restart index if the most significant bits were protected on last round

if ((iniBit == (REG_WIDTH - MOD_SIZE)))

36

37

new_iniBit = 0

38

else // Protected the most significant n bits if not protected

new_iniBit = REG_WIDTH - MOD_SIZE;

39

40

// Copy new bits to protect keeping the bits already protected if possible

41

if ((new_iniBit > iniBit) AND ((new_iniBit + MOD_SIZE) == REG_WIDTH)

AND ((REG_WIDTH mod MOD_SIZE) != 0))

42

43

a_rc = {a[REG_WIDTH..(REG_WIDTH-(new_iniBits-iniBits))], a_rc >> (new_iniBits-iniBits)}

44

b_rc = {b[REG_WIDTH..(REG_WIDTH-(new_iniBits-iniBits))], b_rc >> (new_iniBits-iniBits)}

45

c_rc = {c[REG_WIDTH..(REG_WIDTH-(new_iniBits-iniBits))], c_rc >> (new_iniBits-iniBits)}

d_rc = {d[REG_WIDTH..(REG_WIDTH-(new_iniBits-iniBits))], d_rc >> (new_iniBits-iniBits)}

46

47

e_rc = {e[REG_WIDTH..(REG_WIDTH-(new_iniBits-iniBits))], e_rc >> (new_iniBits-iniBits)}

else if ((new_iniBit < iniBit) AND ((REG_WIDTH div 2) > MOD_SIZE))

48

49

a_rc = {a_rc << (iniBit - new_iniBit), a[(iniBit - new_iniBit)..new_iniBit]</pre>

b_rc = {b_rc << (iniBit - new_iniBit), b[(iniBit - new_iniBit)..new_iniBit]

c_rc = {c_rc << (iniBit - new_iniBit), c[(iniBit - new_iniBit)..new_iniBit]</pre>

50

51

d_rc = {d_rc << (iniBit - new_iniBit), d[(iniBit - new_iniBit)..new_iniBit]</pre>

52

53

e_rc = {e_rc << (iniBit - new_iniBit), e[(iniBit - new_iniBit)..new_iniBit]</pre>

else //Copy all bits from the original signals

54