## Scalability and Virtualization enhancement in Spiking Neural Hardware based on PSOC

A Master's Thesis

Submitted to the Faculty of the

Escola Tècnica d'Enginyeria de Telecomunicació

de Barcelona

Universitat Politècnica de Catalunya

By

Roberto Gattuso

In partial fulfilment of the requirements for the degree of ELECTRONIC SYSTEMS ENGINEERING

Advisor: Jordi Madrenas Boadas Co-supervisor: Mireya Zapata

Barcelona, July 2019

## Abstract

This thesis work is focussed on the scalability and virtualization enhancement of *HEENS* architecture, which is a spiking neural hardware emulator. All blocks are described in VHDL, simulated to check their behaviour and finally the whole system is synthesized and implemented on a PSOC, in order to verify time constraints and area occupied.

In particular, all the improvements made concern the processing element array, which represents spiking neurons that have to be emulated. Each processing element consists of an ALU, a register file, a virtualization register, a LFSR and memory blocks containing synaptic parameters and membrane potential values.

Finally the architecture has a new spike distribution structure, making the system more scalable, and virtualization is introduced, in order to extend the array without requiring more resources, thus saving space on the board. Exploiting at most the available area, it has been possible to simulate a 13x13 array with problem-free timings.

## Acknowledgments

This thesis work would never have existed without the support of many people who have been present during this beautiful journey abroad. First of all, I have to thank Prof. Jordi Madrenas for having accepted me as a graduate student while I was still in Italy and for being present during these months, guiding this work, always ready to help me to find a solution to every problem, and Mireya Zapata, always available to collaborate despite the difficulties of distance, giving an huge support for FPGA test. I also want to thank Prof. Maurizio Martina, my advisor in Italy, who has had to monitor my work and despite the distance has always wanted to receive updates and give advice about them. I do not forget all the important people who have been close to me during these months, giving me help each in its own way: Martina, Francesca, Vittoria, Salvo; my quiet flatmates of Barcelona, Lorenza and Elisa, and those of Turin, Antonio and Totò; all the Erasmus friends met during this journey; the laboratory guys, Josep Angel, Diana, Josep Maria. I can not mention everyone, but thank you all for being part of my life.

Last but not least, I dedicate this work to my family, without whose moral support, their trust in me and their efforts, I would never have arrived where I am now. Thanks for existing.

## Abbreviations

AER Address Event Representation

ALU Arithmetic and Logic Unit

BRAM Block Random Access Memory

EPSP Excitatory Post-Synaptic Potential

HEENS Hardware Emulator of Evolved Neural System

IF Integrate and Fire IPh Initialization Phase

IPSP Inhibitory Post-Synaptic Potential

ISA Instruction Set Architecture

IZ Izhikevich

LFSR Linear-Feedback Shift Register

LIF Leaky Integrate and Fire

LIFO Last In First Out

LSB Less Significant Bit

LUT Lookup Table

ND Neural processing Device

MC Master Chip

MSB Most Significant Bit

PE Processing Element

PSP Post-Synaptic Potential

SIMD Single Instruction Multiple Data

SNAVA Spiking Neural-Networks Architecture for Versatile Applications

SNN Spiking Neural Network

VHDL Very High speed integrated circuits Hardware Description Language

# Table of contents

| $\mathbf{A}$ | bstra        | ct                                                | ]   |  |  |

|--------------|--------------|---------------------------------------------------|-----|--|--|

| $\mathbf{A}$ | ckno         | wledgments                                        | II  |  |  |

| $\mathbf{A}$ | bbre         | viations                                          | III |  |  |

| 1            | Intr         | roduction                                         | 1   |  |  |

| <b>2</b>     | State of Art |                                                   |     |  |  |

|              | 2.1          | Biological neurons network                        | 3   |  |  |

|              | 2.2          | Spiking Neuron Networks                           | 5   |  |  |

|              |              | 2.2.1 Leaky Integrate-and-Fire model              | 6   |  |  |

|              |              | 2.2.2 Izhikevich's neuron model                   | 7   |  |  |

|              |              | 2.2.3 Synaptic plasticity and STDP                | 7   |  |  |

|              |              | 2.2.4 Polychronization                            | 8   |  |  |

|              |              | 2.2.5 Computational power of neurons and networks | 9   |  |  |

|              | 2.3          | SNN Architectures                                 | 10  |  |  |

| 3            | Arc          | hitecture Review                                  | 12  |  |  |

|              | 3.1          | HEENS architecture                                | 12  |  |  |

|              | 3.2          | Processing Element array                          |     |  |  |

|              | 3.3          | IF Assembly Code                                  | 19  |  |  |

| 4            | Pip          | elining and Extension of the Multiprocessor Array | 22  |  |  |

|              | 4.1          | · · · · · · · · · · · · · · · ·                   | 22  |  |  |

|              | 4.2          | Array Extension                                   |     |  |  |

|              | 4.3          | Synthesis and Implementation                      |     |  |  |

| 5            | Vir          | tualization                                       | 39  |  |  |

|              | 5.1          | IF Assembly Code supporting virtualization        | 39  |  |  |

|              |              | 5.1.1 Memory Interface                            | 41  |  |  |

|              | 5.2          | Virtualization Design                             | 44  |  |  |

|              | 5.3                                  | 5.2.1 Simulations                                     |    |  |  |  |

|--------------|--------------------------------------|-------------------------------------------------------|----|--|--|--|

| 6            | 6 Conclusions and future development |                                                       |    |  |  |  |

| A            | A Instruction Set                    |                                                       |    |  |  |  |

| В            | Asse                                 | embler Code                                           | 58 |  |  |  |

|              | B.1                                  | IF                                                    | 58 |  |  |  |

|              | B.2                                  | IF_VIRT                                               | 61 |  |  |  |

| $\mathbf{C}$ | Net                                  | list                                                  | 65 |  |  |  |

|              | C.1                                  | $netlist\_ringosc5x5.txt$                             | 65 |  |  |  |

|              | C.2                                  | netlist_ringosc10x10.txt                              | 65 |  |  |  |

|              | C.3                                  | $netlist\_snake10x10.txt$                             | 66 |  |  |  |

|              | C.4                                  | $netlist\_BPF\_VIRT.txt  .  .  .  .  .  .  .  .  .  $ | 69 |  |  |  |

| D            | VH                                   | DL listing                                            | 70 |  |  |  |

|              | D.1                                  | PE.vhd                                                | 70 |  |  |  |

|              | D.2                                  | PE_row.vhd                                            | 83 |  |  |  |

|              | D.3                                  | PE_array.vhd                                          | 88 |  |  |  |

| Bi           | bliog                                | raphy                                                 | 93 |  |  |  |

# List of figures

| 2.1 | Neuron models based on the dot product computation [1]                                                                                                                                           | 4  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | A model of spiking neuron: EPSP (red curve) or IPSP; they are all                                                                                                                                |    |

|     | added (blue line) [1]                                                                                                                                                                            | 4  |

| 2.3 | Structure of a neuron network                                                                                                                                                                    | 5  |

| 2.4 | The Integrate-and-Fire electrical model                                                                                                                                                          | 6  |

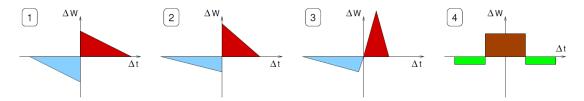

| 2.5 | Various shapes of STDP windows with LTP in blue and LTD in red for excitatory connections (windows 1 to 3). Standard Hebbian rule (window 4) with brown LTP and green LTD are usually applied to |    |

|     | inhibitory connections [1]                                                                                                                                                                       | 8  |

| 3.1 | HEENS architecture consisting of a Master Chip (MC) and Neural                                                                                                                                   |    |

|     | processing devices (NDs) connected in a ring [2]                                                                                                                                                 | 13 |

| 3.2 | HEENS processing stages[2]                                                                                                                                                                       | 14 |

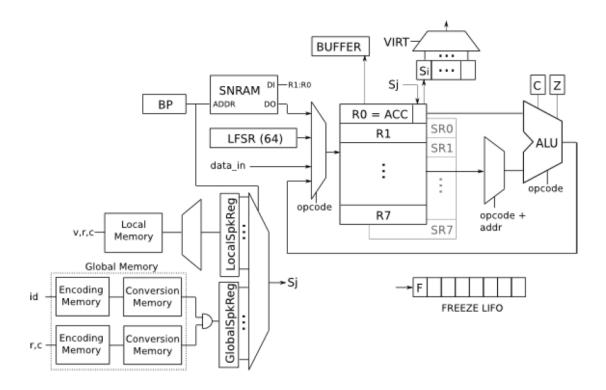

| 3.3 | Block diagram of HEENS multiprocessor architecture[3]                                                                                                                                            | 15 |

| 3.4 | Processing Element block diagram [4]                                                                                                                                                             | 18 |

| 3.5 | Simulation of the three neuron's membrane potentials trend as a func-                                                                                                                            |    |

|     | tion of time done with $QuestaSim$ software                                                                                                                                                      | 20 |

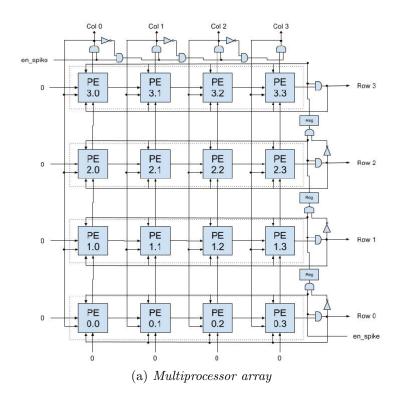

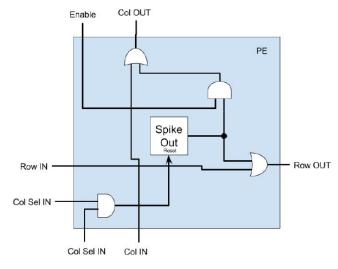

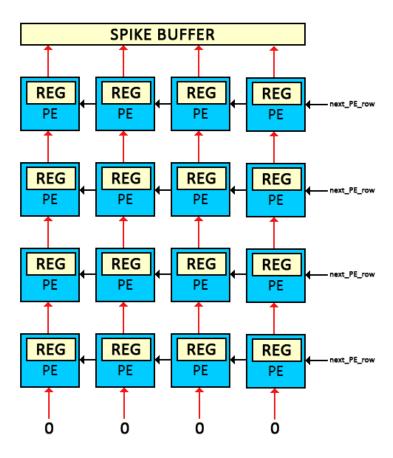

| 4.1 | Previous multiprocessor array and PE block diagrams [4]                                                                                                                                          | 23 |

| 4.2 | Block diagram of the new pipelined architecture of the multiprocessor                                                                                                                            |    |

|     | array. REG corresponds to the spike_out register                                                                                                                                                 | 24 |

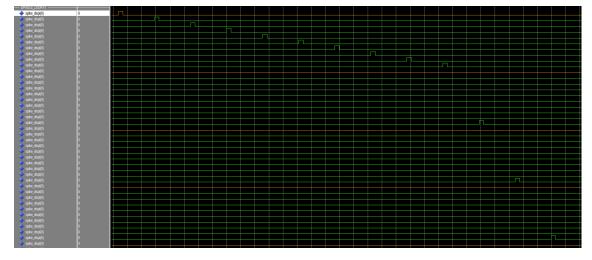

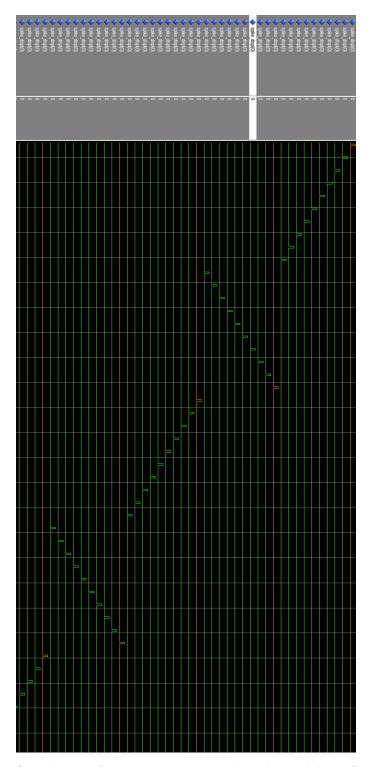

| 4.3 | Simulation with QuestaSim of a spiking PE (orange line)                                                                                                                                          | 26 |

| 4.4 | Block diagram of 5x5 ring oscillator network                                                                                                                                                     | 28 |

| 4.5 | Simulation of 5x5 array using a ring oscillator configuration done with                                                                                                                          |    |

|     | QuestaSim software. Row n.0 is in orange                                                                                                                                                         | 29 |

| 4.6 | Simulation of 10x10 array using a ring oscillator configuration done                                                                                                                             |    |

|     | with QuestaSim software. Row n.0 is in orange                                                                                                                                                    | 29 |

| 4.7 | Simulation of 9x7 array using a ring oscillator configuration done with                                                                                                                          |    |

|     | QuestaSim software. Row n.0 is in orange                                                                                                                                                         | 30 |

| 4.8 | Simulation of 16x16 array using a ring oscillator configuration done                                                                                                                             |    |

|     | with QuestaSim software. Row n.0 is in orange                                                                                                                                                    | 30 |

| 4.9 | Block diagram of 10x10 "snake path" network                                                                                                                                                      | 31 |

| 4.10 | Simulation of 10x10 array using a "snake path" configuration done           |    |

|------|-----------------------------------------------------------------------------|----|

|      | with QuestaSim software. Row n.0 is in orange                               | 32 |

| 4.11 | Xilinx Zynq-7000 SoC ZC706                                                  | 33 |

| 4.12 | Floorplanning of a $10x10$ array done with $Vivado$ software                | 34 |

|      | Area utilization of the whole architecture with 10x10 multiprocessor        |    |

|      | array done with <i>Vivado</i> software                                      | 35 |

| 4.14 | Power report of 10x10 array done with <i>Vivado</i> software                | 35 |

|      | Clock summary provided by <i>Vivado</i> software                            | 36 |

| 4.16 | Timing report of the architecture implementing a 10x10 multiproces-         |    |

|      | sor array without pipeline stages [4]                                       | 37 |

| 4.17 | Schematic of the critical path provided by <i>Vivado</i> software           | 37 |

|      | Device view of the critical path provided by <i>Vivado</i> software         | 38 |

|      |                                                                             |    |

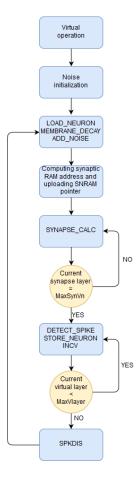

| 5.1  | Flowchart of IF Assembly Code supporting virtualization                     | 40 |

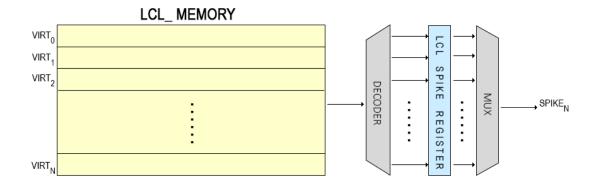

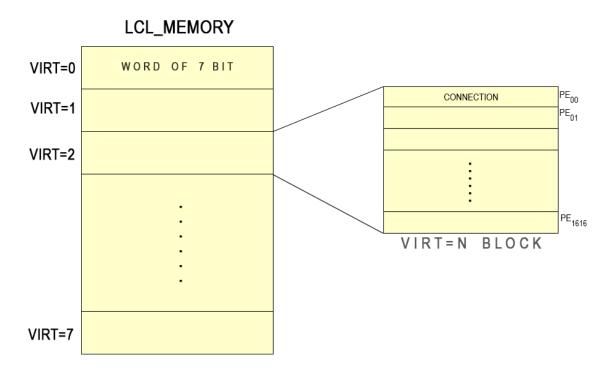

| 5.2  | SNRAM mapping                                                               | 41 |

| 5.3  | Local memory decoding                                                       | 42 |

| 5.4  | Local memory mapping                                                        | 43 |

| 5.5  | Block diagram of $HEENS$ processing element supporting virtualization.      | 45 |

| 5.6  | Focus on PE blocks that manage distribution phase and support vir-          |    |

|      | tualization                                                                 | 46 |

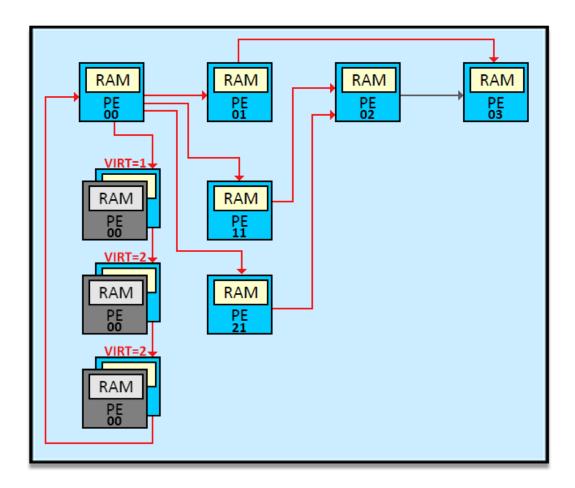

| 5.7  | Block diagram of 4x4 "band pass filter path" network, including a           |    |

|      | "ring oscillator" path between virtual layers of PE[0;0]. Red and           |    |

|      | grey arrows indicate respectively synapses with a positive or negative      |    |

|      | weights                                                                     | 47 |

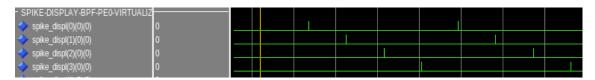

| 5.8  | Simulation, done with <i>Questasim</i> software, of a ring oscillator be-   |    |

|      | tween virtual layers of $PE[0;0]$                                           | 48 |

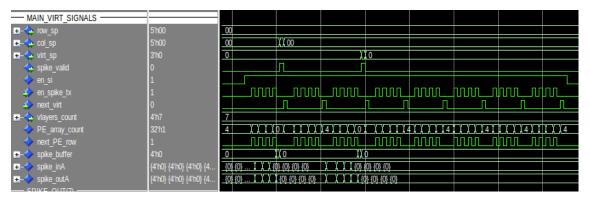

| 5.9  | Simulation, done with <i>Questasim</i> software, of all control signals in- |    |

|      | volved into virtualization                                                  | 48 |

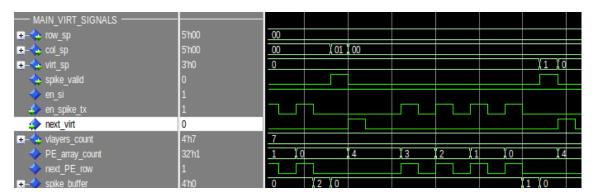

| 5.10 | Simulation, done with <i>Questasim</i> software, of the distribution of two |    |

|      | spikes coming from different virtual layers                                 | 49 |

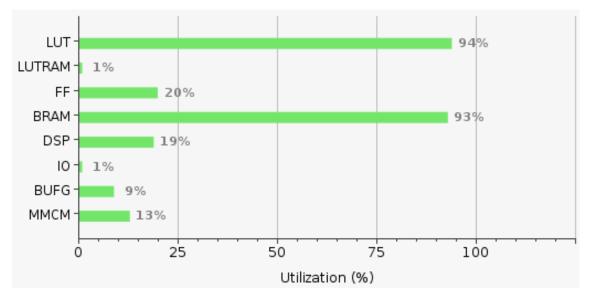

| 5.11 | Area utilization of the architecture supporting virtualization with         |    |

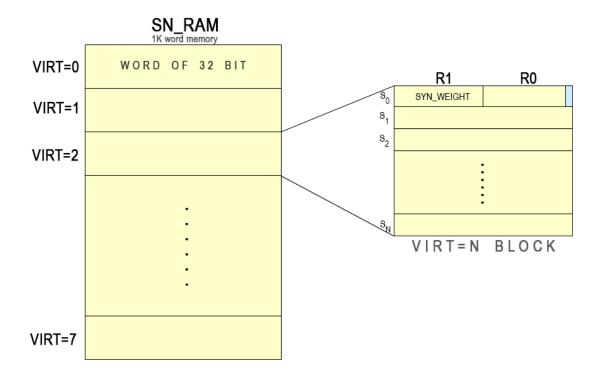

|      | 12x12 multiprocessor array done with $Vivado$ software                      | 50 |

| 5.12 | Floorplanning of a 12x12 array supporting virtualization done with          |    |

|      | Vivado software                                                             | 51 |

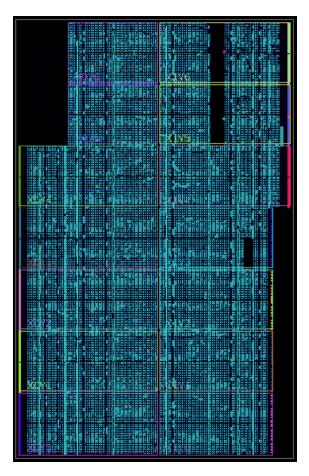

| 5.13 | Area utilization of the architecture supporting virtualization with         |    |

|      | 13x13 multiprocessor array done with $Vivado$ software                      | 52 |

| 5.14 | Floorplanning of a 13x13 array supporting virtualization done with          |    |

|      | Vivado software                                                             | 53 |

## List of tables

|     | Control values of the Register Bank                              |    |

|-----|------------------------------------------------------------------|----|

|     | -<br>-                                                           |    |

| 4.1 | Netlist format.                                                  | 27 |

| 4.2 | Report timing summary provided by <i>Vivado</i> software         | 36 |

| 5.1 | New netlist format supporting virtualization                     | 44 |

| 5.2 | Report timing summary of a 12x12 array supporting virtualization |    |

|     | provided by <i>Vivado</i> software                               | 51 |

| 5.3 | Report timing summary of a 13x13 array supporting virtualization |    |

|     | provided by <i>Vivado</i> software                               | 53 |

## Chapter 1

## Introduction

The study of human brain has been the subject of multiple investigations in order to understand how it works and being able to imitate its behaviour.

Reverse engineering, that generally is the process by which a man-made object is de-constructed to reveal its designs, architecture, or to extract knowledge from the object, applied to reproducing human intelligence, has led to a revolution of science in several fields with a wide range of applications such as speech recognition, robotics, devices smart, navigation, vision, etc. [5]. The growing interest in having efficient platforms that exhibit massive parallelism, energy efficiency, scalability with efficient connectivity and plasticity [1] has made nowadays simulation of complex biological neural systems a trending research area; moreover neuroscientists consider it an important tool in understanding the structure and dynamics of the human brain [6]. Since human brain holds all these characteristics, therefore its unparalleled performance has encouraged many engineers to develop bio-inspired simulators that mimic part of the human brain functionality. There are various approaches related to this field that concentrate their efforts in reaching a trade-off between realism, scalability, speed, flexibility etc.

From these assumptions, several neural network models were born over the years, such as Spiking Neuron Networks (SNNs), that belong to the 3rd generation of neural networks. This thesis project starts from the *HEENS* ("Hardware Emulator of Evolvable Neural Systems") architecture, that has been developed by the formerly Advanced Hardware Architecture group of the Department of Electronics Engineering of Universitat Politècnica de Catalunya (UPC); currently the architecture is kept on by new Integrated Smart Sensors and Health Technologies (ISSET) group.

Digital hardware is designed for simulating SNN. This work, in particular, is focussed on the hardware part of the HEENS processing element array, making improvements in terms of scalability, operation speed and resource occupancy. The first goal consists in trying to increase the array without violating time constraints: pipeline stages are introduced with the purpose to allow the system to support a

greater number of neurons while preserving the operation speed. Another goal is to support the virtualization of PE up to seven neurons in addition of the main layer: this means that, without introducing new PEs, it is possible to emulate them, increasing the number of neurons to be simulated without using new hardware resources.

Moreover, the architecture is synthesized and implemented on the Xilinx Zynq-7000 SoC ZC706 board, which is an MPSoC device chosen to enhance the system configurability and monitoring, since it integrates both processor and FPGA architectures into a single device. The array size is extended as much as possible to test if time constraints are violated when the area occupancy on the board is close to 100%, so verifying if the introduced pipeline stages have reduced the critical path enough to preserve the correct behaviour of the system.

## Chapter 2

## State of Art

The human brain study has been the subject of multiple investigations in order to understand how it works and being able to imitate its behaviour. The state of art investigation is of priority importance to understand firstly which are nowadays the most important models that describe a biological neural network and then which are the most significant architectures able to emulate it.

Therefore, this chapter is an introduction step into spiking neural networks world, which belongs to the last generation of neural networks: basic biological notions will be introduced, followed by a description of the most relevant neural models, concluding with a reference to the different variants of implementations that modern architectures adopt.

#### 2.1 Biological neurons network

A biological neural system consists of millions of highly integrated neurons with multiple dynamic functions operating in coordination with each other.

The original work of McCulloch & Pitts in 1943 proposed a neural network model based on simplified "binary" neurons, where a single neuron is represented by a state that can be either *active* or *not active*, and at each neural computation step the state of of the neuron under examination is determined by calculating the weighted sum of the states of all the afferent neurons [1].

$$y = \sum_{i} x_{i} w_{i} \qquad y = \begin{cases} 1 & \text{if } x_{i} w_{i} > \theta \\ 0 & \text{if } x_{i} w_{i} \leq \theta \end{cases}$$

(2.1)

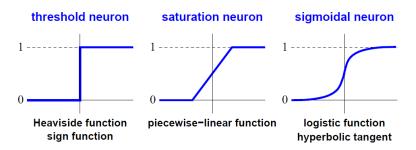

Connections between neurons are mapped from neuron  $N_i$  to neuron  $N_j$ ) and each of them has specific a weight  $(w_{ij})$ . If the weighted sum of the states  $x_i$  of all the neurons  $N_i$  connected to a neuron  $N_j$  exceeds the characteristic threshold  $\theta$  of  $N_j$ , the state of  $N_j$  is set to active, otherwise it is not. This first model, called "threshold

neuron", is the simplest one and it was replaced by more realistic models based on linear or non-linear threshold functions (respectively "saturation" and "sigmoidal" neuron) as shown in fig.2.1.

Figure 2.1. Neuron models based on the dot product computation [1].

Separately, neurobiological research has greatly progressed and, regarding the study of cognitive processing, individual spikes time is intended as the means of communication and neural computation. The current consent agrees that cognitive processes are most likely based on the activation of transient assemblies of neurons although the underlying mechanisms are not yet understood well [1].

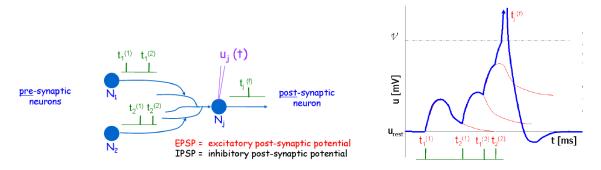

Figure 2.2. A model of spiking neuron: EPSP (red curve) or IPSP; they are all added (blue line) [1].

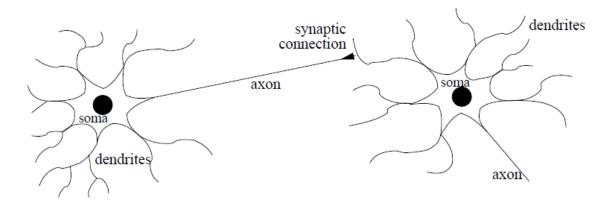

Fig.2.2 shows a model of spiking neuron: in the left picture each pre-synaptic spike generates an excitatory post-synaptic potential (EPSP) or an inhibitory post-synaptic potential (IPSP) in case of negative weight. A post-synaptic neuron  $N_j$  fires a spike whenever the weighted sum of incoming EPSPs generated by its pre-synaptic neurons reaches a given threshold  $\nu$ . Instead the right graphic shows how the membrane potential of  $N_j$  varies through time, under the action of four incoming spikes. Entering into detail, fig.2.3 shows an example of a basic neuron network. Most biological neurons rely on pulses as an important part of information transmission from one neuron to another one and in a rough and non-exhaustive outline, a

neuron can generate an action potential (the spike) at the soma, the cell body of the neuron. Then, this brief electric pulse (with 1 or 2ms of duration) travels through the neuron's axon arriving to the receiving end of target neurons, the dendrites. In the final part of the axon, synapses connect one neuron to another one, and at the arrival of each individual spike, the synapses may release neurotransmitters along the synaptic cleft. These neurotransmitters are taken up by the neuron at the receiving end, modifying the state of that post-synaptic neuron, in particular the membrane potential. The transient impact a spike has on the neuron's membrane potential is generally referred to as the post-synaptic potential (PSP), and it can either inhibit the future firing (IPSP) or excite the neuron, making it more likely to fire (EPSP). Depending on the neuron, and the specific type of connection, a PSP may directly influence the membrane potential for anywhere between tens of microseconds and hundreds of milliseconds [1].

Figure 2.3. Structure of a neuron network.

#### 2.2 Spiking Neuron Networks

Spiking Neuron Networks (SNNs) are often referred to as the 3rd generation of neural networks. They derive their strength and interest from an accurate modelling of synaptic interactions between neurons, taking into account the time of spike firing [1]. One example of such coding that easily compares to traditional neural coding, is temporal coding, a straightforward method for translating a vector of real numbers into a spike train. The basic idea is biologically well-founded: the more intensive the input is, the earlier the spike transmission will be. Hence a network of spiking neurons can be designed with n input neurons  $N_i$  whose firing times are determined through some external mechanism. The network is fed by successive n-dimensional input analog patterns  $\mathbf{x} = (x_1, ..., x_n)$  that are inside a bounded interval  $T_{in}$  and

translated into spike trains through successive temporal windows. In each time window, a pattern x is temporally coded by one spike emission of neuron  $N_i$  at time  $t_i = T_{in} - x_i$ , for all i. This temporal coding, with other assumptions, shows that any traditional neural network can be emulated by an SNN. [1]

The first difficult task is to define the model of spiking neurons and synaptic plasticity, as there exist numerous variants already. A spiking neuron model accounts for the impact of impinging action potentials (spikes) on the targeted neuron in terms of the internal state of the neuron, as well as how this state relates to the spikes the neuron fires.

#### 2.2.1 Leaky Integrate-and-Fire model

Leaky Integrate-and-Fire (LIF) is a neuron model much more computationally tractable that other ones, as the Hodgkin-Huxley from which it derived from.

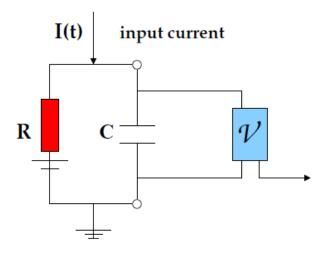

Figure 2.4. The Integrate-and-Fire electrical model.

Fig.2.4 represents this simple model, where  $\nu$  is the threshold voltage that has to be overcome to generate a spike. This simplification has to be able to approximate the real behaviour shown in fig.2.2.Compared to the Hodgkin-Huxley model, the most important simplification in the LIF neuron implies that the shape of the action potentials is neglected and every spike is considered as a uniform event defined only by the time of its appearance. It can be modelled as a RC circuit and a comparator. The neuron receives a train of impulses coming from pre-synaptic neurons, represented as an input current I(n) charging the capacitor. The mathematical model of the membrane potential u(t) in the LIF is described by a single

first-order linear differential equation [1]:

$$C\frac{\mathrm{d}}{\mathrm{d}t}(u(t)) = -\frac{1}{R} \cdot (u(t) - u_{rest}) + I(t)$$

(2.2)

$$\tau_m \frac{\mathrm{d}}{\mathrm{d}t} (u(t)) = (u_{rest} - u(t)) + RI(t)$$

(2.3)

where  $\tau_m = \text{RC}$  is taken as the time constant of the neuron membrane, modelling the voltage leakage. Additionally, the firing time  $t^f$  of the neuron is defined by a threshold crossing equation  $u(t^f) = \theta$ , under the condition  $u(t^f) > 0$ . Immediately after  $t^f$ , the potential is reset to a given value  $u_{rest}$  called resting potential.

#### 2.2.2 Izhikevich's neuron model

In the class of spiking neurons defined by differential equations, the two-dimensional Izhikevich (IZ) neuron model is a good compromise between biophysical plausibility and computational cost [1]. It is defined by the coupled equations:

$$\frac{\mathrm{d}}{\mathrm{d}t}(u(t)) = 0.04u(t)^2 + 5u(t) + 140 - w(t) + I(t) \qquad \frac{\mathrm{d}}{\mathrm{d}t}(w(t)) = a(bu(t) - w(t)) \quad (2.4)$$

with after-spike resetting: if  $u \leq \theta$  then  $u \leftarrow c$  and  $w \leftarrow w + d$ . This neuron model is capable to reproducing many different firing behaviours that can occur in biological spiking neurons.

#### 2.2.3 Synaptic plasticity and STDP

In all the neurons models, most of the parameters are constant values and specific to each neuron. The exception are synaptic connections that are the basis of adaptation and learning. Synaptic plasticity refers to the adjustments and even formation or removal of synapses between neurons in the brain [1]. From the biological point, it is possible to summarize changes of synaptic weights in two types: those with effects lasting several hours are referred as Long Term Potentiation (LTP) or Long Term Depression (LTD), if the weight values are gotten stronger or weaker; instead, those weight changes in the second or minute time scale are denoted as Short Term Potentiation (STP) and Short Term Depression (STD). One important finding that is receiving increasing attention is Spike-Timing Dependent Plasticity (STDP), which is a form of synaptic plasticity sensitive to the precise timing of spike firing relative to impinging pre-synaptic spike times. A basic computational rule has come out: a maximal increase of synaptic weight occurs on a connection when the pre-synaptic neuron fires a short time before the post-synaptic one, whereas a late

pre-synaptic spike, just after the post-synaptic firing, leads to decrease the weight [1]. If both pre and post spikes are too temporally distant, the weight remains unchanged. For computational purposes, STDP is most commonly modelled in SNNs using temporal windows for controlling the weight LTP and LTD that are derived from neurobiological experiments. Different shapes of STDP windows have been used in recent literature: They are smooth versions of the shapes represented by polygons in fig.2.5.

Figure 2.5. Various shapes of STDP windows with LTP in blue and LTD in red for excitatory connections (windows 1 to 3). Standard Hebbian rule (window 4) with brown LTP and green LTD are usually applied to inhibitory connections [1].

X-axis is the spike timing, which is the difference  $\Delta t = t_{post} - t_{pre}$  of firing times between the pre and post synaptic neurons. The synaptic change  $\Delta W$  on Y-axis operates on the weight update. For excitatory synapses, the weight  $w_{ij}$  is increased when the pre-synaptic spike is supposed to have a causal influence on the post-synaptic spike, i.e. when  $\Delta t > 0$  and close to zero (pictures 1-3 in fig.2.5) and decreased otherwise [1]. For inhibitory synaptic connections, it is common to use a standard Hebbian rule, just strengthening the weight when the pre and post synaptic spikes occur close in time, regardless of the sign of time difference  $t_{post} - t_{pre}$ .

#### 2.2.4 Polychronization

Nowadays, a growing empirical evidence is that neurons can generate spike-timing patterns with millisecond temporal precision: patterns can be found in the firing sequences of single neurons or in the relative timing of spikes of multiple neurons forming a functional neuronal group [7].

Indeed, if two or more neurons have a common post-synaptic target and fire synchronously, then their spikes arrive to the target at the same time, thereby evoking potent post-synaptic responses. Considering axonal conduction delays are negligible or equal, if neurons fire asynchronously, their spikes arrive to the post-synaptic target at different times evoking possibly only weak or no response.

Nevertheless, depending on the type and location of the neurons, axonal conduction delays could be relevant: for this reason, *Polychronization* takes into account this aspect. Since the firings of neurons are not synchronous, but time-locked

to each other, it is possible to refer to such groups as polychronous, where  $poly(\pi o \lambda v \zeta)$  means many and  $chronous(\chi \rho o v o \zeta)$  stands for time or clock in Greek. Moreover, Polychrony should be distinguished from asynchrony, since the latter does not imply reproducible time-locking pattern, but usually describes noisy random non-synchronous events.

Finally, whenever the neurons do fire with the spike-timing pattern determined by the connectivity and delays, the group is *activated* and the corresponding neurons *polychronize*.

#### 2.2.5 Computational power of neurons and networks

Information processing in spiking neuron networks is based on the precise timing of spike emissions (pulse coding) rather than the average numbers of spikes in a given time window (rate coding) [1].

In particular, SNNs add a new dimension, the temporal axis, to the representation capacity and to the processing abilities of neural networks. It is possible to describe different approaches to establish the computational power and the complexity of SNNs thinking on how to exploit these properties. In 1997, Maass [1] proposed to classify neural networks models as follows:

- 1st generation: Networks based on McCulloch & Pitts' neurons as computational units, i.e. threshold gates, with only digital outputs.

- 2nd generation: Networks based on computational units that apply an activation function with a continuous set of possible output values, such as sigmoid or polynomial or exponential functions (e.g. MLP, RBF networks). The real-valued outputs of such networks can be interpreted as firing rates of natural neurons.

- 3rd generation: Networks which employ spiking neurons as computational units, taking into account the precise firing times of neurons for information coding.

This thesis work is based on the hardware design of the *HEENS* architecture, that emulates neural networks models belonging to the 3rd generation.

#### 2.3 SNN Architectures

Nowadays, simulation of complex biological neural systems is a trending research area. Many implementation of SNN models adopted, each one with its specific advantages and disadvantages; it is possible to report some of these different approaches.

Analog implementations exploit transistor's sub-threshold range operations to create compact and high-speed processing neural simulators: *BrainScaleS* is one of the most prominent projects in full custom analog design to simulate exponential integrate-and-fire neurons. These implementations offer extremely low area and energy consumption for very large-scale networks. [8] However, they are difficult to program and to scale, and they have high manufacturing costs and they require time to be designed and to be tuned. Therefore, the full custom analog implementations could be useful for those applications where the behaviour of the SNN is very well defined and characterized [6].

In contrast to analog-based solutions, most digital implementations are less expensive and more flexible. Currently many of them use general-purpose multiprocessors, Graphical Processing Units (GPUs) or FPGAs. These digital architectures offer wide range of flexibility and reconfigurability to process large scale SNN models at high speed [6].

One of the recently highlighted multiprocessor-based SNN simulators is *TrueNorth*, which implements LIF neurons with high number of synapses without plasticity [9]. *SpiNNaker* is another well-known multiprocessor-based SNN simulator: its programmable feature allows SpiNNaker to support different SNN models at the cost of highly complex processing cores [10].

GPU cards can provide a powerful solution when highly parallel computing is required, so several advanced GPU-based simulators have been proposed during the last ten years: one of them is *NEST* (Neural Simulation Tool) that supports several neural and synaptic models. Its low degree of biophysical detail has been a critical issue [11].

FPGA-based SNN simulation has been proposed and implemented in several works [6]. Zamarreno-Ramos proposed a scalable–reconfigurable neuromorphic Address Event Representation (AER) configured as 2D mesh. They claim that the proposed architecture is capable of managing spike traffic using routing approaches in a single or multiple FPGAs. The architecture simulates simple IF neurons to perform the convolution operation that is used in image processing (character recognition), but neurons do not involve plasticity [12].

A recent innovation in the field of SNN is *Loihi*, a neuromorphic chip fabricated in Intel's 14-nm process, having a total of 130,000 artificial neurons and 130 million synapses. It integrates a wide range of novel features for state-of-the-art modelling of SNN in silicon: hierarchical connectivity, dendritic compartments, synaptic delays,

and, most importantly, programmable synaptic learning rules [13]. The chip is implemented as a many-core mesh, each of which houses a learning engine that can support a variety of machine learning models.

The FPGA digital implementations trade off model flexible and high speed processing. Instead, the GPU and general purpose multiprocessor approaches seem to have the flexibility to implement several SNN models and the scalability to implement fairly large-scale networks. The problem is that all these implementations rely on a general purpose Instruction Set Architecture (ISA) and on chip communication to simulate SNN: evidently, there would be some performance loss and power consumption because of certain functionalities that are useless for SNN simulation. Finally, Spiking Neural Networks for Versatile Applications (SNAVA) is an example of special purpose architecture that could not have this kind of performance loss and power consumption: it is the predecessor of HEENS, the architecture which this thesis work is focussed on and whose features are described in chapter 3. The ISA of SNAVA has been tailored to SNN simulation to get the best out of the utilized hardware. SNAVA is a scalable and programmable parallel architecture that supports real-time, large-scale, multi-model SNN computation[6]. This parallel architecture is implemented in modern FPGAs devices to provide high performance execution and flexibility to support large-scale SNN models. Flexibility is defined in terms of programmability, which allows easy synapse and neuron implementation. This has been achieved by using a special-purpose Processing Elements for computing SNNs, and analyzing and customizing the instruction set according to the processing needs to achieve maximum performance with minimum resources. Its architecture is mainly composed of an array of SIMD (Single Instruction Multiple Data) units, a single control unit and a number of communication units that support software to configure and monitor the system in real time (1 ms time step simulation). In addition, SNAVA is scalable architecture and has the flexibility to be implemented into several chips forming a system in any topology of user's choice.

## Chapter 3

### Architecture Review

This project starts from the *HEENS* (Hardware Emulator of Evolvable Neural Systems) architecture, that has been developed by the Advanced Hardware Architecture group of the Department of Electronics Engineering of Universitat Politècnica de Catalunya (UPC). This architecture is an evolution of a previous one, called *SNAVA* ("Spiking Neural-Networks Architecture for Versatile")[6], and it works with a more efficient Processing Element array in terms of functionality and resource occupancy. HEENS is more versatile and it allows to load and run via software different models of neurons and change their synaptic interconnection dynamically without resynthesizing the project. Moreover, the versatility of this architecture allows to easily resize the array (number of PE and all the necessary connections for proper operation) using only two parameters: the number of rows and columns.

The work of this thesis project is focussed on the hardware part of the PE array, in particular on the improvement of the architecture in terms of scalability, frequency and resource occupancy, trying to increase the size of array by acting on these aspects. In this chapter there is explained the starting point of this thesis work, focusing in particular on the PE array design.

#### 3.1 HEENS architecture

HEENS is an architecture designed for multi-FPGA implementations for SNN emulation in real time, which has been designed to support evolution network with a high degree of configurability, with a spike communication scheme called AER ("Address Event Representation"), that can be hierarchically extended. It allows several chips to be interconnected in a ring topology (Fig. 3.1) in a Master/Slave and point-to-point hybrid communication scheme. Chip Master (MC) takes control of the network to configure the ring and the neuronal application in all the nodes and it controls the dynamic on-line reconfiguration of each node [14].

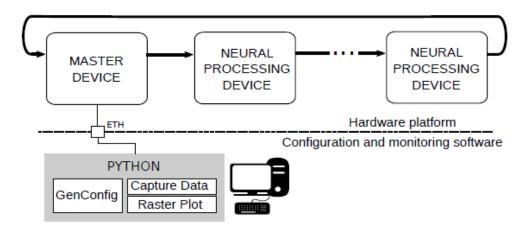

Figure 3.1. HEENS architecture consisting of a Master Chip (MC) and Neural processing devices (NDs) connected in a ring [2].

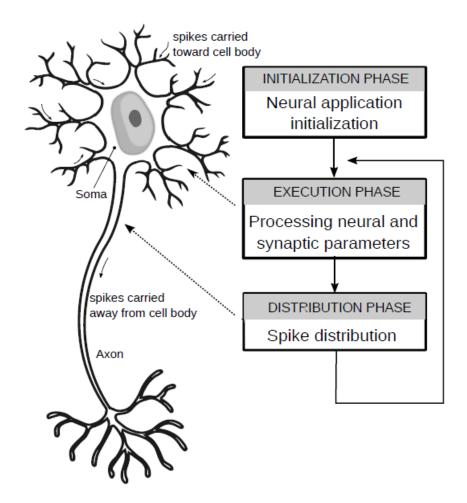

HEENS bases its processing sequence by emulating the biological behavior of neurons, for which it divides its processing into four phases of operation (as shown in Fig. 3.2)[14]:

- Initialization Phase (IPh): the ring that makes up the multi-chip platform is configured, so it is required to identify each node (ID) and the ring size.

- Execution Phase (EPh): this phase has biological correspondence with the soma. Here the neuronal algorithm is processed by calculating and updating the state variables. Each neuron uses individual parameters for its processing. The start and end of this phase is marked by an internal control signal called eo\_exec.

- Distribution Phase (DPh): it manages the propagation of neurotransmitters through the synapses. Spikes obtained in the EPh are propagated and delivered to the destination neurons located in the same or in different NDs.

Figure 3.2. HEENS processing stages[2].

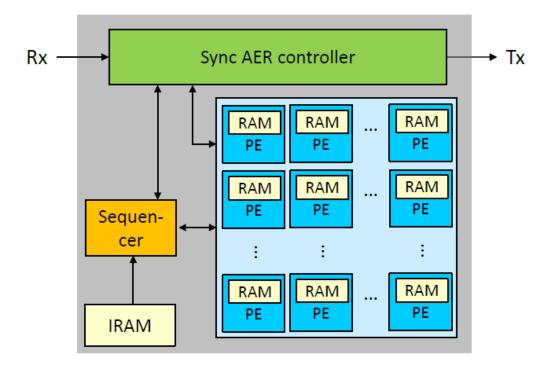

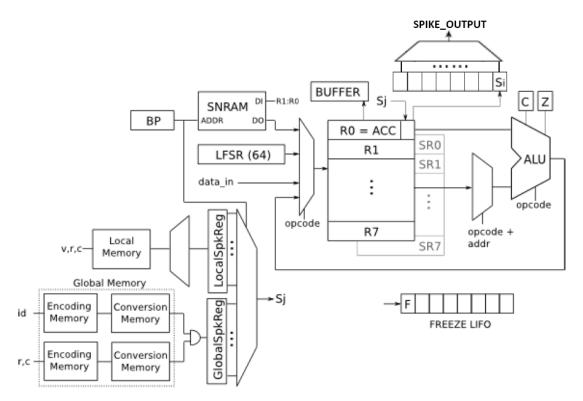

The multiprocessor architecture is illustrated in Fig. 3.3 and it corresponds to a ND of the neural network. This performs the processing of neuronal activity programmed by the user and it uses a Single Instruction Multiple Data (SIMD) computation scheme with a single control unit to achieve data level parallelism in the PE array. In fact, each processing elements disposes local memories, holding the modelling parameters of each specific neuron: this means each processor has to run the same set of operations with different local parameters along, allowing the use of a single programmable control unit. This technique is suitable for the implementation of neural networks because it reduces area costs and offers high computational performance, reducing dramatically the resource requirements compared to GPUs or architectures that makes use of complex general purpose cores.

Figure 3.3. Block diagram of HEENS multiprocessor architecture[3].

The main blocks that comprise it and described below are:

- Communication buses: the address and data buses that allow the flow of information to the array are multiplexed between those that transmit configuration packets and those that deliver execution informations corresponding to the opcodes dispatched by the Sequencer and spike events delivered by the controller. Selection of these is given by the internal signal called *config* that is activated depending on the phase that is being processed.

- Control Unit (Sequencer and Instruction-RAM): HEENS-MP is a Harvard type architecture. The instructions are read from a single memory (IRAM). Each PE has its local data memory (SNRAM) where it stores the synaptic and neuronal parameters of each neuron. Sequencer enables the distribution signal en\_spike after the Execution Phase (EPh), during which it sends instructions to all processors at the same time and all of them calculate the membrane potential in function of the input spikes, synapses and initial configuration. If a neuron spikes, this information is stored in the spike\_out register, that is located inside the PE. It has a size equal to the chosen virtualization level.

- AER-SRT Controller: it brings the capability of interconnect more FPGAs in a

synchronous ring topology (SRT) to increase the number of neurons emulated. Once the algorithm has been processed in the PEs, a row sweep is performed to obtain the post-synaptic spikes triggered by the neurons when the membrane voltage has exceeded the threshold voltage. The spikes generated at each execution cycle are encoded in address events and stored in a FIFO waiting to be transmitted during the DPh.

• PE array: it is the matrix of PE that composes a Neural processing device. More details are explained in section 3.2.

This thesis work is focussed on the PE array block.

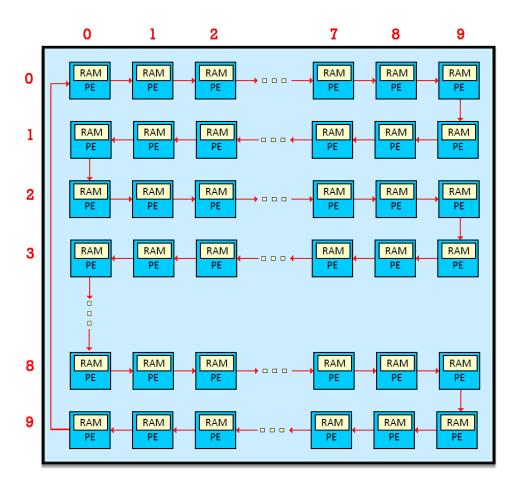

#### 3.2 Processing Element array

The array shown in Fig. 3.3 is a 2D array of PEs: its size is parametrizable according to the numbers of rows and columns of the array and the virtual level, which allows to make a 3D array if the level is higher than 0. Due to the hierarchical and modular nature of HEENS, the PEs process two types of spikes: local (generated in the same ND) and global (those coming from others NDs or from the MC).

In Fig. 3.4 the block diagram of PE is shown; the internal components correspond to an Harvard type architecture and the main units that constitute it are [14]:

- ALU: it supports 16-bit fixed point arithmetic and logical operations. *Opcode* is the 6-bit control signal used to choose witch operation ALU has to do. The Carry (C) and Zero (Z) status flags are accessible to the user.

- Register File (R0-R7): a bank of 8 general purpose 16-bit registers that interacts directly with the ALU through the accumulator register R0. Moreover, there is also a shadow registers bank (SR0-SR7), whose access is managed by the Sequencer, used to extend the space of storage of neuronal or synaptic variables. Through the reg\_code control signal it is possible to manage data\_in inputs (eight 16 bit inputs) in different way. Tab. 3.1 shows the possible controls of the register file:

| Regcode | Function                                                      |

|---------|---------------------------------------------------------------|

| 000     | $R_x <= \mathrm{Data\_in\_x}$                                 |

| 001     | reset if $EN_{-}x$ is asserted                                |

| 010     | set if $EN_x$ is asserted                                     |

| 011     | swap with respective shadow register if $EN_{-}x$ is asserted |

| 100     | $SR_x \le R_x$ if the register is enabled                     |

| 101     | $R_x \ll SR_x$ if the register is enabled                     |

Table 3.1. Control values of the Register Bank.

where  $R_x$  and  $SR_x$  are respectively the register and the shadow register in position x, EN is an 8-bit control signal that enables each register.

- Synaptic/Neural Memory (SNRAM): it is the data memory in charge of storing neuronal and synaptic parameters, seeds of LFSR block and any other data of the neurons processed by the PE in each virtual level.

- Local and Global memories (BRAM): this block is composed by a block of local memory (where the interconnectivity between local neurons is modelled) and an associative scheme that allows the decoding of global connections. The global memory block models the interconnection between neurons of different NDs: each PE has  $s_G 1$  global synapses processed at the main level (VIRT = 0) to emulate a hierarchical connection characterized by sparse connectivity between clusters.

- Virtualization (VIRT): this block emulates more than one neuron per PE per execution cycle. The virtual level is the parameter that defines n pipelined virtualization levels plus a main level, which is VIRT = 0. implementing virtualization is one of the targets of this work.

- Pseudo Random Generator (LFSR): the seed of this 64-bit register is defined by software with the SEED instruction, and it is stored in the SNRAM memory. This register allows generating uncorrelated noise for each PE.

- Freeze LIFO: FREEZE instructions are linked to the Carry and Zero flags and they use a LIFO for their execution, to stack up to eight levels for nested conditions.

Figure 3.4. Processing Element block diagram [4].

#### 3.3 IF Assembly Code

HEENS architecture is able to emulate the leaky Integrate and Fire (IF) algorithm, which is one of the most used models for emulation SNN. The idea of this model consists on computing he membrane potential as a function of the receiver spikes through the predefined synapses. The assembler code (see Appendix B.1) runs the IF algorithm: it takes into account specific key values of membrane potential, taken from different biological studies in literature. These values are shown in the table 3.2:

| Membrane Potential | Hexadecimal value | Potential value $[10^{-5}V]$ |

|--------------------|-------------------|------------------------------|

| $V_{REST}$         | FFFFE4A8          | -7000                        |

| $V_{THRES}$        | FFFFEA84          | -5500                        |

| $V_{DEPOL}$        | FFFFE0C0          | -8000                        |

| $V_{ACT}$          | 00001771          | +1000                        |

Table 3.2. Membrane potential key values.

#### where:

- $V_{REST}$  is the Resting potential, equal to -70 mV;

- $V_{THRES}$  is the Threshold voltage, equal to -55 mV;

- $V_{DEPOL}$  is the Depolarization voltage, equal to -80 mV;

- $V_{ACT}$  is the Action potential, equal to 10 mV.

When the algorithm starts, after random initialization, using the subroutine  $LOAD\_NEURON$  (Appendix B.1), membrane potential of each PE is stored in their respective R2 register and the synapse weight into R1. Then, with the  $MEM\_BRANE\_DECAY$  subroutine, the membrane potential decay is calculated using a time constant  $\tau_{decay}$ , which is less but close to 1. In fact, storing the current membrane potential in R2 into the accumulator (MOVA R2) and resting potential in R4 (LDALL R4,  $V_{REST}$ ), the algorithms does the following computation:

$$V'_{mem} = (V_{mem} - V_{REST}) \cdot \tau_{decay} + V_{REST}$$

(3.1)

where  $V_{mem}^{\prime}$  is the new membrane potential after decay.

Every time a neuron receives a spike through one of its synapses, its  $V_{mem}$  increases or decreases according to the specific excitatory or inhibitory synapse weight. For this reason, it is necessary a loop ( $LOOP\ tot\_synapses$ ) in which all synapses

of each neuron are read in order to detect possible incoming spikes. This loop implements the following calculation to obtain the new membrane potential:

$$V_{mem}^{"} = V_{mem}^{'} + \sum_{k=0}^{n-1} s_k \cdot w_k \tag{3.2}$$

where n is the total number of synapses,  $w_k$  is the synapse weight of the k-th synapse and  $s_k$  is a value equal to 1 or 0, respectively if a spike impinges that synapse or not.  $w_k$  is stored into R1 register and the spike  $s_k$  into the LSB of the accumulator (LOADSP). Each time a sum is computed, the accumulator is reset ( $RST\ ACC$ ), the pointer BP of the SNRAM, where all the synaptic, neural and some common parameters are loaded, is increased and new parameters, that will be used for the next cycle, are stored inside its respective registers R0 and R1.

Subsequently, after having calculated the new  $V_{mem}^{"}$  for each neuron, through the  $DETECT\_SPIKE$  subroutine the algorithm detects during each execution phase if the membrane potential of some neurons has exceeded the threshold voltage, thus producing post-synaptic spikes. This value is stored in R0 (LDALL ACC,  $V_{THRES}$ ) and it is compared with the current membrane potential in R2, doing a subtraction and checking the Carry Flag of ALU: if it is positive, a spike is generated. In this way, the IF model behaviour is reproduced. Once the spike is detected, the spiking neuron has to be discharged, returning to the initial value of its membrane potential  $V_{mem}$  equal to  $V_{REST}$  (LDALL ACC,  $V_{REST}$ ).

Finally, STORE\_NEURON subroutine is executed: the SNRAM is uploaded storing R1 and the final membrane potential (STORESP) and the pointer BP is increased. Now execution phase ends, spikes are distributed (SPKDIS) and the loop can start again.

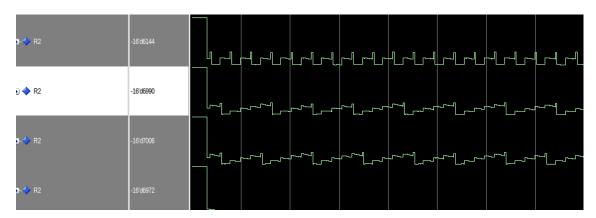

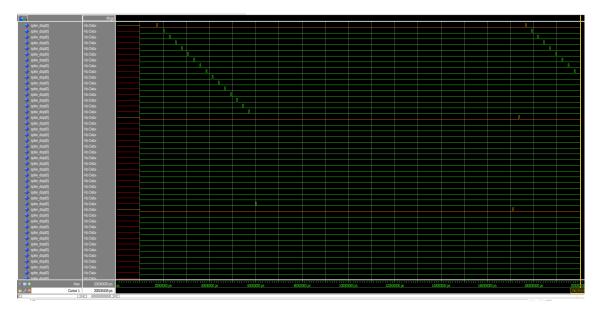

Figure 3.5. Simulation of the three neuron's membrane potentials trend as a function of time done with *QuestaSim* software.

The HEENS architecture has been described in synthesizable VHDL. In Fig.3.5

it is showed the R2 register values of four PEs using the analog format of QuestaSim software. Each time the membrane potential  $V_{mem}$  of a neuron exceeds the threshold voltage, a spike is generated and  $V_{mem}$  resets itself, returning to have a value equal to about the resting potential  $V_{REST}$ . Moreover, every time a neuron receives a stimulus through one of its synapses,  $V_{mem}$  increases and it decays continuously towards  $V_{REST}$  with the  $\tau_{decay}$  constant.

HEENS architecture allows also to change easily the topology of the model: interconnections between neurons (i.e. PE) are described using netlist files, as ones reported in Appendix C and whose explanation is reported in the following chapter, and stored into associative memories. Moreover, it is possible to set the initial membrane potential  $V_{mem}$  for each neuron: in this way it is feasible to decide if a neuron, at the beginning, has a spike and any kind of possible spike paths can be described.

## Chapter 4

# Pipelining and Extension of the Multiprocessor Array

In this chapter there are introduced the first improvements of the architecture in terms of time constraints and area occupancy: designing a new path of the spike distribution, the goal is to extend the array as much as possible without having problems of negative slacks. Simulations are done with QuestaSim software, using as assembler code the one in Appedinx B.1. Regarding the initial membrane potential, for all the following simulations it is assigned a  $V_{mem}$  initiated at -60 mV (10 mV above resting potential) to all PE except PE[0;0], which is initiated at -40 mV: in this way the PE[0;0] will fire, because its values is above  $V_{THRES} = -55$  mV, and any neuron having a synaptic connection with it will fire too as consequence, due to their membrane potential which is slightly below the threshold.

#### 4.1 Spike pipeline

The first goal of this project is to modify the current architecture in order to make a new version of the multiprocessor array in which the critical path during the Distribution Phase (DPh) of spikes is reduced.

The previous architecture is shown in Fig. 4.1.

(b) Processing element

Figure 4.1. Previous multiprocessor array and PE block diagrams [4].

In this architecture, spike distribution follows a combinational path with priority: spikes generated by each PE are processed and forwarded to the neighbour processors. Actually, processor in position [0,0] (row 0 and column 0) has the highest priority, so if it produces a spike, it will be the first to leave the array and be resetted. Then, PE in position [0,1], having the second highest priority, continues to transmit spikes when all the previous ones were clean and so on. This cycle does not end until the sequencer disables distribution signal  $en\_spike$ . To reduce the combinational circuit, pipeline register are inserted at the end of each row.

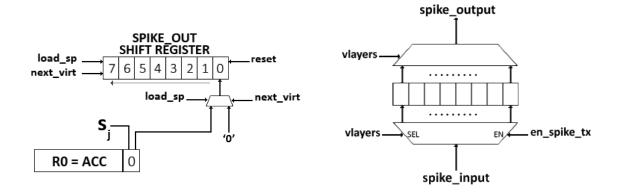

The weak point of this architecture is that, if the size of the array is increased, the critical path could be too long and it could violate timing constraints. Since it is not optimal to reduce clock frequency, which is set at 125MHz, because the other parts of the system have not problems, the proposed solution is to introduce pipeline stages in order to keep constant the clock frequency. The new architecture designed is shown in Fig. 4.2: the priority scheme is replaced by a simpler architecture, where several signals involved before in the priority scheme are deleted. Now the distribution phase is managed shifting spikes that may be present inside PEs.

Figure 4.2. Block diagram of the new pipelined architecture of the multiprocessor array. REG corresponds to the spike\_out register.

When distribution starts, the highest row is stored in the spike buffer and each one below it scrolls in the corresponding row above. Spike buffer could contain at most a number of spikes equal to the column number (i.e. if all the PEs of the highest row have a spike, the buffer will contain all 1s), so the block requires to transmit all spikes of the row in question as many clock cycles as the number of PE owning a spike. To do this, spike buffer checks the position of 1s, then it transmits the first one detected and it resets that position. To transmit a spike, the PE array block (see appendix D.3 for the VHDL description) enables the *spike\_valid* signal and it loads *col\_sp* and *row\_sp* signals, which are the position of the spike to be distributed. When the buffer has only zeros (which is both the case where no PE has a spike or all the spikes of the row have been transmitted), the signal *next\_PE\_row* is enabled and it allows to shift the spike lines. A down-counter, called *PE\_array\_count* with initial equal to the row number, is used to know which row is loaded into the buffer and to end the transmission when it reaches the zero.

The propagation of spikes during the distribution phase is done generating all PE addresses that have a spike. 3 signals are involved to generate the address:

- *spike\_valid*: it is a control signal asserted when it is detected a 1 into the row loaded in the buffer. If there is a spike, that position is resetted and the address is generated in order to distribute it.

- col\_sp: it is the column address of the PE that has fired a spike. When spike\_valid is asserted, it means that a spike is detected into the buffer. Therefore, the column address of that spike is loaded in order to transmit it.

- row\_sp: it is the row address of the PE that has fired a spike. When spike\_valid is asserted, this signal is equal to PE\_array\_count, that is the down-counter position taking into account which row is loaded in the buffer and that is controlled in order to check if there are 1s.

Finally, distribution phase terminates when  $PE\_array\_count$  ends its count (it reaches the 0) and all the spikes in row n.0 are transmitted. When these two conditions happen, the control signal called  $eo\_spike$  is asserted and sent to the sequencer.

Regarding the architecture of PEs, the *spike\_out* register, used to store the possible spike during the execution phase, is used as pipeline register to store spikes of the rows below. *Spike\_out* has a size equal to the virtualization level, so if there is a virtualized array, this shift will involve it too. Now each processing element has only 3 signals used to manage the distribution phase (see appendix D.1 for the VHDL description):

• en\_spike\_tx: it is the control signal referred to the next\_PE\_row signal in the PE array block. When a shift of the spikes is required, this signal is asserted

and the *spike\_out* register is uploaded with the spike of the corresponding PE present in the row below.

- *spike\_out*: it is the spike output signal. When *en\_spike\_tx* is enabled, the spike of the PE is sent to the PE above using this signal.

- $spike\_in$ : it is the spike input signal. When  $en\_spike\_tx$  is enabled,  $spike\_out$  register is updated with this signal, that is the spike of the PE below.

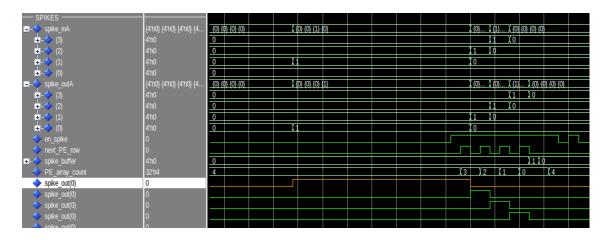

Figure 4.3. Simulation with QuestaSim of a spiking PE (orange line).

In Fig. 4.3 it is illustrated a simulation of a 4x4 array without virtualization: it means that VIRT=0, so the only position of  $spike\_out$  register to take into account is number 0. In particular it is shown the distribution phase of a spiking neuron: in fact the neuron in position [0,0] contains a spike (orange  $spike\_out(0)$  signal) and, when  $en\_spike$  is asserted, distribution starts.  $Next\_PE\_row$  is cycled 4 times because there are 4 shifts to do, so the counter resets in 4 cycles and it ends the distribution phase. Spike shifting is well displayed in the other  $spike\_out(0)$  signals, which correspond to the PE in position [1,0], [2,0] and [3,0]: therefore spike [0,0] shifts along its column, until reaching the  $spike\_buffer$ , which assumes a value equal to "0001" (1 in unsigned format on QuestaSim) at the 4<sup>th</sup> clock cycle, meaning that the PE in column 0 has a spike.

In this particular case, only the neuron in position [0,0] is spiking: if there were other PEs containing a spike, distribution could last longer.

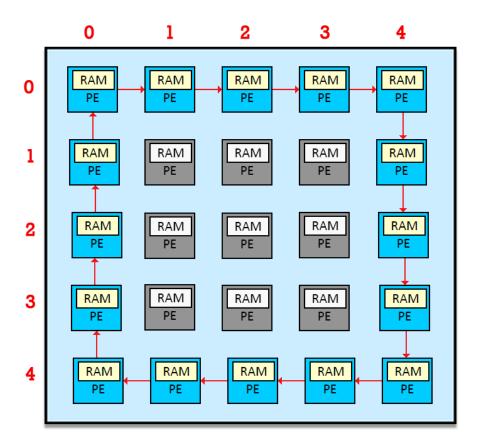

#### 4.2 Array Extension

After that the problem related to the potentially too long combinatorial path has been solved, it is possible to extend the size of the PE array without encountering problems of set-up time. Simulation done so far are made with an 4x4 array, so the next goal is to increase the size solving possible bugs that could happen, since the architecture was tested to work with a 4x4 array.

Once the number of rows and columns is increased, it is important to create and compile a netlist file that describes interconnections between neurons: actually, implementing simple paths permits easily to verify the correct behaviour of the architecture. In appendix C there are reported the netlists used to do the verifications. The format used to describe nets is shown in table 4.1.

| Source            |  |        |     |        | Destination       |                   |

|-------------------|--|--------|-----|--------|-------------------|-------------------|

| virtual_layer row |  | column | row | column | $synapse\_number$ | $synapse\_weight$ |

Table 4.1. Netlist format.

At this stage, virtualization is not yet implemented, so the virtual\_layer is always set to 0 and there is not a virtual\_layer destination, that has to be implemented when virtualization will be introduced. In addition to the location (row and column) of the source neuron, to the location of the destination one and to the synapse\_number, that is the specific synapse of the destination neuron that links both ones, it is possible to decide the synaptic\_weight. This field of the table is a decimal value that has to be written into R1 and R2 registers. Considering that weight value has to be into R1 and R0 and R0 are 16-bit registers, its corresponding binary value has to be left-shifted of 16 positions. In this way, the 16 less significant bits will be stored into the accumulator and the 16 MSBs, representing the synapse weight, will be stored into R0.

It is possible to create any kind of networks, linking one neuron to more than one, using different synapses. The first approach is to create a ring oscillator network, as the one shown in Fig. 4.4.

Figure 4.4. Block diagram of 5x5 ring oscillator network.

Using a ring oscillator as network is a good choice since there are few interconnections, so there are less signal to check and the distance between source and destination is the minimum one. It is important to configure the membrane potential in such a way that, if a neuron is stimulated by a single spike, it fires. If this condition is not satisfied, it is impossible to check if the spread of spike is correct, since if a neuron of the network receives a spike but it has not the sufficient membrane potential to fire, it will not produce a spike to send to the next neuron.

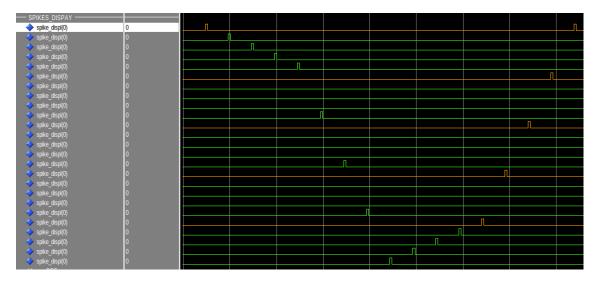

The first approach is to extend a bit the array to 5x5 PEs, to see if there are problems increasing the size more than 4x4. To display better the spike evolution, a signal called  $spike\_displ$  is used instead of  $spike\_out$ : actually,  $spike\_out$  is used also as pipeline register during the distribution phase, so it displays also the spike shifting, and it does not make readable the spike evolution. Therefore,  $spike\_displ$  has only visual utility, but it is not useful for the architecture functioning.

Simulation results are shown in Fig. 4.5. The distribution of spikes works as expected: pulses move along the first row and then they spread into the last column

and so on, closing the circle. It is possible to see that the distribution phase works well: the shorter impulses represent spike shifting along the respective column.

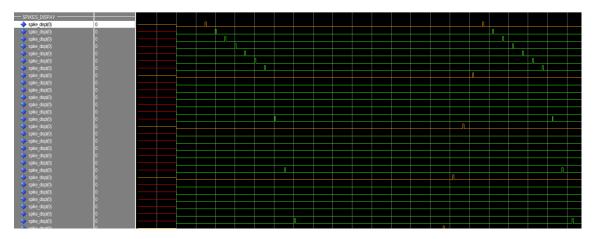

Figure 4.5. Simulation of 5x5 array using a ring oscillator configuration done with QuestaSim software. Row n.0 is in orange.

Then, the PE array size is extended to 10x10. In Fig. 4.6 it is shown the simulation result using a ring oscillator configuration as before.

Figure 4.6. Simulation of 10x10 array using a ring oscillator configuration done with QuestaSim software. Row n.0 is in orange.

An other test is to check if the system supports an array size with a number of columns other than the number of rows. In Fig. 4.7 it is shown the simulation of a 9x7 array, which therefore has an odd number of columns and rows.

Figure 4.7. Simulation of 9x7 array using a ring oscillator configuration done with QuestaSim software. Row n.0 is in orange.

Finally, the PE array size is extended to 16x16, that is the possible maximum size reachable in this project, since the architecture is optimized to support this size at most. In Fig. 4.8 it is shown the simulation result.

Figure 4.8. Simulation of 16x16 array using a ring oscillator configuration done with QuestaSim software. Row n.0 is in orange.

Since it is proved that the architecture works with ring oscillator network, the last test is to verify that it continues to work if the number of nets is increased. In Fig. 4.9 it is shown the netlist in appendix C.3. The path described, called "snake" for its shape, contains a lot of interconnections; moreover, distance between

source-destination neurons is still the minimum one, so the simulation remains easily readable.

Figure 4.9. Block diagram of 10x10 "snake path" network.

In Fig. 4.10 it is illustrate the snake path simulation. Also in this more complicate test, the distribution of spikes works as expected: pulses move along the first row and that they spread to the second one and so on. Also the distribution phase has not problems: even if a lot spikes need to be distributed, there are not time violations, so ti means that it is not necessary to modify the architecture speed (clock frequency is equal to 125MHz).

Figure 4.10. Simulation of 10x10 array using a "snake path" configuration done with QuestaSim software. Row n.0 is in orange.

#### 4.3 Synthesis and Implementation

After simulating the new spike pipeline, the system has to be tested on a board. Originally, the system was implemented on a KC705 development board that contains a Xilinx XC7K325T Kintex 7 FPGA. The design has been migrated to an MPSoC device to enhance the system configurability and monitoring, thus design synthesis and implementation are done with *Vivado* software on Xilinx Zynq-7000 SoC ZC706, that is shown in Fig.4.11: the devlopment board contains a SoC FPGA device, that integrates both processor and FPGA architectures into a single device. Consequently, it can provide higher integration, lower power, smaller board size and higher bandwidth communication between the processor and FPGA: in particular, the Zynq®-7000 SoC family integrates the software programmability of an ARM®-based processor with the hardware programmability of an FPGA.

Figure 4.11. Xilinx Zynq-7000 SoC ZC706.

First step is the synthesis: during this process, *Vivado* checks the compliance with all the constrains in function of the board used and other issues related with time execution latches, which are not detected in the simulation with *QuestaSim*. Also the utilization of the FPGA and its resources (Block RAM, Registers, LUTs...) are computed.

After the synthesis, the implementation has been done: it is a time-consuming process, especially if the array has high dimension, because the software generates all the components to be placed on the FPGA, with all the connections, taking into account the distance between registers and calculating the worst delay to determine

if there are time problems.

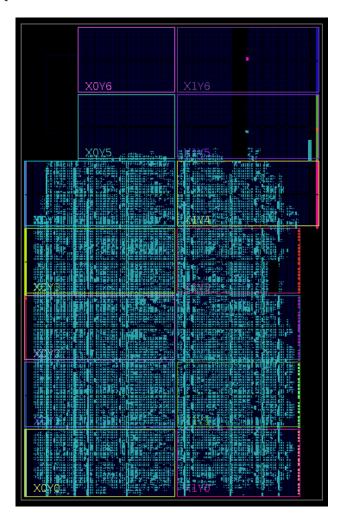

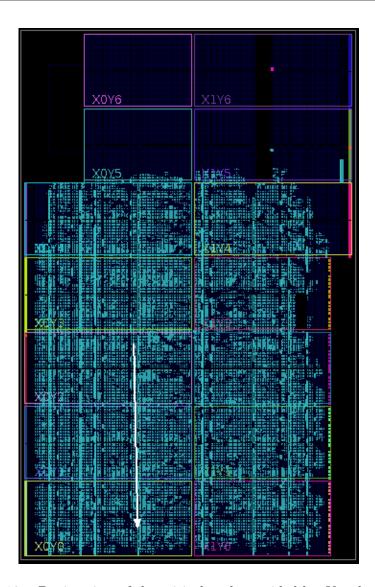

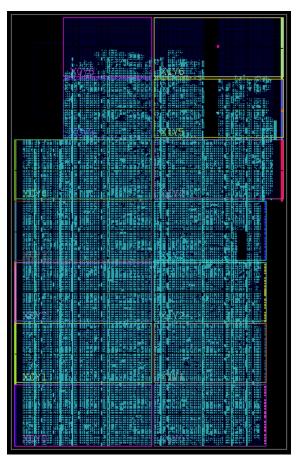

Figure 4.12. Floorplanning of a 10x10 array done with *Vivado* software.

In Fig.4.12 it is shown in blue the area occupancy of the 10x10 multiprocessor array: it is not the maximum possible one, because there is unoccupied space, so it means that on this board it is possible to go beyond 100 PEs.

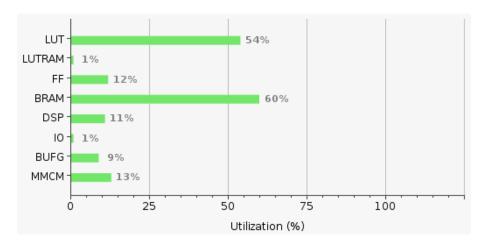

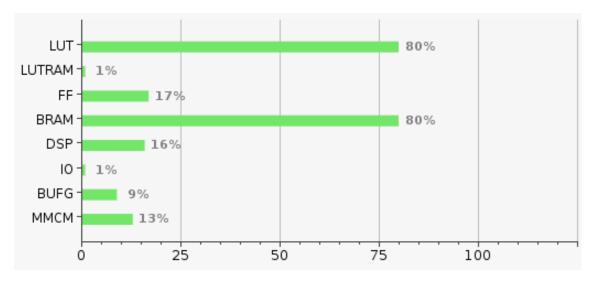

Regarding the resource occupancy, in Fig.4.13 it is shown which are the components of the whole device that use more resources. Rather than logic, BRAMs represent the bottle neck of *HEENS*: with a 10x10 multiprocessor array, they fill 60% of available space, so this means that with this board it is possible to reach an array size equal to 12x12 or 13x13 in the best case. In these forecasts, the virtualization implementation is not considered: theoretically, it will not have much effect on area problems, because the number of PEs will not change and only few control signals and components (such as counters and registers) are planned to be implemented.

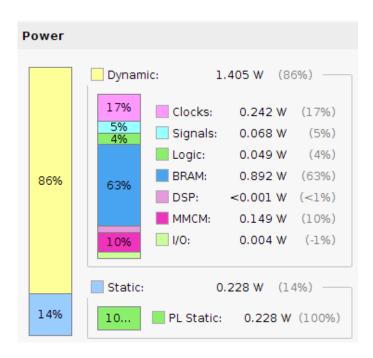

Power report, shown in Fig.4.14, also confirms that BRAMs are the most critical component, due to they are the biggest source of dynamic power consumption. Of course these figures are just presented as an orientation, since power estimation is highly dependent on the resource operation.

Figure 4.13. Area utilization of the whole architecture with 10x10 multiprocessor array done with Vivado software.

Figure 4.14. Power report of 10x10 array done with Vivado software.

Finally, the time report gives informations about time constraints. Fig.4.15

shows both clock frequencies adopted: the first one  $(125 \ MHz)$  is the proper clock used by the architecture; second one  $(200 \ MHz)$  is used, instead, by the AER-SRT controller.

| Q                                     |                |             |                 |

|---------------------------------------|----------------|-------------|-----------------|

| Name                                  | Waveform       | Period (ns) | Frequency (MHz) |

| <pre>v clk_in1_p</pre>                | {0.000 2.500}  | 5.000       | 200.000         |

| clk_out1_clk_wiz_0                    | {0.000 4.000}  | 8.000       | 125.000         |

| clkfbout_clk_wiz_0                    | {0.000 2.500}  | 5.000       | 200.000         |

| dbg_hub/inst/BSCANID.u_xsdbm_id/SWITC | {0.000 16.500} | 33.000      | 30.303          |

Figure 4.15. Clock summary provided by *Vivado* software.

Moreover, table 4.2 shows the slack values obtained during the synthesis. Slack is defined as the difference between actual or achieved time and the desired time for a timing path: it determines if the design is properly working at the specified frequency. Setup Slack is defined as:

$$SetupSlack = DataRequiredTime - DataArrivalTime$$

(4.1)

where "Data Required Time" is the time taken for the clock to traverse through clock path and "Data Arrival Time" is the time required for data to travel through data path.

A positive setup slack, as the one obtained, means design is working at the specified frequency and it has some more margin as well. Since speed is not a goal of this architecture, it is preferred to keep this margin in order to do not have possible problems in future implementations that could increase the critical path.

| Type        | Worst Slack | Total Violation | Failing Endpoints | Total Endpoints |

|-------------|-------------|-----------------|-------------------|-----------------|

| Setup       | 0.190~ns    | 0.000~ns        | 0                 | 162938          |

| Hold        | 0.054~ns    | 0.000~ns        | 0                 | 162938          |

| Pulse Width | 3.232~ns    | 0.000~ns        | 0                 | 55359           |

Table 4.2. Report timing summary provided by *Vivado* software.

These time results, that confirm there are not any time violations, testify that pipeline stages are able to solve timing problems which the system was affected from. Actually, in Fig.4.16 there is shown the time report of the original architecture, without pipeline stages.

| Implemented Design - impl_1   xc   | 7k325tffg9 | 00-2 (ad  | ive)           |            |             |                         |                   |           | ×     |

|------------------------------------|------------|-----------|----------------|------------|-------------|-------------------------|-------------------|-----------|-------|

| Timing - Timing Summary - timing_1 |            |           |                |            |             |                         |                   | _ B C     | ×     |

| □    □    □    □    □    □    □    | ∢ Intra-C  | lock Path | ns - clk_out1, | _clk_wiz_0 | - Setup     |                         |                   |           |       |

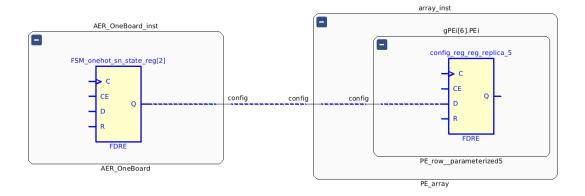

| -General Information               | ⊦ Q N      | ame       | Slack A        | 1 Levels   | High Fanout | From                    |                   |           |       |

| —Timer Settings                    | ₹ P        | ath 1     | -1.59          |            |             | seq_inst/state_reg[2]/0 | array_inst/gPEI[0 | ].PEI/gPE | E)[2] |

| —Design Timing Summary             | <b>₹</b> ₽ | ath 2     | -1.56          | 3 14       | 434         | seq_inst/state_reg[2]/0 | array_inst/gPEi[0 | ].PEi/gPE | Ej[2] |

| —Clock Summary (5)                 | × ₹ P      | ath 3     | -1.54          | 6 16       | 690         | seq_inst/state_reg[2]/0 | array_inst/gPEi[2 | ].PEi/gPE | E)[2] |

| e-Check Timing (6148)              | Dell 2 P   | ath 4     | -1.53          | 1 14       | 4306        | seq_inst/state_reg[2]/0 | array_inst/gPEi[1 | ].PEi/gPE | Ej[2] |

| ntra-Clock Paths                   | - P        | ath 5     | -1.51          | 6 13       | 4306        | seq inst/state reg[2]/0 | array inst/gPEi[1 | ].PEi/gP8 | E][2] |

| ∮−clk in1 p                        | 🔷 🦈 P      | ath 6     | -1.51          | 3 14       | 4306        | seq_inst/state_reg[2]/0 | array_inst/gPEi[1 | ].PEi/gPE | Ej[2] |

| o-clk out1 clk wiz 0               | <b>→</b> P | ath 7     | -1.50          | 2 14       | 4306        | seq inst/state reg[2]/0 | array inst/gPEi[1 | ].PEi/gPE | Ej[2] |

| Setup -1.599 ns (10)               | <b>→</b> P | ath 8     | -1.49          | 4 14       | 2482        | seq_inst/state_reg[2]/0 | array_inst/gPEI[1 | ].PEI/gPE | E)[1] |

| -Hold 0.068 ns (10)                | <b>→</b> P | ath 9     | -1.49          | 3 14       | 4306        | seq_inst/state_reg[2]/0 | array_inst/gPEi[1 | ].PEi/gPE | Ej[2] |

| Pulse Width 3,232 ns (31)          | <b>₹</b> P | ath 10    | -1.49          | 0 14       | 4306        | seq_inst/state_reg[2]/0 | array_inst/gPEi[1 | ].PEi/gPE | E)[2] |

| ⊕-clkfbout clk wiz 0               |            |           |                |            |             |                         |                   |           |       |

Figure 4.16. Timing report of the architecture implementing a 10x10 multiprocessor array without pipeline stages [4].

The architecture has a 10x10 PE array, as the one tested in this chapter, and the setup slack results, whose worst case is equal to -1.599 ns, demonstrate how increasing the size of the array the previous structure was not able to guarantee the right functioning of the architecture.