# "Active Gate Switching Control of IGBT to Improve Efficiency in High Power Density Converters"

Thesis submitted in partial fulfilment of the requirement for the PhD degree issued by the Universitat Politècnica de Catalunya, in its Electronic Engineering Program

Hamidreza Ghorbani

Director: Dr. Prof. Jose Luis Romeral Martinez

Co-Director: Dr. Eng. Vicent Sala

My whole life belong to, my parents *Saleh Ghorbani* and *Zhaleh Sadeghi-nejad*, and my lovely wife *Neda Razzaghi* and our girl *Ariana*.

This Thesis presents to

The Lovely People of Terrassa

### **ACKNOWLEDGMENTS**

My sincere appreciation to my supervisors Prof. Romeral and Vicenc Sala, whose deep knowledge, vast experience, support and encouragement has made this work possible.

A special word of thanks to my wife and my parents who tirelessly supported me, and encouraged me in the difficult moments.

I also would like to thank the members of MCIA research group, to all of them for their friendship and support.

To amazing people of Terrassa, who have given me great moments and also a heart full of love to Cataluña and Spain.

### **Abstract**

Insulated gate bipolar transistor (IGBT) power semiconductors are widely employed in industrial applications. This power switch capability in high voltage blocking and high current-carrying has expanded its use in power electronics. However, efficiency improvement and reducing the size of products is one of main tasks of engineers in recent years. In order to achieve high-density power converters, attentions are focused on the use of fast IGBTs. Therefore, for achieving this desire the trend is designing more effective IGBT gate drivers.

In gate drive (GD) controlling, the main issue is maintaining transient behavior of the MOS-channel switch in well condition; when it switches fast to reduce losses. It is well known that fast switching has a direct effect on the efficiency improvement; meanwhile, it is the major reason of appearing electromagnetic interference (EMI) problems in switched-mode power converters.

Nowadays the most expectant of an active gate driver (AGD) is actively adjusting the switching transient through simple circuit implementation. Usually its performance is compared with the conventional gate driver (CGD) with fixed driving profile. As a result a proposed AGD has the capability of increasing the switching speed while minimizing the switching stress. Different novel active gate drivers (as feed-forward and closed-loop topologies) have been designed and analysed in this study. To improve the exist trade-off between switching losses and EMI problem, all effective factors on this trade-off are evaluated and considered in proposed solutions. Theoretical developments include proposed controlling methods and simulated efficiency of IGBTs switching control. The efficiency improvement has been pursued with considering EMI study in the proposed active gate controller. Experimental tests have been conducted to verify the design and validate the results. Beside technical aspects, cost study has also considered in the closed-loop GD. The proposed gate drivers are simple enough to allow its use in real industrial applications.

# **Contents**

|   | Acronyms                                                  | IV |

|---|-----------------------------------------------------------|----|

|   | List of Tables                                            | 8  |

|   | List of Figures                                           | 9  |

| C | hapter One – Introduction                                 | 13 |

|   | 1.1. Research Topic                                       | 14 |

|   | 1.2. Research problem                                     | 14 |

|   | 1.3. Hypotheses                                           | 15 |

|   | 1.4. Aims and objectives                                  | 16 |

|   | 1.5. Research Methodology                                 | 17 |

|   | 1.6. Chapter descriptions                                 | 18 |

|   | 1.7. References                                           | 19 |

| C | hapter Two – State of the Art                             | 23 |

|   | 2.1. IGBT Characteristics and Modelling                   | 24 |

|   | 2.1.1. IGBT                                               | 24 |

|   | 2.1.2. IGBT Modelling                                     | 25 |

|   | 2.1.2.1. Mathematical Model                               | 25 |

|   | 2.1.2.2. Hefner Model                                     | 26 |

|   | 2.1.2.3. Behavioural Model (Micro-Model)                  | 26 |

|   | 2.1.3. Effective Parameters in Gate Drivers               | 27 |

|   | 2.1.3.1 Gate Resistor (Rg)                                | 27 |

|   | 2.1.3.2 The applied gate voltage signal (vgg)             | 29 |

|   | 2.1.3.3 Stray inductance (L <sub>S</sub> )                | 29 |

|   | 2.1.3.4 The inner parasitic capacitors (CGE, CGC and CCE) | 29 |

|   | 2.1.3.5 Junction temperature (T <sub>J</sub> )            | 30 |

|   | 2.1.3.6 Load variation                                    | 32 |

| 2.2. Classification of Gate Drivers                                            | 32 |

|--------------------------------------------------------------------------------|----|

| 2.2.1. Passive Feed-Forward Control                                            | 32 |

| 2.2.2. Open-Loop Control                                                       | 32 |

| 2.2.3. Closed-Loop Control                                                     | 33 |

| 2.3. Electro-magnetic Interference (EMI)                                       | 34 |

| 2.4. Control Methodology Approach                                              | 37 |

| 2.4.1. An introduction for POSICAST control                                    | 37 |

| 2.4.2. The basic concept of POSICAST                                           | 38 |

| 2.4.3. The principals of POSICAST controller                                   | 39 |

| 2.5. Conclusion                                                                | 40 |

| 2.6 References                                                                 | 42 |

| Chapter Three – Feedforward controller into the IGBT gate driver for switching |    |

| transient improvement_ Turn-on Condition                                       | 49 |

| 3.1. Introduction                                                              | 51 |

| 3.2. Concept of proposed controller                                            | 52 |

| 3.2.1. Turn-on behavior of IGBT                                                | 52 |

| 3.2.2. Structure and operation of the controller                               | 54 |

| 3.2.3. Tuning the controller                                                   | 56 |

| 3.3. Simulation and experimental results                                       | 59 |

| 3.3.1. System simulations                                                      | 59 |

| 3.3.2. Experimental test                                                       | 61 |

| 3.3.3 The effectiveness of new GD on junction temperature                      | 67 |

| 3.4. EMI                                                                       | 68 |

| 3.5. Conclusion                                                                | 70 |

| 3.6. Appendix                                                                  | 70 |

| 3.7. References                                                                | 71 |

| Chapter Four – A Feedforward Active Gate Voltage Control Method for SiC        |    |

| MOSFET Driving                                                                 | 75 |

|    | 4.1. Introduction                                                             | 77  |

|----|-------------------------------------------------------------------------------|-----|

|    | 4.1.1. Overview of Gate Drivers for Power Devices                             | 77  |

|    | 4.1.2. SiC MOSFET Gate Drivers                                                | 78  |

|    | 4.2. Active Gate Driver                                                       | 79  |

|    | 4.2.1. Principles of proposed controller                                      | 79  |

|    | 4.2.2. Parameters and limitations                                             | 82  |

|    | 4.2.3. Controller tuning                                                      | 83  |

|    | 4.2.3.1. Tuning for turn-on                                                   | 83  |

|    | 4.2.3.2. Tuning for turn-off                                                  | 83  |

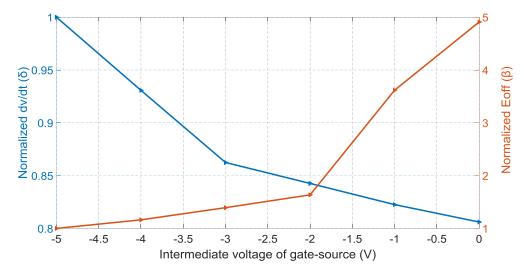

|    | 4.3. The process of validation                                                | 84  |

|    | 4.3.1. Test condition                                                         | 84  |

|    | 4.3.2. Optimized tuning                                                       | 84  |

|    | 4.4. Experimental validation                                                  | 87  |

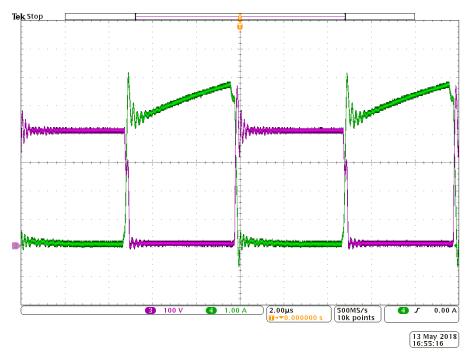

|    | 4.4.1. The test results                                                       | 87  |

|    | 4.4.2. Performance index                                                      | 90  |

|    | 4.5. Conclusion                                                               | 91  |

|    | 4.6. References                                                               | 91  |

| CI | napter Five – A Simple Closed-Loop Active Gate Voltage Driver for Controlling | g   |

|    | dic/dt and dvcE/dt in IGBTs                                                   | 95  |

|    | 5.1. Introduction                                                             | 97  |

|    | 5.1.1. Junction temperature (Tj)                                              | 98  |

|    | 5.1.2. The load variation                                                     | 98  |

|    | 5.1.3. IGBT's nonlinearity                                                    | 98  |

|    | 5.2. Closed-loop Active Gate Control Method                                   | 99  |

|    | 5.2.1. Philosophy of the method                                               | 100 |

|    | 5.2.2. The operation principles                                               | 103 |

|    | 5.3. The Closed-Loop GD Tuning and Experimental Results                       | 105 |

|    | 5.4. The Performance Index of closed-loop GD                                  | 109 |

| 5   | 5.4.1. The Comparison with CGD                                      | 109 |

|-----|---------------------------------------------------------------------|-----|

| 5   | 5.4.2. Electromagnetic Interference Analysis                        | 112 |

| 5   | 5.5. The Cost Study                                                 | 113 |

| 5   | 5.6. Conclusion                                                     | 114 |

| 5   | 5.7. References                                                     | 116 |

| Cha | apter Six – General conclusions and future work                     | 120 |

| 6   | S.1. General Conclusion                                             | 121 |

| 6   | 6.2. Future research plan                                           | 122 |

| 6   | 6.2.1. Closed-loop active gate driver of SiC MOSFETs                | 122 |

| 6   | 6.2.2. Stability analysing closed-loop active gate                  | 122 |

| 6   | 6.2.3. Applying the new closed-loop active gate on power converters | 122 |

| 6   | 6.2.3.1 Total harmonic distortion (THD) study                       | 122 |

| 6   | 6.2.3.2 Reliability Aspect                                          | 123 |

| Cha | apter Seven – Thesis results dissemination                          | 124 |

| 7   | 7.1. Publications                                                   | 125 |

# **Acronyms**

AC Alternating Current

AGC Active Gate Control

AGD Active Gate Driver

BJT Bipolar Junction Transistor

CM Common Mode

DC Direct Current

CGD Conventional Gate Driver

EMC Electro-Magnetic compatibility

EMI Electro-Magnetic Interface

FWD Antiparallel Freewheeling Diode

GD Gate Driver

HAGD Hybrid Active Gate Driver

IGBT Insulated Gate Bipolar Transistor

MOSFET Metal Oxide Semiconductor Field-Effect Transistor

PC POSICAST Control

PCB Printed Circuit Board

PI Proportional Integral

SOA Safe Operation Area

ST-HAGD Self-Tuning Hybrid Active Gate Driver

# **List of Tables**

| Table 2.1. IGBT Comparison                                                          |     |  |  |

|-------------------------------------------------------------------------------------|-----|--|--|

| Table 2.2 Parameters obtained from first I <sub>G</sub> turn-on overcurrent         | 41  |  |  |

| Table 3.1. The controller tuning parameters                                         | 60  |  |  |

| Table 3.2. The performance index                                                    | 61  |  |  |

| Table 3.3. The experimental turn-on performance index                               | 64  |  |  |

| Table 3.4. The experimental turn-on performance index                               | 66  |  |  |

| Table 4.1. Optimal V <sub>GS</sub> value in turn-on condition                       | 86  |  |  |

| Table 4.2 Optimal V <sub>GS</sub> value in turn-on condition                        | 86  |  |  |

| Table 4.3. The controller tuning parameters                                         | 87  |  |  |

| Table 4.4. The performance index                                                    | 91  |  |  |

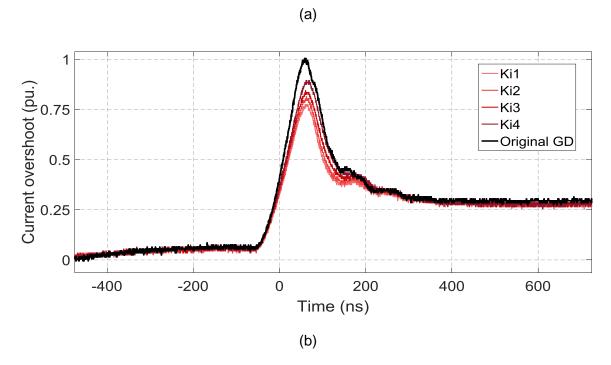

| Table 5.1. Collector current trajectory controlled by closed-loop GD with different | ent |  |  |

| Ki coefficients                                                                     | 106 |  |  |

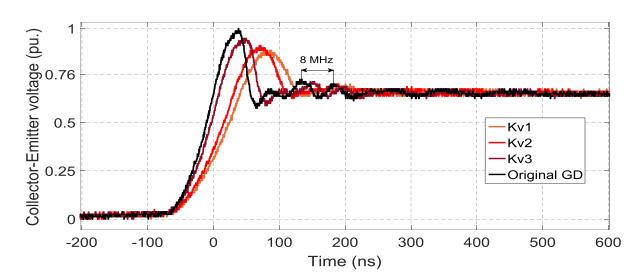

| Table 5.2. V <sub>CE</sub> trajectory controlled by closed-loop GD with different   |     |  |  |

| Kv coefficients                                                                     | 107 |  |  |

| Table 5.3. The performance index                                                    | 111 |  |  |

| Table 5.4. Cost and characteristic comparison                                       | 114 |  |  |

# **List of Figures**

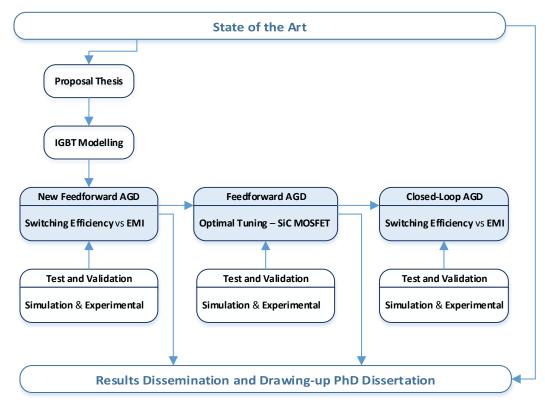

| Figure.1.1 Research Methodology Scheme                                               | 18 |

|--------------------------------------------------------------------------------------|----|

| Figure 2.1 the equivalent circuit of IGBT                                            | 24 |

| Figure 2.2 Equivalent circuit for hard switching                                     | 28 |

| Figure 2.3 Typical current and voltage waveforms                                     | 28 |

| Figure 2.4 Micro-model of an IGBT model                                              | 30 |

| Figure 2.5 Equivalent electric circuit of temperature transient case                 | 31 |

| Figure 2.6 Gate drivers with an adjustable output stage                              | 33 |

| Figure 2.7 Electromagnetic compatibility diagram                                     | 35 |

| Figure. 2.8 Conducted emission limits                                                | 36 |

| Figure. 2.9 Disturbance power limits for household                                   | 37 |

| Figure. 2.10 Sequence of movements in a gantry problem                               | 39 |

| Figure 2.11 Step-response of lightly damped system                                   | 40 |

| Figure 2.12 Open-loop half cycle Posicast                                            | 40 |

| Figure 2.13. Topology of test circuit with Posicast controller in gate driver        | 41 |

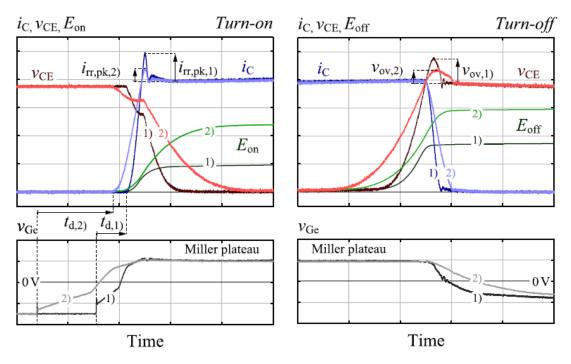

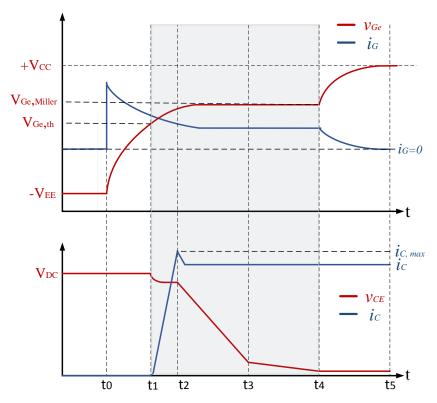

| Figure 3.1. The waveforms of the IGBT at turn-on transient condition                 | 53 |

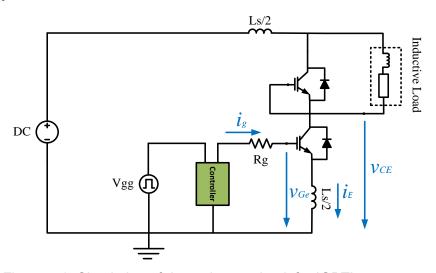

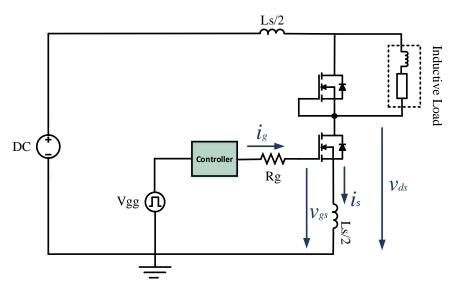

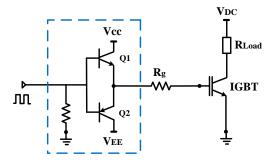

| Figure 3.2. The test circuit and the position of controller in the GD                | 55 |

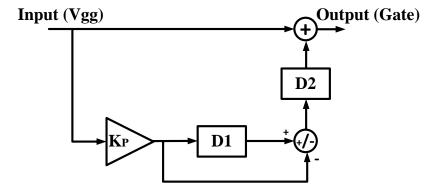

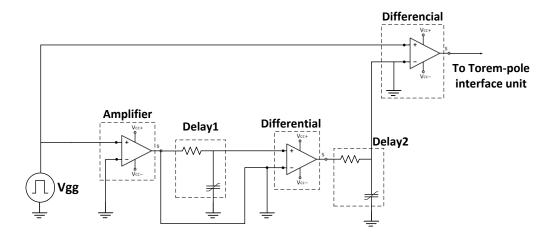

| Figure 3.3 Block diagram of the proposed feedforward controller                      | 55 |

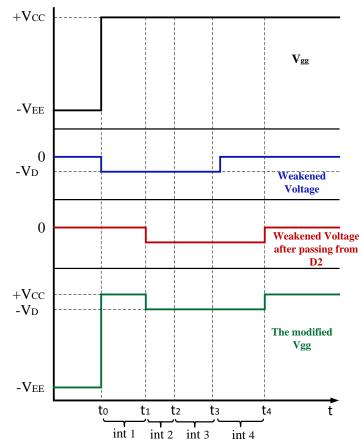

| Figure 3.4. Controller performance for Vgg modification                              | 56 |

| Figure 3.5. a) the general equivalent circuit for IGBT b) the equivalent circuit for | or |

| IGBT during                                                                          | 58 |

| Figure 3.6. Simulation of dynamic test circuit for IGBT's turn on control            | 59 |

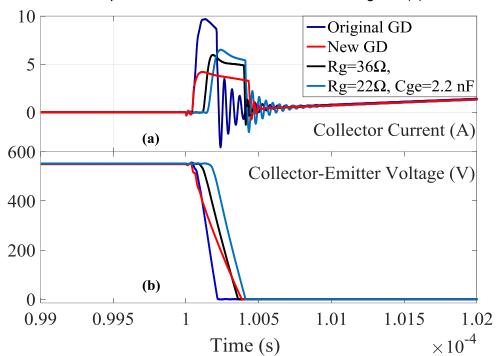

| Figure 3.7. The turn-on switching of IGBT with new GD and CGDs                       | 60 |

| Figure 3.8. The dynamic of voltage and current during turn-on by original GD         |    |

| (Rg= 18 ohms) at 20 KHz and 550 V                                                    | 62 |

| Figure 3.9. The dynamic of voltage and current during turn-on with improved      |     |

|----------------------------------------------------------------------------------|-----|

| driving circuit                                                                  | 63  |

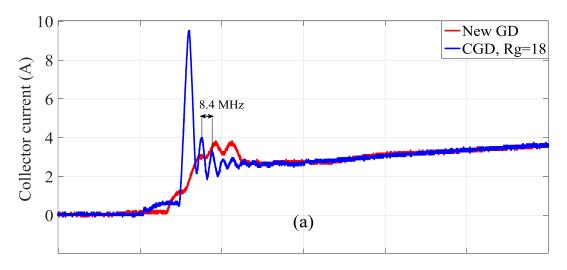

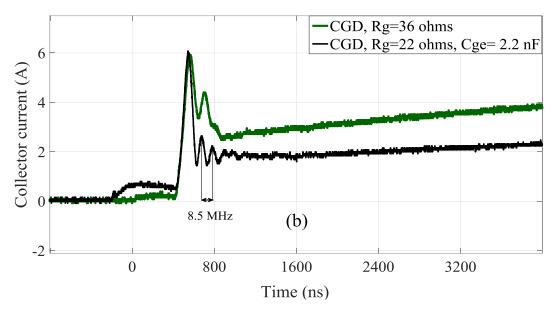

| Figure 3.10. The experimental results of collector current measurement results   | ant |

| from new GD and CGDs                                                             | 64  |

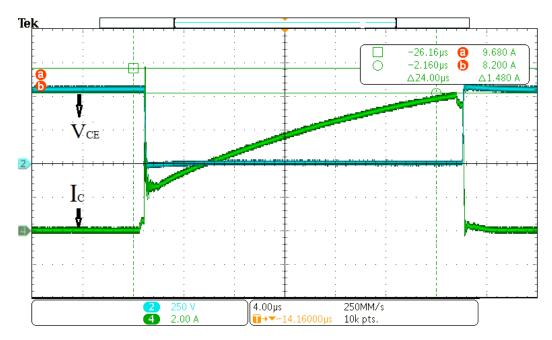

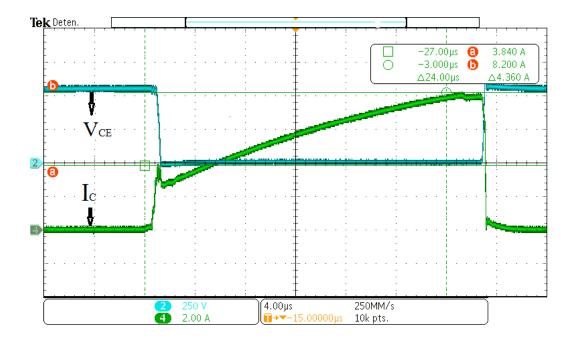

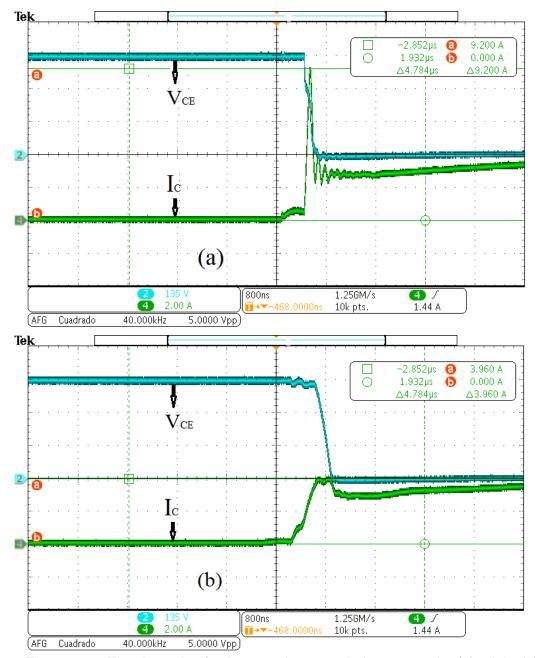

| Figure 3.11. The dynamic of voltage and current during turn-on by (a) original   | GD  |

| (Rg= 22 ohms) and (b) new GD                                                     | 65  |

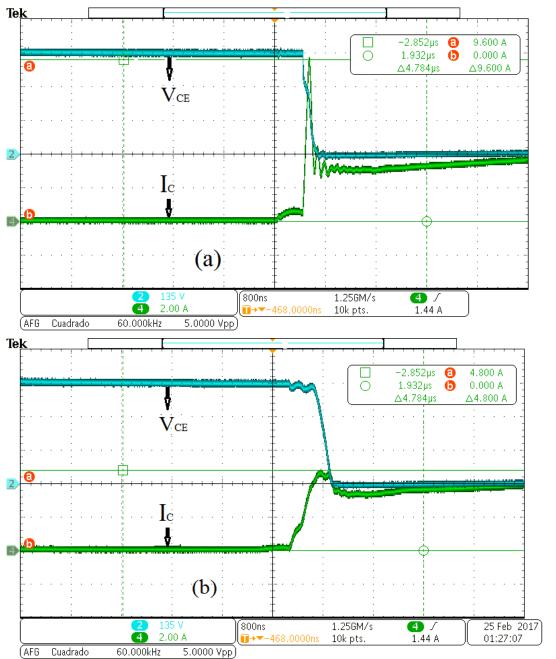

| Figure 3.12 The dynamic of voltage and current during turn-on by (a) original C  | ЭD  |

| (Rg= 22 ohms) and (b) new GD                                                     | 66  |

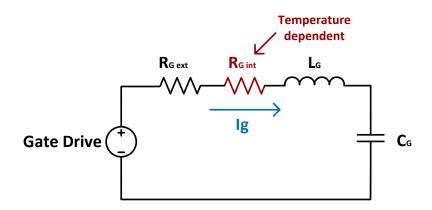

| Figure 3.13. Gate driver RLC network                                             | 67  |

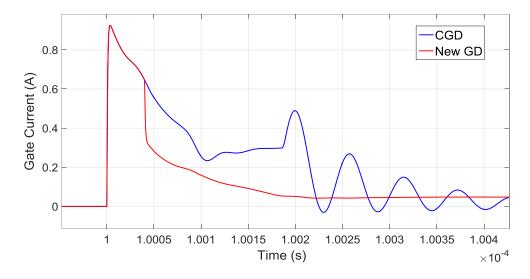

| Figure 3.14 Injected gate current during turn on, by CGD and new GD              | 68  |

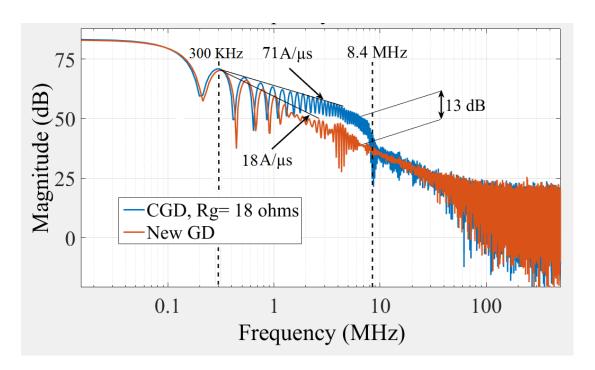

| Figure 3.15 Separated turn-on spectrum of measured currents for original GD      |     |

| and new GD                                                                       | 69  |

| Figure 3.16. The schematic of the proposed feedforward controller                | 71  |

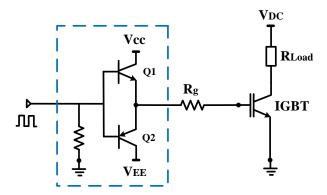

| Figure 3.17. Totem pole interface unit to gate current supply                    | 71  |

| Figure 4.1. Schematic of test circuit                                            | 79  |

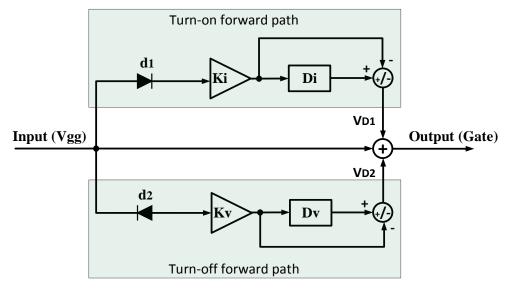

| Figure 4.2. Block diagram of the proposed feedforward controller                 | 80  |

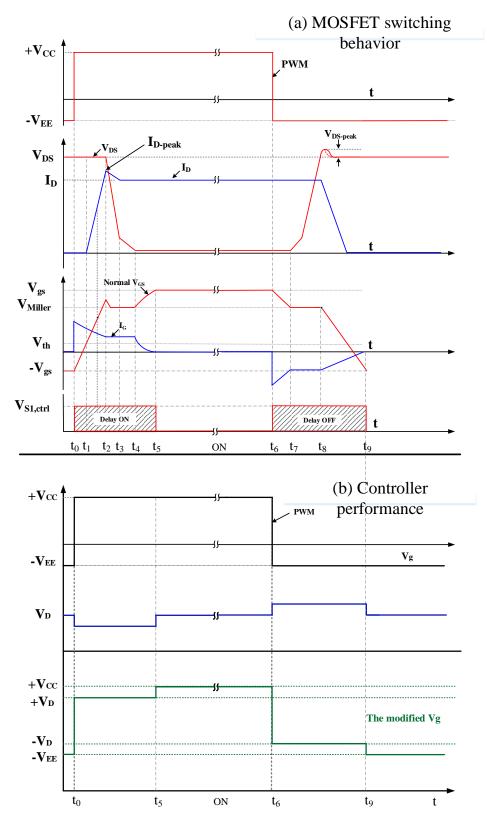

| Figure 4.3. (a) The transient behavior of MOSFET switching and (b) controller    |     |

| performance for Vg modification                                                  | 81  |

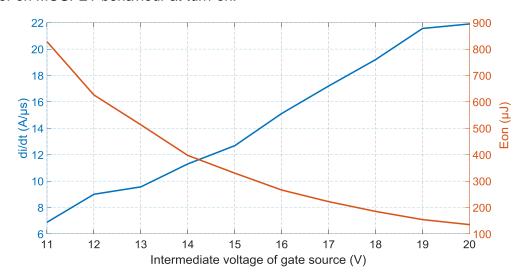

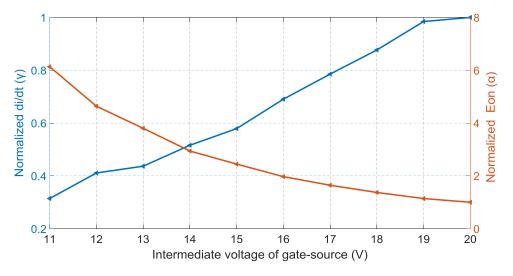

| Figure 4.4. The effect of intermediate gate-voltage levels on the peak value of  |     |

| current transient and did/dt while turn-on control domain                        | 83  |

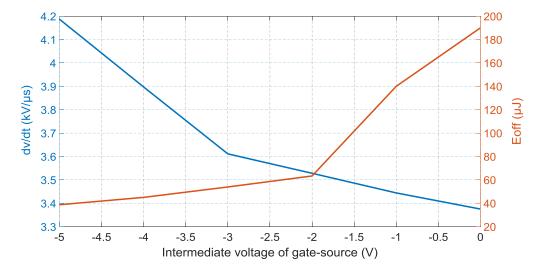

| Figure 4.5. The effect of intermediate gate-voltage levels on voltage transition |     |

| and voltage overshoot in turn-off control domain                                 | 84  |

| Figure 4.6. Optimal intermediate voltage for gate-source (V) at turn-on          | 85  |

| Figure 4.7. Optimal intermediate voltage for gate-source (V) at turn-off         | 86  |

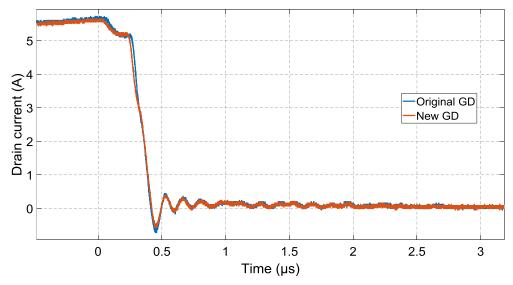

| Figure 4.8. Output voltage and current of MOSFET driven by original GD           | 88  |

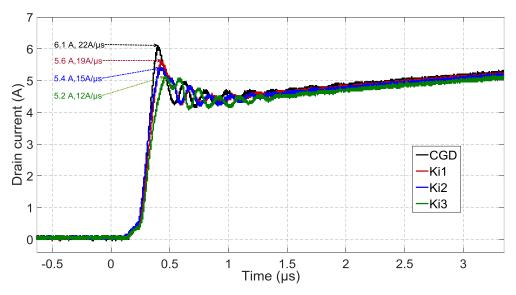

| Figure 4.9. Zoomed view of drain current with different Ki                       | 88  |

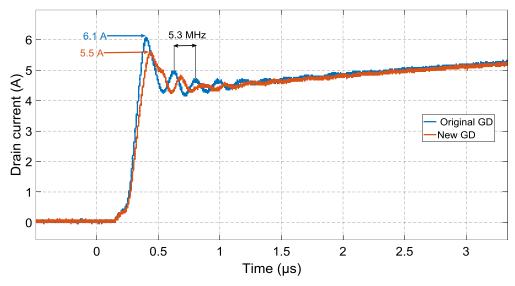

| Figure 4.10. Drain current with new GD (optimal tuning value) and original                 |     |

|--------------------------------------------------------------------------------------------|-----|

| GD at turning-on                                                                           | 89  |

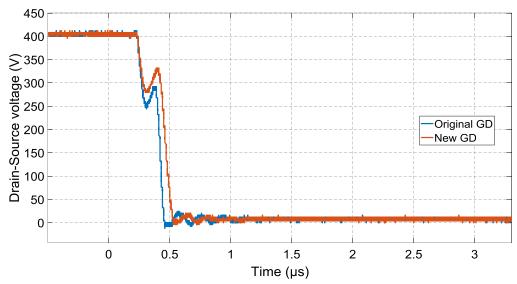

| Figure 4.11. Drain current with new GD (optimal tuning value) and original                 |     |

| GD at turning-off                                                                          | 89  |

| Figure 4.12. Drain-Source voltage with new GD (optimal tuning value) and                   |     |

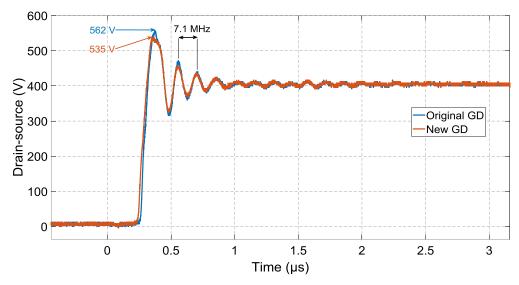

| original GD at turning-on                                                                  | 90  |

| Figure 4.13. Drain-Source voltage with new GD (optimal tuning value) and                   |     |

| original GD at turning-off                                                                 | 90  |

| Figure 5.1. The intrinsic behavior of IGBT at turn-on (a) and turn-off (b)                 | 102 |

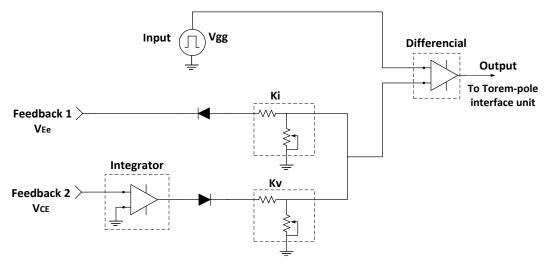

| Figure. 5.2. (a) The test circuit and the proposed controller in GD, (b)                   |     |

| General scheme of the controller                                                           | 103 |

| Figure. 5.3. Voltage type feedback signals originated from turn-on and                     |     |

| turn-off switching transients and corresponding modified vgg                               | 104 |

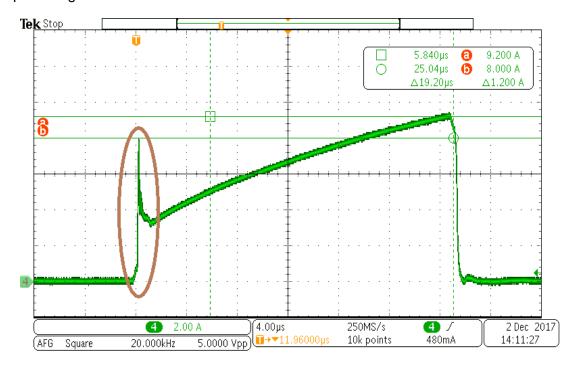

| Figure. 5.4. (a) The collector current waveform, performed by the original                 |     |

| gate driver. (b) The zoomed view                                                           | 106 |

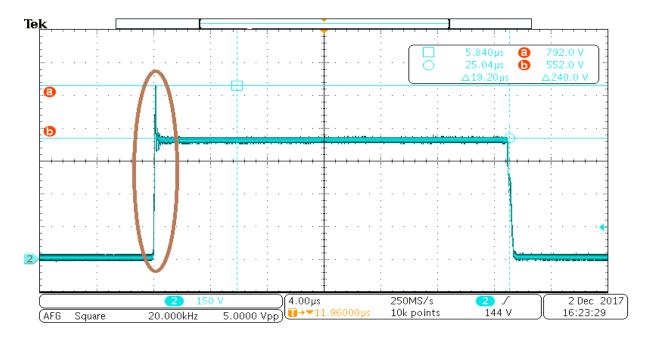

| Figure 5.5. (a) The waveform of collector-Emitter voltage, performed by the                |     |

| original gate driver. (b) The zoomed view                                                  | 107 |

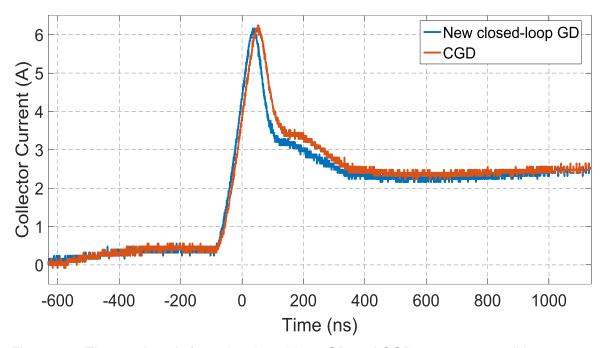

| Figure 5.6. The resultant iC from the closed-loop GD and CGD at turn-on                    |     |

| condition                                                                                  | 109 |

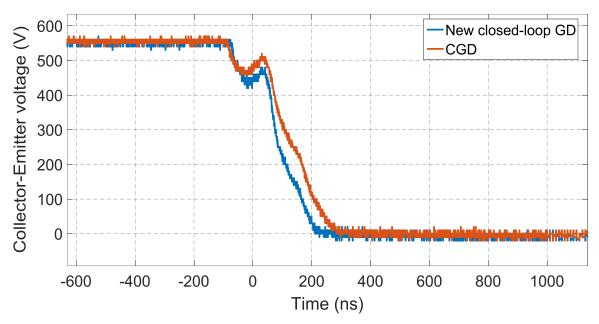

| Figure 5.7. The resultant vCE from closed-loop GD and CGD                                  |     |

| at turn-on condition                                                                       | 110 |

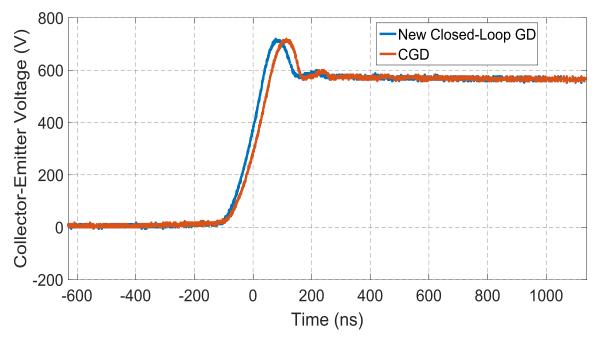

| Figure 5.8. The resultant VCE from closed-loop GD and CGD                                  |     |

| at turn-off condition                                                                      | 111 |

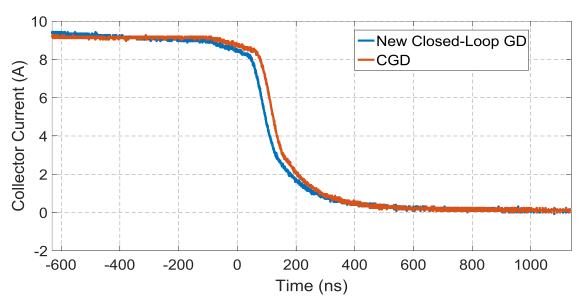

| Figure 5.9. The resultant iC from the closed-loop GD and CGD at turn-off                   |     |

| condition                                                                                  | 111 |

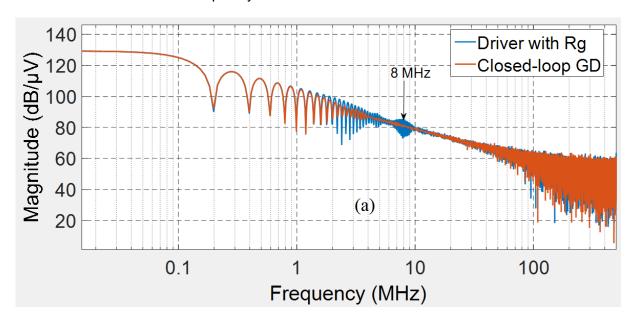

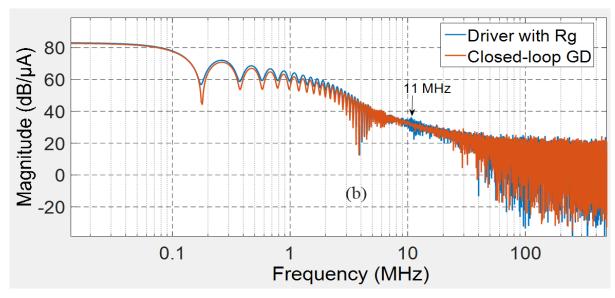

| Figure 5.10. The comparison of resultant spectrum between closed-loop                      |     |

| GD and CGD with Rg=12 $\Omega$ tested on $V_{\text{CE}}$ and $i_{\text{C}}$ experimentally | 113 |

| Figure 5.11. The schematic of the proposed closed-loop controller                          | 115 |

| Active Gate Switching Control of IGBT to Improve Efficiency in High Power Density Convert | ers |

|-------------------------------------------------------------------------------------------|-----|

|                                                                                           |     |

| Figure 5.12. Totem-pole interface unit to gate current supply                             | 115 |

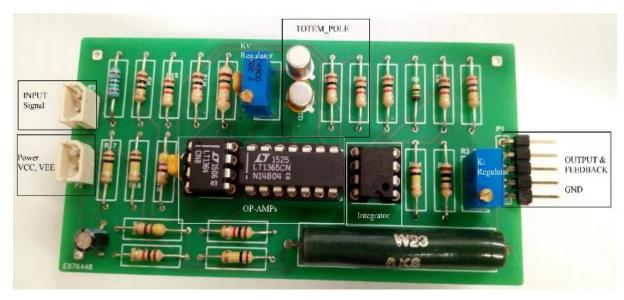

| Figure 5.13. AGD prototype manufactured                                                   | 116 |

### **CHAPTER**

# ONE

# Introduction

This chapter outlines the main lines of inquiry on which this thesis research is engaged. It takes the reader from an introduction of the research field to the thesis's contents, through the hypothesis statements and the exposition of the specific objectives.

# CONTENTS:

- 1.1. Research Topic

- 1.2. Research problem

- 1.3. Hypotheses

- 1.4. Aims and objectives

- 1.5. Chapter descriptions

- 1.6. References

### 1.1. Research Topic

Insulated gate bipolar transistor (IGBT) power semiconductors with antiparallel freewheeling diodes (FWDs) are widely used in industrial. In order to achieve high power density converters many researches have been assigned to the efficiency improvement through minimizing switching losses [1]-[5]. Fast switching is the known solution for minimizing the losses which has encouraged engineers to design proportionate gate drivers. However, increasing switching speed imposes electrical stress on the device and also it is the major source of electromagnetic interference (EMI) in switched-mode power converters [6, 7]. Therefore, the exist trade-off between switching losses and EMI generation should be considered in GD designing. It will be more challenging when we are dealing with IGBTs which operate at high frequency under hard switching conditions.

Several factors for designing the IGBT gate driver are effective. In GD design, the most challenging task is the definition of  $di_{C}/dt$  and  $dv_{CE}/dt$  rates that are independent of other effective factors such as junction temperature, parasitic inductance, load current value and the coupled DC-link voltage etc. [8]. However, using a static gate resistor (Rg); in the drive circuit is known as a conventional solution for the switching control [8], [9]. The result of using conventional gate drive (CGD) is a sub-optimal compromise, which has an undesirable effect on the switching speed and switching losses of the IGBT. To overcome the inherent ineffectiveness of the CGD, many active gate control (AGC) have been reported [8]-[26].

Among the reported driving methods, the gate charge control by active gate voltage controlling or by active gate current driving are effective solutions [27]-[29]. This technic has been considered as a main control method for gate driving. The method has been developed through first as feedforward and then closed-loop controllers.

### 1.2. Research problem

• The first problem in this research is related to switching transient behaviour of the IGBT. Overshoot cancelation in current (ic) and voltage (vce) and elimination of oscillations are known issues for any control system. Many controlling methods were reported in scientific articles to improve the dynamic behavior of IGBTs current and voltage in switching time [10]–[29]. In fact, a proper AGC has significant benefit for IGBT from life time aspect [30] and it prevents to generate some noises in high frequency orders. In addition, the presence of oscillation potentially provokes some parasitic issues such as crosstalk problem in normal operation of converters [31, 32].

- Controlling the slope of collector current (di<sub>C</sub>/dt) and collector-emitter voltage (dv<sub>CE</sub>/dt) to keep them in desired value independent of effective-variable factors; such as junction temperature and load variation, is the main concern of GD designing. Determining a proper di<sub>C</sub>/dt in turn-on and dv<sub>CE</sub>/dt in turn-off conditions depend on the trade-off between switching losses and electromagnetic interference (EMI) problem.

- Efficiency improvement. As regards, the conductance loss is not depends on GD and it highly depends on physical feature of IGBT, hence; reduction of switching losses in both condition (E<sub>On</sub> and E<sub>Off</sub>) is a real solution for efficiency improvement. To achieve this goal, fast switching is a single possible solution which makes switching time smaller. However, the fast switching increases EMI problem that is another concern.

- EMI problem. In real condition, a stray inductance (L<sub>S</sub>) exists in the designed circuit and its value mainly depends on the designed PCB layout [33]. This undesired factor provokes some overshoot (and potentially oscillations) in both current and voltage profiles. On the other hand, fast switching and higher rate of di<sub>C</sub>/dt and dv<sub>CE</sub>/dt intensifies these transients.

- Despite a suboptimal performance of conventional GDs, they are simple enough to attracting industry confidence. In recent decays many perfect and novel GDs have been presented [8], [33]. However; using such controllers increase the cost and complexity of the GDs circuit. Designing a simple and more effective AGD which can compete with CGD is one of main problems in this research.

### 1.3. Hypotheses

In order to address the presented research problems, the following hypotheses have been mentioned as a starting point for this research work:

- Designing mathematical and electrical model of an active gate controller for IGBTs under various load conditions will be necessary for simulation. In addition, the simulated AGD method will be developed based on application based concerns.

- Both switching losses and EMI phenomena affected by applied AGD will be considered in the evaluations. The inherent trade-off between efficiency and EMI must be improved by new AGD then the obtained results will be compared

to conventional gate drive (CGD) methods. The simulated studies will be verified by experimental tests in MCIA laboratory.

- An optimal AGD can be adjusted for Silicon Carbide (SiC) technology MOSFETs as new application. The designed optimal AGD will be validated in experimental environment.

- The presented AGD in feed-forward control method will be developed in close-loop control system as a self-tuned AGD for improving the performances of the power switch. The optimal design of closed-loop AGD is feasible in simulation and real test-bench.

In conclusion, applying new AGD (as feed-forward and close-loop) on high power converters is possible under different load characteristics. Thus, for a high density power converter an efficient and robust AGD will be designed.

### 1.4. Aims and objectives

Covering the mentioned problems of section 1.2 are the main objectives of this dissertation. In general terms, the final goal of this thesis is to develop a controlling system for gate driver of IGBTs and to evaluate switching transient behavior and efficiency with respect to EMI issues. In the following these objectives will be explained in more details:

### Objective I:

To propose an effective gate driver for IGBTs. Proposed controllers should be designed to improve the switching transient behaviour. It means, overshoot and oscillations should be reduced in the profiles of current ( $i_C$ ) and voltage ( $v_{CE}$ ). For performance evaluation, the obtained results must be compared to conventional gate drivers (by changing  $R_g$ ). This is a main objective that is considered in chapter 3, 4 and 5 of the dissertation.

### **Objective II:**

The proposed GD should be developed to improve the exist trade-off between efficiency and EMI. Both subjects should be considered in the performance evaluation of the driver. The proposed controlling concept should be able to embed on feedforward and closed-loop control topologies. In each control format, improving the mentioned trade-off is the main objective. This objective will be discussed in chapter 3 (for feedforward GD) and chapter 5 (for closed-loop GD) of the dissertation.

### **Objective III:**

The developed GD controls the  $di_C/dt$  and  $dv_{CE}/dt$ . Controlling switching transient behavior continuously independent of effective-variable factors; such as junction temperature and load variation, is one of the main objectives of this dissertation. This objective will be faced in chapter 5 of the dissertation.

### **Objective VI:**

Other important objective is achieving a cost-effective and a simple controller with respect to the robustness factors. Therefore, cost study should be considered in the analysis. This objective briefly has been evaluated in chapter 5 of the dissertation.

### **Objective V:**

The optimal tuning of new AGD and then applying on SiC technology of MOSFET is other important subject that Chapter four is dedicated for this purpose. The performance index evaluation in each chapter will be considered.

## 1.5. Research Methodology

To use the available and appropriate scientific sources and building the state of the art was the first step. Proposing possible solutions for the considered problem was the next step. Implementation and achieving experimental results in order to derive proper conclusions was other important stage, and finally, publishing the conducted study, and its results.

Thesis supervisor is in charge of overseeing this project development, providing technical and scientific support. Weekly / monthly or unscheduled meetings have been held with him.

Review and analysis of state of the art was a continuous process. The theoretical and mathematical models were developed by simulations. According to the obtained results from conducted simulations, appropriate strategies and new active gate control methods were proposed.

Getting experimental resources in laboratories of MCIA research center in Terrassa, based on simulation results, was the advanced level of verification.

Finally, the results of experimental test helped us to improve and to fine the controllers and technical developments and all led to publish several papers and writing the current thesis.

The schematic of the research methodology regarding to main objectives is depicted in below diagram.

Figure. 1.1 Research Methodology Scheme

# 1.6. Chapter descriptions

A general review on different controlling algorithms is conducted in chapter two. The basics of active gate drivers and IGBT modelling are explained, and a brief review on different gate drive control methods for IGBTs is presented. Effective parameters in IGBT gate drivers and also EMI will be explained in this chapter. In addition, POSICAST controller as a primary idea is briefly reviewed. This idea will be developed and will be the basic concept of the proposed GDs.

In chapter three, a novel feedforward GD will be proposed to drive of IGBTs. The investigation has been limited to turn-on switching condition. In this chapter the performance of the proposed GD has been evaluated from switching efficiency and also EMI aspects. In this study, the concept, principles, and structure of the proposed control method will be provided and then, the performance of new GD will be evaluated by simulation and experimental results. The impact of the temperature on the proposed open-loop controller are presented as well. The EMI generation of the new gate driver will be compared with the conventional driver. The chapter closes with a discussion of presented controller and conclusion.

Chapter four proposed a new feedforward GD based on what has been presented in previous chapter. This chapter involves the entire switching condition (turn on/off), and the GD has been applied on SiC base technology of MOSFET. The conventional GD still is the base of comparison for the evaluation in this chapter.

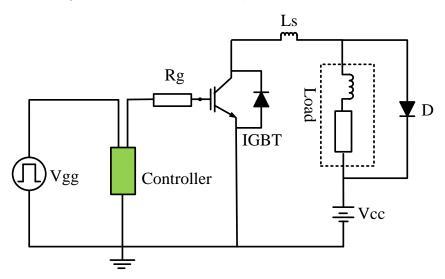

A new closed-loop gate driver for improving switching trajectory in IGBTs will be presented in Chapter five. The proposed closed-loop gate driver is based on an active gate voltage control method, which deals with emitter voltage ( $V_{Ee}$ ) for controlling dic/dt and it gets feedback from the output voltage ( $v_{CE}$ ) in order to control of  $dv_{CE}/dt$ . The sampled voltage-signals modify the profile of applied gate voltage ( $v_{gg}$ ). As a result, the desired GD improves the switching transients with minimum switching loss. The operation principle and implementation of the controller in the GD are thoroughly described. It can be observed that the new GD controls both  $dv_{CE}/dt$  and  $di_{C}/dt$  accurately independent of the variable parameters. The new control method is verified by experimental results. The known trade-off between switching losses and EMI is improved by this simple and effective control method.

In Chapter six, the thesis work is analyzed from a general point of view, and the conclusions and contributions are clearly exposed.

Finally, the publications and collaborations resulting from the research work development are presented in Chapter seven.

### 1.7. References

- [1] Sh. Yin, K.J Tseng, R. Simanjorang, P. Tu, "Experimental Comparison of High-Speed Gate Driver Design for 1.2-kV/120-A Si IGBT and SiC MOSFET Modules", IET Power Electronics, Vol. 10, no. 9, pp. 979 986, Mar. 2017.

- [2] Zh. Zhang, F-Fei. Li, Y-Fei. Liu, "A High-Frequency Dual-Channel Isolated Resonant Gate Driver With Low Gate Drive Loss for ZVS Full-Bridge Converters", IEEE Trans. Power Electronics, vol. 29, no. 6, pp. 3077 3090, Jun. 2014.

- [3] A. Paredes, V. Sala, H. Ghorbani, L. Romeral, "A Novel Active Gate Driver for Improving SiC MOSFET Switching Trajectory", IEEE Trans. Ind. Electron., vol. 64, no. 11, pp. 9032 9042, Nov. 2017.

- [4] F. Zhang, X. Yang, Y. Ren, L. Feng, W. Chen, "Advanced Active Gate Drive for Switching Performance Improvement and Overvoltage Protection of High-Power IGBTs", IEEE Trans. Power Electronics, Early Access Articles

- [5] A. Schindler, B. Koeppl, and B. Wicht, "EMC and switching loss improvement for fast switching power stages by di/dt, dv/dt optimization with 10ns variable current source gate driver," in Electromagnetic Compatibility of Integrated Circuits (EMC Compo), 2015 10th International Workshop on the, Nov. 2015, pp. 18–23.

- [6] C. R. Paul, Introduction to Electromagnetic Compatibility, 2nd ed. Hoboken, NJ: Wiley, 2006.

- [7] J. Biela, M. Schweizer, S. Waffler, and J. W. Kolar, "SiC versus Si—Evaluation of potentials for performance improvement of inverter and DC–DC converter systems by SiC power semiconductors," IEEE Trans. Ind. Electron., vol. 58, no. 7, pp. 2872-2882, Jul. 2011.

- [8] Lobsiger, Y, Kolar. J.W, "Closed-Loop di/dt and dv/dt IGBT Gate Driver", IEEE Trans. Power Electronic, Vol. 30, no. 6, pp. 3402 3417, June. 2015.

- [9] L. Shu, J. Zhang, F. Peng, and Z. Chen, "Active Current Source IGBT Gate Drive With Closed-Loop di/dt and dv/dt Control," IEEE Trans. Power Electron., vol. 32, no. 5, pp. 3787–3796, May. 2017.

- [10] V. John, B. S. Suh, and T. A. Lipo, "High performance active drive for high power IGBTs", IEEE Trans. Ind. Electron., vol. 35, no. 5, pp. 1108 1117, 1999.

- [11] S. Park and T. Jahns, "Flexible dv/dt and di/dt control method for insulated gate power switches," IEEE Trans. Ind. Appl., vol. 39, no. 3, pp. 657–664, May/Jun. 2003.

- [12] P. Palmer and H. Rajamani, "Active Voltage control of IGBTs for high power applications," IEEE Trans. Power Electron., vol. 19, no. 4, pp. 894–901, Jul. 2004.

- [13] L. Dulau, S. Pontarollo, A.Boimond, J.F. Garnier, N. Giraudo, O. Terrasse "A New Gate Driver Integrated Circuit for IGBT Devices With Advanced Protections", IEEE Trans. Power Electronics, Vol. 21, no. 1, pp. 38 44, Jan. 2006.

- [14] N. Idir, R. Bausiere, and J. J. Franchaud, "Active gate voltage control of turn-on di/dt and turn-on dv/dt in insulated gate transistors," IEEE Trans. Power Electron., vol. 21, no. 4, pp. 849-855, Jul. 2006.

- [15] A. Bryant, Y. Wang, S. Finney, T. Lim, and P. Palmer, "Numerical optimization of an active voltage controller for high-power IGBT converters," IEEE Trans. Power Electron., vol. 22, no. 2, pp. 374–383, Mar. 2007.

- [16] P. Grbovic, "An IGBT gate driver for feed-forward control of turn-on losses and reverse recovery current," IEEE Trans. Power Electron., vol. 23, no. 2, pp. 643–652, Mar. 2008.

- [17] Y. Wang, P. Palmer, A. Bryant, S. Finney, M. Abu-Khaizaran, and G. Li, "An analysis of high-power IGBT switching under cascade active voltage control," IEEE Trans. Ind. Appl., vol. 45, no. 2, pp. 861–870, Mar./Apr. 2009.

- [18] P. Grbovi, F. Gruson, N. Idir, and P. Le Moigne, "Turn-on performance of reverse blocking IGBT (RB IGBT) and optimization using advanced gate driver," IEEE Trans. Power Electron., vol. 25, no. 4, pp. 970–980, Apr. 2010.

- [19] L. Chen, B. Ge, and F. Z. Peng, "Modeling and analysis of closed-loop gate drive," in Proc. IEEE Appl. Power Electron. Conf. Expo., Feb. 2010, pp. 1124–1130.

- [20] Lobsiger. Y, Kolar. J.W, "Closed-loop IGBT gate drive featuring highly dynamic di/dt and dv/dt control", IEEE Energy Conversion Congress and Exposition (ECCE), pp. 4754-4761, 2012.

- [21] K. Fink and S. Bernet, "Advanced gate drive unit with closed-looped di/dt control," IEEE Trans. Power Electron, vol. 28, no. 5, pp. 2587–2595, Aug. 2013.

- [22] L. Dang, H. Kuhn, and A. Mertens, "Digital adaptive driving strategies for high-voltage IGBTs," IEEE Trans. Ind. Appl., vol. 49, no. 4, pp. 1628–1636, Jul./Aug. 2013.

- [23] L. Michel, X. Boucher, A. Cheriti, P. Sicard, and F. Sirois, "FPGA implementation of an optimal IGBT gate driver based on Posicast control," IEEE Trans. Power Electron., vol. 28, no. 5, pp. 2569–2575, May 2013.

- [24] Z. Wang, X. Shi, L. M. Tolbert, F. Wang, and B. J. Blalock, "A di/dt feedback-based active gate driver for smart switching and fast overcurrent protection of IGBT modules," IEEE Trans. Power Electron., vol. 29, no. 7, pp. 3720–3732, Jul. 2014.

- [25] T. Lu, Z. Zhao, S. Ji, H. Yu, and L. Yuan, "Active clamping circuit with status feedback for series-connected HV-IGBTs," IEEE Trans. Ind. Appl., vol. 50, no. 5, pp. 3579–3590, Sep./Oct. 2014.

- [26] F. Zhang, Y. Ren, M. F. Tian and X. Yang, "A novel active gate drive for HV-IGBTs using feed-forward gate charge control strategy," 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Sep. 2015, pp. 7009-7014.

- [27] K.Fink, and S.Bernet, "Advanced Gate Drive Unit With Closed-Loop diC/dt Control", IEEE Trans. Power Electronics, Vol. 28, no. 5, pp. 2587 2595, May. 2013.

- [28] J.E. Makaran, "Gate Charge Control for MOSFET Turn-OFF in PWM Motor Drives Through Empirical Means", IEEE Trans. Power Electronic, Vol. 25, no. 5, pp. 1339 1350, May. 2010.

- [29] Bryant. A.T, Lu. L, Santi. E, Hudgins. J.L, Palmer. P.R, "Modeling of IGBT resistive and Inductive Turn-On Behavior", IEEE Trans. Ind. Appl., vol. 44, no. 3, pp. 904-914, May/Jun. 2008.

- [30] Bo Wang; Yong Tang; Ming Chen "Study on Electric Characteristic of IGBT at Different Junction Temperature" Asia-Pacific Power and Energy Engineering Conference, PP. 1-4, 2011.

- [31] S. Jahdi, O. Alatise, J.A.O. Gonzalez, R. Bonyadi, L. Ran, P. Mawby, Temperature and switching rate dependence of crosstalk in Si-IGBT and SiC power modules, IEEE Trans. Ind. Electron. 63 (2) (Feb. 2016) 849–863.

- [32] D.W. Peters, Turn-on delay time of MOS transistors, Proc. IEEE 56 (1) (1968) 89–90.

- [33] A. Paredes, V. Sala, H. Ghorbani, L. Romeral, "A Novel Active Gate Driver for Improving SiC MOSFET Switching Trajectory", IEEE Trans. Ind. Electron., vol. 64, no. 11, pp. 9032 9042, Nov. 2017.

# **CHAPTER**

# **TWO**

# State of the Art

In this chapter, a literature review is conducted on different aspects of IGBT gate drivers. These aspects include IGBT modelling, basic controlling methods of gate drivers, efficiency improvement methods and cancellation of EMI problems. Moreover, the basic ideas of proposed active gate controller are presented. After knowing the mentioned subjects, analysing the IGBT's behaviour will be easy to understand. Also, the initial idea of proposed active gate controller will be presented to figure out the trajectory of the development.

### CONTENTS:

2.7.

| 2.1. | IGBT Structure and Modelling         |

|------|--------------------------------------|

| 2.2. | Effective Parameters in Gate Drivers |

| 2.3. | Classification of Gate Drivers       |

| 2.4. | Electro-magnetic Interference (EMI)  |

| 2.5. | Control Methodology Approach         |

| 2.6. | Conclusion                           |

|      |                                      |

References

## 2.1. IGBT Characteristics and Modelling

#### 2.1.1. IGBT

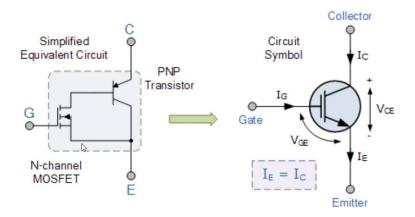

The Insulated Gate Bipolar Transistor (IGBT) is a semiconductor which inherently has combined from a Bipolar Junction Transistor (BJT) and a Field Effect Transistor (MOSFET). Thereby, it combines the advantages of MOSFETs and BJTs for use in power electronics and industrial circuits. The IGBT has inherited the best parts of these two types of common transistors. The high input impedance and high switching speeds of a MOSFET with the low saturation voltage of a bipolar transistor all in a semiconductor make it an attractive power switch. This hybrid combination makes possible to conduct a large amount of collector-emitter currents with negligible gate current. In fact, IGBT is an FET integrated with a BJT in a form of Darlington type configuration as shown in Figure. 2.1.

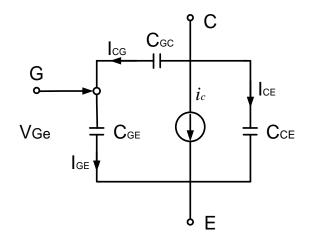

Figure 2.1 the equivalent circuit of IGBT

An IGBT is simply turned-on or turned-off by activating and deactivating its *Gate* terminal. Applying a positive input voltage signal across the Gate-Emitter bases (v<sub>Ge</sub>) will keep it in active region or ON state. To turn-off the device, the Gate-Emitter bases get a zero or slightly negative voltage signal. So, as simple as MOSFET switching, IGBT can be switched. In addition, IGBT has much lower on-state channel resistance than a MOSFET which makes it more efficient because of lower conducted loss.

Advantageously, IGBT only requires a small voltage pulse on its Gate to maintain conduction through Collector to Emitter, unlike BJT's which require a continuously Base current that should be sufficient enough to maintain saturation.

Unlike MOSFET, the IGBT is a unidirectional device, it means, the collector current (i<sub>c</sub>) only may flow through from Collector to Emitter. So, the current control is dedicated to the forward direction and the switch does not meet any reverse direction current. The advantage that

creates a better current profile in OFF switching condition (removing undershoot). Its consequence can be seen in the cancelation of EMI.

In general, the advantages of using the IGBT over other types of transistors can be listed as; high voltage blocking capability, low resistance while ON state (R<sub>ON</sub>), ease driving, fast switching and roughly zero gate drive current (i<sub>g</sub>). Thereby, IGBTs are attractive choice for industrial application like switch-mode power supplies or power converters which deals with high level of voltage and frequency.

A general comparison between IGBT's and BJT's, MOSFET's is presented in table 2.1.

| Device<br>Characteristic | Power<br>BJT                       | Power<br>MOSFET                | IGBT                             |

|--------------------------|------------------------------------|--------------------------------|----------------------------------|

| Voltage Rating           | High <1kV                          | High <1kV                      | Very High >1kV                   |

| Current Rating           | High <500A                         | Low <200A                      | High >500A                       |

| Input Drive              | Current, h <sub>FE</sub><br>20-200 | Voltage, V <sub>GS</sub> 3-10V | Voltage, V <sub>GE</sub><br>4-8V |

| Input Impedance          | Low                                | High                           | High                             |

| Output Impedance         | Low                                | Medium                         | Low                              |

| Switching Speed          | Slow (uS)                          | Fast (nS)                      | Medium                           |

| Cost                     | Low                                | Medium                         | High                             |

Table 2.1. IGBT Comparison

### 2.1.2. IGBT Modelling

Since 1985, most of IGBT models have been presented in scientific articles. Mainly they categorize based on the modelling method. Here the models are categorized into three different classes. Although the most of published IGBT models are developed for simulation of IGBT behaviour in circuits, some models like mathematical models are developed for analysing device operation mechanism. Such models mainly have focused on the device structure understanding.

The classified models are mentioned below:

#### 2.1.2.1. Mathematical Model

It is an analytical models based on semiconductor physics. The physical properties have expressed by mathematic equations. The expressions describe the electrical behavior. Layer by layer all parts in IGBT are described by mathematic equations. The obtained equations can be implemented into various simulators to emulate IGBT behavior for different applications.

Numerous early IGBT models were based on IGBT physics. The first time, IGBT Turn-off characteristic was modeled by Baliga [7], [8]. This analysis for IGBT behavior is a common

method and a recently complete physics-based analysis IGBT circuit model has been presented [9], [10]. This kind of modelling has a better accuracy but is more complex in parameter setting and model analysis.

### 2.1.2.2. Hefner Model

Hefner [13]-[16], developed the mathematical model as a combination of MOSFET and BJT (the equivalent circuits of that in reflected in figure 5.2). Although by Kuo et al [11], [12] the configuration was validated with discrete MOSFET and PNP transistors at turn-off, under resistive load condition. However, this model is not comprehensive for simulation because the MOSFET part, that is critical in transient simulation, has not been involved. The model was enlarged to a punch-through structure and a dynamic electro-thermal model [17], [18] as well. Similar to Hefner model, Kraus presented an interesting model. Although the both Hefner and Kraus models were experimentally verified, a direct comparison of the two methods has been presented in [19]. Due to the Hefner model depends strongly on the redistribution of charge into the drift region during switching, while the Kraus model mostly relies upon the process of charge extraction from the drift region by the electric field [20]. The conclusion is that the both models cannot be compared theoretically, and it is difficult to say which one is more realistic. In [19], a comparison of both models against experiment was done, the results showed that the Hefner model was found to be the more adaptive with experimental results and more robust as well. The Hefner model was also less sensitive to the inputs; for this reason, it was more challenging to extract the parameters for the Kraus model.

Gradually, Laplace transforms of the carrier transport equations were applied into an electrical sub-circuit to model the IGBT. Actually, Hefner method compromises between precision and simple of implementation. However, Hefner model is highly based on IGBT's physical structure which includes of a MOSFET and PNP.

### 2.1.2.3. Behavioral Model (Micro-Model)

The Hefner model relies on IGBT's physical structure. The Hefner model needs some physical parameters such as the drawn channel width and the drawn channel length parameters. Micromodel simulates IGBT behaviour without attention its physical structure. The requirement IGBT characteristics are applied by different ways. The resultant expressions, databases or components are then used in a simulator to model the IGBT. It consist IGBT electrical characteristics, thermal characteristics and etc. The micro model has simplified the IGBT's behaviour as a current source in a core. In [21], IGBT output characteristics were modelled by parasitic capacitors and current source. The nonlinear capacitors values and source current were obtained from an IGBT database. Specific characteristics of the IGBT that the previous sub-section has considered them are normally neglected in this category.

### 2.1.3. Effective Parameters in Gate Drivers

A gate driver provides the switching condition for IGBTs through applying a proportional voltage signal to the Gate-Emitter. Of course, it makes the required isolation for separating the control signals from the power side as well. The most important task for a GD is turning-on and turning-off the IGBT under proportional rates of dic/dt and dv<sub>CE</sub>/dt independent of the load effects [22].

To design an optimized GD, it is necessary to know which parameters have effect on the IGBT driving. This survey should be done with respect to below concerns.

- IGBT losses

- Reverse recovery current of the freewheeling diode

- Current overshoot in turn-on

- Voltage overshoot in turn-off

- EMI

The state of the art continues by describing the effective parameters on switching trajectory.

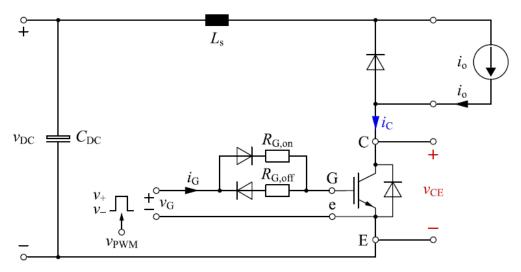

## 2.1.3.1 Gate Resistor (Rg):

Driving through changing the value of the gate resistor ( $R_g$ ), cf. *Fig. 2.2* is a very simple GD technique which widely has been used in industrial. This approach is known as conventional gate driver (CGD). The current and voltage waveforms at hard switching are highly depend on the values of  $R_g$ ,on/off. The GD with low resistors leads to increase absolute values of the gate current  $i_g$ , hence, IGBT switches quickly. Although that may create transients consequently, however, fast switching has benefit in enhancing the efficiency because of small switching time (reducing switching loss) [1]. Switching transients in current and voltage generates Electromagnetic Interference (EMI) issues. This subject is explained in 2.3 part in detail.

Figure 2.2, Equivalent circuit for hard switching including a push–pull gate driver. Ls represent the sum of the dc-link. (The figure retrieved from ref. [22]).

As shown in figure 2.3, both turn-on and turn-off modes are faster switching by lower  $R_{G,on/off}$  in compare with second condition which has higher  $R_{G,on/off}$ . The achieved advantage at fast switching results a lower efficiency. On the contrary, by slow switching we can see a low peak reverse recovery current ( $i_{rr}$ ), low turn-off overvoltage ( $v_{ov}$ ) and low EMI in consequence.

Figure 2.3, Typical current and voltage waveforms at hard switching by means of a push–pull gate driver during turn-on and turn-off using small 1) or large 2) gate resistors R<sub>g</sub>,on/off. The figure from [22].

A technique for determination of gate resistance ( $R_g$ ) value has been presented in [25]. The study was based on the analysing the equivalent circuit of a simple IGBT model. The extracted equations are mentioned below.

Equation 2.1

$$i_G = \frac{V_{gg} + - V_{Ge}}{R_G}$$

Equation 2.2

$$\frac{dv_{CE}}{dt} = -\frac{i_G}{C_{GC}}$$

$$\frac{di_C}{dt} \approx \frac{i_G}{C_{GE}} (g_m + v_{Ge} \frac{dg_m}{dv_{Ge}})$$

Equation 2.3

The equations show that the gate resistor may change the absolute value of the gate current ig, which affects to the transient behaviour of both voltage and current in output.

## 2.1.3.2 The applied gate voltage signal (vgg):

As can be seen in Eq. 2.1, the voltage value of gate signal is another effective factor to influence on gate current and switching behaviour. In fact, changing the voltage value of  $v_{gg}$  is other method to drive the IGBTs. Some benefits of this control method have been reported in articles [26], and some others evaluated the effect of this method on the junction temperature of the switch device [27]. However, the voltage value of the  $v_{gg}$  is an effective parameter on the transient behaviour of IGBTs.

## 2.1.3.3 Stray inductance (LS):

Stray or parasitic inductance  $L_S$  exists in all circuit paths and connectors. Figure 2.2 shows GD and the current path in the IGBT, the anti-parallel diode and stray inductance. In all paths and tracks of a circuit, the parasitic inductance can be gotten a value. However, as was assumed in [28] a single symbol is enough to present the total value of stray inductance in a circuit; so,  $L_S$  is an equivalent value for whole parasitic inductance.

The effect of stray inductance on the switching transients can be seen in below equations.

Equation 2.4

$$V_{CE,\,ov} = -L_s \frac{d_{ic}}{dt}$$

Equation 2.5

$$\frac{dic}{dt} = \frac{V_{DC} - V_{CE}}{L_s}$$

Equation 2.6

$$i_{rr} \approx \sqrt{Q_{rr} \frac{dic}{dt}}$$

Equation 2.4, shows the direct effect of  $L_S$  on the turn-off overvoltage  $V_{CE,ov}$ . At turn-on,  $L_S$  affects to the  $di_C/dt$  and consequently the peak reverse recovery current is being influenced by this factor. Equations 2.5 and 2.6 approve the role of this undesirable factor on IGBT switching. The elimination of stray inductance more than any other factor depends on the art of the hardware engineer while designing printed circuit board (PCB). The position of components, length and width of tracks, vicinity of DC routes with AC parts, the class of protection and martial of PCB all have a great effect on the value of this problematic parameter [28]-[30].

# 2.1.3.4 The inner parasitic capacitors (CGE, CGC and CCE):

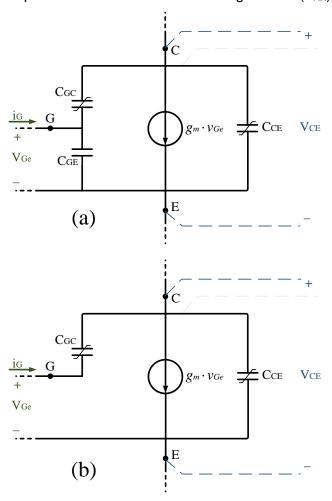

In order to produce high density power converters, operation in high frequency with fast switching is a necessity. In such condition one of the effective parameter in switching transients is inner parasitic capacitors of an IGBT. We know that the presence of parasitic capacitances in semiconductors is unavoidable and typically their values depend on the physical features. So, sometimes the proper selection of switch device is even effective than designing a good gate driver. The parasitic capacitance consists of the input capacitance, the reverse transfer

capacitance, and the output capacitance is expressed in [31]. The relations of inner capacitors between each other are presented in below equations.

Figure 2.4 Micro-model of an IGBT model

Equation 2.7

$$G_{iss} = C_{GE} + C_{GC}$$

Equation 2.8  $C_{rss} = C_{GC}$  Equation 2.9  $C_{oss} = C_{GC} - C_{CE}$

Where, in the inner parasitic capacitors;  $C_{iss}$  is IGBT input capacitor and  $C_{rss}$  is IGBT reverse capacitor. Also, the output capacitance ( $C_{oss}$ ) and Miller capacitance ( $C_{GC}$ ) roles are clear in above-mentioned expressions.

### 2.1.3.5 Junction temperature (TJ):

The change in junction temperature  $(T_J)$  of an IGBT may varies the characterises of an IGBT such as threshold value of gate-emitter voltage  $(v_{Ge,th})$ , injected gate current  $(i_g)$  and the nominal value of collector current  $(i_C)$  and collector-emitter voltage  $(V_{CE})$ . This can be a disturbance for operation of some gate drivers or at least it makes some extra consideration for controller designers.

Also, T<sub>J</sub> it is an essential parameter in determination of optimal point and reliability of an IGBT. So, the junction temperature should be considered in the power loss calculation and the analysis. The power losses in the converters can be classified as either conduction losses or switching losses. This classification depends on the thermal characteristics of the device [32].

Due to thermal capacitance, the transmission of thermal energy is not an instant parameter. The transfer time is related to the heat capacity, therefore, can be assumed that the thermal loss time is constant.

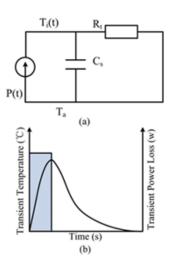

When the constant time ( $\tau$ ) is almost small, Eq. (2.10) is a roughly good approximation, where the heat capacity ( $C_S$ ) of the thermal transfer path and can be calculated from Equation (2.11). Equation (2.12) demonstrates the momentum value of a transient junction temperature. The equivalent electrical circuit for the transient case is illustrated in Figure 2.5 (a). The temperature variation induced by the transient heat transfer and the single-pulse power loss are shown in Figure 2.5 (b).

Equation 2.10  $\tau = (\pi.Rt.Cs)/4$  Equation 2.11  $Cs = Cv. \ A. \ d$  Equation 2.12  $T_i(t) = P_{loss} \ [4t/(\pi.Rt.Cs)]^{0.5} + Ta$

Figure 2.5 Equivalent electric circuit of temperature transient case and trend of temperature variation

When starting and in emergency steering, there are many changes in power consumptions. Because the time required for heat transfer is longer than the transition time, the junction temperature will increase rapidly. Equation (2.13) provides an approximate (the coefficients can be obtained from the manufacture's datasheet):

Equation 2.13

$$T_J=P_{DM}\times Z_{thJC}+T_C$$

Where  $T_J$  is the junction temperature,  $P_{DM}$  is the transient power loss,  $Z_{thJC}$  is the transient thermal resistance, and  $T_C$  is the ambient temperature. The transient pulse power is an important factor for calculating the transient temperature. The transient single-pulse power loss can be obtained from the manufacture's datasheet and the operating procedures.

### 2.1.3.6 Load variation:

The load variation is the main problem for passive and feedforward gate driver controllers [22]. This factor affects to the transient behavior of IGBTs. Especially in hard switching condition when IGBT operates under inductive loads, preserving the dv<sub>CE</sub>/dt and di<sub>C</sub>/dt in proportional slope rates is a serious issue for having EMI standards [33]. Moreover, the load and its demanded current have significant effect on the Miller plateau area in IGBT while turn on/off transients [34]. So, the load variation in value and feature may vary the switching times including turn-on/off delay time, turn-on/off rise/fall time and active/inactive region times. These changes may lead to appear cross-talk sometimes.

This factor like previous part may change IGBT's behaviour in gate side and all previous concerns are valid for this case as well.

### 2.2. Classification of Gate Drivers

In this part, the gate drivers are classified into three different categorizes. The classification subdivided into passive, open-loop and closed-loop control methods. The advantages and disadvantages of each one of them are discussed.

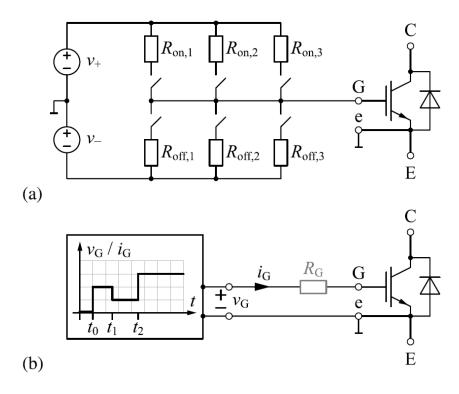

### 2.2.1 Passive Feed-Forward Control

Feed-forward controllers are individual adjustable drivers to regulate of dic/dt and dvcE/dt. Figure 2.6 is a simple instance of feed-forward controller for AGD of IGBT based on push–pull gate driver circuit. This method mainly controls the gate of an IGBT through applying an external gate resistor of external capacitors i.e.  $C_{GE}$  and / or a  $C_{GC}$ . The applied extra  $C_{GC}$  reduces the value of  $dv_{CE}/dt$  and the insertion of an extra  $C_{GE}$  slows down the  $di_{CE}/dt$  [35]. Simple structure and low complexity and also cheapness are the most important advantages of the feedforward controllers. However, the traditional version of this approach deals with longer switching delay and more switching losses [36]. The other scenario for gate driving by feed-forward method is the adjusting of the shape of applied gate voltage ( $V_{gg}$ ) [37]. This type of gate driver applies passively generated voltage slope to the Gate while turn-on condition. In fact the slope rate of dic/dt is defined by the specific slope of the gate voltage. This strategy is the same for controlling the gate-emitter voltage. So, a specific  $dv_{CE}/dt$  can be controlled by a specific slope of gate voltage signal.

This control method for solving some particular problems, according to its simple structure can be a candidate for GDs.

### 2.2.2. Open-Loop Control

An open-loop control is a stand-alone controller which could be applied in GDs for keeping gate current under control. This control method includes three different solutions: standard gate

driving (by employing switchable or adjustable gate resistors) [38], [39] see Fig 2.6, current-mode gate driving (gate current control) [40]-[44] and voltage-mode driving (gate voltage control) [45].

Figure 2.6 Gate drivers with an adjustable output stage by (a) switchable gate resistors and (b) switchable gate voltage or gate current source featuring discrete resistances / voltage / current levels.

In this method to control IGBT behaviour, the switching transients are subdivided into different / specific intervals based on each stage of switching behaviour. The open-loop controller applies its effect on a specific interval/s according to its scenario. Normally, this control method operates based on a fixed profile [46], an operating point dependent action [38], [47], or by getting feedback from the switching transients [34], [39], [48].

The main drawbacks of all passive and open-loop controllers are their disability to following circuit variations and their independent function regarding to the load and/or temperature variation. On the other hand, the tuning of an open-loop controller is more difficult because of its high sensitivity to defined parameters values. So, closed-loop concepts with negative feedback are applied to achieve a more precise control.

# 2.2.3. Closed-Loop Control

Unlike the open-loop or passive gate driving controllers, a closed-loop gate driver adapts IGBT with various non-linearity parameters continuously [22], [49]. Since, the performance of an IGBT with open-loop or passive gate drivers is not optimal (without getting feedback from variable

factors and output data) some problems like longer switching delay, lower immunity for noises and higher switching losses are expectable. Also, a closed-loop AGC targets transient improvement in order to mitigate EMI issues with many different control methods [22], [26], [34], [48], and [49].

Moreover, in hard switching condition that the dynamic of changes in temperature and profiles of output voltage and current are roughly high, closed-loop gate drivers may perform a perfect control to ensure the operation of the IGBT in the safe operation area (SOA) [49]. However, such controllers deal with feedback signals which make them more complex than previous controllers. Although such GDs have been designed to guarantee the stability and SOA against the perturbations conditions however, their presence complicates the structure of GDs and potentially can be a concern from economic aspect as well.

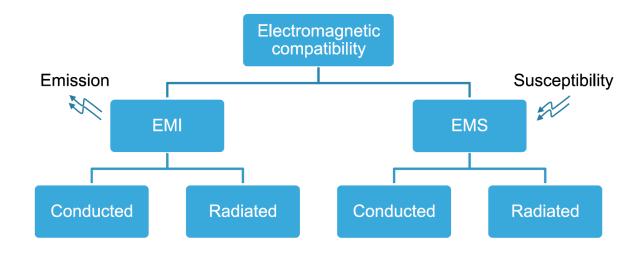

# 2.3. Electro-magnetic Interference (EMI)

Electromagnetic Compatibility (EMC) is the ability of electrical and electronic systems, equipment and devices to operate in their intended electromagnetic environment within a defined safety margin, without suffering or causing unacceptable degradation as a result of electromagnetic interference (ANSI C64.14-1992). The standard classifies EMC into electromagnetic interference (EMI) and electromagnetic susceptibility (EMS). Figure 2.7 demonstrates this classification with corresponding subclasses. In this thesis EMI is under focus which refers to disruptive electromagnetic energy transmitted from one electronic device or equipment to another. EMI emits its effects as:

- Conducted emission when it is propagated along a power line

- Radiated emission when it transmitted through free space

EMS represents the immunity factor against perturbations like electrostatic discharge (ESD), electrical fast transient (EFT), burst capacitive, surge immunity and electromagnetic waves [50].

Figure 2.7, Electromagnetic compatibility diagram

Power switches like IGBTs that have high dv/dt and di/dt rates are the main source of EMI [51]. Other sources for EMI are; microcontrollers (MCs), transient power components i.e. electromechanical relays and lighting.

As mentioned in the diagram, the EMI problem has been subdivided into conducted emission and radiated emission. In the case of conducted emission two mechanisms cause this noise which are the differential mode (DM) and common mode (CM) Noise. Conventionally, the DM noise is caused by switch current which only flows at the connecting line [51]-[53]. The high rate of dic/dt in turn-on condition may generate this phase of conducted emission. The source of the CM noise is related to high rates of dv/dt in turn-off condition. Also, the parasitic capacitors between device and the ground are other reasons for the advent of CM interferences [52] and [53]. As a result, in both switching conditions we should observe EMI consideration.

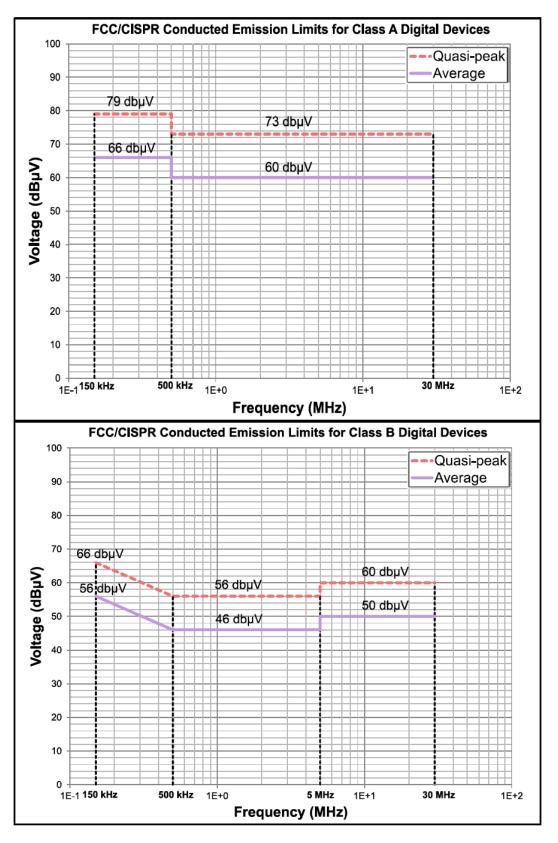

The standard [CEI EN 55022] limits the conducted emission noise in 150 kHz to 30 MHz frequency rang. This specification includes both industrial (class A) and domestic (class B) devices. The limits for conducted quasi-peak and average value emission are demonstrated in Fig 2.8. Although the conducted emissions are expressed as noise currents, they are measured in voltages as  $dB\mu V$ .

As can be seen in the figure, if each of quasi-peak and average emission values exceed from their defined limits the result of the conducted emission test will be failed. Of course we should consider the class (A or B) of the device under test (DUT) in our evaluations.

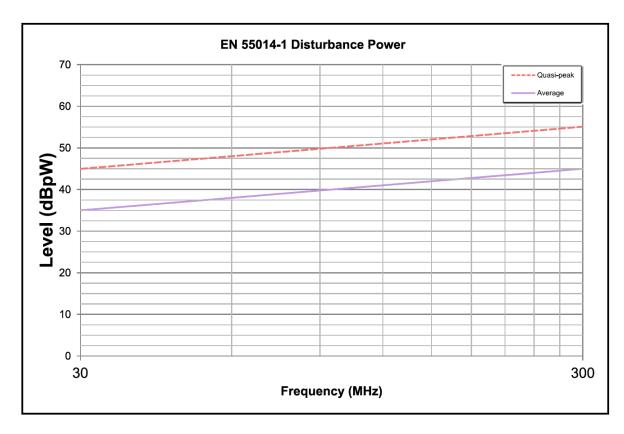

The other aspect of switching noise in EMI is radiated emission. All electronic components can emit electromagnetic fields. The emission of unwanted electromagnetic energy in the space may cause interference in the normal operation of a device with itself or with its adjacent devices [54]. The phenomenon which is known as radiated emissions can be measured through the disturbance power test. The corresponding standard [CEI EN 55014-1] for disturbance power test specifies the limits (in dBpW) in 30 MHz to 300 MHz frequency range for both quasi-peak and average values. Fig 2.9, shows the defined limits by standard. The presented limits in the figure are for household.

The frequencies above 30 MHz mainly are radiated by the power lines. Therefore, the disturbance power test can be measured via the power supplied by electrical equipment (in standard test condition) [54].

Figure. 2.8 Conducted emission limits [54]

Figure. 2.9 Disturbance power limits for household based on EN 55014-1 standard

#### 2.4. Control Methodology Approach

To find a proper solution for solving the mentioned problem in IGBT driving control, many control methods were studied. To find or creation of the desired controller, it must have same characteristics such as simple structure, applicable into GDs, flexible to use it as feedforward and closed-loop controllers, known as a robust controller and effective for cancelation of overshoot and oscillations.

POSICAST control method had all above features, so, the initial studies were done based on this control method. In this part, before introducing the concept of this controller, a brief history of POSICAST in different electrical and electronic applications is presented. The objective is better knowing this controller and its presence in science and industry.

#### 2.4.1. An introduction for POSICAST control

The POSICAST control method first was presented by Prof. Otto J. M. Smith. He described its basic principles in 1957 [55]. Then it became as a real solution for damping oscillations in mechanical systems and then after a decay in electrical systems [56]–[60]. The first case studies for this controller were related to mechanical applications; however, recently POSICAST-based feedback control has been used in the field of power electronics and electrical engineering. Reference [61] has proposed a digital POSICAST-based controller for a buck type DC-DC converter in order to obtain the advantage of POSICAST superior damping

qualities while reducing the sensitivity of classical feed-forward POSICAST. In addition, rather than a conventional (two-step) POSICAST, a three-step compensator based on the POSICAST concept has been presented in [62]. As a combination approach for damping of PWM current source rectifiers, this approach also was carried out in [63] for shaping the modulation signals for high switching frequency DC-DC converters, inverters and PWM rectifiers. For compensating the voltage sags and damping of high frequency oscillations at medium voltage of distribution system, an investigation of Dynamic Voltage Restorer (DVR) transient response was presented in [64]. Also, this study employed POSICAST into the closed-loop control for damping resonance problem. Recently, this controller has been introduced as a simple and effective solution for oscillation damping and improving dynamic behaviour in electrical power systems [65–68] as well.

Summarizing, the POSICAST is a feedforward controller which has been selected as a potential approach for active gate drivers. However, it has also been used in the topology of some closed-loop controllers. Despite its simple structure, the performance of this controller in damping the oscillations is highly effective.

#### 2.4.2. The basic concept of POSICAST

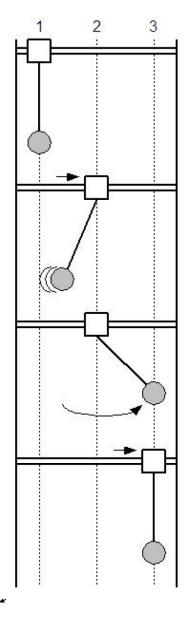

POSICAST is an effective feed-forward control method that damps disturbance-based oscillations in a well-tuned condition. This control method has enough capability to offer a transient response with deadbeat reflection.

The concept of POSICAST control can be described with an example. As illustrated in Fig. 2.10 we assume the moving a pendulum weight suspended by a string attached to a gantry. The heavy ball in the beginning has stayed at position '1'. The objective is to move the ball from the beginning position to position '3' without any unwanted oscillations in final position. In fact, because of the inertia law a rigid mass in an instant relocation will have some oscillation (depending on the weight and speed of the movement) around the final point. POSICAST solves this problem with applying a stop before destination. The duration and location of this stop is important to stay in the final destination without fluctuations. That way, first we should realize that in which point of the way the ball should stop till the ball reaches to position '3' in its maximum point of swing (finding position 2. see Fig. 2.10). Then we should know how long time it necessary to stop in position '2'. However, as the bob reaches position '3', the gantry immediately moves again to position '3'. As a result, the heavy ball will rest at its final position with minimum deviation [69].

Figure. 2.10 Sequence of movements in a gantry problem

#### 2.4.3. The principals of POSICAST controller

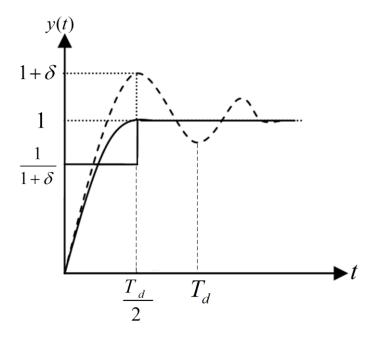

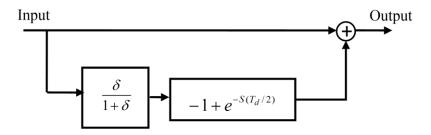

As mentioned before, Posicast is a feed-forward control that damps transient-based oscillations. Fig. 2.11 demonstrates an analytical form of Posicast response. The overshoot in the response is defined by two parameters: first "Td", which denotes the time of the underdamped response period; and then "1+ $\delta$ ", which is the peak value of the overshoot. The  $\delta$  denotes the normalized overshoot factor that ranges from zero to one [70]. Posicast divides the step-reference signal into two separate parts. In the classical half-cycle Posicast, which is shown in Fig. 2.12. The controller first subtracts a scaled amount from the input signal (in the lower path). Consequently, the peak of the lightly damped response coincides with the desired final value of the system response. The time of the peak step-response is equal to one-half of the natural damped period (Td/2). This path makes a time delay. Then, the original value of the input step signal is applied

to the system (in the upper path). Finally, the output remains at the desired final value. The system output is shown in Fig. 2.11 (solid line); the uncompensated output is also shown for comparison (dashed line). The Posicast is an open-loop controller; therefore, it has high sensitivity to the parameter variations or any mismatch problem. In some researches this weakness was compensated by applying a feedback into the controller [71].

Figure 2.11 Step-response of lightly damped system

Figure 2.12 Open-loop half cycle Posicast

#### 2.5. Conclusion

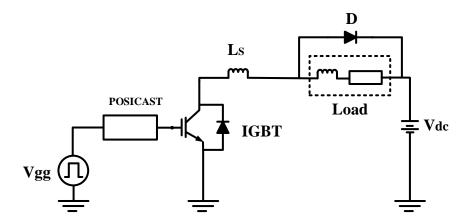

In preliminary studies, POSICAST feedforward controller was embedded into the gate driver of IGBT. The studies first were done by simulation analysis. The test circuit is shown in Fig. 2.13, where Posicast controller has been connected to the GATE. A single stray inductance was assumed to present the total stray inductance of the circuit; then,  $L_s$  is the equivalent parasitic inductance. A half cycle Posicast control (see Fig. 2.12) was applied into the GATE. Also, an inductive-resistive load by connection with an antiparallel diode has applied to the circuit. The test condition for the circuit is selected as  $V_{cc}$ =600v,  $I_c$ = 20A,  $V_g$ =  $\pm$ 15 v,  $R_g$ = 1 $\Omega$  and  $L_s$ =0.5 $\mu$ H. IGBT is switching in 20kHz frequency. The simulation is done in Simulink/MATLAB by fix

step time (t=1e<sup>-10</sup> sec). All technical characteristics and parameters of IGBT model are based on N-channel IGBT of NGTB20N60L2TF1G.

Figure 2.13. Topology of test circuit with Posicast controller in gate driver

As described in previous section, to design the Posicast controller only two parameters should be determined. First, the elapsed time of overshoot and the second parameter is the overshoot value. These parameters are obtained from the I<sub>G</sub> dynamic behavior (incl. second interval) in first turn-on switching, which are listed in table 1. Normally, in a specified condition, these transients are happening continuously.

Table 2.2 Parameters obtained from first I<sub>G</sub> turn-on overcurrent

| Parameter         | Value | Unit     |

|-------------------|-------|----------|

| δ                 | 0.34  | Per unit |

| T <sub>d</sub> /2 | 0.9   | Nano Sec |

The minimizing IGBT losses (through as much as fast switching) besides minimum switching stress (it can be warranted by slow switching) has almost always been a main purpose for gate driver designers. To achieve such trade-off, in this survey, suppressing dic/dt overcurrent by gate current controlling has been chosen as a solution.

As reported in many articles [55], [56], [66], [68]-[71] an open-loop half cycle POSICAST is a very sensitive solution. It means, its performance is highly dependence on the accuracy of the tuning. As can be seen in Table 1, to create 0.9 ns delay (in real test-bench) is a tough goal. Except the feasibility issue, many environmental factors potentially may affect to the created delay time.

On the other hand, the internal second order behaviour of IGBT is negligible. The step response appeared in IGBT's voltage and current (while switching) mainly caused by parasitic inductance

and/or capacitance of circuit's paths. So, even assuming complete removal of internal factors, we won't see significant improvements practically.

Hence, although POSICAST became as an inspirational way to design of gate driver however, this method was not used in the development process.

In the next chapter, feedforward control methods with respect to mentioned concerns are presented.

#### 2.6. References

- [1] Application Manual Power Semiconductors. E-Book. 2012.

- [2] B. J. Baliga, M. S. Adler, P. V. Gray, R. P. Love, and N. Zommer, "Insulated gate rectifier (IGR): A new power switching device," in Proc.Tech. Dig. IEDM, 1982, pp. 264–267.

- [3] K. Sheng, B.W. Williams, and S. J. Finney, "A Review of IGBT Models", IEEE Trans Power Electronics, Vol. 15, No. 6, pp. 1250- 1266, Nov. 2000.

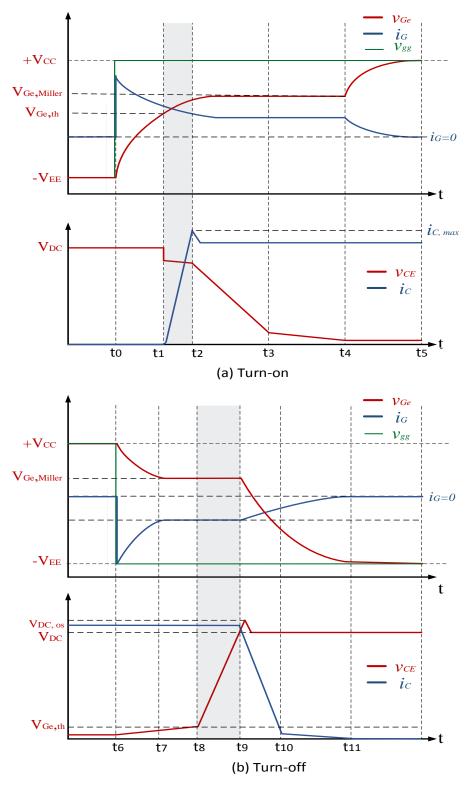

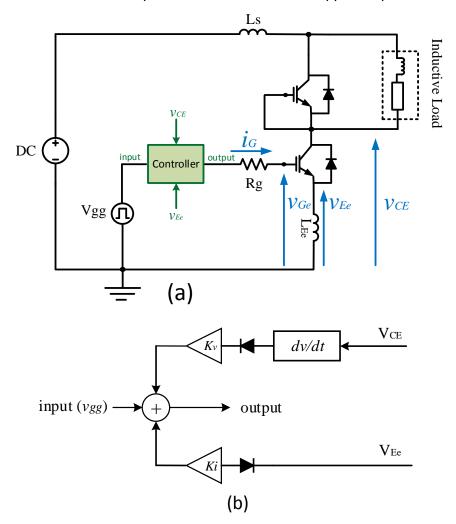

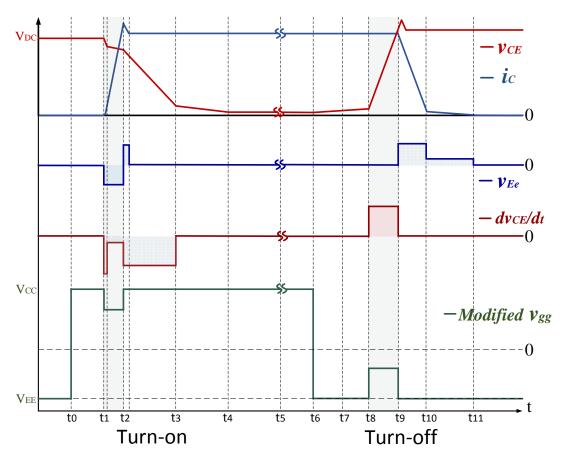

- [4] http://www.pwrx.com/pwrx/docs/cm750hg-130r.pdf