# Programación de CPLDs de Xilinx y evaluación del software de desarrollo ISE WebPack 8.2i

Carlos Córcoles Brualla y Emiliano Aldabas Rubira

Universitat Politècnica de Catalunya (UPC)

Escola d'Enginyeria de Terrassa (EET)

Colom 1, 08222 TERRASSA Barcelona

ccorcoles@circutor.es

#### Resumen

Este trabajo es un resumen del proyecto final de carrera realizado por el autor [1] en la *Escola d'Enginyeria de Terrassa*. En líneas generales se ha programado un CPLD de Xilinx en ABEL-HDL y VHDL utilizando el programa gratuito ISE WebPack 8.2i que suministra el fabricante. La orientación del trabajo es docente y pretende servir de ayuda a aquellos alumnos que utilizan por primera vez este entorno.

# 1. Introducción

Este proyecto pretende ser una guía que facilite a los interesados en el la programación de dispositivos lógicos programables (PLD) la tarea de aprender tanto los diferentes lenguajes de programación como el entorno de desarrollo.

En él se presentan los tipos de PLD existentes, junto con una pequeña descripción histórica y funcional de cada uno de ellos.

De la misma forma, se presentan los programas que se utilizan.

Esta presentación contempla la descarga de Internet, la instalación y el uso o generación de proyectos en diversos lenguajes mediante unos ejemplos guiados paso a paso para que el lector conozca tanto la herramienta como los pasos a seguir, facilitándole de este modo el aprendizaje y la creación de proyectos propios.

Los principales objetivos del proyecto son:

- Realizar tutorial detallado del programa ISE WebPack 8.2i, de Xilinx.

- Describir los PLD genéricos y los CPLD, concretamente la familia XC9500.

- Realizar tutorial del programa de transferencia Adept Suite.

- Realizar una extensa colección de prácticas en lenguaje ABEL HDL.

- Describir el funcionamiento y simulación de los autómatas finitos en el entorno Boole-Deusto.

- Desarrollar y mejorar un secuenciador de fases para proteger los motores de inducción, frente a inversiones de giro no deseadas.

Fig. 1. Simulación de un circuito combinacional con ISE WebPack 8.2i.

- · Analizar una solución aportada por otros autores.

- Detectar los puntos mejorables.

- Proponer soluciones utilizando autómatas finitos.

- Implementar la solución final mediante el leguaje ABEL HDL.

### 2. Evaluación de las herramientas

En referencia al funcionamiento del software de programación y transferencia ISE WebPack 8.2i de Xilinx, se pueden destacar [2]:

- La versión WebPack 8.2i es la primera versión del software de Xilinx que permite simular el comportamiento del programa antes de su transferencia.

- Permite tres formas diferentes de simulación: con retardos de propagación, sin retados y como quedaría el circuito una vez implantado en el CPLD.

- La transferencia desde el programa Xilinx no es posible mediante un cable JTAG USB a pesar de disponer de un módulo especial de transferencia llamado iMPACT. Únicamente funciona la transferencia a través del puerto paralelo.

- Es necesario utilizar el software de transferencia Adep Suite que proporciona el fabricante del cable JTAG.

- ISE WebPack 8.2i es un software con una dificultad media-alta de utilización, pero con una pequeña guía que indique las pautas a seguir se convierte en un software ameno y sencillo de usar, siendo una herramienta indispensable para programar los CPLDs de Xilinx en ABEL y VHDL.

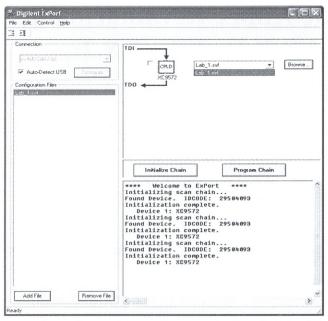

Fig. 2. Transferencia del programa con Adept Suite a través del puerto USB.

En referencia al funcionamiento del software de transferencia Adept Suite [3]:

- Es un software sencillo de utilizar ya que sólo necesita habilitar la conexión con la CPLD, seleccionar el programa (archivo \*.svf) que se desea transferir y activar la transferencia.

- Dispone de pocas opciones de menú lo que facilita su uso notablemente.

- Debemos habilitar la detección automática del cable USB y pulsar "Initialize Chain" para que el programa detecte el dispositivo conectado automáticamente.

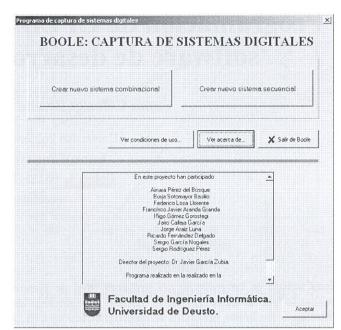

En referencia al funcionamiento del software de diseño digital Boole Deusto [4]:

- Boole Deusto que se divide en dos partes bien diferenciadas. Ambas partes son de gran ayuda para diseñar y documentar un trabajo ya que permiten exportar los gráficos, esquemas lógicos e informes del proyecto al portapapeles. Esto facilita la preparación de informes de prácticas a los alumnos.

- 1- Sistemas Combinacionales: Esta parte es muy útil para resolver diagramas de Karnaugh, evaluar tablas de la verdad, etcétera. Sencilla de usar, aunque con muchas opciones de introducción de datos y simplificación de funciones.

Fig. 3. Pantalla de presentación de Boole Deusto.

2- Sistemas Secuenciales: Con gran variedad de opciones. También sencillo de usar aunque con mayor número de opciones ya que permite simular autómatas de Moore y de Mealy. También permite visualizar los circuitos con flipflops de tipo JK y de tipo D. En la versión utilizada se han detectado limitaciones para introducir diagramas de más de 13 estados y 49 transiciones.

## 3. Conclusiones

En esta presentación se han resumido las conclusiones del proyecto final de carrera desarrollado para facilitar a los alumnos de la *Escola d'Enginyeria de Terrassa* (EET) la introducción a la programación de CPLDs de la firma Xilinx y al diseño de circuitos digitales, tanto combinacionales como secuenciales.

#### Referencias

- C. Córcoles, "Programación de CPLDs de Xilinx y evaluación del software de desarrollo ISE WebPack 8.2i", Escola d'Enginyeria de Terrassa (EET), UPC, 2009

- [2] Xilinx, Inc. "ISE WebPack 8.2i", www.xilinx.com

- [3] Digilent, Inc. "Adept Suite", http://digilentinc.com/

- [4] J. García Zubía, "Boole Deusto", http://paginaspersonales.deusto.es/zubia/