# Aggressive undervolting of FPGAs: power & reliability trade-offs

### **Behzad Salami**

ADVERTIMENT La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del repositori institucional UPCommons (<a href="http://www.tdx.cat/">http://www.tdx.cat/</a>) le repositori cooperatiu TDX (<a href="http://www.tdx.cat/">http://www.tdx.cat/</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei UPCommons o TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a UPCommons (\*framing\*). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

ADVERTENCIA La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del repositorio institucional UPCommons (<a href="http://upcommons.upc.edu/tesis">http://upcommons.upc.edu/tesis</a>) y el repositorio cooperativo TDR (<a href="http://www.tdx.cat/?locale-attribute=es">http://www.tdx.cat/?locale-attribute=es</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio UPCommons No se autoriza la presentación de su contenido en una ventana o marco ajeno a UPCommons (<a href="https://raming/framing/">framing/</a>). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

WARNING On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the institutional repository **UPCommons** (http://upcommons.upc.edu/tesis) and the cooperative repository TDX (http://www.tdx.cat/?localeattribute=en) has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading nor availability from a site foreign to the UPCommons service. Introducing its content in a window or frame foreign to the UPCommons service is not authorized (framing). These rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author.

# Aggressive Undervolting of FPGAs: Power & Reliability Trade-offs

# Behzad Salami Department of Computer Architecture Universitat Politècnica de Catalunya (UPC)

A thesis submitted for the degree of

Doctor of Philosophy in Computer Architecture

November, 2018

Advisor: Dr. Adrián Cristal Kestelman

Co-Advisor: Dr. Osman S. Unsal

For my Family

# Acknowledgements

First of all, I would like to express my deep and sincere gratitude to my Ph.D. advisors Dr. Adrian Cristal Kestelman and Dr. Osman S. Unsal for giving me this great opportunity to attend their research group at BSC, and also, for their advice, guidance, confidence, and patient demeanor later during my Ph.D. studies. Without their deep technical knowledge to guide me, my Ph.D. studies would never successfully happen. With a warm and friendly behavior, they showed me in practice how to enjoy of working and how research can provide satisfaction if I am building something useful. What I learned from them will stay with me in my professional and personal life forever.

I would also like to express my acknowledge to Professor Mateo Valero. Mateo's leadership has fostered an outstanding academic atmosphere at BSC that I was fortunate to be a part of. I had also a great chance to travel with Mateo and his lovely wife Angela to my home country, Iran. For me, this trip was full of good times, incredible experiences, and unique lessons. These experiences and lessons will play considerable role to shape of my future professional and personal life.

During my Ph.D. studies, I had chances to collaborate with many deeply knowledgeable researchers. Some of these experiences were really unique for me. I would like to use this opportunity to send my thanks message to Dr. Pradip Bose, Dr. Alper Buyuktosunoglu, and Dr. Augusto Vega

from IBM Watson, a major part of this thesis was done in collaboration with them, and also, to Dr. Dirk Koch from University of Manchester who was my internship advisor.

I would also like to extend my thanks to the my Ph.D. defense and predefense committee, including Prof. Hamid Sarbazi-Azad, Prof. Onur Mutlu, Dr. Daniel Jimenez Gonzalez, Dr. Miquel Moreto, and Dr. Carles Hernandez Luz for their time to review and precise comments for improving the thesis.

Also, I acknowledge to outstanding and friendly staff at BSC and UPC for their support over the years.

I was fortunate to have had brilliant colleagues which turned into great friends including Oscar Palomar, Daniel Nemirovski, Azam Seyyedi, Burcu Ozcelik Mutlu, Gulay Yalcin, Nikola Marković, Nehir Sonmez, Oriol Arcas-Abella, Gorker Alp Malazgirt, Ivan Ratković, Alberto Gonzalez, Julian Pavon, Leonardo Bautista-Gomez, Oyku Melikoglu, Albert Kahira, Cristobal Ramirez, Kai Keller, Santhosh Kumar Rethinagiri, Milan Stanić, Tugberk Arkose, Damian Roca, Josue Esparza, Javier Arias, Adria Armejach, and Gina Alioto.

During my stay at Barcelona, I had the chance to meet many people in my after-work life, and some of them turned into great friends. We shared our good or bad times together. I would like to thanks my friends including Jamileh Jafari, Hamid Tabani, and Pouya Esmaili.

Finally, I would like to send my deep thanks to my lovely family, my brothers Sadegh, Turaj, and Ayhan, my sister, Zarrin, and specially my parents, Hossein and Roghiyeh, for their boundless dedication and encouragement.

This thesis received funding from the European Union's Horizon 2020 Programme under the LEGaTO project (www.legato-project.eu), grant agreement n° 780681, and the European Union Seventh Framework Program (FP7) under the AXLE project (www.axleproject.eu), grant agreement n° 318633. Also, I got grant from HiPEAC for my three-months internship at University of Manchester. Finally, this thesis is in part supported by Ministry of Economy and Competitiveness of Spain under contract n° TIN2015-65316-p.

#### **Abstract**

In this work, we evaluate aggressive undervolting, i.e., voltage underscaling below the nominal level to reduce the energy consumption of Field Programmable Gate Arrays (FPGAs). Usually, voltage guardbands are added by chip vendors to ensure the worst-case process and environmental scenarios. Through experimenting on several FPGA architectures, we confirm a large voltage guardband on FPGAs. In turn, significant power consumption is saved, by eliminating this voltage guardband; however, further undervolting may cause reliability issues as the result of the circuit delay increase, and faults might start to appear. We perform a detailed fault characterization in terms of the rate, location, type, as well as experimentally analyzing the sensitivity to environmental temperature, with a primarily focused on FPGA on-chip memories, or Block RAMs (BRAMs). Understanding this behavior can allow to deploy efficient mitigation techniques, and in turn, FPGA-based designs can be improved for better energy, reliability, and performance tradeoffs.

Finally, as a case study, we evaluate a typical FPGA-based Neural Network (NN) accelerator when the FPGA voltage is underscaled. In consequence, the substantial NN energy savings come with the cost of NN accuracy loss. To attain power savings without NN accuracy loss below the voltage guardband gap, we propose a novel technique and also evaluated the built-in ECC mechanism of BRAMs. Hence, we develop an

application-dependent BRAMs placement technique that relies on the deterministic behavior of undervolting faults and mitigates these faults by mapping the most reliability sensitive NN parameters to BRAM blocks that are relatively more resistant to undervolting faults. Finally, as a more general technique, we apply the built-in ECC of BRAMs and observe a significant fault coverage capability thanks to the behavior of undervolting faults, with a negligible power consumption overhead.

Keywords: FPGA, Voltage Scaling, Power Consumption, Reliability

# **Abbreviations**

| ASIC | Application-Specific Integrated Circuit  |

|------|------------------------------------------|

| BRAM | Block Random Access Memory               |

| COP  | Critical Operating Point                 |

| CPU  | Central Processing Unit                  |

| DRAM | Dynamic Random Access Memory             |

| DSP  | Digital Signal Processor                 |

|      | Dynamic Voltage Frequency Scaling        |

| ECC  | Error Correction Code                    |

| FIP  | Fault Inclusion Property                 |

|      | Field Programmable Gate Array            |

|      | Floating Point Unit                      |

|      | Fault Variation Map                      |

|      | Graphic Processor Unit                   |

|      | Hardware Description Language            |

|      | High-Level Synthesis                     |

|      | High Performance Computing               |

|      | ntelligently-Constrained BRAMs Placement |

| ITD    | Inverse Temperature Dependency                     |

|--------|----------------------------------------------------|

| LUT    | Look-Up Table                                      |

| ML     | Machine Learning                                   |

| NN     | Neural Network                                     |

| RAM    | Random Access Memory                               |

| RTL    | Register-Transfer Level                            |

| SECDED | Single-Error Correction and Double-Error Detection |

| SOC    | System On Chip                                     |

| SRAM   | Static Random Access Memory                        |

| TMR    | Triple Modular Redundancy                          |

# Contents

| 1 | Introduction                                  |                                            |                |  |

|---|-----------------------------------------------|--------------------------------------------|----------------|--|

|   | 1.1                                           | Background                                 | 1              |  |

|   |                                               | 1.1.1 FPGA Architecture                    | 1              |  |

|   |                                               | 1.1.2 Aggressive Undervolting              | 3              |  |

|   | 1.2                                           | Key Challenges and Motivations             | 4              |  |

|   | 1.3                                           | Scope of the Thesis                        | 6              |  |

|   | 1.4                                           | Contributions                              | 8              |  |

|   | 1.5                                           | Outline                                    | 10             |  |

| 2 | Unc                                           | derstanding FPGAs Undervolting             | 11             |  |

|   |                                               |                                            |                |  |

|   | 2.1                                           | Experimental Methodology                   | 11             |  |

|   | <ul><li>2.1</li><li>2.2</li></ul>             | Experimental Methodology                   | 11<br>12       |  |

|   |                                               |                                            |                |  |

|   | 2.2                                           | FPGA Undervolting: Idle Power Minimization | 12             |  |

| 3 | <ul><li>2.2</li><li>2.3</li><li>2.4</li></ul> | FPGA Undervolting: Idle Power Minimization | 12<br>15       |  |

| 3 | <ul><li>2.2</li><li>2.3</li><li>2.4</li></ul> | FPGA Undervolting: Idle Power Minimization | 12<br>15<br>18 |  |

|   | 3.3  | Fault   | Variability Within BRAMs                                  | 25 |

|---|------|---------|-----------------------------------------------------------|----|

|   |      | 3.3.1   | Column-wise Fault Analysis                                | 25 |

|   |      | 3.3.2   | Row-wise Fault Analysis                                   | 26 |

|   | 3.4  | The Ir  | npact of the Die-to-Die Process Variation                 | 27 |

|   | 3.5  | Fault   | Inclusion Property (FIP)                                  | 30 |

|   | 3.6  | Туре    | of Faults: Single-, Double-, Or Multiple-Bit?             | 30 |

|   | 3.7  | Impac   | et of the Environmental Temperature                       | 31 |

|   | 3.8  | Summ    | nary                                                      | 34 |

| 4 | Eval | luating | FPGA-based NN Accelerator on Low-Voltage FPGA BRAMs       | 35 |

|   | 4.1  | Backg   | round on NN Resilience                                    | 35 |

|   |      | 4.1.1   | The Architecture of the NN Accelerator                    | 36 |

|   | 4.2  | Exper   | imental Methodology of NN Evaluations                     | 38 |

|   | 4.3  | Impac   | et of Voltage Scaling Below $V_{min}$ on the NN Accuracy  | 42 |

|   | 4.4  | Fault   | Mitigation Techniques                                     | 42 |

|   |      | 4.4.1   | Intelligently-Constrained BRAM Placement (ICBP)           | 43 |

|   |      | 4.4.2   | Built-in ECC                                              | 52 |

|   |      | 4.4.3   | Discussion on the Mitigation Techniques                   | 59 |

| 5 | Rela | ated Wo | ork                                                       | 61 |

|   | 5.1  | Power   | e-efficient and Reliable FPGAs                            | 61 |

|   | 5.2  | Power   | and Reliability of FPGAs versus CPUs, GPUs, and ASICs     | 62 |

|   | 5.3  | Power   | and Reliability of FPGA BRAMs versus DRAMs and SRAMs      | 63 |

|   | 5.4  | Aggre   | essive Undervolting                                       | 66 |

|   |      | 5.4.1   | Voltage Guardband                                         | 66 |

|   |      | 5.4.2   | Simultaneous Voltage and Frequency Underscaling           | 66 |

|   |      | 5.4.3   | Aggressive Undervolting into the Critical Voltage Regions | 67 |

|   | 5.5  | Recen   | t Related Studies on NNs                                  | 68 |

|    |       | 5.5.1    | Simulation-Based Resilience Study of Low-voltage NNs      | 69         |

|----|-------|----------|-----------------------------------------------------------|------------|

|    |       | 5.5.2    | Real Hardware-Based Resilience Study of Low-voltage NNs . | <b>7</b> 0 |

| 6  | Con   | clusior  | 1                                                         | 73         |

|    | 6.1   | Summ     | nary and Conclusion                                       | <b>7</b> 3 |

|    | 6.2   | Lesson   | ns Learned                                                | 76         |

|    | 6.3   | Future   | e of Aggressive FPGAs Undervolting                        | <b>7</b> 9 |

| 7  | Pub   | lication | ns                                                        | 83         |

|    | 7.1   | Public   | eations from the Thesis                                   | 83         |

|    | 7.2   | Public   | cations not Included in the Thesis                        | 84         |

| Li | st of | Figures  | 3                                                         | 87         |

| Li | st of | Tables   |                                                           | 91         |

| Bi |       |          |                                                           |            |

1

# Introduction

In this chapter, we provide background information about the scope of the thesis and later on, explain the key challenges, motivations, our solutions, and finally, introduce the thesis outline.

# 1.1 Background

The concentration of this thesis is on aggressive undervolting for commercial Field Programmable Gate Arrays (FPGAs). Hence, in this section, we briefly introduce these concepts.

#### 1.1.1 FPGA Architecture

In modern computing systems, FPGAs play a crucial role to accelerate state-of-the-art applications, thanks to their inherent capability to execute computations in streaming fashion on a massively parallel substrate. FPGAs are increasingly employed within the modern data centers and are expected to be in 30% of data centers by 2020 [7]. They are used to accelerate many state-of-the-art applications such as database query processing [19], [139], [141], [140], Neural Networks (NN) [59], [74], and genome sequence analytic [14], among others. FPGAs combine the

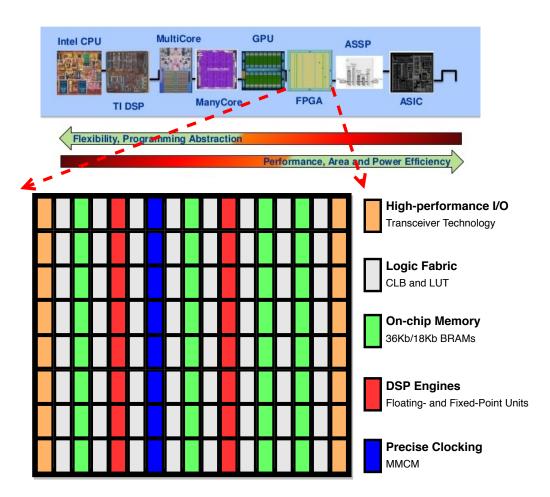

Figure 1.1: FPGAs among other digital devices (source: Intel/Altera [2]).

flexibility of CPUs with the efficiency of Application-Specific Integrated Circuits (ASICs), see Figure 1.1. Hence, the concentration of this thesis is to study FP-GAs with the aim of making them more power-efficient, which can suit them for power-constrained environments. Modern FPGAs are composed of a wide range of reconfigurable components, *e.g.*, Block RAMs (BRAMs), Digital Signal Processors (DSPs), Configurable Logic Blocks (CLBs), among others. These components in a tightly-coupled structure can be efficiently exploited to accelerate computation-, memory, or I/O-intensive applications to achieve the goal of high-throughput computation. Usually, these components are floorplanned in a column-oriented way, as

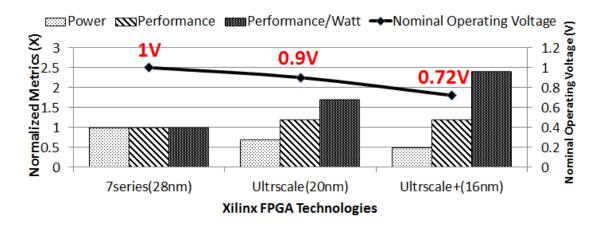

Figure 1.2: Voltage scaling in in Xilinx device family generations [10].

illustrated in Figure 1.1. For computations, corresponding components need to be appropriately configured at run- or compile-time. Most of the state-of-the-art commercial FPGAs including the studied commercial FPGAs in this thesis are Static RAM (SRAM)-based, which means that the configuration bitstream is stored in on-chip SRAMs and FPGA components get configured by reading the corresponding parts of this bitstream.

# 1.1.2 Aggressive Undervolting

The power consumption of digital circuits, *e.g.*, FPGAs is directly related to their supply voltage level. Hence, any voltage underscaling can directly deliver power/energy efficiency gains. For instance, as shown in Figure 1.2, for Xilinx FPGA generations, the nominal operating voltage has been lowered from 1V in Virtex-7 series (28nm) to 0.72V in Ultrascale+ series (16nm); resulting in 1.2X and 2.4X in power and performance/watt efficiency, respectively [10]. As a more aggressive effort, for each technology node, the supply voltage underscaling below the standard nominal level can deliver further power savings. We target this approach in the thesis.

#### 1. INTRODUCTION

For different types of chips such as CPUs [22], [72], [153], [127], [171], Graphics Processing Units (GPUs) [91], ASICs [165], Dynamic RAMs (DRAMs) [36], and SRAMs [174] it has been experimentally shown that the nominal operating voltages set by vendors are extremely conservative for real-world applications. This phenomenon is due to the voltage guardband added by vendors to ensure the correct operation under worst-case environmental and process conditions. Thus, as earlier mentioned, the promising approach to achieve energy efficiency is the aggressive undervolting, *i.e.*, voltage underscaling below the standard nominal level. However, as the works above as well as our experimental studies confirm, the potential of the aggressive undervolting is fully vendor-, chip-, architecture- dependent. The concentration of this thesis is to study aggressive undervolting for commercial FPGAs experimentally.

However, the downside of the aggressive undervolting is that voltage underscaling below the voltage guardband can cause reliability issues and faults might start to appear. Unlike the DVFS technique, the frequency is not scaled down in the aggressive undervolting approach. Therefore energy savings can be more significant. However, aggressive undervolting leads to timing related faults, which can cause applications to crash or terminate with wrong results. This thesis aims to extend the aggressive supply voltage underscaling approach, *i.e.*, power and reliability trade-off, detailed fault characterization, and effective mitigation for FPGAs.

# 1.2 Key Challenges and Motivations

In comparison to ASICs, the power consumption of FPGAs is a first-order concern, especially in nano-scale manufacturing technologies. It has been shown that the power and energy efficiency of FPGAs is estimated to be  $\sim 10X-\sim 20X$  worse than in the corresponding ASIC designs [135], [183], [83], [122], [123] as it is also

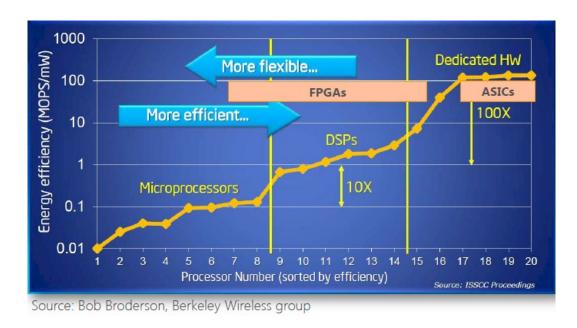

Figure 1.3: Detailed energy efficiency of FPGAs [1].

confirmed from industry perspective, see Figure 1.3. This gap is due to the inherent structure of FPGA resources, which provide the configurability as an advantage against ASICs; however, configurability incurs additional power consumption overhead. The relatively lower power and energy efficiency of FPGAs can make them less attractive for power-limited environments such as high performance embedded computing scenarios and mobile environments, among others. Thus, the key challenge that this thesis aims to tackle is the power/energy dissipation of FPGAs.

There are many techniques deployed to minimize the power consumption of FP-GAs, such as architectural improvements [10] [3], power-aware tools [43] [85] [49], bitstream compression [125], clock or voltage gating [126] [182], [95], [162] among others. This thesis concentrates on an orthogonal approach, aggressive undervolting. As summarized in equations 1.1, 1.2, and 1.3, the total power consumption including the dynamic, *i.e.*, the signal transition power, and static power, *i.e.*, leakage power, are directly functions of the supply voltage [5]; thus, as expected, any

#### 1. INTRODUCTION

undervolting can directly lead to the power consumption reduction.

$$P_{total} = P_{dynamic} + P_{static} (1.1)$$

$$P_{dynamic} = \alpha.C.f.V^2 \tag{1.2}$$

$$P_{static} = \sum Leakage\_Current.V \tag{1.3}$$

, where  $\alpha$ , C, f, V, and  $Leakage\_Current$  are the technology-dependent constant coefficient, capacitance, working frequency, supply voltage, and total leakage current of the digital circuit, respectively.

With the aim of evaluating the aggressive undervolting technique to achieve energy-efficient FPGA-based accelerators, the key research questions that are answered by this thesis are listed below:

- 1. Is there any potential in FPGAs to take advantage of aggressive undervolting?

- 2. Do technology architecture, process variation, etc., play any role in the impacts of aggressive undervolting in FPGAs?

- 3. Is the effect of aggressive undervolting on the reliability deterministic or stochastic?

- 4. Which kind of real-world application can take advantage of the energy efficiency through aggressive undervolting?

# 1.3 Scope of the Thesis

To have a thorough study, our experiments include several representative platforms from Xilinx, a main vendor, *i.e.*, VC707 (performance-optimized architecture) [11],

ZC702 (FPGA integrated with ARM-core) [13], and two identical samples of KC705 (power-optimized architecture) [12] platforms. These four platforms allow us to study different architectures and also the impact of die-to-die process variation for KC705. Experimentally confirming the voltage guardband for multiple components of FPGAs, we observe that data can be safely retrieved without any observable fault when the supply voltage is underscaled below the nominal level, *i.e.*,  $V_{nom}$ , and until a certain minimum safe voltage level, *i.e.*,  $V_{min}$ . Further voltage underscaling causes faults.

For a more detailed study, the concentration of this thesis is BRAMs, since BRAMs play a key role in the acceleration of state-of-the-art applications such as NNs and bioinformatics [14], and also, they considerably contribute in the total power consumption of such FPGA designs of up to 30% [59]. Also, unlike many FPGA components, the supply voltage of BRAMs can be independently regulated, which allows detailed power and reliability trade-off analysis. Hence, the reliability aspects of BRAMs under aggressively low-voltage operations are extensively studied. This study includes the characterization of faults in terms of the rate, location, type as well as the impact of the environmental temperature.

As a case study application, we concentrate on the NN accelerator. NNs are state-of-the-art applications that are increasingly used in the context of many real-world environments such as autonomous cars [160], [143], [65], mobile scenarios [86], [90], [73], personalized medicine [39], [51], [67], game industry [147], among others. Also, due to the size of matrices that NNs needs to compute, the computation and power required is significant [146], [154]. To achieve energy-efficient NN, hardware accelerators such as GPU- [124], FPGA- [134], and ASIC-based [70], [135], [63] systems have recently received significant attention. Among them, FPGA-based accelerators have unique features such as the relatively short deployment time versus ASICs and more energy-efficient against GPUs. Hence, to achieve

#### 1. INTRODUCTION

an energy-efficient FPGA-based NN accelerator, we push a typical accelerator to operate under low-voltage FPGA BRAMs, and evaluate mitigation techniques to prevent NN accuracy loss as the result of undervolting faults.

#### 1.4 Contributions

This thesis aims to evaluate the aggressive undervolting technique for commercial FPGAs empirically. Toward this goal, the thesis has three main contributions, which are summarized as follows:

- 1. **Voltage Guardband:** This thesis is the first effort to empirically study aggressive voltage underscaling of FPGAs below the standard nominal level. Through experimenting on four platforms, we confirm a conservative voltage guardband until the minimum safe voltage level, *i.e.*, *V*<sub>min</sub> for different FPGA components. By eliminating this large voltage gap, a significant power saving gain is achieved without compromising to the performance or reliability, for instance, more than an order of magnitude power savings for on-chip BRAMs.

- 2. **Fault Characterization:** We perform the first detailed experimental bit-level characterization study of the behavior of faults when the supply voltage of FPGA on-chip BRAMs is underscaled below  $V_{min}$ . Understanding the behavior of these faults can provide an opportunity to deploy efficient mitigation techniques, and in turn, a better trade-off for low-voltage FPGA-based designs can be achieved. More specifically, we observe that:

- The fault rate exponentially increases by further undervolting; however, with a considerable difference among platforms, which is the result of technological differences and also process variation.

- The location and rate of undervolting faults do not considerably change over time. In other words, undervolting faults exhibit a deterministic behavior.

- Within BRAMs, faults usually occur in certain few columns; however, these most-vulnerable columns are different among all BRAMs.

- Undervolting faults are fully non-uniformly distributed among BRAMs.

- Undervolting faults manifest themselves mostly as '1' to '0' bit-flips.

- On a given BRAM raw, undervolting faults lead mostly to single-bit type faults. Multi-bit type faults start to appear as the voltage is further reduced.

- At higher environmental temperatures, the fault rate reduces as the result of the Inverse Temperature Dependence (ITD) property of the nanoscale technology nodes [117].

- Undervolting faults follow the Fault Inclusion Property (FIP), *i.e.*, faults in a certain voltage level, stay (and potentially extend) in lower voltages, as well.

- 3. **FPGA-Based Accelerator:** We perform the first study of the efficiency of NN accelerators under the aggressively low-voltage operation of commercial FPGAs. We observe that the data sparsity of state-of-the-art NN benchmarks makes them inherently robust against undervolting faults; however, by aggressive undervolting, the NN accuracy is impacted. To attain the subsequent power saving without NN accuracy loss, we present two fault mitigation techniques, which rely on the behavior of undervolting faults.

#### 1.5 Outline

The subsequent sections of this thesis are structured as follows. The FPGA undervolting experimental methodology, and also, the major behavior of the power and reliability trade-off is explained in Chapter 2. The fault characterization under aggressive low-voltage FPGA operations is detailed in Chapter 3. Chapter 4 explains the effect of FPGA undervolting in the typical NN and evaluate the proposed fault mitigation techniques. Chapter 5 reviews the recent related works and Chapter 6 summarizes our findings and lessons learned in this study. Finally, Chapter 7 includes the list of publications from the thesis.

# **Understanding FPGAs Undervolting**

In this chapter, we introduce the experimental methodology, elaborate the FPGA platform undervolting, and also, discuss the behavior of FPGA BRAMs under aggressively reduced supply voltage.

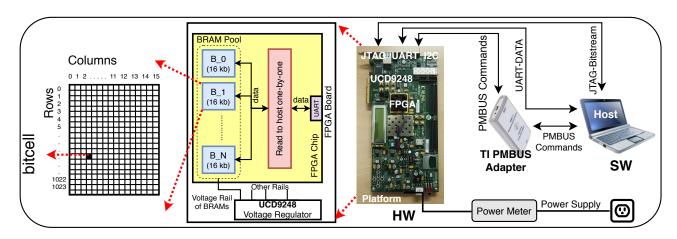

# 2.1 Experimental Methodology

We perform our experiments on a set of representative commercial FPGA platforms from Xilinx, *i.e.*, one VC707, one ZC702, and two KC705s. Common for all platforms, BRAMs are distributed all over the chip with a unique size of 16 Kbits each. Each BRAM is a matrix of bitcells with 1024 rows, and 16 columns<sup>1</sup>. BRAMs can be either individually accessed or cascaded to build larger memories (with some overheads). This methodology provides flexibility for the FPGA designers to have single-cycle access to on-chip memories as per bandwidth or size needs. More details of our tested platforms are shown in Table 2.1. All platforms are fabricated with 28nm technology, and the standard nominal voltage of BRAMs is the same,  $V_{nom} = 1V$ . However, VC707 is designed for performance while KC705 is optimized for the power consumption. Also, a different design approach is used for

<sup>&</sup>lt;sup>1</sup>Each row has two additional bits as parity that is not considered in this section. We will elaborate on their role in Section 4.4.2.

| Hardware Platform (Board)          | VC707       | ZC702                 | KC705*       |

|------------------------------------|-------------|-----------------------|--------------|

| Device Family                      | Virtex-7    | Zynq7000              | Kintex-7     |

| Chip Model                         | XC7VX485T   | XC7Z020               | XC7K325T     |

| Speed Grade                        | -2          | -1                    | -2           |

| Number of BRAMs                    | 2060        | 280                   | 890          |

| Basic Size of Each BRAM            | 1024*16-bit | 1024*16-bits          | 1024*16-bits |

| Technology Node                    | 28nm        | 28nm                  | 28nm         |

| Nominal $V_{CCBRAM}$ ( $V_{nom}$ ) | 1V          | 1V                    | 1V           |

| Design Consideration               | Performance | FPGA-CPU Architecture | Power        |

Table 2.1: Specifications of tested FPGA platforms.

ZC702, which is targeted for hardware-software (FPGA-CPU) co-designs. Furthermore, we choose two KC705 platforms that allow us to evaluate the undervolting effects on the same model, as well. Hence, for a thorough evaluation, we selected these representative platforms.

# 2.2 FPGA Undervolting: Idle Power Minimization

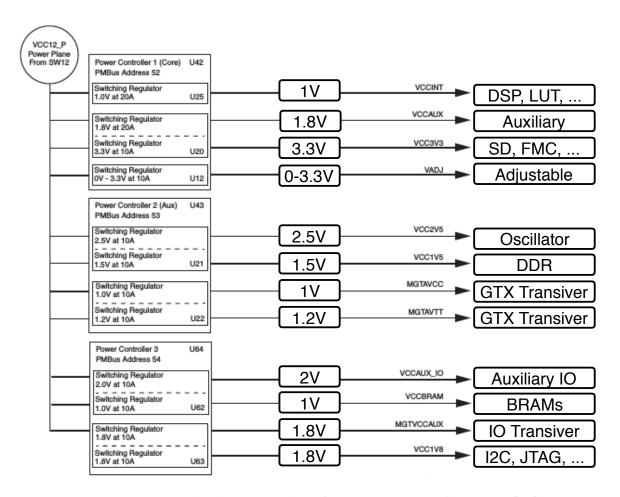

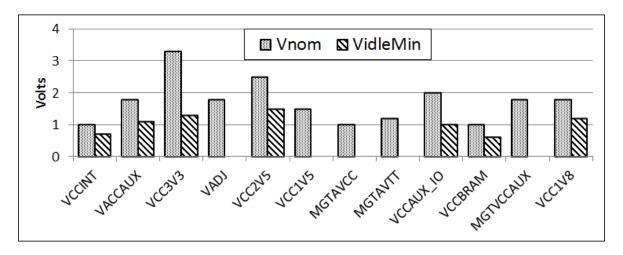

Through the Power Management Bus (PMBUS) standard [4], it is possible to independently and dynamically regulate and monitor the supply voltage of such FPGA components as BRAMs ( $V_{CCBRAM}$ ), core logic ( $V_{CCINT}$ ), i.e., Look-Up Tables (LUTs) and Digital Signal Processors (DSPs), among others. An on-board voltage regulator is responsible for this aim. Although there is no standard for the list of these components with the capability of independently regulated, the difference among our studied platforms is not significant. For instance, the on-board voltage distribution is shown in Figure 2.1 for VC707. To modify supply voltages, we use Texas Instrument (TI) PMBUS USB Adapter, and the provided C-based Application Programming Interface (API), which facilitates accessing the on-board voltage

<sup>\*</sup> Two identical samples of KC705 (A & B) are tested.

Figure 2.1: On-board voltage regulator for FPGAs, shown for VC707 [11].

controller through the host [6]. Note that in the studied platforms, the voltage regulator is hardwired to the host, and accessible through the PMBus standard.

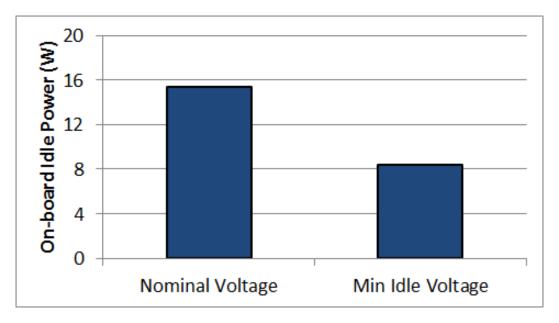

As the first experiment, we aim to minimize the Idle power consumption of the FPGA platform, *i.e.*, the power that is dissipated when there is no application running on the board and all components can go to the idle mode, through undervolting the platform's components listed in Figure 2.1. Toward this goal, we set the supply voltage of the platform's components at a minimum voltage level that the platform does not crash, *i.e.*,  $V_{idleMin}$ . In turn, the on-board status LEDs are changed from Figure 2.3a at the nominal voltage level to 2.3b below the  $V_{idleMin}$ .

#### 2. UNDERSTANDING FPGAS UNDERVOLTING

Figure 2.2: FPGA platform undervolting until the crash voltage level, shown for VC707 [11].

(a) At the standard nominal voltage level, *i.e.*,  $V_{nom}$ .

(b) Below the minimum Idle voltage level, *i.e.*,  $V_{idleMin}$ .

Figure 2.3: Status LEDs under different voltages, shown for VC707 [11].

It means that further undervolting causes the system crashing, which is exposed by an unset of the DONE pin. Note that at the  $V_{idleMin}$ , there is no guarantee that the system operates in a safe behavior; however, the FPGA bitstream is recognized as correct. Through this undervolting mechanism, the idle power consumption is significantly reduced, for instance, 1.9X for VC707 as shown in Figure 2.4.

Figure 2.4: Minimized Idle power consumption through undervolting as detailed in Figure 2.2, shown for VC707 [11].

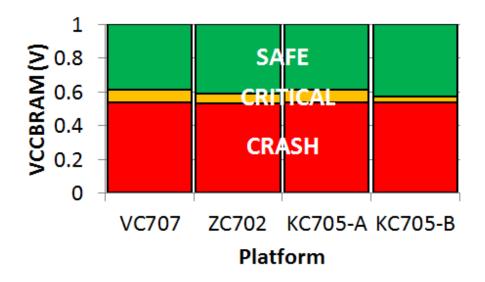

# 2.3 Safe, Critical, and Crash Voltage Regions

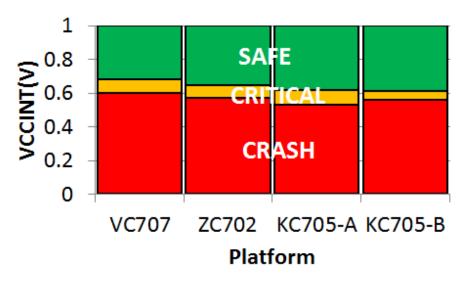

Unlike the idle power that is drawn when only the power supply is connected, application running can consume additional power consumption. In this section, we aim to discover the minimum safe voltage of such FPGA components as  $V_{CCINT}$  and  $V_{CCBRAM}$ . These voltage rails feed the most important on-chip FPGA components. As can be seen in Figure 2.5, for both  $V_{CCINT}$  and  $V_{CCBRAM}$ , there is a conservative voltage guardband for all platforms below the nominal level (SAFE), which creates an opportunity for energy savings. Further undervolting causes observable faults (CRITICAL), until a voltage level that platforms stop operating (CRASH). Note that for all platforms, the nominal voltage level of both voltage rails is 1V; however, other voltage levels slightly vary among platforms. For the more detailed study, we concentrate on  $V_{CCBRAM}$ , since its independent voltage rail allows to evaluate BRAMs individually in fine-grain level at the critical voltage region, unlike the

$V_{CCINT}$  that feeds several components such as LUTs and DSPs. Further power and reliability trade-off of the BRAMs at the critical region is discussed later in this section.

The experimental setup of BRAMs evaluation is shown in Figure 2.6. It is composed of two distinct hardware and software components. The task of the hardware FPGA platform is to access BRAMs and transmit their content to the host, using a serial interface. In ZC702, this serial interface is controlled by the ARM processor; however, in other platforms, we built our hardware serial interface. Note that we verify and validate that this interface is entirely reliable at any  $V_{CCBRAM}$  level and is not affected by the BRAMs undervolting. On the other side, the host issues the required PMBUS commands to set a certain voltage to  $V_{CCBRAM}$ . Also, it initializes BRAMs and analyzes potentially faulty data retrieved from BRAMs. On this setup, the reduced  $V_{CCBRAM}$  can cause the timing violations and in turn, corrupting some of the bitcells of some of BRAMs. We follow the method shown in List. 2.1 to analyze the behavior of these faults comprehensively.

Then, we retrieve the contents of BRAMs one-by-one and within each BRAM row-by-row, and transfer them to the host. In the host, we analyze the rate and location of faults. This process is repeated 100 times for each voltage level to obtain statistically significant results. The reported results in this chapter are the median of these 100 tests. After a soft reset, we gradually decrease  $V_{CCBRAM}$  by 10mV and repeat the process until the lowest voltage that our design operate,  $V_{crash}$ . For each voltage level, the fault rate and power consumption of BRAMs are recorded. Finally, to measure the power consumption with acceptable accuracy, we use a power meter, while to extract the power contribution of BRAMs in the nominal voltage level, we use Xilinx Power Estimation (XPE) tool. Thus, we report total power consumption including dynamic and static, which are both directly reduced by undervolting. Note that BRAMs considered in this thesis internally operate

(b) VCCINT.

Figure 2.5: Undervolting FPGA components, *i.e.*, Internal ( $V_{CCINT}$ ) and BRAM ( $V_{CCBRAM}$ ) voltages. (SAFE: no observable fault occur. CRITICAL: faults manifest. CRASH: FPGA stops operating.)

at a fixed frequency of  $\sim 500 \text{Mhz}$  [10], and externally the design is operating on the maximum frequency without timing violation at the nominal voltage level,

#### 2. UNDERSTANDING FPGAS UNDERVOLTING

Figure 2.6: Experimental setup to perform fault characterization through FPGA BRAMs aggressive voltage underscaling.

List 2.1: Pseudo-code to restudy liability behavior of voltage scaling on FPGA BRAMs at the CRITICAL, on the experimental setup of Figure 2.6.

```

1: V_{CCBRAM} = V_{min};

2: while (V_{CCBRAM} >= V_{crash}) begin

3:

while(numRun <= 100) begin

4:

delay(1sec);

5:

Transfer content of BRAMs to the host;

6:

Analyse faulty data (rate and location);

7:

numRun++;

8:

end

9:

V_{CCBRAM} - = 10(mV);

10: end

```

determined by the FPGA compiling tools.

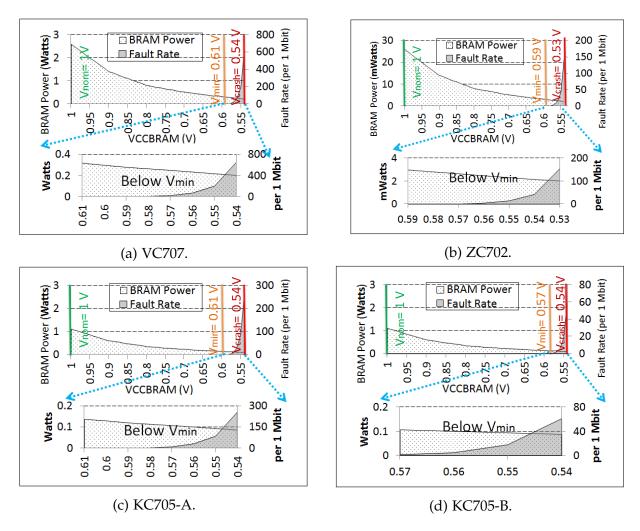

# 2.4 Power and Reliability Trade-offs

This section describes the overall behavior of FPGA BRAMs in terms of the power consumption and reliability trade-off when their supply voltage is aggressively reduced. We repeat experiments on all platforms, mentioned earlier. As can be seen in Figure 2.7, our experiments on lowering the supply voltage of BRAMs below nominal level,  $V_{nom}$ , demonstrate two thresholds. *First*, a voltage guardband,  $V_{min}$ , that separates the fault-free and faulty regions. *Second*,  $V_{crash}$  that is the lowest level of the voltage that our design practically operates. For all tested platforms,  $V_{nom} = 1V$  due to the factory settings. However, through our experiments, we observe a slight difference for  $V_{min}$  and  $V_{crash}$ . Note that repeating these tests in more noisy and harsh environments, *i.e.*, worst case environmental conditions, can cause observable faults above observed  $V_{min}$ , as well. Below the  $V_{crash}$  region, we observed that the DONE pin is unset, which at nominal levels indicates incorrect bitstream. To have an initial exploration, we evaluated the environmental temperature; however, the large guardband is experimentally observed.

The common observation for studied platforms is that when  $V_{CCBRAM} >= V_{min}$ , no observable faults occur. However, underscaling  $V_{CCBRAM}$  below  $V_{min}$  the fault rate exponentially increases, while the power consumption quadratically reduces but with different scales for different platforms. When  $V_{CCBRAM} = V_{min}$ , significant BRAMs power savings gain is achieved over  $V_{nom} = 1V$ , more than an order of magnitude, without comprising any performance or incurring any reliability degradation. As can be seen, both power consumption and reduction are less in KC705 than VC707, which is the consequence of having relatively fewer BRAMs and also the inherent power optimizations adopted for KC705 by the vendor. Also, BRAMs power consumption in ZC702 is relatively less than other platforms, since it is composed of a much smaller number of BRAMs.

Further undervolting below  $V_{min}$ , the fault rate exponentially increases, up to 652, 153, 254, and 60 per 1 Mbits ( $\sim 0.06\%$ , 0.01%, 0.03%, and 0.005%)<sup>1</sup> at  $V_{crash}$ ,

<sup>&</sup>lt;sup>1</sup>Since the overall fault rates are very small, instead of percentage (%), we present them in terms of number of faults per 1Mbit, for clearer charts.

#### 2. UNDERSTANDING FPGAS UNDERVOLTING

Figure 2.7: Major observations under low-voltage operations in FPGA BRAMs for studied commercial platforms.

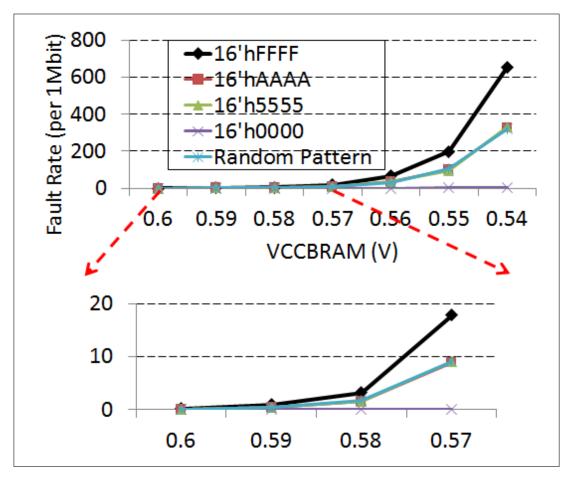

for VC707, ZC702, KC705-A, and KC705-B, respectively (with pattern= 16'hFFFF). Note that through our experimental observations, the vast majority of these faults are '1' to '0' bit flips, on average 99.9% for all platforms. We verify this observation by repeating the same tests with other data patterns. The fault rate is proportional to the number of '1' bits; for example, with pattern= 16'hFFFF the fault rate is

<sup>\*</sup> Different scales for different charts.

<sup>\*\*</sup> power results are reported as mWatts in ZC702 and in Watts for others.

<sup>\*\*\*</sup> At ambient temperature.

Figure 2.8: The impact of the data pattern in the fault rate on VC707 (similar behavior is observed for other platforms.)

almost double than pattern= 16'hAAAA, and with pattern=16'h0000 few faults are observed, as shown as an example on VC707 in Figure 2.8. In the same line, we did not observe any meaningful correlation in the various permutations of '0' and '1' in the data pattern, for instance, as can be seen, the fault rate of pattern= 16'hAAAA, 16'h5555, and a random pattern are almost the same.

# Fault Characterization Through FPGA BRAMs Undervolting

In this section, we comprehensively characterize the behavior of faults, where  $V_{CCBRAM}$  is underscaled at the CRITICAL voltage region from  $V_{min}$  to  $V_{crash}$ . Considering the impact of the data pattern that is explained in Section 2, the detailed fault characterization in this section is for data pattern= 16'hFFFF, which corresponds the highest fault rate since as shown in Section 2, '1'-to-'0' bit flips are much more common than '0'-to-'1' flips.. Understanding the behavior of undervolting faults can allow the deployment of efficient fault mitigation techniques and in turn, better reliability, energy, and performance trade-off can be achieved for FPGA designs.

### 3.1 Fault Stability Over Time

As earlier mentioned, we repeat each test 100 times to get statistically significant results. We did not observe a significantly different results among different runs, as shown in Table 3.1. Thus, the fault rates and as experimentally observed, faults locations show a stable behavior over time without meaningfully changing over the time. This observation is considered in our application-aware fault mitigation

# 3. FAULT CHARACTERIZATION THROUGH FPGA BRAMS UNDERVOLTING

Table 3.1: Fault rate stability over time. (Fault rate analysis of 100 runs at  $V_{crash}$  with pattern=16'hFFFF.)

| Parameter               | VC707 | ZC702 | KC705-A | KC705-B |

|-------------------------|-------|-------|---------|---------|

| AVERAGE fault rate*     | 652   | 153   | 254     | 60      |

| MINIMUM fault rate*     | 630   | 140   | 237     | 51      |

| MAXIMUM fault rate*     | 669   | 162   | 264     | 69      |

| STD. DEV of fault rates | 7.3   | 5.9   | 4.8     | 1.8     |

<sup>\*</sup> per 1 Mbit.

technique that is discussed in Chapter 4.

### 3.2 Fault Variability Among BRAMs

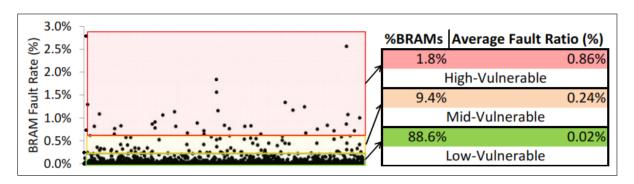

By statistically analyzing the experimental results, we observe that faults are not uniformly distributed over different BRAMs. Common for all platforms, we observe that a big percentage of BRAMs, *e.g.*, 38.9% in VC707 at the lowest voltage level  $V_{crash} = 0.54V$ , never experience faults; however, faults manifest in a small percentage of them. For instance, on VC707 when  $V_{CCBRAM} = V_{crash} = 0.54V$ , the maximum, minimum, and average fault rate within BRAMs are 2.84%, 0%, and 0.04%, respectively. For further analysis, we clustered this statistical information in low-, mid-, and high-vulnerable classes of BRAMs, using the k-means clustering algorithm. For all platforms, a vast majority of BRAMs are clusted as low-vulnerable. For instance, we show detailed results of VC707 in Figure 3.1. As can be seen, 88.6% of BRAMs are recognized as low-vulnerable with an average fault rate of 0.02%,  $\sim$  3.4 faults within an individual BRAM with the size of 1024\*16-bits.

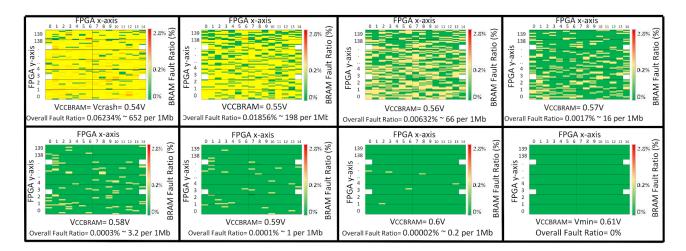

The fault rate variability among BRAMs is the result of the within-die process variation and as discussed earlier is permanent. Accordingly, we construct a chip-dependent Fault Variation Map (FVM). FVM is extracted by mapping the observed fault rates to the physical location of BRAMs on the tested chips. Through Vivado,

Xilinx toolkit, we extract the required information to build FVM, including the floorplan of the chip and the placement information of BRAMs. For instance, FVM of VC707 is shown in Figure 3.2, when  $V_{CCBRAM}$  is underscaled from  $V_{min} = 0.61V$  to  $V_{crash} = 0.54V$ . FVM has the granularity of BRAM. Note that in this figure other FPGA components are ignored for the sake of more clarity of FVM.

### 3.3 Fault Variability Within BRAMs

We performed a statistical analysis to analyze the fault distribution schema within those faulty BRAMs, from both column- and row-wise view.

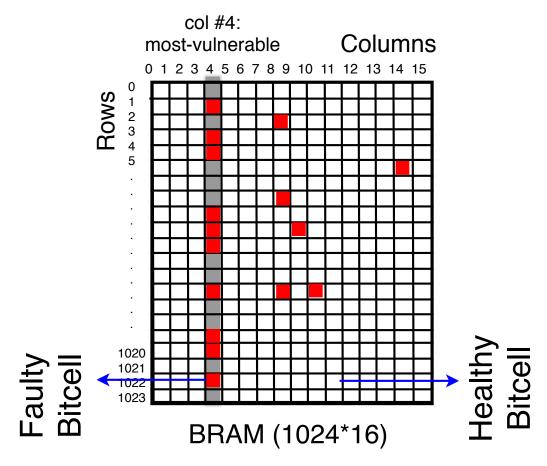

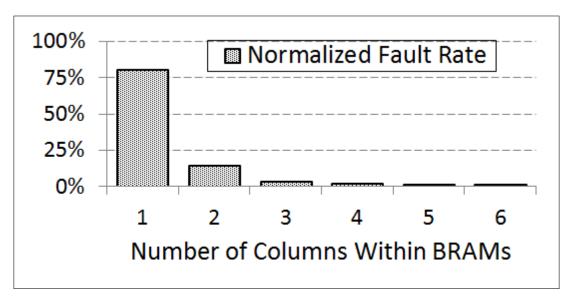

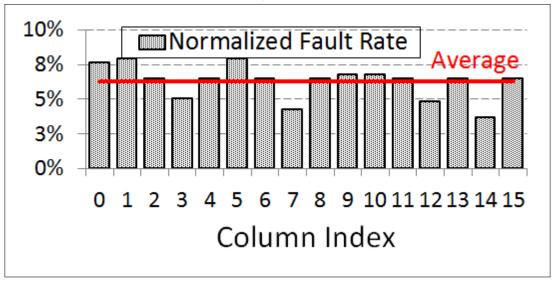

#### 3.3.1 Column-wise Fault Analysis

Our observations reveals that faults mostly occur in a few certain columns within BRAMs. In other words, for each faulty BRAM, a few (one or two) most vulnerable column of bitcells exist, among 16 available columns, as illustrated in Figure 3.3. Figure 3.4a shows the number of most vulnerable columns within faulty BRAMs. As can be seen, more than 80% of faults occur in a single column, 17% in two

Figure 3.1: Clustering BRAMs to low-, mid-, and high-vulnerable classes using K-mean algorithm.

<sup>\*</sup> This figure shows the clustering at  $V_{crash} = 0.54V$  for only VC707 since very similar behavior is observed for other platforms.

# 3. FAULT CHARACTERIZATION THROUGH FPGA BRAMS UNDERVOLTING

Figure 3.2: BRAMs Fault Variation Map (FVM), scaling  $V_{CCBRAM}$  from  $V_{min} = 0.61V$  to  $V_{crash} = 0.54V$ .

columns, and so on. However, these most vulnerable columns do not occur in identical column indexes, for different BRAMs. As can be seen in Figure 3.4b, there is almost a uniform distribution of fault rate in different 16 available column indexes, when fault rate is averaged for all BRAMs.

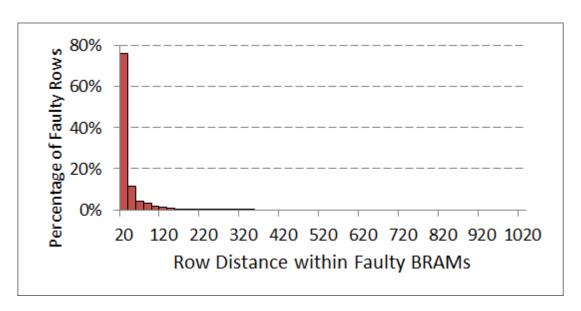

#### 3.3.2 Row-wise Fault Analysis

By a statistical analysis of locations of faults within faulty BRAMs, we observe that there is a spatial correlation between faulty rows. Our hypothesis is that the BRAM wordlines are weaker than bitlines to support low voltage operation. However, we were not able to verify this hypothesis since there is no publicly available document that details the circuit level design of Xilinx BRAMs. In other words, by increasing the distance between rows, the probability of the fault is considerably reduced. As

<sup>\*</sup> Each small rectangular box represents a BRAM mapped to the corresponding X and Y physical location on FPGA, shown for Virtex-7 FPGA in VC707 platform containing 2060 BRAMs.

<sup>\*\*</sup> White boxes represent the empty physical locations of BRAMs.

<sup>\*\*\*</sup> For a clearer representation, other FPGA components such as LUTs and DSPs are not shown.

Figure 3.3: Illustration of column-wise fault distraction within BRAMs.

shown in Figure 3.5, within our BRAMs with 1024 rows, the minimum distance of more than 90% of faulty rows is on average of 20. A similar behavior is discussed for systematic process variation [145], [89]; thus, our conclusion is that the behavior observed about the undervolting faults is the direct consequence of the systematic process variation.

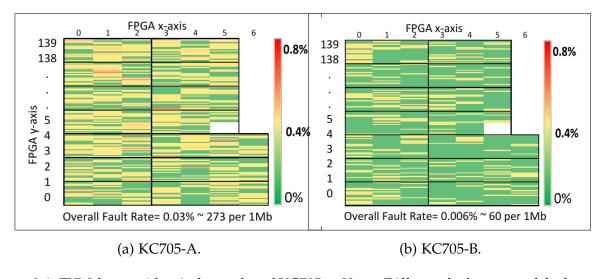

### 3.4 The Impact of the Die-to-Die Process Variation

We perform a further analysis of understanding the effects of voltage scaling on two samples of the same platform, *i.e.* KC705-A and KC705-B, which can show

(a) Column vulnerability within individual BRAMs.

(b) Column vulnerability among individual BRAMs.

Figure 3.4: Column-wise fault characterization within BRAMs.

the impact of the die-to-die process variation. As earlier noted, KC705-A shows a significantly higher fault rate. Furthermore, with extracting their FVMs, we observe a significant difference in the fault map among BRAMs, see Figure 3.6, thanks to

<sup>\*</sup> Shown for  $V_{CCBRAM}$  at  $V_{crash} = 0.54V$  for VC707.

Figure 3.5: Row-wise fault characterization within BRAMs.

<sup>\*</sup> Shown for  $V_{CCBRAM}$  at  $V_{crash} = 0.54V$  for VC707.

Figure 3.6: FVM for two identical samples of KC705 at  $V_{crash}$ . Different fault rates and fault locations (FVM) are experimentally observed.

the die-to-die process variation. For instance, BRAM#(116,1) has high-vulnerability in KC705-A; however, it has low-vulnerability in KC705-B.

### 3.5 Fault Inclusion Property (FIP)

Fault Inclusion Property (FIP) is a property that we experimentally observed by monitoring the fault location and rate under various supply voltages below  $V_{min} = 0.61V$ . FIP is said to exist if all the faulty bits in a certain level of  $V_{CCBRAM}$  are still faulty in further reduced levels of voltage. FIP was previously observed for CPU cache structures [58], here we confirm that FIP holds for FPGA on-chip memories as well, as visualized in Figure 3.7a for VC707 (verified for other platforms, as well). While it may not be the best representation as the figure shows the stacked fault rates; however, through our experimental results we observed both location as well as rate of faults in a certain voltage level are exactly repeated in lower voltage levels. Also, FIP in the BRAM-level can be seen in the FVM of Figure 3.2.

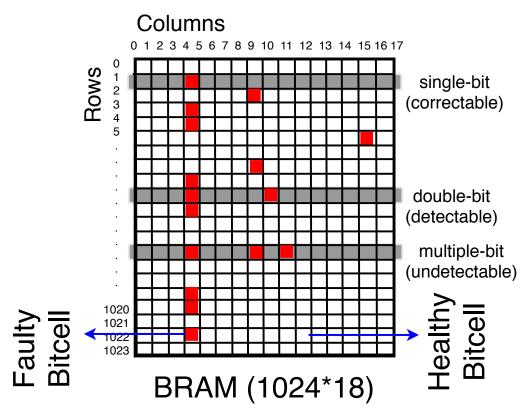

### 3.6 Type of Faults: Single-, Double-, Or Multiple-Bit?

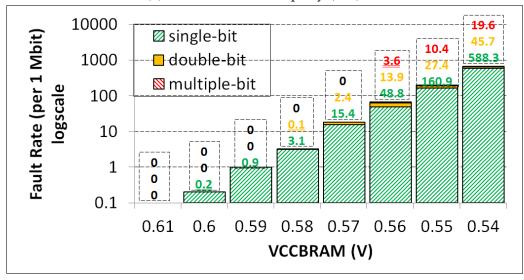

We categorize faults into or single-bit, double-bit, and multiple-bit faults. Figure 3.7b shows a histogram of these fault types, in different voltage levels at the critical voltage region, *i.e.*, from  $V_{min} = 0.61V$  to  $V_{crash} = 0.54V$  on VC707. We observe that first, a vast majority of these faults are single- or multiple-bit faults; for instance, more than 90% and a further 7% at  $V_{crash} = 0.54V$ , respectively. Second, by further voltage underscaling, single-bit faults manifest before double-bit, and in turn, double-bit faults manifest before multiple-bit faults. The faults behavior mentioned above is the consequence of the FIP. In other words, within a memory row which experiences faults, by further undervolting, those initial faulty bits are still faulty and also potentially expanded to other bits. Consequently, single-bit faults can be potentially converted to double-bit and similarly, double-bit faults can be potentially converted to multiple-bit faults.

(b) Single-, Double-, or Multiple-bit faults.

Figure 3.7: Further analysis of faults location, undervolting BRAMs from  $V_{min} = 0.61V$  to  $V_{crash} = 0.54V$ , shown for VC707.

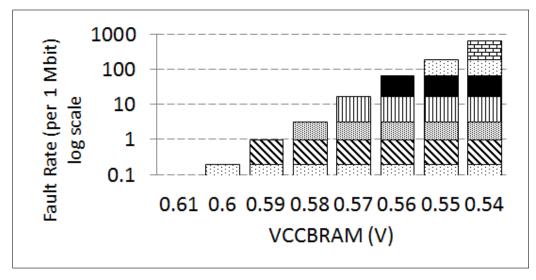

### 3.7 Impact of the Environmental Temperature

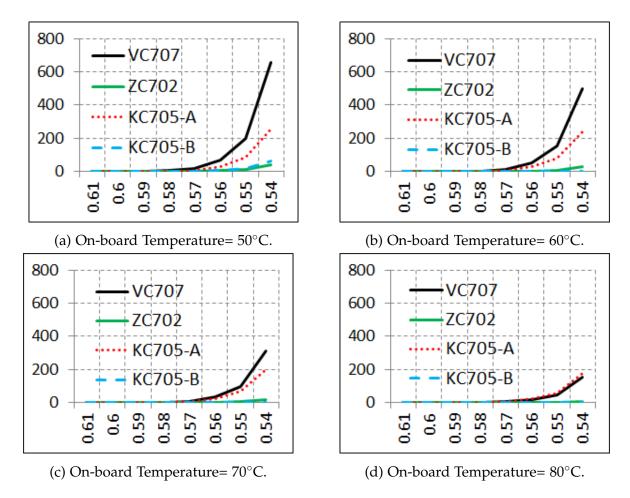

We perform an experiment to study the effect of the environmental temperature on the behavior of faults when  $V_{CCBRAM}$  is lowered below  $V_{min}$ . Toward this goal,

# 3. FAULT CHARACTERIZATION THROUGH FPGA BRAMS UNDERVOLTING

Figure 3.8: The correlation among on-board temperature, supply voltage of BRAMs, technology, and fault rate.

we place the hardware board inside a heat chamber where we regulate the temperature. We monitor the on-board temperature using PMBus commands. Through experiments, BRAMs fault rates are extracted and shown in Figure 3.8 under the on-board temperatures of 50°C (default temperature), 60°C, 70°C, and 80°C. As can be seen, with heating up, the fault rate constantly reduces; for instance, by more than 3X in VC707, when the temperature is increased from 50°C to 80°C. This observation is the consequence of the Inverse Thermal Independence (ITD)

<sup>\*</sup> x-axis:  $V_{CCBRAM}$  from  $V_{min} = 0.61V$  to  $V_{crash} = 0.54V$ .

<sup>\*\*</sup> y-axis: the fault rate per 1Mbit.

Figure 3.9: Different fault rate changes of the studied FPGA platforms over different temperatures at  $V_{CCBRAM} = V_{crash}$ .

property [117]. ITD is a thermal property of digital devices with nano-scale technology nodes; and states that under ultra low-voltage operations, the circuit delay reduces at higher temperatures. The reason is that as the technology node scales down, the supply voltage approaches the threshold voltage. Hence, at low-voltage regimes, increasing the temperature reduces the threshold voltage and allows the

Table 3.2: Summary of fault characterization in FPGA-Based BRAMs and comparing with the modern DRAMs, i.e,. DDR-3.

| BRAM [our work]                        | DRAM [36]                              |  |

|----------------------------------------|----------------------------------------|--|

| Large voltage margin.                  | Large voltage margin.                  |  |

| Fault type: stuck-at-0                 | Fault type: No Info!                   |  |

| Pattern-dependent Faults               | Pattern-free Faults                    |  |

| Exponential Fault Rate up to ~0.1%     | Exponential Fault Rate up to ~20%      |  |

| Significant Variation among BRAMs      | Significant Variation among DRAM Banks |  |

| Follows Fault Inclusion Property (FIP) | No Info!                               |  |

| Inverse Relation of Temperature        | Direct Relation of Temperature         |  |

| and Fault Rate                         | and Fault Rate                         |  |

# 3. FAULT CHARACTERIZATION THROUGH FPGA BRAMS UNDERVOLTING

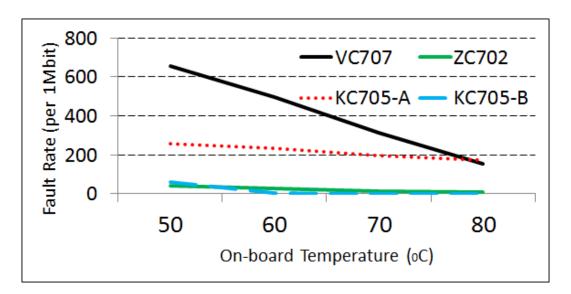

device to switch faster. In turn, with the circuit delay decreasing, the number of critical paths, and subsequently, the fault rate reduces. This property is experimentally verified in our case, for commercial FPGAs. Also, as can be seen in Figure 3.9, the fault rate in VC707 is reduced more aggressively than KC705-A. A relatively 156% more fault rate in 50°C is reduced to 11.6% less fault rate in 80°C, for VC707 vs. KC705-A. The architectural and technological difference between these platforms can be the reason since their design goal is different, *i.e.*, performance (VC707) vs. power (KC705-A). Also, by heating up, the fault rate is significantly lower for VC705-B than KC705-A, as the consequence of the process variation.

### 3.8 Summary

We presented comprehensive fault characterization results under BRAM undervolting below  $V_{min}$ . Our experimental observations such as stuck-at-0 behavior of faults and significant fault rate variability among BRAMs, can provide an opportunity to optimize power-reliability trade-offs in aggressively low-voltage regimes, for applications implemented onto FPGAs. We summarize our observations and findings in Table 3.2. Also, we compare our observations with a recent characterization work on DDR-3 [36], mostly in the behavioral-level. Although, there is a technological difference between them, *i.e.*, BRAMs are SRAM-based while DDR-3 are DRAM-based, the comparison highlights their significant similar fault behavior under low-voltage operations; although, there are some differences, as well. For instance, the effect of the environmental temperature and also the type of faults (mostly '1'-to-'0' bit flips for BRAMs versus more uniform for DDR-3) are the main differences, which can be due to the architectural difference among two memories.

4

# Evaluating FPGA-based NN Accelerator on Low-Voltage FPGA BRAMs

In this chapter, we present and discuss the results of our study on the impact of the BRAM voltage scaling below nominal level,  $V_{nom} = 1V$ , in a typical FPGA-based NN accelerator. More specifically, our study includes the power consumption and NN accuracy trade-off, and investigation of two fault mitigation technique when NN is operating below  $V_{min}$ , *i.e.*, a proposed intelligent placement technique and also, built-in ECC. First, we briefly describe the NN resilience and the experimental methodology, and later on, discuss the efficiency of low-voltage FPGA-based NN.

### 4.1 Background on NN Resilience

Machine learning models and in particular NNs are increasingly being used in the context of nonlinear "cognitive" problems, such as natural language processing and computer vision. These models can learn from a dataset in the training phase and make predictions on a new, previously unseen data in the inference/prediction/classification phase with ever-increasing accuracy. However, the compute-and power-intensive nature of NNs prevents their effective deployment in resource-constrained environments, such as mobile scenarios [175]. Hardware acceleration,

e.g., FPGAs offers a roadmap for enabling NNs in these scenarios [152], [94], [135], [42], [16], [74]. However, similar to general purpose devices, hardware accelerators are also susceptible to faults (permanent/hard and transient/soft), as more specifically studied in this thesis, as the result of the aggressive voltage underscaling approach.

In recent years NN resilience is studied with different approaches, *e.g.*, software-level simulations or theoretical analyzes [156], [132], SPICE simulations [135], [93], [180], [181], and experimenting on the real hardware operating on low-voltage regimes, *e.g.*, SRAMs [165], [174], [173]. Among them, it is evident that software-level simulations and theoretical analyzes lack the information of the underlying hardware platform and are relatively less precise. In contrast, SPICE-based studies are more precise; however, these studies require significant circuit-level efforts.

Among the most relevant existing works on the NN resilience, Minerva [135] performs a characterization on the sparsity of data and analyzes the efficiency of leveraging fixed-point data representation model. In the same line, [157] studied the vulnerability of various layers of NN. Also, recently [93] studied the fault propagation in an ASIC model of NN focused on the vulnerability of different NN layers. This thesis approaches the resilience study on real faults that are generated through aggressive undervolting.

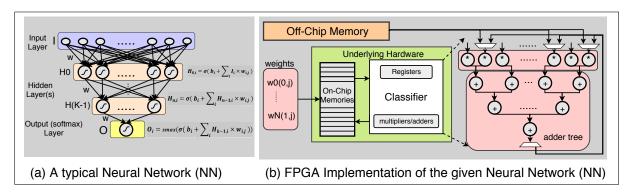

#### 4.1.1 The Architecture of the NN Accelerator

Specifications of the experimented RTL NN with a baseline configuration is summarized in Table 4.1. Our study features a typical fully-connected NN that is also widely used in the structure of other NN models [135]. Our study targets the inference phase of NN since training is normally a one-time process; additionally, the inference is repeatedly performed to classify unknown data. As can be seen in Figure 4.1(a), this NN model is composed of input, hidden, and output layers,

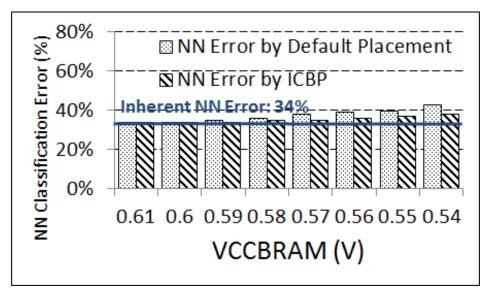

where all adjacent layers are fully connected to each other. The first/last layer is the input/output layer and has one neuron for each component in the input/output vector. Between the input and output layers, there are single/multiple hidden layers. The interconnection between neurons of adjacent layers is determined based on a collection of weights and biases, whose values are tuned in the training phase. Each NN neuron uses an activation function to determine its output. Finally, in the output layer, a softmax function generates the final output of the NN. We perform our experiments on a 6-layer NN, *i.e.*, ( $\{L_i, i \in [0,5]\}$ ), one input, four hidden, and one output layer(s). The four hidden layer sizes are fixed at 1024, 512, 256, 128 while input and output layer sizes are benchmark-dependent (784, 54 and 2437 for input while 10, 8 and 52 for output layers for the three NN applications studied in this thesis, *i.e.*, MNIST [87], Forest [24], and Reuters [25], respectively.). Thus, there are five matrix multipliers among adjacent layers, i.e., ({Layer<sub>i</sub>,  $j \in [0,4]$ }), where  $Layer_i$  refers to the matrix multiplication of  $L_i$  and  $L_{i+1}$ . Among benchmarks, MNIST is a set of black and white digitized handwritten digits, each image composed of 784\*8-bit pixels, the output infers the number from 0 to 9 (10 output classes), with 60000 training- and 10000 inference images. Forest includes cartographic observations for classifying the forest cover type. Reuters covers news articles for text categorization. MNIST is most widely-used by the ML community to evaluate the efficiency of novel NN methods. Hence, we use MNIST as the main benchmark to evaluate our resilience studies. To demonstrate the generality of experimental observations, we briefly present results for Forest and Reuters, as well.

For experiments, we first export weights and biases of the trained NN that is performed off-line using a MATLAB implementation, initialize BRAMs of FPGA, and then start streaming 10000 input images to perform the inference. Also, for representing data, we use the fixed-point low-precision model. Note that lowering

Figure 4.1: The overall methodology to resilience study of the RTL NN Accelerator.

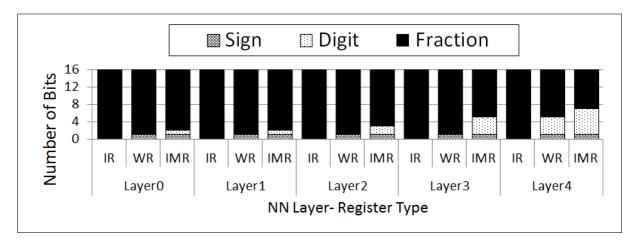

the precision of data is a common technique for applications in the approximate computing domain, in particular for NNs performing inference [60], to achieve power and performance efficiency with negligible accuracy loss. Following this approach, we use a per-layer minimum precision fixed-point model. The bit-width of data (input, weights, and intermediate) is fixed to 16-bits, composed of the sign, digit, and fraction components. Toward this goal, with a pre-processing analysis, we extract the minimum bit-widths of the sign and digit components per layer, and the fraction component fills the rest of the 16 bits. As we experimentally observed, this quantification does not lead to any considerable accuracy loss in comparison to a full-precision data model. The minimum precision is used in this thesis is summarized in Figure 4.2.

### 4.2 Experimental Methodology of NN Evaluations

We perform our studies on the NN that is that is shown in Figure 4.1(b) and summarized in Table 4.1. In our system architecture, weights of the NN are located inside BRAMs and input images are being streamed through the off-chip DDR-3. The required calculation of the image classification, matrix multiplication plus sigmoid function activation, are performed in parallel by leveraging DSPs and LUTs

Table 4.1: Detailed specifications of the baseline RTL NN setup.

| Neural Network (NN)                                  |                                      |  |  |  |

|------------------------------------------------------|--------------------------------------|--|--|--|

| Туре                                                 | Fully-Connected                      |  |  |  |

| Phase                                                | Inference                            |  |  |  |

| Topology (number of layers)                          | 6L (1L input, 4L hidden, 1L output)  |  |  |  |

| Per Layer Size (number of neurons)                   | (784, 1024, 512, 256, 128, 10)= 2714 |  |  |  |

| Total Number of Weights                              | $\sim$ 1.5 million                   |  |  |  |

| Original Activation Function                         | Logarithmic Sigmoid (logsig)         |  |  |  |

| Original Benchmark                                   |                                      |  |  |  |

| Name                                                 | MNIST [87]                           |  |  |  |

| Type                                                 | Handwritten Digits (Images)          |  |  |  |

| Number of Images                                     | Training: 60000, Inference: 10000    |  |  |  |

| Number of Pixels per Image                           | 28*28= 784                           |  |  |  |

| Number of Output Classes                             | 10                                   |  |  |  |

| Additional Benchmarks                                |                                      |  |  |  |

| 1. Forest (cartographics of forest types)            | [24]                                 |  |  |  |

| <b>2. Reuters</b> (articles for text categorization) | [25]                                 |  |  |  |

| Data Representation Model                            |                                      |  |  |  |

| Туре                                                 | 16-bits Fixed-Point (Figure 4.2)     |  |  |  |

| Sign-bit Precision                                   | Minimum per layer (1 or 0 bit)       |  |  |  |

| Digit-bit(s) Precision                               | Minimum per layer                    |  |  |  |

| Fraction-bit(s) Precision                            | 16- (number of sign- and digit-bits) |  |  |  |

| An Example Synthesize Results                        |                                      |  |  |  |

| FPGA Platform-Chip                                   | VC707-Virtex7                        |  |  |  |

| Maximum Operating Frequency                          | 100Mhz                               |  |  |  |

| BRAM Usage (Total: 2060)                             | 70.8%                                |  |  |  |

| DSP Usage (Total: 2800)                              | 8.6%                                 |  |  |  |

| <b>FF Usage</b> (Total: 303,600)                     | 3.8%                                 |  |  |  |

| LUT Usage (Total: 607,200)                           | 4.9%                                 |  |  |  |

| Number of PEs                                        | 64                                   |  |  |  |

Figure 4.2: Minimum precision to represent data of RTL NN, *i.e.*, Inputs (*IRs*), Weighs (*WRs*), and Intermediate (*IMRs*).

of the FPGA and results are streamed to the host computer to perform the final step of the NN accuracy analysis. This setup is typical for most of the FPGA-based NN accelerator, as surveyed in [59]. In this section, we present results for the VC707 platform since a very similar efficiency is observed for other platforms.

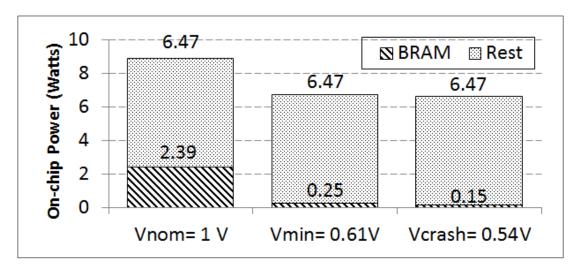

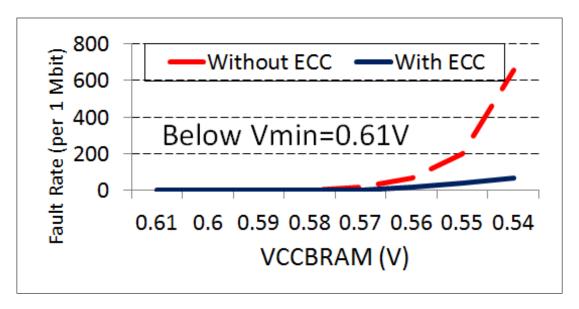

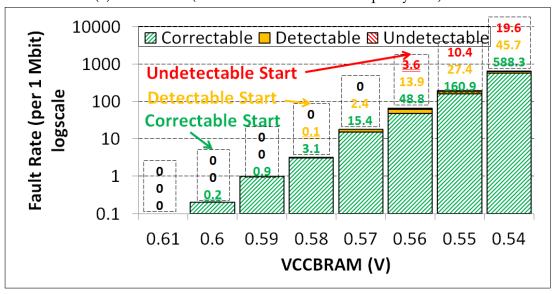

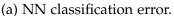

On this setup, the on-chip power breakdown at various  $V_{CCBRAM}s$ , i.e.,  $V_{nom} = 1V$ ,  $V_{min} = 0.61V$ , and  $V_{crash} = 0.54V$ , is shown in Figure 4.3. As can be seen, more than an order of magnitude BRAM power dissipation is reduced from  $V_{nom} = 1V$  to the guardband gap on  $V_{min} = 0.61V$ , which in turn delivers 24.1% total on-chip power reduction. Further voltage lowering to  $V_{crash} = 0.54V$ , reduces 40% of BRAM power over  $V_{min} = 0.61V$ ; however, as a result of the timing faults, the NN classification error is in turn impacted. This impact and the proposed fault mitigation technique are discussed later in this section.

Figure 4.3: On-chip power breakdown of our FPGA-based NN at  $V_{nom}$ ,  $V_{min}$ , and  $V_{crash}$  (VC707). Rest includes on-chip power consumption of DSPs, LUTs, routing resource, etc.

Figure 4.4: Impact of BRAM voltage scaling in the NN classification error, lowering  $V_{CCBRAM}$  from  $V_{min} = 0.61V$  to  $V_{crash} = 0.54V$ .

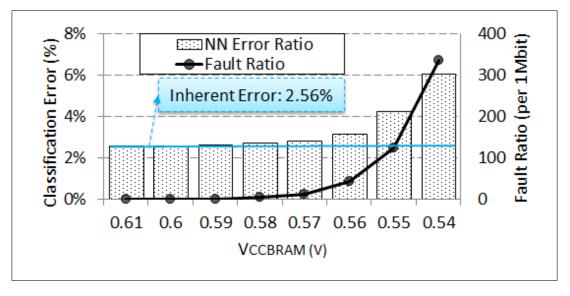

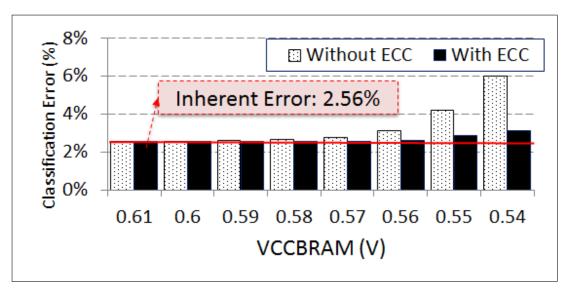

# 4.3 Impact of Voltage Scaling Below $V_{min}$ on the NN Accuracy

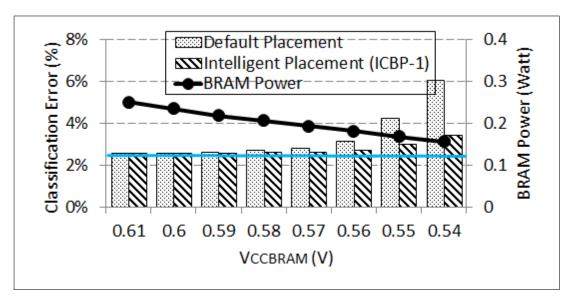

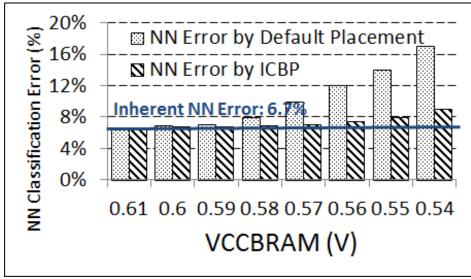

When  $V_{CCBRAM}$  is underscaled in the critical region between  $V_{min} = 0.61V$  and  $V_{crash} = 0.54V$ , faults occurring in some of BRAMs bitcells degrade the NN accuracy. In fact, the classification error is increased from 2.56% (inherent classification error without any fault) to 6.15% when  $V_{CCBRAM} = V_{crash} = 0.54V$ , see Figure 4.4. The NN classification error (left y-axis) increases exponentially, correlated directly with the fault rate increase in BRAMs (right y-axis), as expected. Also, we observe that the fault rate in BRAMs filled with the NN weights is significantly less than the default pattern= 16h'FFFF. The reason is that weights are sparse, our statistical analysis indicates that 76.3% of the bits having the logic value '0'. These bits have a negligible probability to be flipped, especially considering that most of the timing faults in the critical low voltage operation are stuck-at-0. This experimentally verified failure characteristic is the reason that MNIST application on our NN is inherently fault-tolerant against faults in extremely low-voltage operations on FPGAbased BRAMs. Through statistical experimentation, we confirm this data sparsity for other NN benchmarks such as Forest [24] and Reuters [25]. Also, other state-ofthe-art has also confirmed the sparsity of many other NN benchmarks [135], [112], and a wider range of other applications, as well [8]. It means these applications would be inherently fault-tolerant for the type of failures experienced in FPGA BRAM undervolting.

### 4.4 Fault Mitigation Techniques

To prevent NN accuracy loss under low-voltage operations, we evaluate two techniques, *i.e.*, a novel BRAM placement technique and built-in ECC.

Figure 4.5: Methodology of Intelligently-Constrained BRAM Placement (ICBP).

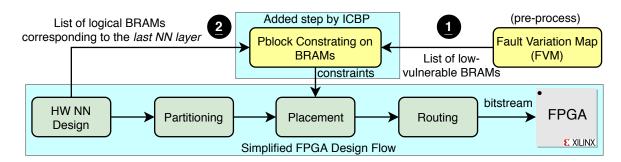

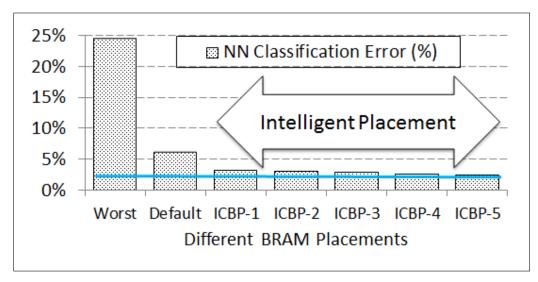

#### 4.4.1 Intelligently-Constrained BRAM Placement (ICBP)

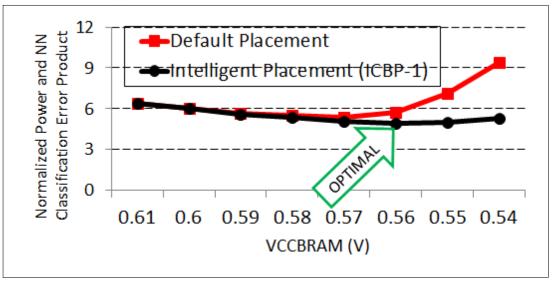

The overall methodology of the proposed fault mitigation technique, Intelligently-Constrained BRAM Placement (ICBP), is shown in Figure 4.5. It can be used for low-voltage regions below  $V_{min} = 0.61V$ . The principal motivation is that low-voltage operations dramatically reduce power consumption (for our case, 40% in  $V_{crash} = 0.54V$  over  $V_{min} = 0.61V$ ); however, cause faults, which, in turn, leads to NN accuracy loss (for our case, 3.59% additional NN classification error in  $V_{crash} = 0.54V$ ). The objective is to achieve this power-savings without significant impact on the NN classification error.

#### **Elaborating ICBP**

ICBP relies on two key observations:

- 1 As detailed in Section II, we observed that faults occur in reduced voltage BRAMs have deterministic and chip-dependent behavior with an entirely non-uniform distribution between different BRAMs that is exposed as FVM. As earlier mentioned, FVM extraction is a pre-processing stage.

- 2 We observed that various layers of the given NN have a different inherent vulnerability to faults. We conducted a pre-processing analysis and observed that inner layers (layers closer to the output) are relatively more vulnerable,

as similarly observed in [142], [157], [93], since faults in these layers have relatively less probability to be masked through the quantification in the activation functions. The sensitivity of NN layers, *i.e.*,  $\{Layer_j, j \in [0,4]\}$  is evaluated by injecting simulated randomly-generated faults in corresponding weights of individual layers at the Register-Transfer Level (RTL). In other words, we inject some random faults in weights of individual NN layers and let the NN accomplishes the classification. By monitoring the classification error of the faulty NN, we can evaluate the vulnerability of each NN level.

Due to these observations, ICPB introduces a simple yet effective BRAM placement algorithm that maps the weights of the inner NN layers to low-vulnerable BRAMs, targeting to mitigate faults and achieve power-savings with minimized NN classification accuracy loss. Note that FPGAs are uniquely suited to benefit from ICBP. In comparison, CPUÂt's have inherent disadvantages that make it challenging to apply aggressive undervolting ideas such as ICBP for their on-chip memories due to two reasons: *First*, it is extremely difficult, if not impossible to construct the undervolting fault map for CPU on-chip memories such as caches. *Second*, it is very cumbersome, if not impossible, to reconfigure and remap application data into cache regions that have a low vulnerability.

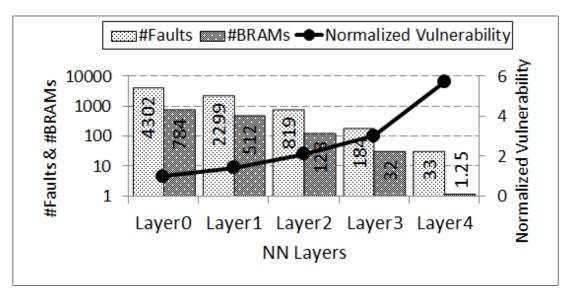

For further analysis, we present detailed statistical information of the different layers of the given NN, *i.e.*, the size (in terms of utilized number of BRAMs to locate weights of the corresponding NN layer), number of faults, and the normalized vulnerability of the individual layers, as shown in Figure 4.6. As can be seen, outer layers (closer to the input layer) are relatively larger, which experience more faults, as expected. Note that by statistical analysis, we observed that outer layers are relatively more sparse; thus, the per-layer fault rate is not precisely proportional to

Figure 4.6: Statistical analysis of NN layers: size (#BRAMs), #Faults (at  $V_{crash} = 0.54V$ ), and normalized vulnerability.

the per-layer size; however, both size (number of BRAMs) and the number of faults show an exponential behavior among various layers. Also, it is important to note that we conducted a software-based statistical fault injection campaign to extract the vulnerability of different NN layers. As can be seen, for instance,  $Layer_5$  is around 6X more vulnerable than the first one,  $Layer_0$ , which means that the same rate of faults injected in  $Layer_4$  causes 6X NN classification error than injecting the same number of faults in  $Layer_0$ . The conclusion of analyzing different NN layers is that inner layers are significantly smaller and relatively less probable to experience faults; however, they are the most vulnerable layers. In other words, a fault in a inner NN layer has a more significant impact on the quality of the result; thus, they need better protection.

#### Implementation Methodology of ICBP

As earlier noted, in ICBP we aim to constrain the BRAM placement algorithm to map the logical BRAMs of inner NN layers to low-vulnerable physical BRAMs in

List 4.1: Illustrating Pblock Creation and BRAM Assignement for FPGAs.

**1:** *create\_pblock* low-vulnerable\_pblock

#### %Creation of a Pblock, low-vulnerable\_pblock

**2:** resize\_pblock [get\_pblocks low-vulnerable\_pblock] -add {RAMB18\_X0Y44 RAMB18\_X3Y91 RAMB18\_X1Y26}

#### %Assigning 3 physical BRAMs to low-vulnerable\_pblock

**3:** *add\_cells\_to\_pblock* [get\_pblocks low-vulnerable\_pblock] [get\_cells -quiet [list {l-BRAM[0]}{l-BRAM[1]}]]

%Assigning 2 logical BRAMs to low-vulnerable\_pblock

the chip. Note that logical BRAMs are defined in the high-level Verilog design description and in contrast, physical BRAMs refers to the BRAM locations in the FPGA. Toward this goal, we exploit the Physical Blocks (Pblocks) facility of Vivado, a Xilinx implementation tool. Pblocks provides a fully flexible facility to constrain logical blocks, *e.g.*, BRAMs, to a physical region in the FPGA. As described in Section 3.2, we classify physical BRAMs into low-, mid-, and high-vulnerable classes. Having the list of physical locations of these BRAMs (XY), we first, create corresponding low-, mid-, and high-vulnerable Pblocks and then, appropriately assign the logical BRAMs into these Pblocks.

The example in List 4.1 illustrates the creation and BRAM assignment of Pblocks using TCL commands. This example creates a Pblock (low-vulnerable\_pblock), assigns three physical BRAMs in locations (X0Y44, X3Y91, and X1Y26), and adds two logical BRAMs (l-BRAM[0] and l-BRAM[1]). This is a post-synthesize constraint that is added to the Xilinx Design Constraints (XDC) file. In consequence, the placement tool of Vivado will try to find the most efficient placement of these two logical BRAMs into the specified three physical BRAMs locations. By following this methodology, we create our three low-, mid-, and high-vulnerable Pblocks, each includes the corresponding physical BRAMs specified by our fault characterization.

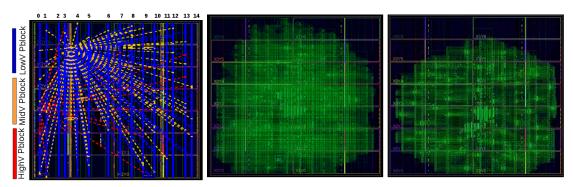

(a) The schematic of Low- (b) The Schematic of the (c) The schematic of the , Mid-, and High-vulnerable Proposed ICBP in NN de- Default Placement in NN Pblocks.

Figure 4.7: Pblocks and its Impact in the Schematic of the NN Design Placement in VC707 Platform.

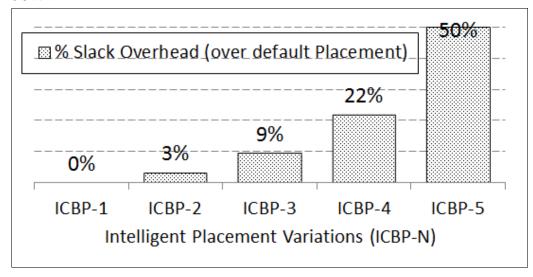

Figure 4.7a shows a schematic of the created Pblocks in the VC707 platform. As expected, the low-vulnerable\_pblock is dominating since it involves 88.6% of physical BRAMs. Also, the effect of ICBP in the final implementation of the design can be seen by comparing its schematic view in Figure 4.7b with the default placement (without any Pblock constraint) in Figure 4.7c. Note that Figure 4.7b refers to the design that all logical BRAMs of our design including all weights (not only the inner layers) are forced to be located in low-vulnerable BRAMs. As expected, the default placement results in more compacted design since the low-vulnerable BRAMs are distributed all over the chip, which limits ICBP to make a more compacted design. This specific design increases the timing slack by 50% over the default placement. However, as earlier noted, we aim to locate only inner layers of the NN into low-vulnerable BRAMs, which can eliminate this overhead, thanks to their significantly smaller sizes of inner layers. Later in this section, we discuss this trade-off and different aspects of ICBP.

#### **Experimental Results of ICBP**