© 2017 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

# Experimental verification of memristor-based material implication NAND operation

# M. Maestro, J. Martin-Martinez, A. Crespo-Yepes, M. Escudero, R. Rodriguez, M. Nafria, X. Aymerich and A. Rubio

Abstract— Memristors are being considered as promising devices for highly dense memory systems as well as the potential basis of new computational paradigms. In this scenario, and in relation with data processing, one of the more specific and differential logic functions is the material implication logic also named as IMPLY logic. Many papers have been published in this framework but few of them are related with experimental works using real memristor devices. In the paper authors show the verification of the IMPLY function by using Ni/HfO<sub>2</sub>/Si manufactured devices and laboratory measurements. The proper behavior of the IMPLY structure (2 memristors) has been shown. The paper also verifies the proper operation of a two-steps IMPLY-based NAND gate implementation, showing the electrical behavior of the circuit in a cycling operation. A new procedure to implement a NAND gate that requires only one step is experimentally shown as well.

Index Terms— IMPLY function, material implication, memristive circuits, memristors, NAND gate implementation, resistive switching.

# I. INTRODUCTION

Memristors, firstly introduced in 1971 by L. Chua [1] and later revisited by the research group of S. Williams from HP Labs in 2008 [2], present very advantageous characteristics such as fast operation, high scalability and low power consumption [3]-[11] as well as non-volatility. These features have attracted the interest of the scientific community to study memristors as potential candidates to implement complex memory blocks [3],[11], neuromorphic systems [12], [13], analog and digital processing circuits [14]–[19] and in-memory computation systems [20], [21]. In this sense, one of the most innovative and interesting applications of memristors is data computing. Memristors introduce new paradigms to implement logic computing, not based on the traditional Von Neumann architecture where the data are separately stored in memory and processed in a processor, but overlapping them in the same structure [21], [22]. In this sense, memristor-based material implication (IMPLY) logic gate was proposed in [14] as a 'stateful' logic where the data can be processed and stored in the same element. Several works have explored the use of material implication for logic applications. In [23], several strategies for arithmetic operations with memristors-based structures are described and the design of an adder and a multiplier is presented. In [24] the authors also examine the use of memristors to design different types of adders. In [25], a design methodology of the IMPLY logic family, including some design requirements to support the IMPLY logic family are described. However, these and most of the works presented in the literature are only based on simulations and a lack of experimental works related to material implication logic implemented with real devices is observed. Between the very few experimental works presented in the literature, in [26] a study of material implication-based gates is done, but using SiOx-based memristors and it is only focused on the IMPLY gate. Therefore, experimental works to finally demonstrate the functionality of the material implication-based logic circuits and to verify the promising results expected from simulations are still needed. Thus, in this paper, a deeper experimental investigation to contribute to the final validation of the use of material implication as a new paradigm of computing architecture is performed.

Usage of memristors in IMPLY gates can be shown thanks to the Resistive Switching (RS) phenomenon which takes place in Metal-Insulator-Semiconductor or Metal-Insulator-Metal (MIS/MIM) structures and consists in successive changes between two different resistance states of the dielectric named Low Resistance State (LRS) and High Resistance State (HRS), showing a memristive behavior. Unipolar resistive switching in MIS memristors can be described by thermochemical processes [27]. First change from HRS to LRS is possible due to the growth of a conductive filament along the insulator region, connecting top electrode and bottom electrode. Filament formation is governed by the temperature and field-induced generation of defects [28]. On the contrary, in LRS-HRS change, the previously formed filament is partially destroyed limiting the conduction between the

albert.crespo@uab.es, rosana.rodriguez@uab.es, montse.nafria@uab.es,

xavier.aymerich@uab.es).

<sup>&</sup>quot;This work was supported in part by the Spanish MINECO and ERDF (TEC2013-45638-C3-1/2-R) and the Generalitat de Catalunya (2014SGR-384)".

M. Maestro, J. Martin-Martinez, A. Crespo-Yepes, R. Rodriguez, M. Nafria and X. Aymerich are with the Departament d'Enginyeria Electrònica, Universitat Autònoma de Barcelona, Bellaterra 08193, Spain (e-mail: marcos.maestro@uab.es, Javier.martin.martinez@uab.es,

M.escudero and A. Rubio are with the Electronic Engineering Department, Universitat Politecnica de Catalunya, Barcelona, 08034, Spain (e-mail: manuel.escuredo@upc.edu, antonio.rubio@upc.edu).

top electrode and the bottom controlled by thermally electrode atoms induced by HRS and LRS states can be values implicated in digital allowing the implementation in which material implication

Section II describes the experimental devices revisit the principles of the III, the IMPLY and NAND demonstrated on fabricated section IV a new procedure to operation is proposed, which sequential steps from 2 to 1 as [20]. The procedure to

Fig. 2. Typical I-V characteristic of the memristors used in this work. Voltage polarity to provoke Set and Reset processes is negative.

electrode. This process is enhanced diffusion of top local joule heating [28]. The related with the two Boolean '0' operations, and ·1<sup>'</sup>, of logic gates with memristors is based [26]. composition of the employed in the work and we IMPLY function. In section logic gates are experimentally MIS-memristors. Moreover, in perform the NAND logic reduces the number of proposed in previous works improve NAND gate

implementation can be extended to perform other logic gates, with the subsequent saving of the computing time. Finally, section V concludes with a summary of the main results.

# II. MEMRISTORS DESCRIPTION

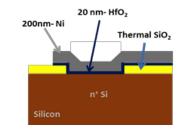

Fabricated memristors used in this work are Ni/HfO<sub>2</sub>/Si MIS devices based on (100) n-type CZ silicon wafers with resistivity between 0.007 $\Omega$ cm and 0.013 $\Omega$ cm [29]. After standard wafer cleaning, a wet thermal oxidation process was done at 1100°C leading to a 200nm-thick SiO<sub>2</sub> layer. This field oxide was patterned by photolithography and wet etching. Prior to the high-k deposition, a cleaning in H<sub>2</sub>O<sub>2</sub>/H<sub>2</sub>SO<sub>4</sub> and a dip in Hf(5%) were performed. Subsequently, 20nm-thick HfO<sub>2</sub> layers were grown by atomic layer deposition (ALD) using Tetrakis (dimethylamido)-hafnium (TDMAH) and H<sub>2</sub>O as precursors, and N<sub>2</sub> as carrier and purge gas. The deposition temperature was 225°C. The top metal electrode, consisting of a 200nm-thick Ni layer, was deposited by magnetron sputtering. The resulting structures are square cells of 5x5µm<sup>2</sup>. A schematic cross-section of the final device structure is shown in Fig. 1.

In Fig. 2, typical I-V characteristic of a memristor is depicted. Voltages at which samples change from HRS to LRS ( $V_{SET}$ ) and from LRS to HRS ( $V_{RESET}$ ) and current at LRS ( $I_{LRS}$ ,  $I_{ON}$ ) and at HRS ( $I_{HRS}$ ,  $I_{OFF}$ ) are also indicated. In these samples, which present both bipolar and unipolar behavior, the unipolar type with negative voltage polarity to trigger set and reset processes gives the best endurance results of the RS phenomenon [30], [31]. More than 3000 cycles of negative switching can be reached [30]. During SET process, current was limited to  $250\mu$ A to guarantee good functionality of the memristor. An analysis of the energies involved in the triggering of the set and reset mechanisms, which are of the order of pJ and  $\mu$ J, respectively, can be found in [32]. On the other hand, the stability and variability of these samples has been previously presented in [30], [31]. Cycleto-cycle variability, in voltages and currents, seems to be important, although, not so relevant for the gate functionality. Despite the fact that the goal of this paper is not the study of variability implications, device-to-device variability has been also observed to decrease gate operation success percentages. To perform all the measurements presented in this work, around 15 samples were used.

In the memristor samples employed in this work, initially, approximately 20 cycles changing successively between LRS and HRS were performed on each memristor, in order to achieve a stable behavior of the conductive filament generation/destruction. After this previous forming process, successive changes between the HRS and LRS in the cell can be performed with set and reset voltages and currents in a reduced range of values. When memristor is at HRS (see Fig. 2), there is a low current flow,  $I_{OFF}$ , due to the fact that the conductive filament is partially broken and, digitally, this state is associated to a '0' Boolean value. On the contrary, when memristor is at LRS (Fig. 2) a significant current flow,  $I_{ON}$ , is allowed through the conductive filament. In this case, this state is associated to the Boolean value '1'. In this work, instead of evaluating the memristor resistance, we have considered the values of  $I_{OFF}$  and  $I_{ON}$  currents (measured at -0.8V) as a measure of the '0' and '1' logic states, respectively, for an easier understanding of the experimental results. Therefore, the maximum value of memristor current to be considered as '0' has

been stablished at  $0.1\mu$ A, achievable for the current to

#### III. MEMRISTOR-BASED

Fig. 3 (a) schematically two memristors (P and Q) connected to a resistance terminal grounded. Top

Fig. 1. Cross-section of the memristor device used in this work.

whereas the minimum value be '1' state has been  $10\mu$ A.

#### LOGIC GATES DESCRIPTION

shows an IMPLY gate, where have their bottom electrodes  $(R_G)$ , which has the other electrodes of memristors are

to apply operational used the literature this voltage is avoid misunderstanding with considered instead), in order to table shown in Fig. 3(c). The or 'if P then Q', being the state possible combinations of the P and Q result in four different table. In case 1, for example, initially at HRS, i.e. '0' logic voltage values are applied to to LRS because the voltage provoke such resistance change. remains unaltered keeping '0' is below the voltage necessary change. For the rest of the provoked in any of the operational voltage values as in kept accomplishing the truth circuital analysis of the IMPLY

The IMPLY gate can be the

Fig. 3. (a) IMPLY and (b) NAND gates schematic circuits. (c) IMPLY and (d) NAND gates truth tables

voltages, V<sub>COND</sub> and V<sub>IMPLY</sub> (in labeled as V<sub>SET</sub>, however to V<sub>SET</sub> in Fig. 2, V<sub>IMPLY</sub> is implement the IMPLY truth gate operates as 'P implies Q' of O the output of the gate. The initial logic states of memristors cases, as it is indicated in the both memristors must be state, then, when the proper the memristors, Q state changes drop across it is enough to On the contrary, the state of P logic state since its voltage drop to originate a resistance state cases, no state change is memristors. Applying the same case 1, initial logic states are table in Fig. 3(c). A detailed gate can be found in [15]. basis to implement other logic

gates. Fig. 3(b) shows the schematics of a NAND gate. The structure is similar to the IMPLY gate but, in this case, a third memristor (S), biased with V<sub>S</sub>, is added to P and Q of the IMPLY gate as indicated in the Fig. 3(b) [25]. The output of the NAND cell is stored in the state of memristor S. The truth table of the NAND gate is indicated in Fig. 3(d). Note that R<sub>G</sub> value has been 1M $\Omega$ , in order to accomplish the relation R<sub>ON</sub><R<sub>G</sub><R<sub>OFF</sub> as indicated in [14]. R<sub>ON</sub> and R<sub>OFF</sub> have been in average lower than 50k $\Omega$  and larger than 50M $\Omega$ .

#### IV. EXPERIMENTAL VERIFICATION OF THE IMPLY AND NAND GATES

# A. Experimental setup

For all the measurements, a semiconductor parameter analyzer (SPA) Agilent 4156C has been used to applied the operation voltages and register the current through memristors. For every memristor involved in the logic gate, source measurement units (SMUs) has been connected (2 SMUs for IMPLY case and 3 for NAND case). Additionally, a voltage source unit (VMU) was connected to monitor the voltage  $V_G$ . For the initialization step, voltage ramps were separately applied to every memristor to switch memristors to '0' or '1' state according to the case. Then, to perform the operation step, constant voltages were simultaneously applied to the memristors involved in such a step. After several attempts, trying different voltages values, finally the chosen operation voltages have been  $V_{COND}$ = -2V and  $V_{IMPLY}$ = -4V, which are the ones that produce the better IMPLY gate performance in most of the analyzed gate cases. Eventually, the final states of memristors were measured applying a small voltage ramp up to -0.8V. x

#### B. IMPLY logic gate

For the IMPLY experimental measurements using the circuit shown in Fig. 3(a), one of the cases from 1 to 4 of the truth table (Fig. 3(c)) is selected. Memristors P and Q are initialized to those states corresponding to the selected case, that is '0' (memristor at HRS) or '1' (memristor at LRS). Operation voltages ( $V_P$  and  $V_Q$ ) are applied to change the initial Q state (for case 1) or to keep it for the rest of the cases. Operational voltages applied to memristors do not depend on the considered case. For our devices, the voltage applied to P is  $V_P=V_{COND}=-2V$  and  $V_Q=V_{IMPLY}=-4V$  to Q. Currents through P and Q and the voltage,  $V_G$ , are now measured to verify the memristors states, both before and after the voltage application.

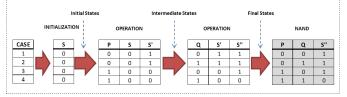

Fig. 4 shows states of the memristors for the four IMPLY cases (from top to bottom, case 1 to case 4). The states of P and Q before (initial states) and after (final states) operation are shown expressed in terms of the current flowing through the devices (equivalent to the devices' resistances). We can observe that the truth table is accomplished correctly.

# C. NAND logic gate

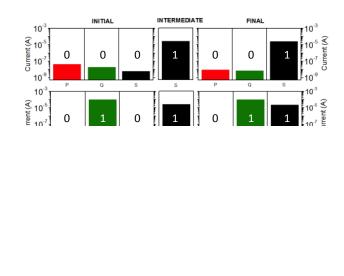

A NAND gate has also been verified using the circuit shown in Fig. 3(b). Similarly, as for the IMPLY gate, after the initial forming cycles of each memristor, a particular case of the NAND truth table is selected. Then, the three memristors are initialized to the corresponding states (Fig. 3(d)). In this case, the procedure consists of two different sequential steps (**Error! Reference source not found.**). In the first step, an IMPLY operation between memristors P and S is performed, whose operation voltages are  $V_P=V_{COND}=-2V$  and  $V_S=V_{IMPLY}=-4V$ . Once the required S state is reached (S'), subsequently, a second IMPLY operation, between Q and S (at S' state) takes

Fig. 7. NAND implementation, with continuous sequence of operation with two IMPLY operation steps. Intermediate state of memristor S is

included showing that the first operation step was performed correctly.

CASE 2:

# CASE 4:

Fig. 4. Initial and final states of memristors P and Q involved in the IMPLY Logic Gate. Q final state corresponds to the output of the gate.

Fig. 5. Schematic sequence flow for NAND measurements involving two IMPLY operation steps.

place applying  $V_Q=V_{COND}=-2V$  and  $V_S=V_{IMPLY}=-4V$ . This final state of S (S'') is established as the output of NAND gate.

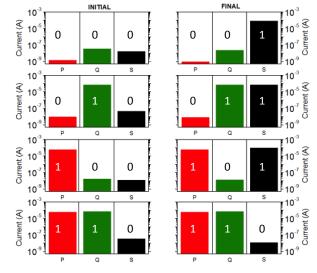

Fig. 6 shows the experimental four NAND cases successfully performed (from top to bottom cases 1-4). Initial and final states are depicted for each memristor. An additional S state (intermediate state, after the first operation step) is included to confirm that the first IMPLY operation between memristors P and S has been successful.

Besides the single NAND cases measurements, successive measurements of the four NAND cases have also been performed. After each operation, a new case is chosen randomly and later the experimental procedure above mentioned to analyze

the NAND gate is followed. states (initial and final) for each of the four NAND cases bottom). As in Fig. 6 included to corroborate that successfully. In this experiment the effect of the the devices is observed, fluctuation of the current, but logic operation in all the cycles current at '0' and '1' region (current values above respectively), the successive percentage of success of has been demonstrated.

So far, IMPLY and NAND experimentally demonstrated as memristors, by using the next section, the NAND improved, using only one

Fig. 6. NAND implementation with two IMPLY operation steps. The first one is between memristors P and S with the output state stored in the S. The second IMPLY operation is between Q and S, being the initial state of S the output of the previous IMPLY operation. After the first operation step, state of S is included to verify that the first IMPLY operation is well-performed. Fig. 7 shows memristors several successful cycles for (case 1-case 4 from top to intermediate S state is the first operation step occurs continuous logic evaluation cycle-to-cycle variability of showing а stochastic keeping the validity of the cases. Although in some states overpass the forbidden and below 0.1µA and 10µA performance (with а around 80%) of such a gate

logic gates have been using High-k MIS structures standard procedures [25]. In gate performance is operation step instead of two.

# V. A NEW NAND OPERATION

This new NAND operation proposes a procedure with only one operation step where the three memristors (P, Q and S) are simultaneously biased. Unlike previous procedures, an additional voltage,  $V_{COND2}$ , has been applied.

#### A. Theoretical circuit analysis

First, a circuit analysis taking into account the three memristors has been done. Considering the memristors of the circuit shown in Fig. 3(b) behave as three resistances ( $R_P$ ,  $R_Q$ , and  $R_S$ ) and applying Kirchhoff's current law at  $V_G$  node, the voltage at node G is:

$$V_{G} = \frac{R_{G}R_{Q}R_{S}V_{P} + R_{G}R_{P}R_{S}V_{Q} + R_{G}R_{P}R_{Q}V_{S}}{R_{P}R_{Q}(R_{S} + R_{G}) + R_{G}R_{Q}(R_{S} + R_{P})}$$

(1)

$V_G$  takes different values depending on the particular NAND case, since initial memristor states differ from one case to another. Remember that when the initial state of the memristor is '0', the memristor resistance is high ( $R_{OFF}$ ). On the other hand, if the memristor state is '1', then the memristor resistance is low ( $R_{ON}$ ). The value of  $R_G$  should be  $R_{ON} < R_G < R_{OFF}$  with at least one order of magnitude difference between  $R_{ON}$  and  $R_G$  and between  $R_G$  and  $R_{OFF}$ . For each NAND case, we will evaluate the relation between  $V_P$ ,  $V_Q$  and  $V_S$  that must be fulfilled to get the suitable  $V_G$  value that implements each NAND case in only one operation step.

In the case 1 of the NAND truth table (Fig. 3(d)), initial resistance value of memristors P, Q and S should be  $R_{OFF}$  ('0' logic state) and, at the end, S resistance should change to  $R_{ON}$ . Voltage drop in P, Q and S can be calculated as  $V_X$ - $V_G$  (being  $V_X$  the voltage at the top electrode of each memristor). Then, if operational voltages applied to P and Q were  $V_{COND1}$  while for S was  $V_{IMPLY}$ , with  $V_{IMPLY}$ > $V_{COND1}$ , (2) would be obtained (substituting these values in (1) and simplifying). Considering the resistance relation described in the last paragraph,  $V_G$  would be negligible.

$$V_G = \frac{R_G V_{imply} + 2R_G V_{cond1}}{R_{off} + 3R_G} \approx 0$$

(2)

Then, since  $V_G \approx 0$ , voltage drops across P and Q would be approximately  $V_{COND1}$ , and across S almost  $V_{IMPLY}$ . This would provoke the S resistance change from  $R_{OFF}$  ('0') to  $R_{ON}$  ('1'), while P and Q remain the same state ('0') with resistance  $R_{OFF}$ .

In case 2, resistances of memristors P, Q and S should be  $R_{OFF}$ ,  $R_{ON}$  and  $R_{OFF}$  respectively and, as before, S resistance should change to  $R_{ON}$ . If P and Q were biased at  $V_{COND2}$  and S with  $V_{IMPLY}$ ;  $V_G$  would be given by (3). Taking into account the memristor resistance values,  $V_G$  would be negligible again. The voltage drops through P, Q and S would be  $V_{COND2}$ ,  $V_{COND2}$  and  $V_{IMPLY}$  respectively (with  $V_{IMPLY} > V_{COND2}$ ) provoking the change of the S resistance from  $R_{OFF}$  to  $R_{ON}$  and modifying the stored logic state from '0' to '1'. As expected, P and Q would remain in the same initial state.

$$V_G = \frac{R_G R_{on} V_{imply} + (R_G R_{on} + R_G R_{off}) V_{cond2}}{(R_{off} + 2R_G) R_{on} + R_G R_{off}} \approx 0$$

(3)

Similarly occurs in case 3. Since P and Q are supposed to be interchangeable and initial states are  $R_P=R_{ON}$ ,  $R_Q=R_{OFF}$  and  $R_S=R_{OFF}$ ,  $V_G$  follows the same equation, (3). Therefore, voltage drops across memristors, considering  $V_P=V_Q=V_{COND2}$  and  $V_S=V_{IMPLY}$ , would be the same as in case 2 giving the correct final memristors states.

Finally, in case 4, initial states of memristors P, Q and S are equal to  $R_{ON}$ ,  $R_{ON}$  and  $R_{OFF}$ , respectively and S resistance should not change. If voltages applied to P and Q were  $V_{COND1}$  and  $V_S=V_{IMPLY}$ ,  $V_G$  would be given by the expression in (4).

$$V_G = \frac{R_G R_{on} V_{imply} + 2R_G R_{off} V_{cond1}}{\left(R_{off} + R_G\right) R_{on} + 2R_G R_{off}} \approx V_{cond1}$$

(4)

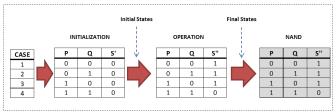

In this case, voltage drops at the memristors differ from the rest of cases. In both P and Q the voltage drop would be zero, while for S the voltage drop would be  $V_{IMPLY}$ - $V_{CONDI}$ <V<sub>IMPLY</sub>. Thus, all memristors would maintain its initial state value. Therefore, NAND truth table (Fig. 3(d)) implementation in a single step is theoretically demonstrated.

# B. Experimental verification

As in section IV, the SPA has been used to apply the operation voltages and register the current through the memristors in order to initialize the memristors and perform the operation step. After individually performing each case of NAND gate function under different applied voltages, finally, it has been found that the values that allow successful functionality of the NAND are again $V_{\text{COND1}} = -2V$ ,  $V_{\text{COND2}} = 0V$  and  $V_{\text{IMPLY}} = -4V$ . For the measurement of final states of memristor a voltage ramp up to -0.8V has been applied.

**Error!** Reference source not found. graphically shows the proposed sequence to perform the NAND gate in only one operation step. Firstly, all memristors are initialized (initial states). Later, the unique operation step takes place applying the adequate voltages to P, Q and S simultaneously according to the case. Finally, the memristors state is read to verify the correct gate behavior. The initialization and evaluation of memristors states is also done when the standard NAND procedure is used. However, the number of operation steps performed to provoke the NAND gate output is different: with the standard produce two operation steps are required (first an IMPLY operation between P and S memristors and, secondly, another IMPLY operation

between Q and S memristor). operation, only one operation memristor s are involved at the the two operation steps of the **Reference source not found.** these operation voltages, simultaneously and verify the provokes an S-output that truth table.

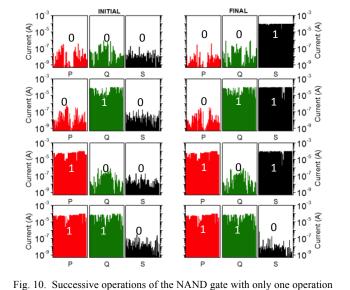

The experimental results procedure are presented in found. where initial and final for all NAND cases when two sequential steps appear because in this case, needed. These results based NAND operation is step. Successive operations randomly, on the same gate, NAND gate, with only one

measurement. As in two-step states are in the forbidden values of  $1\mu$ A). However, mostly above  $10\mu$ A, the one-step NAND has been that only the successful being the success percentage of the memristor dispersion is addressed in future works.

# VI. CONCLUSION

In this paper, memristorlogic gates have been using Ni/HfO<sub>2</sub>/Si Successive NAND operations been successfully also operation correctness even in cycle-to-cycle device new procedure to operate the proposed, which requires computing time when IMPLY-based requires two steps). This operational voltage for the the shown case this additional

# REFERENCES

- [1] L. O. Chua, Circuit Element," *IEEE* no. 5, pp. 507–519,

- [2] D. B. Strukov, G. S. Williams, "The missing 453, no. 7191, pp. 80–3,

- [3] H. Y. Y. Lee *et al.*, RESET problem for with sub-ns switching

TABLE I EXPERIMENTAL VOLTAGES APPLIED SIMULTANEOUSLY TO THE NAND CIRCUIT TO PROVOKE THE DIFFERENT CASES OF THE NAND OUTPUT IN ONLY ONE OPERATION STEP.

step. Cycle-to-cycle device variability is observed.

| CASE | $V_{P}(V)$ | V <sub>Q</sub> (V) | $V_{s}(V)$ |

|------|------------|--------------------|------------|

| 1    | -2         | -2                 | -4         |

| 2    | 0          | 0                  | -4         |

| 3    | 0          | 0                  | -4         |

| 4    | -2         | -2                 | -4         |

Fig. 9. Schematic flow sequence of one operation step procedure for NAND logic gate.

Fig. 8. NAND implementation with only one IMPLY operation step.

With this NAND new where the step. three same time, is done, instead of standard procedure. Error! shows the combination of which are applied required relationships. This corresponds to the NAND

obtained following previous Error! Reference source not memristor states are depicted Intermediate states (shown were required, Fig. 6) do not only one operation step is demonstrate that memristorpossible using uniquely one were also performed to obtain the different logic cases of the operation step.

cases in a successive operation NAND (Fig. 7) several '0' region (current reaching since current values at '1' are successive performance of also performed. Also mention cycles have been included around 80%. The reduction one of the next tasks to be

based IMPLY and NAND experimentally demonstrated manufactured devices. (for all four input cases) have showing performed, the the presence of the inherent fluctuations. Additionally, a NAND gate has been only one step, reducing the compared previous to implementations (that technique requires a third NAND structure, though in voltage is GND.

"Memristor—The Missing *Trans. Circuit Theory*, vol. 18, 1971.

Snider, D. R. Stewart, and R. S. memristor found.," *Nature*, vol. 2008.

"Evidence and solution of over-HfOX based resistive memory speed and high endurance," in

IEEE International Electron Devices Meeting (IEDM), 2010, p. 19.7.1-19.7.4.

- [4] C. H. Cheng, C. Y. Tsai, A. Chin, and F. S. Yeh, "High performance ultra-low energy RRAM with good retention and endurance," in 2010 International Electron Devices Meeting, 2010, p. 19.4.1-19.4.4.

- [5] A. C. Torrezan, J. P. Strachan, G. Medeiros-Ribeiro, and R. S. Williams, "Sub-nanosecond switching of a tantalum oxide memristor.," *Nanotechnology*, vol. 22, no. 48, p. 485203, Dec. 2011.

- [6] F. Nardi *et al.*, "Control of filament size and reduction of reset current below 10μA in NiO resistance switching memories," *Solid. State. Electron.*, vol. 58, no. 1, pp. 42–47, Apr. 2011.

- [7] A. C. Torrezan, J. P. Strachan, G. Medeiros-Ribeiro, and R. S. Williams, "Sub-nanosecond switching of a tantalum oxide memristor.," *Nanotechnology*, vol. 22, no. 48, p. 485203, Dec. 2011.

- [8] B. Govoreanu *et al.*, "10×10nm2 Hf/HfOx crossbar resistive RAM with excellent performance, reliability and low-energy operation," in *International Electron Devices Meeting (IEDM)*, 2011, p. 31.6.1-31.6.4.

- [9] Y. Y. Chen *et al.*, "Balancing SET/RESET Pulse for >10<sup>10</sup> Endurance in HfO<sub>2</sub>/Hf 1T1R Bipolar RRAM," *IEEE Trans. Electron Devices*, vol. 59, no. 12, pp. 3243–3249, Dec. 2012.

- [10] H.-S. P. Wong et al., "Metal-Oxide RRAM," Proc. IEEE, vol. 100, no. 6, pp. 1951–1970, Jun. 2012.

- [11] B. J. Choi *et al.*, "Electrical performance and scalability of Pt dispersed SiO<sub>2</sub> nanometallic resistance switch.," *Nano Lett.*, vol. 13, no. 7, pp. 3213–7, Jul. 2013.

- [12] M. Prezioso, F. Merrikh-Bayat, B. D. Hoskins, G. C. Adam, K. K. Likharev, and D. B. Strukov, "Training and operation of an integrated neuromorphic network based on metal-oxide memristors," *Nature*, vol. 521, no. 7550, pp. 61–64, 2015.

- [13] M. Chu et al., "Neuromorphic Hardware System for Visual Pattern Recognition with Memristor Array and CMOS Neuron," IEEE Trans. Ind. Electron., vol. 62, no. 4, pp. 2410–2419, 2015.

- [14] J. Borghetti, G. S. Snider, P. J. Kuekes, J. J. Yang, D. R. Stewart, and R. S. Williams, "Memristive' switches enable 'stateful' logic operations via material implication.," *Nature*, vol. 464, no. 7290, pp. 873–876, 2010.

- [15] M. Teimoory, A. Amirsoleimani, J. Shamsi, A. Ahmadi, S. Alirezaee, and M. Ahmadi, "Optimized implementation of memristorbased full adder by material implication logic," in *21st IEEE International Conference on Electronics, Circuits and Systems (ICECS)*, 2014, pp. 562–565.

- [16] S. Balatti, S. Ambrogio, and D. Ielmini, "Normally-off Logic Based on Resistive Switches Part I: Logic Gates," *IEEE Trans. Electron Devices*, vol. 62, no. 6, pp. 1831–1838, 2015.

- [17] G. S. Rose, J. Rajendran, H. Manem, R. Karri, and R. E. Pino, "Leveraging Memristive Systems in the Construction of Digital Logic Circuits," *Proc. IEEE*, vol. 100, no. 6, pp. 2033–2049, Jun. 2012.

- [18] L. Xie, H. A. Du Nguyen, M. Taouil, and K. Bertels Said Hamdioui, "Fast boolean logic mapped on memristor crossbar," in 2015 33rd IEEE International Conference on Computer Design (ICCD), 2015, pp. 335–342.

- [19] G. Snider, "Computing with hysteretic resistor crossbars," *Appl. Phys. A*, vol. 80, no. 6, pp. 1165–1172, Mar. 2005.

- [20] S. Li, C. Xu, Q. Zou, J. Zhao, Y. Lu, and Y. Xie, "Pinatubo: A processing-in-memory architecture for bulk bitwise opeartions in emerging non-volatile memories," in *Proceedings of the 53rd Annual Design Automation Conference on - DAC '16*, 2016, pp. 1–6.

- [21] S. Hamdioui *et al.*, "Memristor for computing: Myth or reality?," in *Design, Automation & Test in Europe Conference & Exhibition* (*DATE*), 2017, 2017, pp. 722–731.

- [22] E. Linn, R. Rosezin, S. Tappertzhofen, U. Böttger, and R. Waser, "Beyond von Neumann—logic operations in passive crossbar arrays alongside memory operations," *Nanotechnology*, vol. 23, no. 30, p. 305205, Aug. 2012.

- [23] K. Bickerstaff and E. E. Swartzlander, "Memristor-based arithmetic," in *Conference Record of the Forty Fourth Asilomar Conference on Signals, Systems and Computers*, 2010, pp. 1173–1177.

- [24] D. Mahajan, M. Musaddiq, and E. E. Swartzlander, "Memristor based adders," in *48th Asilomar Conference on Signals, Systems and Computers*, 2014, pp. 1256–1260.

- [25] S. Kvatinsky, G. Satat, N. Wald, E. G. Friedman, A. Kolodny, and U. C. Weiser, "Memristor-Based Material Implication (IMPLY) Logic: Design Principles and Methodologies," *IEEE Trans. Very Large Scale Integr. Syst.*, vol. 22, no. 10, pp. 2054–2066, Oct. 2014.

- [26] F. Zhou, L. Guckert, Y.-F. Chang, E. E. Swartzlander, and J. Lee, "Bidirectional voltage biased implication operations using SiO<sub>x</sub> based unipolar memristors," *Appl. Phys. Lett.*, vol. 107, no. 18, p. 183501, 2015.

- [27] F. Pan, S. Gao, C. Chen, C. Song, and F. Zeng, "Recent progress in resistive random access memories: Materials, switching mechanisms, and performance," *Mater. Sci. Eng. R Reports*, vol. 83, pp. 1–59, Sep. 2014.

- [28] X. Wu *et al.*, "Intrinsic nanofilamentation in resistive switching," J. Appl. Phys., vol. 113, no. 11, p. 114503, Mar. 2013.

- [29] M. B. Gonzalez, J. M. Rafi, O. Beldarrain, M. Zabala, and F. Campabadal, "Analysis of the Switching Variability in Ni/HfO2-based RRAM Devices," *IEEE Trans. Device Mater. Reliab.*, vol. 14, pp. 1–1, 2014.

- [30] M. B. Gonzalez, M. C. Acero, O. Beldarrain, M. Zabala, and F. Campabadal, "Investigation of the resistive switching behavior in Ni/HfO2-based RRAM devices," in 10th Spanish Conference on Electron Devices (CDE), 2015, vol. 14, no. 2, pp. 1–3.

- [31] A. Rodriguez, M. B. Gonzalez, E. Miranda, F. Campabadal, and J. Suñe, "Temperature and polarity dependence of the switching behavior of Ni/HfO<sub>2</sub>-based RRAM devices," *Microelectron. Eng.*, vol. 147, pp. 75–78, 2015.

[32] M. Maestro *et al.*, "Analysis of Set and Reset mechanisms in Ni/HfO<sub>2</sub>-based RRAM with fast ramped voltages," *Microelectron. Eng.*, vol. 147, pp. 176–179, Nov. 2015.