# Design of broadband inductor-less RF front-ends with high dynamic range for G.hn

Xavier Trulls Fortuny Department of Electronic Engineering Technical University of Catalonia

> Thesis' advisors: Diego Mateo Peña Adrià Bofill Petit

A thesis submitted for the degree of *PhilosophiæDoctor (PhD)*

year month

### Act of qualification of the Doctoral Thesis

Gathered the tribunal consisting of the undersigned to mark the doctoral thesis:

| Thesis' title:  | Design of broadband inductor-less RF front-ends with high dynamic range for G.hn |

|-----------------|----------------------------------------------------------------------------------|

| Thesis' author: | Xavier Trulls Fortuny                                                            |

The tribunal agrees to mark with the qualification of:

| $\Box$ Unacceptable         |                    |

|-----------------------------|--------------------|

| $\Box$ Satisfactory         |                    |

| $\Box$ Very good            |                    |

| $\Box$ Excellent            |                    |

| $\Box$ Excellent, Cum Laude |                    |

| Barcelona,                  |                    |

| The president               | The secretary      |

| (name and surname)          | (name and surname) |

| Member                      |                    |

|                             |                    |

|                             |                    |

|                             |                    |

(name and surname)

# Design of broadband inductor-less RF front-ends with high dynamic range for G.hn

Xavier Trulls Fortuny

Thesis' supervisors Diego Mateo Peña Adrià Bofill Petit

Full report of Xavier Trulls Fortuny's PhD thesis to apply for the title of PhilosophiæDoctor (PhD)

2008-2012

PhD programme "Electronic Engineering" Electronic Engineering Department Technical University of Catalonia (UPC)

### Abstract

System-on-Chip (SoC) was adopted in recent years as one of the solutions to reduce the cost of integrated systems. When the SoC solution started to be used, the final product was actually more expensive due to lower yield. The developments in integrated technology through the years allowed the integration of more components in lesser area with a better yield. Thus, SoCs became a widely used solution to reduced the cost of the final product, integrating into a single-chip the main parts of a system: analog, digital and memory.

As integrated technology kept scaling down to allow a higher density of transistors and thus providing more functionality with the same die area, the analog RF parts of the SoC became a bottleneck to cost reduction as inductors occupy a large die area and do not scale down with technology. Hence, the trend moves toward the research and design of inductor-less SoCs that further reduce the cost of the final solution.

At the same time, as the demand for home networking high-data-rates communication systems has increased over the last decade, several standards have been developed to satisfy the requirements of each application, the most popular being wireless local area networks (WLANs) based on the IEEE 802.11 standard. However, poor signal propagation across walls make WLANs unsuitable for high-speed applications such as high-definition in-home video streaming, leading to the development of wired technologies using the existing in-home infrastructure. The ITU-T G.hn recommendation (G.9960 and G.9961) unifies the most widely used wired infrastructures at home (coaxial cables, phone lines and power lines) into a single standard for high-speed data transmission of up to 1 Gb/s. The G.hn recommendation defines a unified networking over power lines, phone lines and coaxial cables with different plans for baseband and RF. The RF-coax bandplan, where this thesis is focused, uses 50 MHz and 100 MHz bandwidth channels with 256 and 512 carriers respectively. The center frequency can range from 350 MHz to 2450 MHz. The recommendation specifies a transmission power limit of 5 dBm for the 50 MHz bandplan and 8 dBm for the 100 MHz bandplan, therefore the maximum transmitted power in each carrier is the same for both bandplans.

Due to the nature of an in-home wired environment, receivers that can handle both very large and very small amplitude signals are required: when transmitter and receiver are connected on the same electric outlet there is no channel attenuation and the signal-to-noise-plus-distortion ratio (SNDR) is dominated by the receiver linearity, whereas when transmitter and receiver are several rooms apart channel attenuation is high and the SNDR is dominated by the receiver noise figure. The high-dynamic-range specifications for these receivers require the use of configurable-gain topologies that can provide both high-linearity and low-noise for different configurations. Thus, this thesis has been aimed at researching high dynamic range broadband inductor-less topologies to be used as the RF front-end for a G.hn receiver complying with the provided specifications.

A large part of the thesis has been focused on the design of the input amplifier of the front-end, which is the most critical stage as the noise figure and linearity of the input amplifier define the achievable overall specifications of the whole front-end. Three prototypes has been manufactured and measured using a 65 nm CMOS process: two input RFPGAs and one front-end using the second RFPGA prototype.

Keywords: broadband, inductor-less, RF, front-end, high dynamic range, wired communications To my family,

for the continuous support over the years.

### Acknowledgements

I would like to thank *Broadcom Corporation* and *Gigle Networks* (prior to acquisition by the former) for the project offer, especially former *Gigle Networks* CTO Jed Hurwitz and Group Manager Keith Findlater for supporting my involvement in this project. I also want to thank the company staff that provided continuous support and valuable insight on how to improve the content, especially my thesis co-advisor Adrià Bofill and fellow co-workers Xavier Redondo and Tomeu Servera.

I thank the Technical University of Catalonia (UPC), the Electronic Engineering Department and especially my university co-advisor Diego Mateo for all the support over the duration of this thesis, as well as fellow university research comrades (in no particular order, Dídac Gómez, Marc Molina, Marc Pons and Enrique Barajas).

I acknowledge that the work presented in this thesis has been partly subsidized by the Spanish Ministry of Industry under the Avanza R&D plan with project number TSI-020100-2009-597.

I also thank *Agilent Technologies* and Lluis Pradell from the RF&MW research group at the Technical University of Catalonia for providing measuring equipment.

Finally, I would like to thank a plethora of friends, close friends and even closer friends who have walked beside me and helped me on this long journey, sharing a lot of unforgettable moments. Thanks to all the people who have shared those moments with me, because as one great literary mind once said, "[...] ist eine Reise unschtzbar; sie belebt, berichtigt, belehrt und bildet".

And, most importantly, to my family, who has always been there for me and deserve much more than a simple acknowledgement.

### Contents

| Li            | st of | Figures   xx                                               | /ii |

|---------------|-------|------------------------------------------------------------|-----|

| $\mathbf{Li}$ | st of | Tables x                                                   | xi  |

| G             | lossa | ry xx                                                      | iii |

| 1             | Intr  | oduction                                                   | 1   |

|               | 1.1   | Thesis Framework                                           | 1   |

|               | 1.2   | G.hn recommendation                                        | 1   |

|               | 1.3   | Towards low-cost broadband inductor-less SoCs              | 4   |

|               | 1.4   | Research Goals and Contributions                           | 4   |

|               | 1.5   | Thesis Organization                                        | 5   |

| <b>2</b>      | Rec   | eiver Front-End Fundamentals                               | 7   |

|               | 2.1   | Introduction                                               | 7   |

|               | 2.2   | Noise and Sensitivity                                      | 8   |

|               | 2.3   | Distortion                                                 | 9   |

|               | 2.4   | Dynamic Range                                              | 13  |

|               |       | 2.4.1 NPR Measurements                                     | 14  |

|               | 2.5   | Frequency Conversion                                       | 18  |

| 3             | Hig   | h-dynamic-range Broadband Inductor-Less RF Amplifier Tech- |     |

|               | niqu  | les                                                        | 21  |

|               | 3.1   | Introduction                                               | 21  |

|               | 3.2   | Input Impedance Matching                                   | 22  |

|               |       | 3.2.1 Parallel Resistance                                  | 22  |

|               |       | 3.2.2 Resistive Feedback                                   | 23  |

|   |                    | 3.2.3                                                                           | Common-Gate                                                                                                                                                                                                                                                                                                                                            | 25                                                       |

|---|--------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|   |                    | 3.2.4                                                                           | Active Feedback                                                                                                                                                                                                                                                                                                                                        | 29                                                       |

|   |                    | 3.2.5                                                                           | Implications on the prototype designs $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                      | 31                                                       |

|   | 3.3                | Induct                                                                          | cor-less Loads                                                                                                                                                                                                                                                                                                                                         | 33                                                       |

|   |                    | 3.3.1                                                                           | Resistive Loads                                                                                                                                                                                                                                                                                                                                        | 33                                                       |

|   |                    | 3.3.2                                                                           | Active Loads                                                                                                                                                                                                                                                                                                                                           | 33                                                       |

|   |                    | 3.3.3                                                                           | Active Inductors                                                                                                                                                                                                                                                                                                                                       | 34                                                       |

|   |                    | 3.3.4                                                                           | Capacitive Peaking                                                                                                                                                                                                                                                                                                                                     | 39                                                       |

|   |                    | 3.3.5                                                                           | Implications on the prototype designs                                                                                                                                                                                                                                                                                                                  | 40                                                       |

|   | 3.4                | High-l                                                                          | Linearity Techniques                                                                                                                                                                                                                                                                                                                                   | 41                                                       |

|   |                    | 3.4.1                                                                           | Derivative Superposition                                                                                                                                                                                                                                                                                                                               | 42                                                       |

|   |                    | 3.4.2                                                                           | Harmonic Termination                                                                                                                                                                                                                                                                                                                                   | 44                                                       |

|   |                    | 3.4.3                                                                           | Noise/Distortion Cancellation                                                                                                                                                                                                                                                                                                                          | 46                                                       |

|   |                    | 3.4.4                                                                           | Post-distortion                                                                                                                                                                                                                                                                                                                                        | 48                                                       |

|   |                    | 3.4.5                                                                           | Configurable-Gain Topologies                                                                                                                                                                                                                                                                                                                           | 50                                                       |

|   |                    |                                                                                 |                                                                                                                                                                                                                                                                                                                                                        |                                                          |

|   |                    | 3.4.6                                                                           | Implications on the prototype designs                                                                                                                                                                                                                                                                                                                  | 53                                                       |

| 4 | RFI                |                                                                                 |                                                                                                                                                                                                                                                                                                                                                        |                                                          |

| 4 | RFI                | PGA 1                                                                           | Implications on the prototype designs                                                                                                                                                                                                                                                                                                                  |                                                          |

| 4 |                    | PGA ]<br>ı                                                                      |                                                                                                                                                                                                                                                                                                                                                        | -                                                        |

| 4 | tion               | PGA 1<br>1<br>Introd                                                            | Prototype I: Single-Input Switchable Capacitive Attenua-                                                                                                                                                                                                                                                                                               | 57                                                       |

| 4 | <b>tion</b><br>4.1 | PGA 1<br>1<br>Introd                                                            | Prototype I: Single-Input Switchable Capacitive Attenua-                                                                                                                                                                                                                                                                                               | -<br><b>57</b><br>57                                     |

| 4 | <b>tion</b><br>4.1 | PGA 1<br>Introd                                                                 | Prototype I: Single-Input Switchable Capacitive Attenua-<br>uction                                                                                                                                                                                                                                                                                     | 57<br>58                                                 |

| 4 | <b>tion</b><br>4.1 | PGA 1<br>Introd<br>Design<br>4.2.1<br>4.2.2                                     | Prototype I: Single-Input Switchable Capacitive Attenua-         uction                                                                                                                                                                                                                                                                                | <b>57</b><br>57<br>58<br>58                              |

| 4 | <b>tion</b><br>4.1 | PGA 1<br>Introd<br>Design<br>4.2.1<br>4.2.2                                     | Prototype I: Single-Input Switchable Capacitive Attenua-         uction                                                                                                                                                                                                                                                                                | 57<br>57<br>58<br>58<br>60                               |

| 4 | <b>tion</b><br>4.1 | PGA 1<br>Introd<br>Design<br>4.2.1<br>4.2.2<br>4.2.3                            | Prototype I: Single-Input Switchable Capacitive Attenua-         uction                                                                                                                                                                                                                                                                                | <b>57</b><br>57<br>58<br>58<br>60<br>63                  |

| 4 | <b>tion</b><br>4.1 | PGA 1<br>Introd<br>Design<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                   | Prototype I: Single-Input Switchable Capacitive Attenua-<br>uction                                                                                                                                                                                                                                                                                     | 57<br>57<br>58<br>58<br>60<br>63<br>64                   |

| 4 | <b>tion</b><br>4.1 | PGA 1<br>Introd<br>Design<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5          | Prototype I: Single-Input Switchable Capacitive Attenua-<br>uction                                                                                                                                                                                                                                                                                     | 57<br>57<br>58<br>58<br>60<br>63<br>64<br>65             |

| 4 | <b>tion</b><br>4.1 | PGA 1<br>Introd<br>Design<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5          | Prototype I: Single-Input Switchable Capacitive Attenua-<br>uction                                                                                                                                                                                                                                                                                     | 57<br>57<br>58<br>58<br>60<br>63<br>64<br>65<br>67       |

| 4 | <b>tion</b><br>4.1 | PGA 1<br>Introd<br>Design<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6 | Prototype I: Single-Input Switchable Capacitive Attenua-         uction         n         Core Concept         Circuit Topology         Selectable Input Impedance Matching         Second Stage and By-Pass         Switchable Capacitive Attenuation Capacitor Sizing         Optimization of the Active Feedback Impedance Matching         4.2.6.1 | 57<br>57<br>58<br>58<br>60<br>63<br>64<br>65<br>67<br>69 |

| <b>5</b> | 5 RFPGA Prototype II: Double-Input Switchable Capacitive Attenua- |                                                                                                                                                              |

|----------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | tion                                                              | n 89                                                                                                                                                         |

|          | 5.1                                                               | Introduction                                                                                                                                                 |

|          | 5.2                                                               | Design                                                                                                                                                       |

|          |                                                                   | 5.2.1 Core Concept $\ldots \ldots 90$                                                  |

|          |                                                                   | 5.2.2 Circuit Topology $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots $                                                              |

|          |                                                                   | 5.2.3 Sizing of the Attenuation Steps                                                                                                                        |

|          |                                                                   | 5.2.3.1 Cascoded Common-Source Sizing                                                                                                                        |

|          |                                                                   | 5.2.3.2 Degenerated Common-Source Sizing                                                                                                                     |

|          |                                                                   | 5.2.3.3 Capacitive Ladder Sizing $\ldots \ldots 101$                                          |

|          |                                                                   | 5.2.4 Noise Comparison with the Multiple-Stage Topology 105                                                                                                  |

|          |                                                                   | 5.2.4.1 Noise at Highest-Gain Setting $\ldots \ldots \ldots \ldots \ldots \ldots 105$                                                                        |

|          |                                                                   | 5.2.4.2 Noise at Attenuation Settings $\dots \dots \dots$    |

|          | 5.3                                                               | Experimental Results                                                                                                                                         |

|          | 5.4                                                               | Summary                                                                                                                                                      |

| 6        | Fro                                                               | nt-End Prototype 119                                                                                                                                         |

|          | 6.1                                                               | Introduction                                                                                                                                                 |

|          | 6.2                                                               | Mixer Topology                                                                                                                                               |

|          | 6.3                                                               | Front-End Architecture                                                                                                                                       |

|          | 6.4                                                               | Circuit Design                                                                                                                                               |

|          |                                                                   | 6.4.1 Switching Stage $\ldots \ldots \ldots$ |

|          |                                                                   | 6.4.2 Current Re-Use Transconductance Amplifier                                                                                                              |

|          |                                                                   | 6.4.3 Buffers                                                                                                                                                |

|          | 6.5                                                               | Experimental Results                                                                                                                                         |

|          | 6.6                                                               | Summary                                                                                                                                                      |

| 7        | Cor                                                               | nclusions and Future Work 141                                                                                                                                |

|          | 7.1                                                               | Conclusions                                                                                                                                                  |

|          | 7.2                                                               | Future Work                                                                                                                                                  |

| -        | 0                                                                 | ences 147                                                                                                                                                    |

## List of Figures

| 1.1  | G.hn bandplans                                                                                                   | 2  |

|------|------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Actual versus ideal behavior of an amplifying device                                                             | 10 |

| 2.2  | Location of second-order and third-order non-linearities $\ldots$                                                | 11 |

| 2.3  | Third-order intercept point                                                                                      | 11 |

| 2.4  | SNDR calculation at large and small input signal power                                                           | 13 |

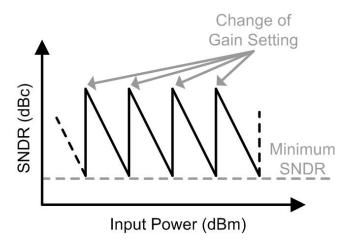

| 2.5  | SNDR vs input power with constant SNDR steps $\ldots \ldots \ldots \ldots \ldots$                                | 14 |

| 2.6  | NPR measurement process                                                                                          | 15 |

| 2.7  | Agilent Signal Studio for Noise Power Ratio configuration $\ldots \ldots \ldots$                                 | 16 |

| 2.8  | Sample screenshot of NPR input signal after applying pre-distortion                                              |    |

|      | zooming into the notch                                                                                           | 17 |

| 2.9  | Sample screenshot of a front-end output NPR measurement zooming into $% \mathcal{A} = \mathcal{A} = \mathcal{A}$ |    |

|      | the notch $\ldots$              | 17 |

| 2.10 | Common mixer implementation in CMOS $\ldots \ldots \ldots \ldots \ldots \ldots$                                  | 18 |

| 2.11 | SSB and DSB mixer concepts                                                                                       | 19 |

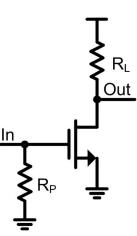

| 3.1  | Basic topology of the parallel resistance input impedance matching                                               | 23 |

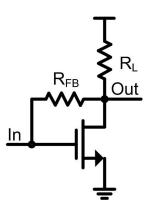

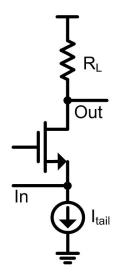

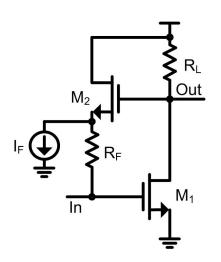

| 3.2  | Basic topology of the resistive feedback input impedance matching $\ . \ . \ .$                                  | 24 |

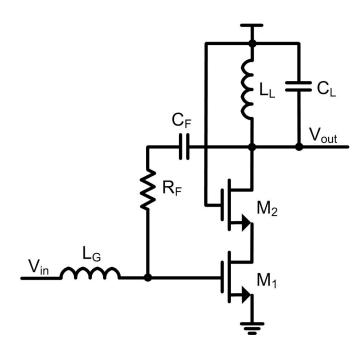

| 3.3  | Resistive feedback using input inductor                                                                          | 25 |

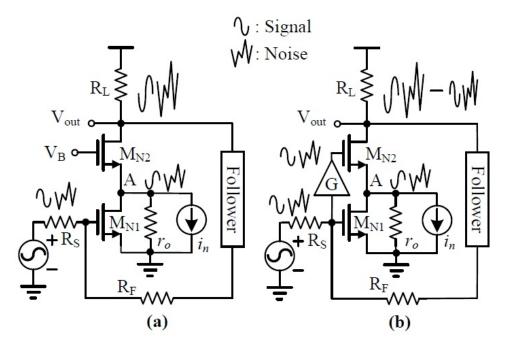

| 3.4  | Resistive feedback using feedforward noise and distortion cancellation $\ .$                                     | 26 |

| 3.5  | Basic topology of the common-gate input impedance matching $\ldots$ .                                            | 26 |

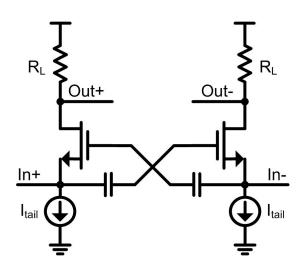

| 3.6  | Basic topology of the common-gate capacitive cross-coupling input impedan                                        | ce |

|      | matching                                                                                                         | 27 |

| 3.7  | Basic topology of the common-gate dual capacitive cross-coupling input                                           |    |

|      | impedance matching                                                                                               | 28 |

### LIST OF FIGURES

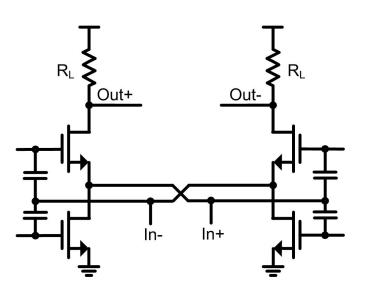

| 3.8  | Combined common-gate common-source topology providing simultane-                                                   |    |

|------|--------------------------------------------------------------------------------------------------------------------|----|

|      | ous input impedance matching, single-ended to differential conversion                                              |    |

|      | and noise-canceling                                                                                                | 29 |

| 3.9  | Basic topology of the active feedback input impedance matching $\ldots$ .                                          | 30 |

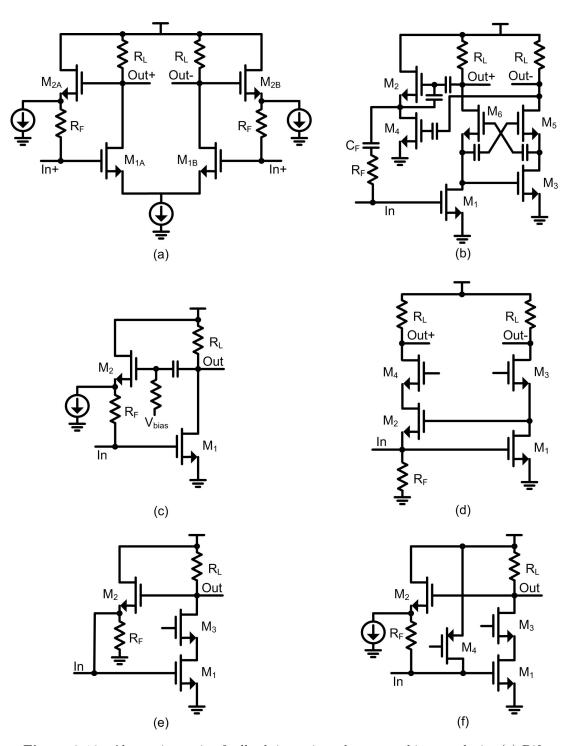

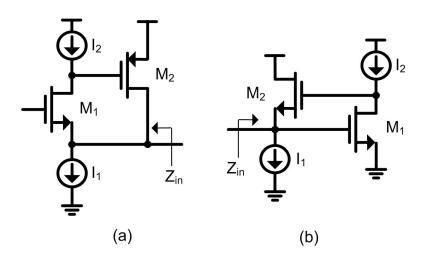

| 3.10 | Alternative active feedback input impedance matching topologies                                                    | 32 |

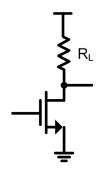

| 3.11 | Basic topology of an amplifier with resistive load $\ldots \ldots \ldots \ldots \ldots$                            | 34 |

| 3.12 | Basic topologies of a circuit with active loads $\ldots \ldots \ldots \ldots \ldots \ldots$                        | 35 |

| 3.13 | Basic topology of an active inductor                                                                               | 36 |

| 3.14 | Active inductor using the Wu topology                                                                              | 38 |

| 3.15 | Active inductors using the Lin-Payne and Hara topologies                                                           | 38 |

| 3.16 | Capacitive peaking topology                                                                                        | 40 |

| 3.17 | Derivative superposition structure                                                                                 | 42 |

| 3.18 | Third-order coefficients of the main $(g_{3B})$ and auxiliary $(g_{3A})$ transistors                               |    |

|      | in the derivative superposition method $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                   | 43 |

| 3.19 | Impedances affecting the behavior of the harmonic termination third-                                               |    |

|      | order cancellation technique $\ldots \ldots \ldots$ | 45 |

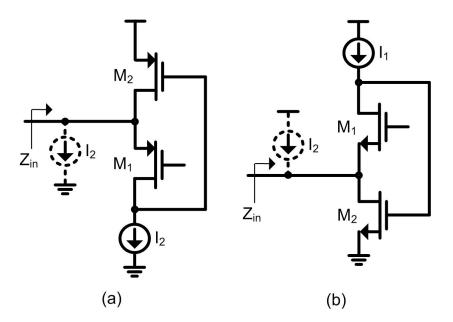

| 3.20 | Noise/distortion cancellation topologies $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                        | 46 |

| 3.21 | Signal phases in the noise/distortion cancellation topology                                                        | 47 |

| 3.22 | Basic topology of the post-distortion technique                                                                    | 49 |

| 3.23 | Alternative implementation of post-distortion                                                                      | 50 |

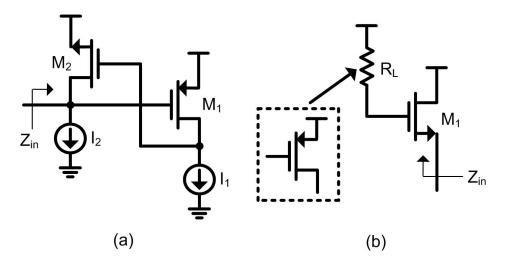

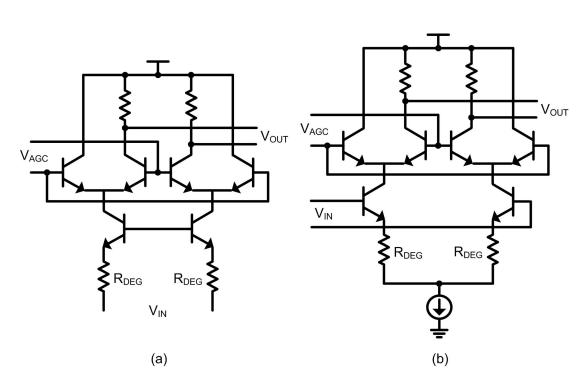

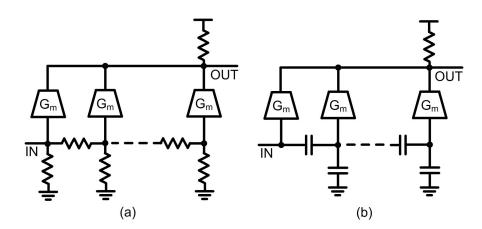

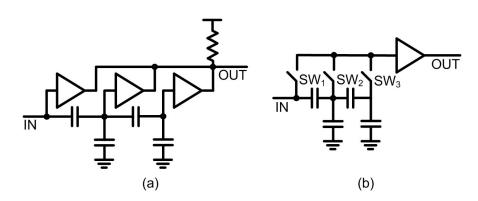

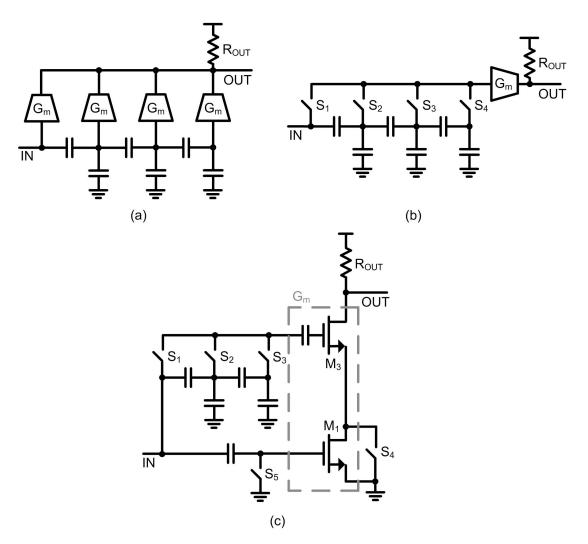

| 3.24 | Configurable-gain amplifier topologies                                                                             | 51 |

| 3.25 | Variable- $G_m$ amplifiers with current steering and degeneration $\ldots \ldots$                                  | 52 |

| 3.26 | Pre-attenuation based amplifier topologies                                                                         | 53 |

| 4.1  | Nonswitchable and switchable capacitive attenuation topologies                                                     | 59 |

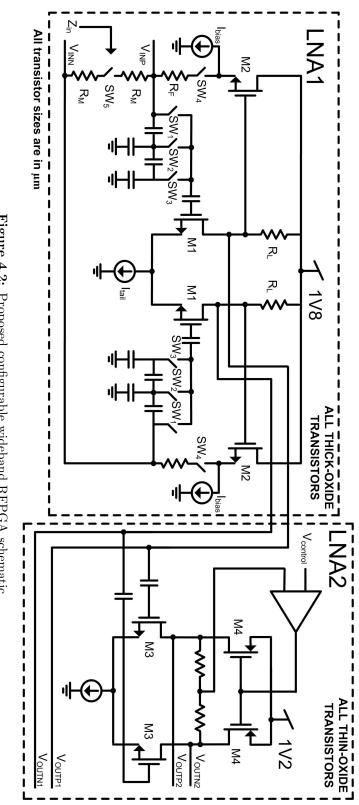

| 4.2  | Proposed configurable wideband RFPGA schematic                                                                     | 62 |

| 4.3  | Proposed configuration of RFPGA prototype I in a front-end implemen-                                               |    |

|      | tation                                                                                                             | 63 |

| 4.4  | Capacitor ladder using a C-2C structure                                                                            | 65 |

| 4.5  | Capacitor ladder including the parasitic capacitances of the switches                                              | 66 |

| 4.6  | Circuit model of the capacitor ladder including switch parasitic capaci-                                           |    |

|      | tances and channel resistance                                                                                      | 68 |

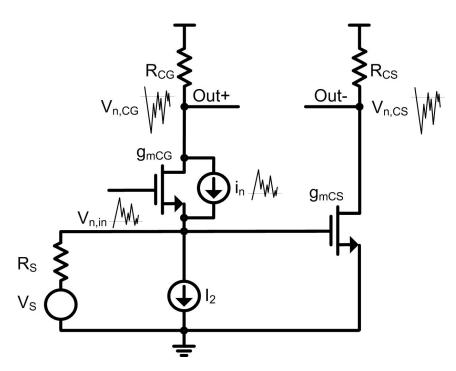

| 4.7  | LNA1 simplified schematic used for noise optimization calculations                                                 | 69 |

### LIST OF FIGURES

| 4.8  | Noise factor optimization through $R_F$ tuning $\ldots \ldots \ldots \ldots \ldots$             | 73  |

|------|-------------------------------------------------------------------------------------------------|-----|

| 4.9  | LNA1 simplified schematic used for input impedance optimization cal-                            |     |

|      | culations                                                                                       | 74  |

| 4.10 | Input structure of a front-end                                                                  | 76  |

| 4.11 | Active feedback input impedance matching behavior at high frequencies                           |     |

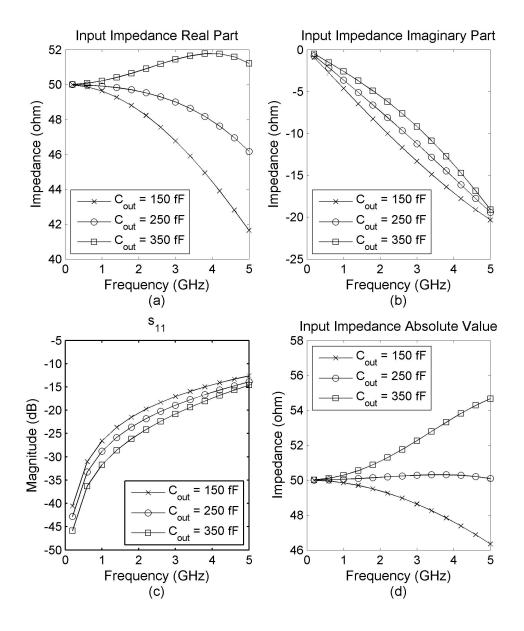

|      | for different values of $C_{out}$                                                               | 78  |

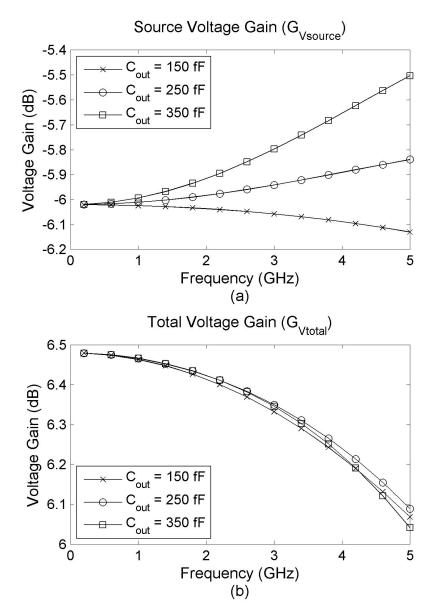

| 4.12 | Source voltage gain and total voltage gain (source plus amplifier) us-                          |     |

|      | ing the active feedback input impedance matching topology for different                         |     |

|      | values of output capacitance                                                                    | 80  |

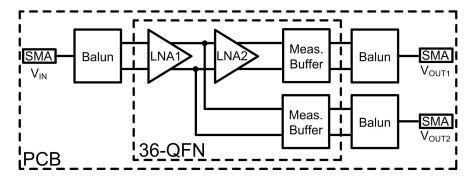

| 4.13 | PCB measurement setup                                                                           | 81  |

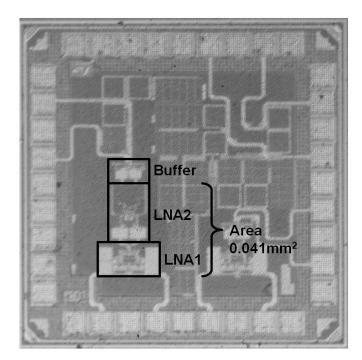

| 4.14 | Microphotograph of the RFPGA                                                                    | 81  |

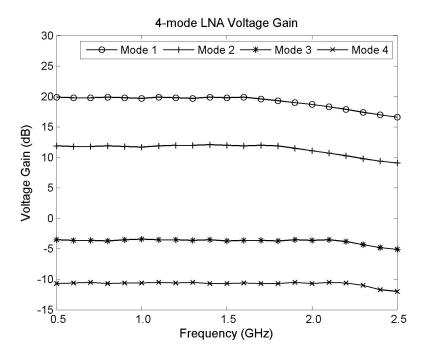

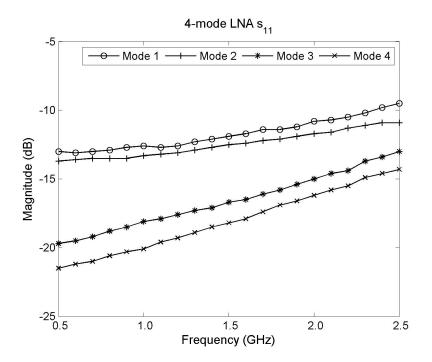

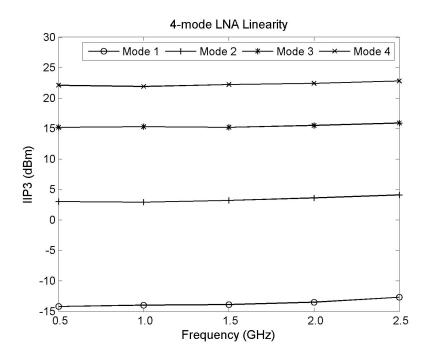

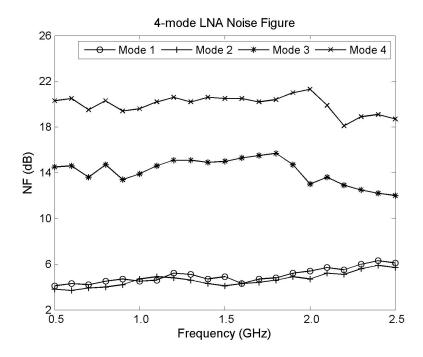

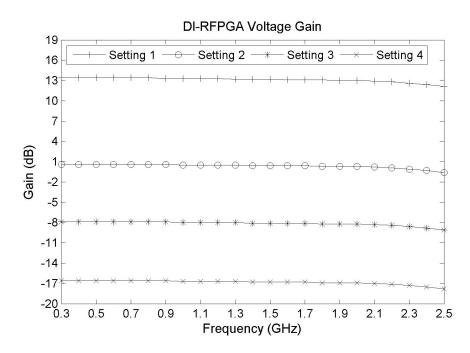

| 4.15 | Measured voltage gain of the RFPGA four settings                                                | 82  |

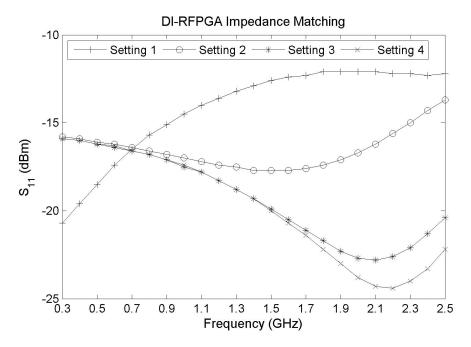

| 4.16 | Measured $s_{11}$ of the RFPGA four settings $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 83  |

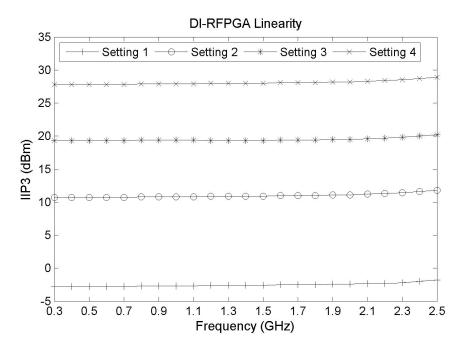

| 4.17 | Measured IIP3 of the RFPGA four settings                                                        | 83  |

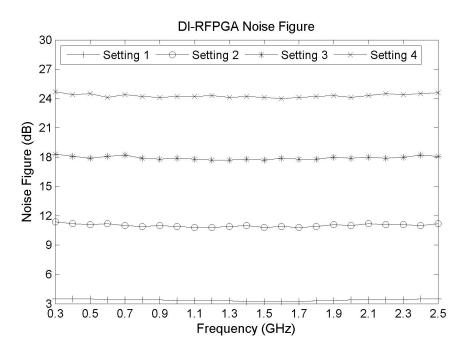

| 4.18 | Measured noise figure of the RFPGA four settings                                                | 84  |

|      |                                                                                                 |     |

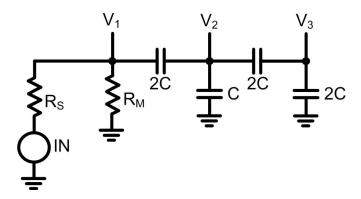

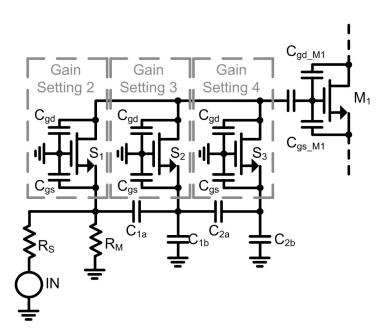

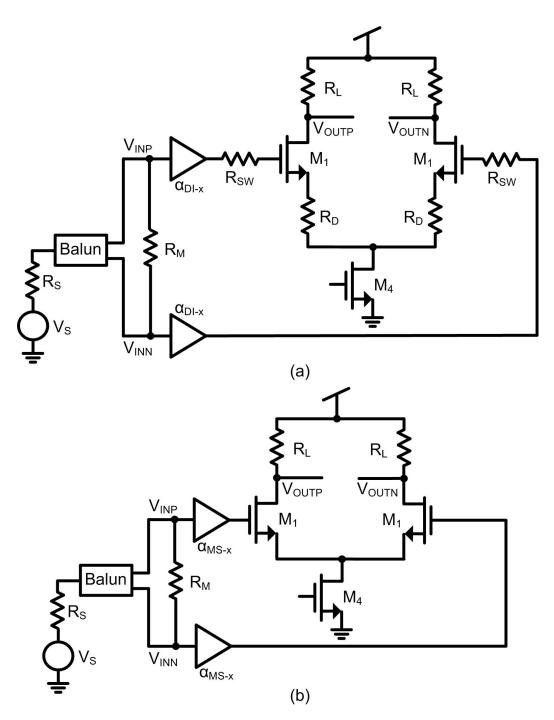

| 5.1  | Implementations of capacitive attenuation PGAs                                                  | 92  |

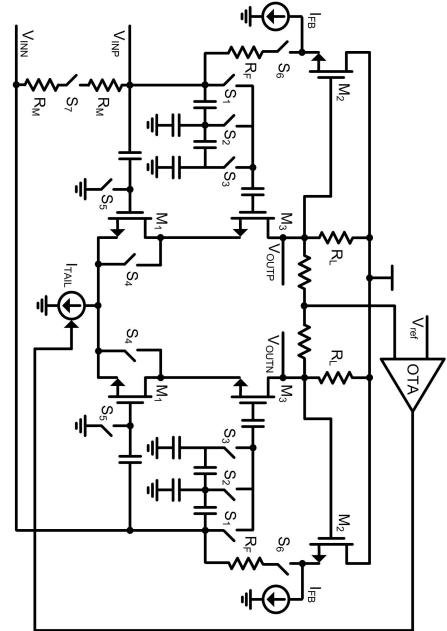

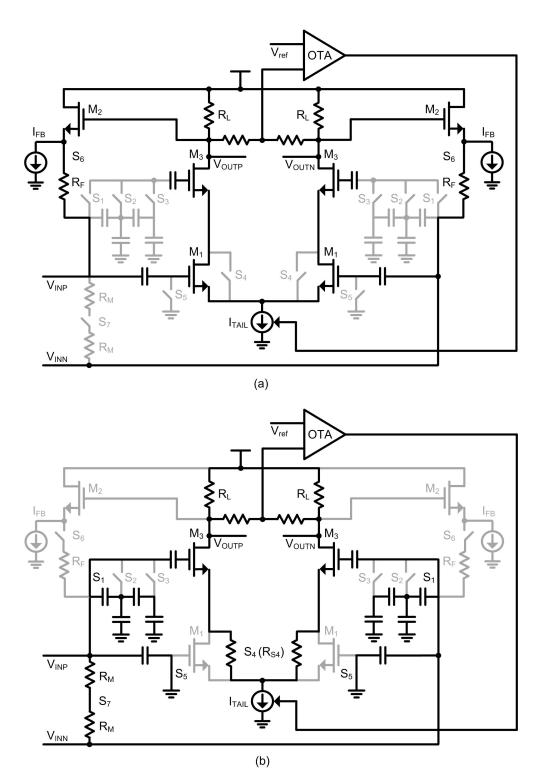

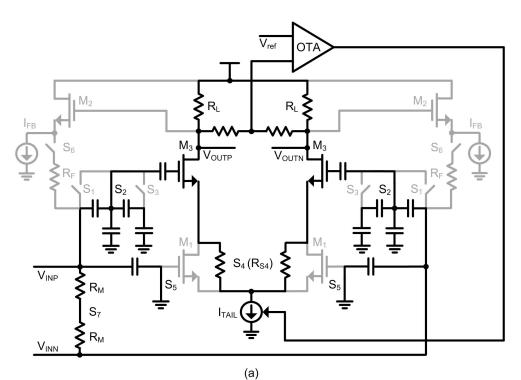

| 5.2  | Schematic of the differential double-input RFPGA with switchable ca-                            |     |

|      | pacitive attenuation                                                                            | 94  |

| 5.3  | Schematic of the differential double-input RFPGA with switchable ca-                            |     |

|      | pacitive attenuation: gain settings 1 and 2                                                     | 96  |

| 5.4  | Schematic of the differential double-input RFPGA with switchable ca-                            |     |

|      | pacitive attenuation: gain settings 3 and 4                                                     | 97  |

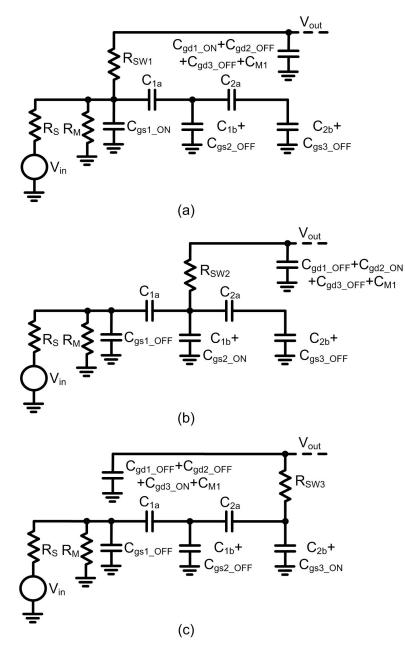

| 5.5  | Simplified schematics of the MS and DI topologies at different gain settings                    | 100 |

| 5.6  | Double-input switchable capacitive attenuation including switch para-                           |     |

|      | sitic capacitances                                                                              | 102 |

| 5.7  | DI-RFPGA simplified schematic used for noise calculations at the highest-                       |     |

|      | gain setting                                                                                    | 103 |

| 5.8  | Simplified schematic of the DI and MS topologies used for noise calcu-                          |     |

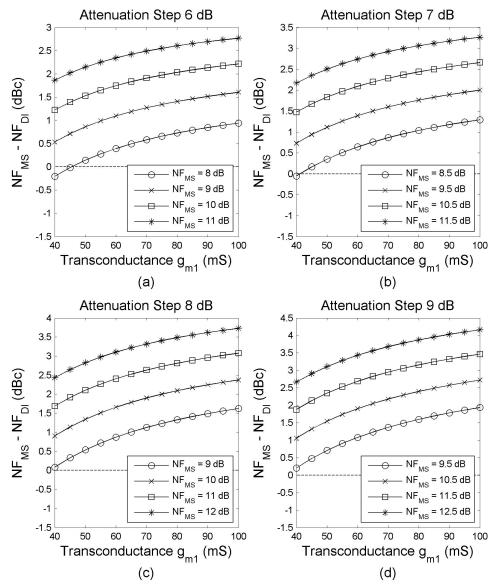

|      | lations at attenuation settings                                                                 | 107 |

| 5.9  | Noise figure difference between the MS and the DI topologies (Gain                              |     |

|      | Setting 2)                                                                                      | 111 |

### LIST OF FIGURES

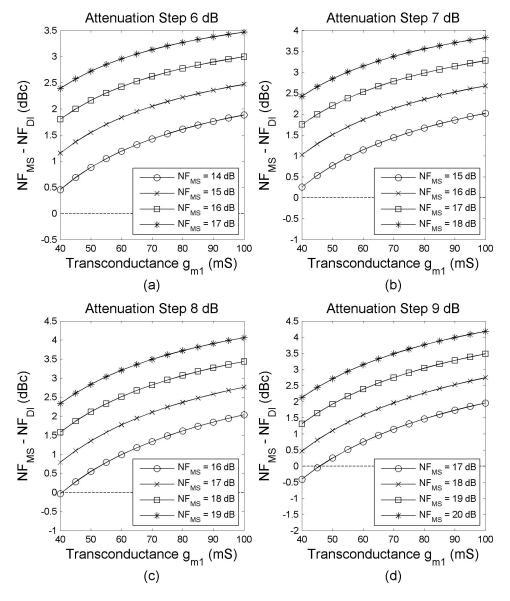

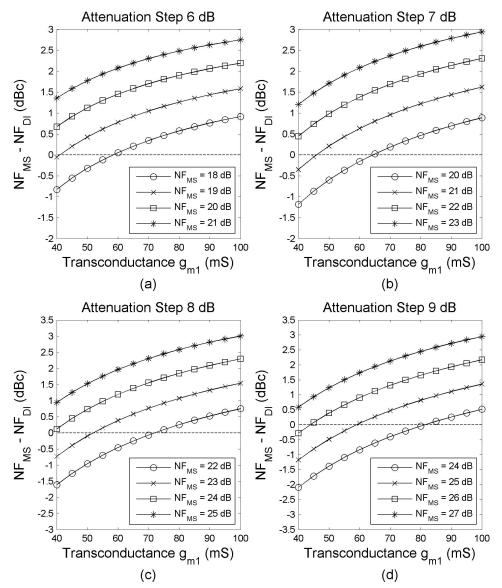

| 5.10 | Noise figure difference between the MS and the DI topologies (Gain            |

|------|-------------------------------------------------------------------------------|

|      | Setting 3)                                                                    |

| 5.11 | Noise figure difference between the MS and the DI topologies (Gain            |

|      | Setting 4)                                                                    |

| 5.12 | DI-RFPGA voltage gain measurement results                                     |

| 5.13 | DI-RFPGA $s_{11}$ measurement results                                         |

| 5.14 | DI-RFPGA IIP3 measurement results                                             |

| 5.15 | DI-RFPGA noise figure measurement results                                     |

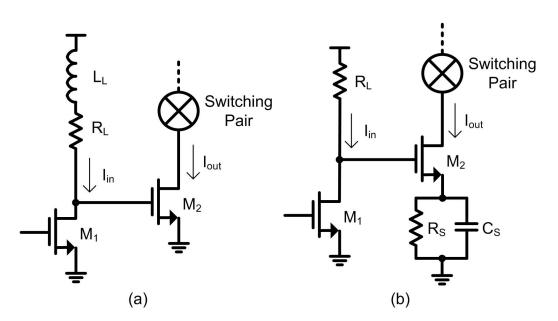

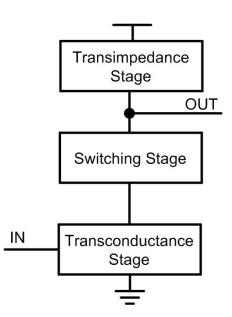

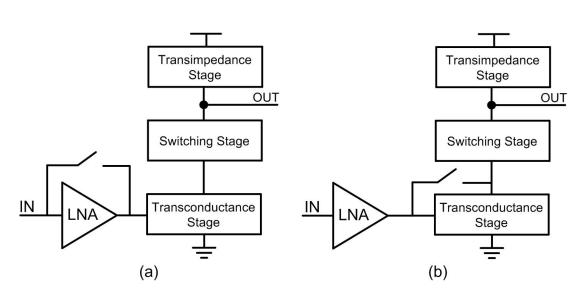

| 6.1  | Blocks in an active mixer                                                     |

| 6.2  | Front-end with by-passable LNA and front-end with by-passable mixer           |

|      | transconductance                                                              |

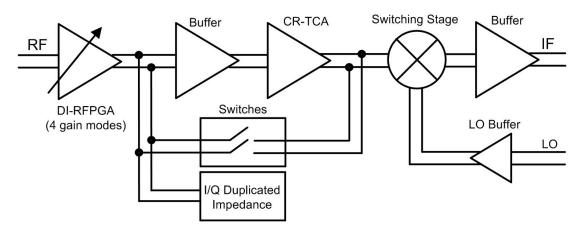

| 6.3  | Architecture of the implemented front-end                                     |

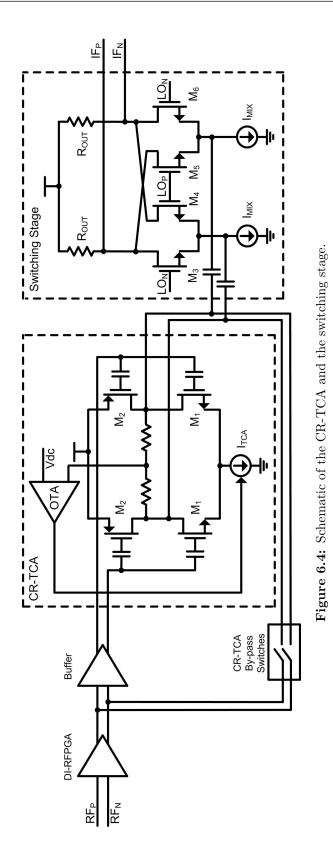

| 6.4  | Schematic of the CR-TCA and the switching stage 125                           |

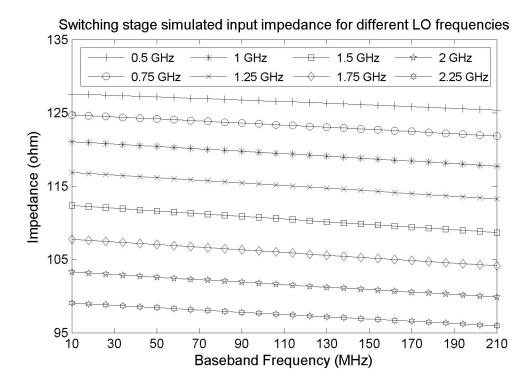

| 6.5  | Simulated input impedance of the switching stage for different LO fre-        |

|      | quencies                                                                      |

| 6.6  | SNDR vs input power with constant SNDR steps                                  |

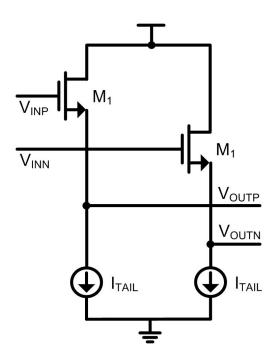

| 6.7  | Buffers schematic                                                             |

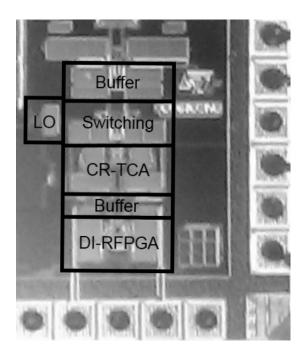

| 6.8  | Front-end prototype microphotograph                                           |

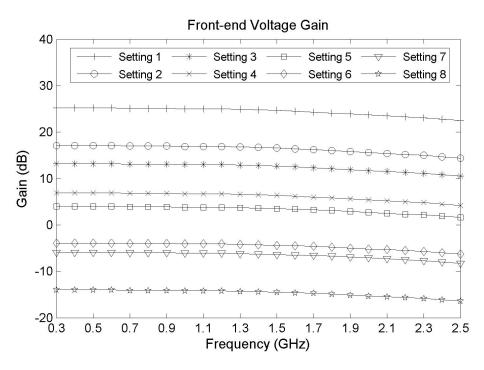

| 6.9  | Front-end voltage gain measurement results                                    |

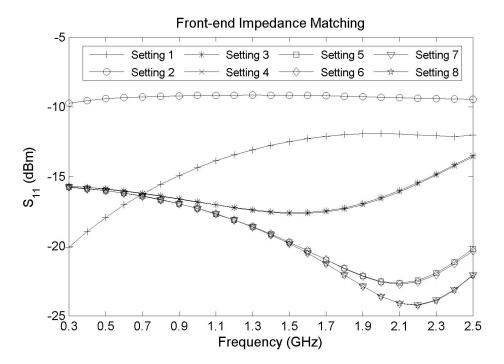

| 6.10 | Front-end $s_{11}$ measurement results                                        |

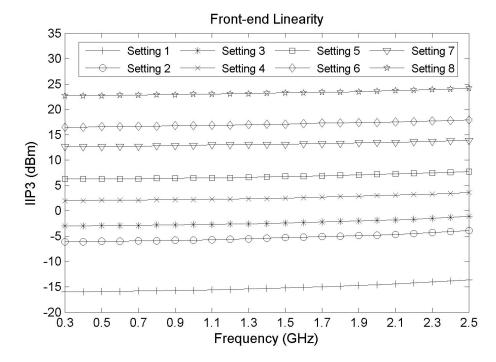

| 6.11 | Front-end IIP3 measurement results                                            |

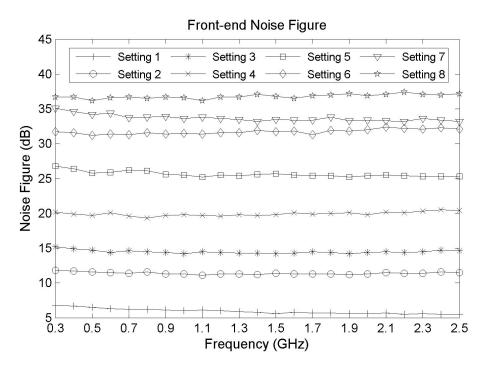

| 6.12 | Front-end noise figure measurement results                                    |

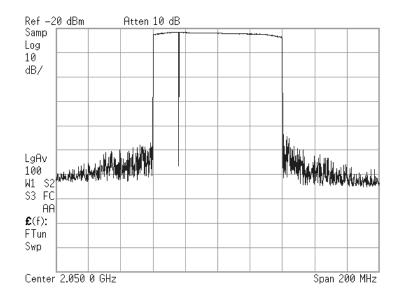

| 6.13 | Instance of the input signal in an NPR measurement (full channel view) 135    |

| 6.14 | Instance of the output signal in an NPR measurement (full channel view) $136$ |

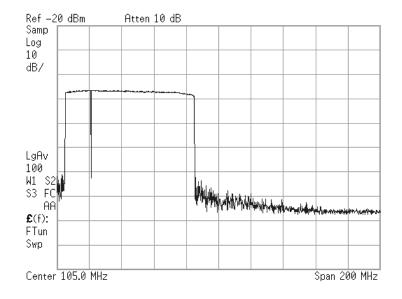

| 6.15 | Instance of the input signal in an NPR measurement (zoom into the             |

|      | carriers)                                                                     |

| 6.16 | Instance of the output signal in an NPR measurement (zoom into the            |

|      | carriers)                                                                     |

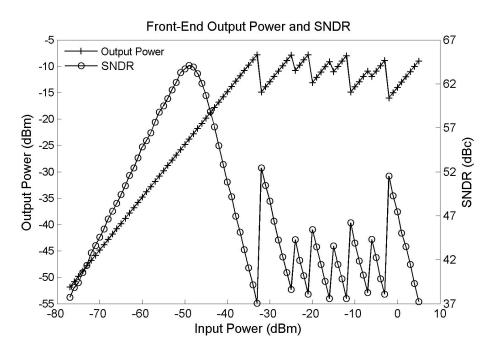

| 6.17 | SNDR and output power evolution versus input power                            |

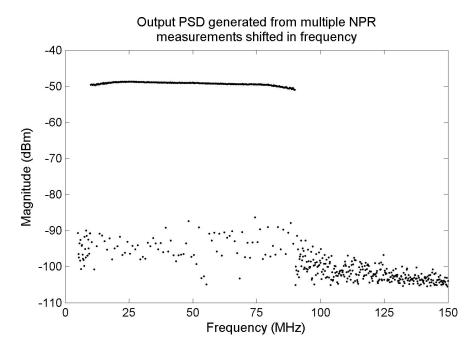

| 6.18 | Full channel output spectrum containing all the individual NPR notch          |

|      | measurements                                                                  |

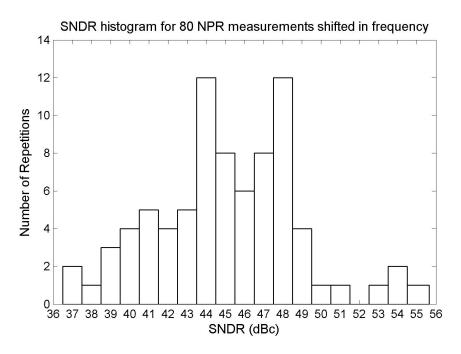

| 6.19 | Histogram of the NPR notch measurements                                       |

### List of Tables

| 1.1 | Physical medium and number of carriers used in each G.hn bandplan         | 2   |

|-----|---------------------------------------------------------------------------|-----|

| 1.2 | G.hn RF front-end specifications                                          | 5   |

| 3.1 | High-Linearity Techniques Performance Comparison                          | 55  |

| 4.1 | Noise factor dependencies of each component of LNA1 at highest gain       |     |

|     | setting                                                                   | 71  |

| 4.2 | RFPGA Prototype I experimental results                                    | 85  |

| 4.3 | RFPGA performance comparison                                              | 86  |

| 5.1 | Noise factor dependencies of each component of MS and DI topologies       |     |

|     | at highest gain setting                                                   | 104 |

| 5.2 | Noise factor dependencies of each component of MS and DI topologies       |     |

|     | at attenuation settings                                                   | 108 |

| 5.3 | Attenuation values for the different settings of the DI and MS topologies | 108 |

| 5.4 | RFPGA Prototype II experimental results                                   | 114 |

| 5.5 | DI-RFPGA performance comparison                                           | 118 |

| 6.1 | Simulated power consumption of each front-end stage                       | 124 |

| 6.2 | Order of the front-end gain settings                                      | 128 |

| 6.3 | Front-end Prototype experimental results                                  | 131 |

| 6.4 | G.hn RF front-end specifications                                          | 140 |

| 7.1 | G.hn RF front-end specifications                                          | 143 |

| 7.2 | Front-end Prototype experimental results                                  | 145 |

## Glossary

| ACPR          | Adjacent Channel Power Ratio           |

|---------------|----------------------------------------|

| ADC           | Analog-to-Digital Converter            |

| AGC           | Automatic Gain Control                 |

| BER           | Bit-Error Rate                         |

| CTB           | Composite Triple Beat                  |

| DI            | Double-Input                           |

| DSB           | Double-sideband                        |

| F             | Noise Factor                           |

| IF            | Intermediate Frequency                 |

| IIP3          | Third-Order Input Intercept Point      |

| IMD           | Intermodulation Distortion             |

| ITU           | International Telecommunications Union |

| LNA           | Low Noise Amplifier                    |

| LO            | Local Oscillator                       |

| $\mathbf{MS}$ | Multiple-Stage                         |

| NF            | Noise Figure                           |

| NPR           | Noise Power Ratio                      |

### GLOSSARY

| OIP3           | Third-Order Output Intercept Point     |

|----------------|----------------------------------------|

| ΟΤΑ            | Operational Transconductance Amplifier |

| PCB            | Printed Circuit Board                  |

| PGA            | Programmable Gain Amplifier            |

| $\mathbf{RF}$  | Radio-Frequency                        |

| SFDR           | Spurious Free Dynamic Range            |

| SNDR           | Signal to Noise plus Distortion Ratio  |

| $\mathbf{SNR}$ | Signal to Noise Ratio                  |

| $\mathbf{SoC}$ | System-on-a-Chip                       |

| $\mathbf{SSB}$ | Single-Sideband                        |

| VCO            | Voltage Controlled Oscillator          |

| VGA            | Variable Gain Amplifier                |

### 1

### Introduction

### 1.1 Thesis Framework

This thesis has been developed in the framework of industry through a joint fellowship provided by *Broadcom Corporation* (initially *Gigle Networks*, prior to its acquisition) and the *Technical University of Catalonia* (UPC). The research presented in this thesis has been developed based upon the requirements provided by the company and it is focused on the RF front-end part of a receiver for the ITU-T G.hn recommendation (G.9960 [1] and G.9961 [2]) which received final approval in 2010. The recommendation (the ITU's term for standard) defines networking over power lines, phone lines and coaxial cables with data rates up to 1 Gbit/s and contains a bandplan for RF over coaxial cable (RF-coax), where this thesis is focused.

The work presented in this thesis was partly subsidized by the Spanish Ministry of Industry under the Avanza R & D plan with project number TSI-020100-2009-597.

### 1.2 G.hn recommendation

As the demand for home networking high-data-rates communication systems has increased over the last decade, several standards have been developed to satisfy the requirements of each application, the most popular being wireless local area networks

#### 1. INTRODUCTION

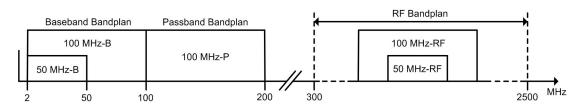

Figure 1.1: G.hn bandplans.

| Bandplan   | $\mathbf{Medium}$ | Number of carriers |

|------------|-------------------|--------------------|

| 50 MHz-B   | Powerline         | 2048               |

|            | Phoneline         | 1024               |

|            | Coax              | 256                |

| 100 MHz-B  | Powerline         | 4096               |

|            | Phoneline         | 2048               |

|            | Coax              | 512                |

| 100 MHz-P  | Powerline         | 1024               |

| 50 MHz-RF  | Coax              | 256                |

| 100 MHz-RF | Coax              | 512                |

|            |                   |                    |

Table 1.1: Physical medium and number of carriers used in each G.hn bandplan.

(WLANs) based on the IEEE 802.11 standard. However, poor signal propagation across walls make WLANs unsuitable for high-speed applications such as high-definition inhome video streaming, leading to the development of wired technologies using the existing in-home infrastructure. The ITU-T G.hn recommendation (G.9960 and G.9961) unifies the most widely used wired infrastructures at home (coaxial cables, phone lines and power lines) into a single standard for high-speed data transmission of up to 1 Gb/s.

The G.hn recommendation defines a unified networking over power lines, phone lines and coaxial cables. The physical medium available and number of carriers used in each bandplan are listed in Table 1.1 and its distribution shown in Fig. 1.1. The RF-coax bandplan, where this thesis is focused, uses 50 MHz and 100 MHz bandwidth channels with 256 and 512 carriers respectively. The center frequency can range from 350 MHz to 2450 MHz. The recommendation specifies a transmission power limit of 5 dBm for the 50 MHz bandplan and 8 dBm for the 100 MHz bandplan, therefore the power spectrum density (PSD) is the same for both bandplans.

Due to the nature of an in-home wired environment, receivers that can handle

both very large and very small amplitude signals are required: when transmitter and receiver are connected on the same electric outlet there is no channel attenuation and the signal-to-noise-plus-distortion ratio (SNDR) is dominated by the receiver linearity, whereas when transmitter and receiver are several rooms apart channel attenuation is high and the SNDR is dominated by the receiver noise figure. The high-dynamic-range specifications for these receivers require the use of configurable-gain topologies that can provide both high-linearity and low-noise for different configurations [3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13].

The minimum value of SNDR depends on the design of each particular application. The G.hn recommendation provides a maximum bit-error rate (BER). The maximum data-rate of a communications system is limited by the maximum bit-error-rate (BER) that is specified to achieve throughput requirements. SNDR, a parameter usually used to define the dynamic range of an analog front-end, is directly related to BER [14, 15, 16]. Therefore, analog front-ends aim at providing a value of SNDR that is above a specified minimum value for a given range of input signal power to comply with the maximum allowed BER of the whole system.

The minimum value of SNDR ultimately depends on the maximum transmission distance that wants to be achieved at a given throughput (as the transmission distance increases, the receiver signal power decreases and thus SNDR decreases) and the maximum throughput that wants to be achieved at minimum distance (as the SNDR increases, the throughput can be increased while maintaining the same transmitted power). The system designer establishes the minimum SNDR of each stage in order to achieve the target value for the whole receiver to comply with the specifications of BER, transmission distance and throughput.

As will be seen in a later subsection, the required specifications for the G.hn frontend provided by the company include a minimum value of SNDR that needs to be achieved for a given range of input power.

#### 1. INTRODUCTION

### 1.3 Towards low-cost broadband inductor-less SoCs

System-on-Chip (SoC) was adopted in recent years as one of the solutions to reduce the cost of integrated systems. When the SoC solution started to be used, the final product was actually more expensive due to lower yield. The developments in integrated technology through the years allowed the integration of more components in lesser area with a better yield. Thus, SoCs have become a widely used solution to reduced the cost of the final product, integrating into a single-chip the main parts of a system: analog, digital and memory.

As integrated technology kept scaling down to allow a higher density of transistors and thus providing more functionality with the same die area, the analog RF parts of the SoC became a bottleneck to cost reduction as inductors occupy a large die area and do not scale down with technology. Hence, the trend moves toward the research and design of inductor-less SoCs that further reduce the cost of the final solution.

At the same time, as the demand for home networking high-data-rates communication systems has increased over the last decade, new communication systems using large channel bandwidths such as G.hn have been created to satisfy these needs. Broadband inductor-less design presents a challenge as inductors cannot be used for peaking in order to compensate the parasitic capacitances.

### **1.4** Research Goals and Contributions

This thesis aims at researching high dynamic range broadband inductor-less topologies to be used as the RF front-end for a G.hn receiver complying with the provided specifications. The main specifications of the RF front-end are defined in Table 1.2.

A large part of the thesis is focused on the design of the input amplifier of the frontend, which is the most critical stage as the noise figure of the input amplifier defines the achievable overall specifications of the whole front-end. Three prototypes have been manufactured in two different runs using a 65 nm CMOS process: two input RF programmable gain amplifiers (RFPGAs) and one front-end using the second RFPGA

| Specification                                | Value                         |

|----------------------------------------------|-------------------------------|

| Number of gain settings                      | 8                             |

| Output voltage (with 12 dB PAR input signal) | $\geq 0.15 \ \mathrm{V}_{pp}$ |

| SNDR                                         | $\geq 35 \text{ dB}$          |

| Power consumption                            | $\leq 50 \text{ mW}$          |

| Input power dynamic range                    | $\geq 80 \text{ dB}$          |

| Maximum input power (100 MHz channel)        | $5~\mathrm{dBm}$              |

| Maximum input power (50 MHz channel)         | 2  dBm                        |

Table 1.2:

G.hn RF front-end specifications.

prototype.

### 1.5 Thesis Organization

Chapter 2 contains an introduction to receiver front-end fundamentals. It explains concepts that will be used later on in the design and measurement of the prototypes such as noise, distortion and dynamic range. This chapter also presents available configurable architectures and the reasons behind choosing pre-attenuation based topologies for the design of the front-end.

Chapter 3 contains an introduction to design techniques for high-dynamic-range broadband inductorless RF amplifier circuits. Some of these techniques are used in the design of the amplifier prototypes, such as the active feedback input impedance matching, providing further insight on its design in the proposed prototypes. Other techniques, such as pre-attenuation based amplifiers to provide high dynamic range, are expanded by providing new alternative circuit topologies improving the existing performance.

Chapter 4 contains the design and experimental results of the first RFPGA prototype. The RFPGA is a fully-differential two-stage configurable pre-attenuation based amplifier providing 4 different gain settings. One of the gain settings is provided by by-passing the second amplifier, whereas the other 3 gain settings are provided by using a switchable capacitive attenuation topology at the input. The RFPGA uses 2 different methods of input impedance matching. The prototype has been fabricated in a 65 nm

#### 1. INTRODUCTION

CMOS technology, packaged inside a QFN and measured on PCB.

Chapter 5 contains the design and experimental results of the second RFPGA prototype. This RFPGA is a fully-differential double-input configurable pre-attenuation based amplifier providing 4 different gain settings with a single stage using a switchable capacitive attenuation topology. The second RFPGA also uses 2 different method of input impedance matching. The prototype has been fabricated in a 65 nm CMOS technology, packaged inside a QFN and measured on PCB.

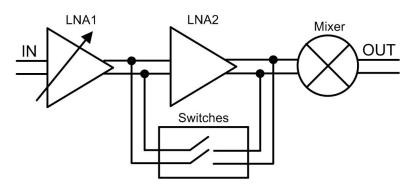

Chapter 6 contains the design and experimental results of the front-end prototype. The front-end input amplifier uses the double-input (DI) RFPGA presented in Chapter 5. The mixer uses a folded topology composed of a current re-use transconductance amplifier (CR-TCA) and a switching stage. The CR-TCA can be by-passed thus connecting the DI-RFPGA directly to the switching stage, providing another method of configuration. Therefore, the front-end provides a total of 8 different gain settings. The prototype has been fabricated in a 65 nm CMOS technology, packaged inside a QFN and measured on PCB.

Chapter 7 contains the conclusions and suggestions for future research.

# Receiver Front-End Fundamentals

### 2.1 Introduction

This chapter presents front-end fundamentals that will be used along the thesis. The chapter starts by introducing the concepts of noise, sensitivity and distortion which are basic measures for both individual circuits and front-ends. These three concepts combine together to obtain the metric of dynamic range, which provides a measure of the circuit's capability to handle a large range of input power while maintaining a minimum signal-to-noise-plus-distortion ratio (SNDR).

We also introduce the noise-power-ratio (NPR) metric which is the process used to measure the front-end dynamic range in Chapter 6. Since the front-end is designed for a multi-carrier system, a metric such as NPR that uses multiple input-tones provides a more reliable measure of circuit distortion than the classical third-order intercept point (IP3). The chapter ends by providing frequency conversion concepts to cover basic mixer specifications.

### 2.2 Noise and Sensitivity

Noise is a parameter of critical importance in any receiver as it corrupts the desired signal carrying the information resulting in an increase of the bit-error rate (BER). The addition of noise by a circuit is usually characterized by the noise factor (F) or alternatively by the noise figure (NF) when using logarithmic scale, which is defined as how the signal-to-noise ratio (SNR) changes from input to output:

$$F = \frac{SNR_{in}}{SNR_{out}} \tag{2.1}$$

Since the signal of interest spans over a given bandwidth, the noise must be integrated over that bandwidth for the calculations. Noise figure is related to sensitivity in the sense that sensitivity is the minimum signal level the system can detect while providing a minimum value of SNR (which is calculated from the maximum allowed BER). By developing Eq. 2.1 we can define the sensitivity at room temperature as [17]:

$$P_{in_{min}} = -174 dBm/Hz + NF + 10 log BW + SNR_{min}$$

$$(2.2)$$

By using the maximum allowed BER of the system, the system designer can extract the minimum SNR value of the front-end. Then, the system designer sets the desired sensitivity of the system which is calculated using the maximum desirable transmission distance (as transmission distance increases, the signal is attenuated by the transmission channel and the received signal power decreases). By using the minimum SNR and the sensitivity and Eq. 2.2, the required NF of the whole front-end is obtained. Finally, the NF of each single stage is established at system level so that the NF of the whole front-end is below the calculated value. The total NF of the front-end can be expressed by the NF and gain of each individual stage [18]:

$$NF_{tot} = 10\log\left(F_1 + \sum_{i=2}^{n} \frac{F_i - 1}{\prod_{j=1}^{i-1} G_j}\right)$$

(2.3)

Where n is the number of stages and G is the gain of each corresponding stage. This

equation considers equal input and output impedances for each stage. For different output and input impedances, which is usually the case in integrated circuits, the cascaded noise figure can be expressed as [18]:

$$NF_{tot} = 10\log\left(F_1 + \sum_{i=2}^{n} \frac{F_i - 1}{\prod_{j=1}^{i-1} G_j^2 \left(\frac{R_{in_j}}{R_{out_{j-1}} + R_{in_j}}\right)^2 \frac{R_{out_{j-1}}}{R_{out_j}}}\right)$$

(2.4)

Where  $R_{in}$  is the input impedance of each corresponding stage,  $R_{out}$  is the output impedance of each corresponding stage and  $G_v$  is the voltage gain of each corresponding stage. As can be seen from the equations, the noise figure of each stage is divided by the gain of the previous stages when their contribution to the whole front-end is taken into account. Therefore, the most critical stage in terms of noise figure is the input amplifier since there is no previous amplification.

### 2.3 Distortion

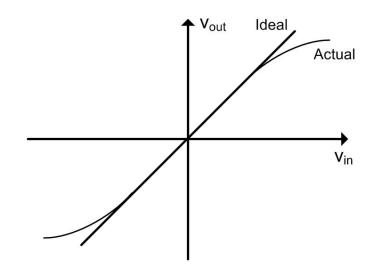

Ideally, an amplifier device has a linear response from input voltage to output voltage. However, in a practical implementation, the devices have a non-linear response as shown in Fig. 2.1. In a simplified time-invariant model, the response of the amplifying device can be represented as a Taylor series:

$$v_{out} = a_0 + a_1 v_{in} + a_2 v_{in}^2 + a_3 v_{in}^3 + a_4 v_{in}^4 + \dots$$

(2.5)

The first term is the output DC voltage of the amplifying device, and the second term is the term of interest corresponding to the amplified input signal. The higher order terms result in unwanted distortion components (intermodulation) which mask the wanted signal reducing the SNR. If *vin* is composed of only one tone, the highorder components are located at frequencies multiple to that of the input tone and the unwanted distortion is located far from the frequency of interest. However, when the input signal contains two or more tones, the high-order components generate harmonics whose frequencies are a combination of the frequencies of the input tones. Some of these

Figure 2.1: Actual versus ideal behavior of an amplifying device.

combinations fall at the frequencies of the input signal, thus adding distortion at the band of interest which decreases the SNR.

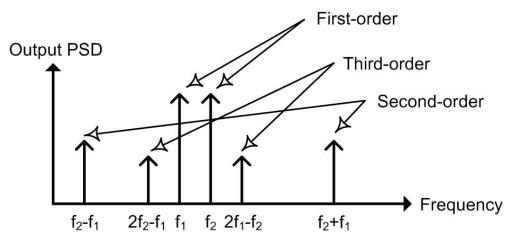

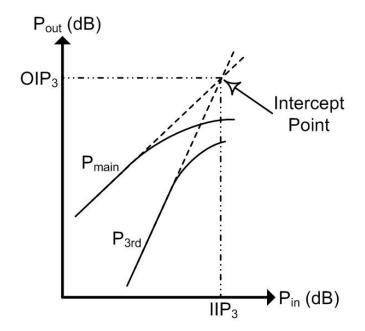

The most significant harmonics in terms of amplitude are due to the second-order and third-order non-linearities [19] whose location is shown in Fig. 2.2. Second-order harmonics can be minimized by using a differential topology. However, third-order harmonics are present in both single-ended and differential topologies. Thus, the most common measure of linearity for RF input amplifiers is the third-order input intercept point (IIP3), which provides the value of input power for which the output wanted signal and output unwanted third-order product have the same power, as shown in Fig. 2.3.

The high-order terms have a slope in logarithmic scale equal to that of the order of the polynomial (second-order non-linearities have a slope of 2, third-order a slope of 3, and so on). Therefore, intermodulation distortion is mainly important when handling large values of input power, since for the small values the power of the harmonics is much smaller than that of the signal of interest (Fig. 2.3). Then, as opposed to noise where the required front-end NF is calculated by using the minimum SNDR for the smallest input power signal, the required front-end IIP3 is calculated by using the minimum SNDR for the largest input power signal. The cascaded IIP3, equivalent to

Figure 2.2: Location of second-order and third-order non-linearities.

Figure 2.3: Third-order intercept point.

the cascaded noise figure, can be calculated from the IIP3 and gain of each individual stage for equal input and output impedances [18]:

$$IIP_{3_{tot}} = -10log\left(\sum_{k=1}^{n} \frac{\sum_{j=1}^{k-1} G_j^2}{IIP_{3_k}}\right)^{\frac{1}{2}}$$

(2.6)

Where  $IIP_{3x}$  is the third-order intercept point of each corresponding stage and  $G_x$  is the voltage gain of each corresponding stage. One difficulty in obtaining a closed expression for the front-end cascaded IIP3 is the distortion components of different stages combine between themselves in a way that depends on the phases of each individual component [20]. The previous equation considers the conservative worst-case where all the phases are equal and thus the intermodulation products add directly.

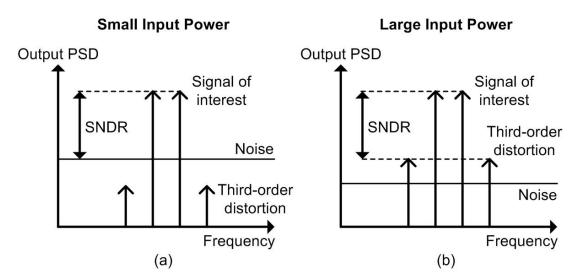

However, the IIP3 metric considers the case of only two input tones. Present broadband communications systems such as G.hn use a large numbers of carriers up to 512 and the theoretical distortion analysis of such a system becomes very complex. The final objective of a distortion measure is to provide a reliable value of intermodulation distortion (IMD) that can be used to calculate the SNDR of the system as shown in Fig. 2.4 for large and small input signal power. Multiple-tone IMD for SNDR calculation can be obtained either by an indirect metric using IIP3 values such as composite triple beat (CTB) [4] or direct metrics such as adjacent channel power ratio (ACPR) and NPR [21, 22] which use a multiple-tone input signal.

As opposed to other communication systems where the distortion and SNDR are based upon the interaction between the signal of interest and out-of-band blockers, in this application there is only one channel with a signal of interest composed of multiple carriers and the out-of-band blockers are filtered with a diplexer. Therefore, the distortion and SNDR are based upon the interaction of all the in-channel carriers between themselves.

Figure 2.4: SNDR calculation at (a) Small input power (b) Large input power.

# 2.4 Dynamic Range

Dynamic range is defined as the difference between the maximum power and the minimum power a circuit can handle, where the definition of maximum and minimum power depends on each particular application. In the case of an RF front-end inside of a whole receiver system, the maximum and minimum power the circuit can tolerate is defined by the minimum SNDR the DSP stage needs to provide the required maximum BER. The maximum power is limited by the distortion generated by the circuits whereas the minimum power is limited by the sensitivity. This difference between the minimum and maximum power values is the dynamic range of the system.

Standards such as G.hn require a large dynamic range as they can receive both large amplitude input signals when both transmitter and receiver are connected at the same wall electrical outlet, and very small amplitude input signals when transmitter and receiver are located far from each other at different rooms. Such a large dynamic range requires the use of Automatic Gain Control (AGC) [19]. When not using AGC, a frontend must comply with the noise and distortion specifications simultaneously, which given current CMOS technologies and power consumption constraints is not viable. Therefore, configurable topologies are a common design solution in high dynamic range

#### 2. RECEIVER FRONT-END FUNDAMENTALS

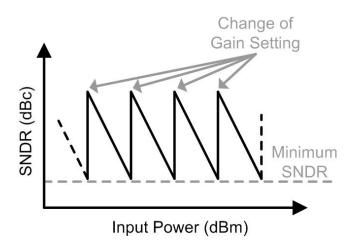

Figure 2.5: SNDR vs input power with constant SNDR steps.

front-ends [3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13].

Configurable topologies provide different gain settings with different specifications of noise and linearity. For the lowest value of input power the front-end is configured at the gain setting which provides the best noise figure, that being the highest gain setting. As the input power increases the minimum SNDR is reached and the front-end is configured at the next gain settings which increasingly provides better linearity, thus resulting in better SNDR as shown in Fig. 2.5, until the maximum input power is reached and the front-end is configured at the last gain setting providing maximum linearity.

The ideal way to perform experimental measures of dynamic range is to use a multiple-tone input signal equivalent to that of the practical application so that the SNDR can be measured directly, instead of measuring separately the noise output power and the distortion output power (through an indirect measure such as using IIP3 to calculate the CTB [4]) and adding them together to find the floor level. This thesis performs the SNDR measurements using the noise power ratio (NPR) metric.

#### 2.4.1 NPR Measurements

NPR is a figure of merit used to measure the SNDR of a given circuit and provides a more reliable value than indirect figures of merit calculated through the IIP3 measured

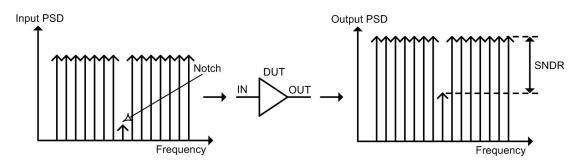

Figure 2.6: NPR measurement process.

values [23]. The NPR measurement is based on creating a broadband input stimulus with power, occupied bandwidth, carrier spacing and spectral shape equivalent to those of the practical case and adding a notch at some frequency location inside the channel. Then, the test signal is fed through the device under test (DUT) and the resulting SNDR is measured at the output using a power spectrum analyzer, as shown in Fig. 2.6.

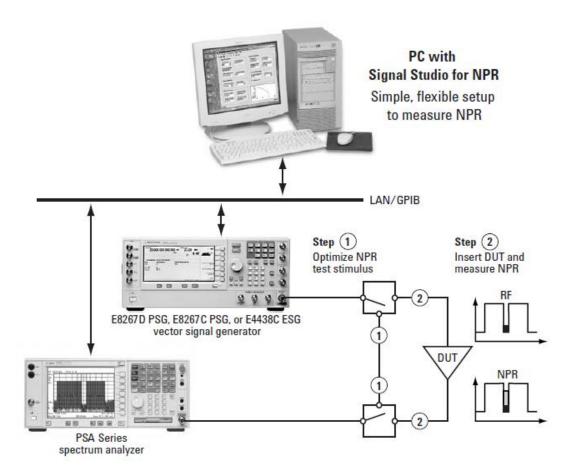

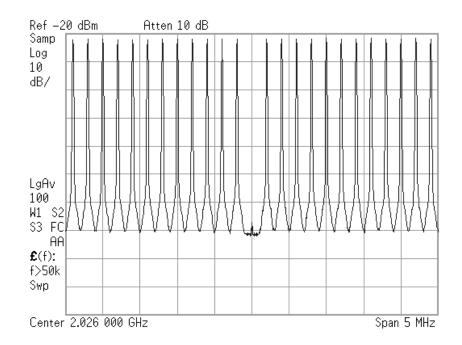

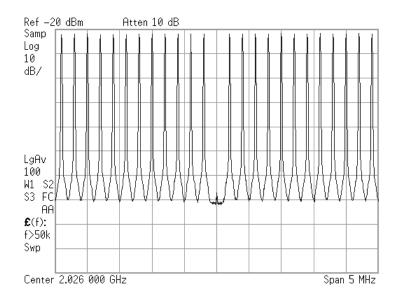

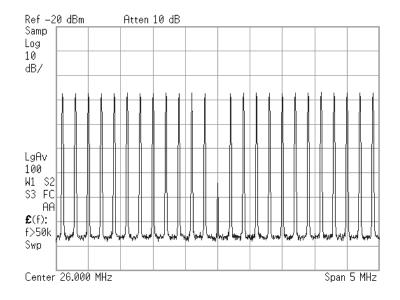

The important factor in an NPR measurement is for the SNDR at the input between the signal of interest and the notch to be sufficiently below the maximum value of SNDR that wants to be measured at the output. To obtain an input SNDR larger than 60 dB in the front-end measures for this thesis, we use the Agilent Signal Studio for Noise Power Ratio [24]. This method uses a computer, a vector signal generator and a power spectrum analyzer connected via LAN or GPIB as shown in Fig. 2.7. The vector signal generator creates an input signal with the specifications (channel bandwidth, carrier spacing, number of carriers and signal power level) configured by the user and the notch power level is measured using the power spectrum analyzer. If the notch is not low enough, the computer configures the vector signal generator to add pre-distortion to the generated signal in order to decrease the notch power. This process is repeated continuously in a closed loop until the required notch power level is achieved or the maximum number of iterations is achieved. A sample screenshot of input signal after applying pre-distortion zooming into the notch is shown in Fig. 2.8, and a sample screenshot of the resulting signal passing through a front-end including down-conversion is shown in Fig. 2.9.

### 2. RECEIVER FRONT-END FUNDAMENTALS

Figure 2.7: Agilent Signal Studio for Noise Power Ratio configuration.

Figure 2.8: Sample screenshot of NPR input signal after applying pre-distortion zooming into the notch.

Figure 2.9: Sample screenshot of a front-end output NPR measurement zooming into the notch.

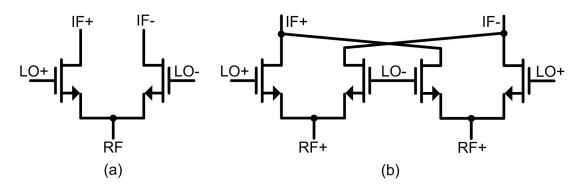

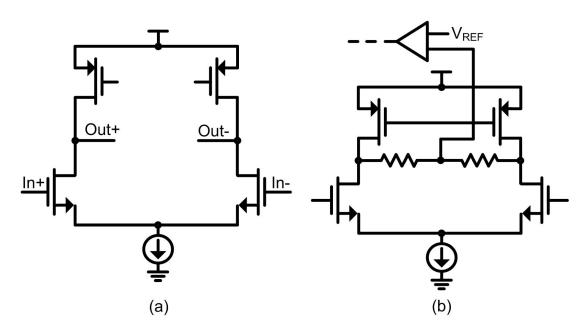

Figure 2.10: Common mixer implementation in CMOS (a) Single-ended (b) Differential.

# 2.5 Frequency Conversion

The RF signals in a receiver need to be down-converted to a lower frequency before they go into the analog-to-digital converter (ADC) which transforms the waveform into a digital signal. The process of digital conversion is not performed at RF due to the high power consumption of ADCs at high frequencies. The circuit that performs the frequency down-conversion process is called mixer and consists of two inputs, the RF and local oscillator (LO) ports, and one output, the intermediate frequency (IF) port.

The mixer contains a circuit that multiplies the LO signal by the RF signal. The product of these two signals can be decomposed into two components, one of which is the sum of the frequencies of RF and LO and the other is the difference. Therefore, the component of interest at the output (IF port) is the RF - LO term (or LO - RF if LO has a higher frequency than RF) which converts the RF signal to a lower frequency. The LO is usually a sinusoid signal.

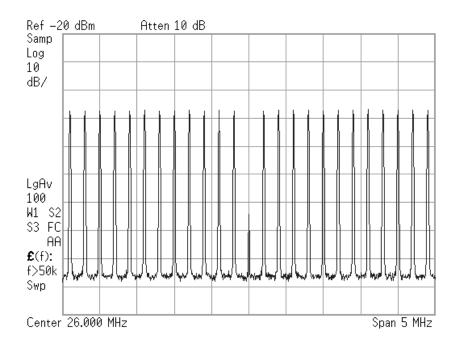

The most common mixer topology in CMOS technology uses the structure shown in Fig. 2.10 (single-ended and differential). The RF signal enters through the source of the transistors and the LO signal through the gate. Two instances of LO signal are used, one at 0 phase and the other at 180 phase identified as LO+ and LO- respectively. The goal in the design process is to have only half of the transistors on at any given time. The resulting differential signal at the output (the IF port) contains two terms as previously mentioned, at the sum and difference frequency of the LO and RF signals.

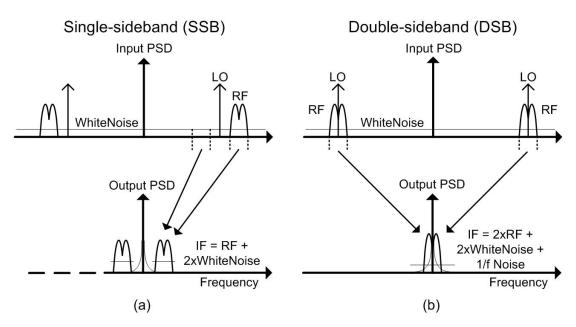

Figure 2.11: SSB and DSB mixer concepts.

The LO frequency can be higher/lower than the RF frequency in which case the mixer topology is called single-sideband (SSB) and is shown in Fig. 2.11a. If the LO frequency is located just in the middle of the RF signal, the mixer topology is called double-sideband (DSB) or direct conversion and is shown in Fig. 2.11b.

In an SSB mixer, the IF signal contains only one instance of the RF signal and two instances of white noise. Thus, the noise figure increases not only due to the noise added by the mixer circuitry itself, but also due to the conversion mechanism. In a DSB mixer, although the IF contains two instances of the RF signal and two instances the white noise, it also contains 1/f noise. In this case, the noise added through the conversion mechanism is due to the 1/f noise. Whether to use a DSB or SSB topology is decided by the system designer. The mixer in this thesis is designed as an SSB topology.

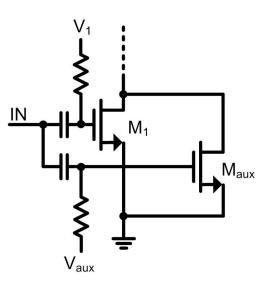

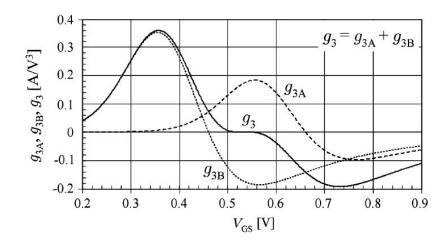

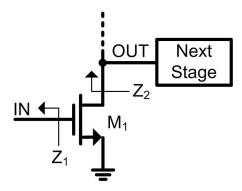

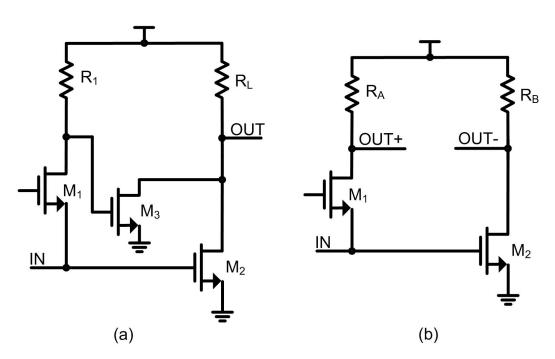

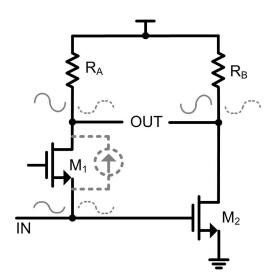

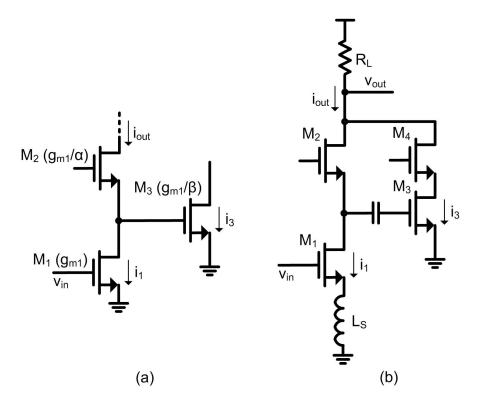

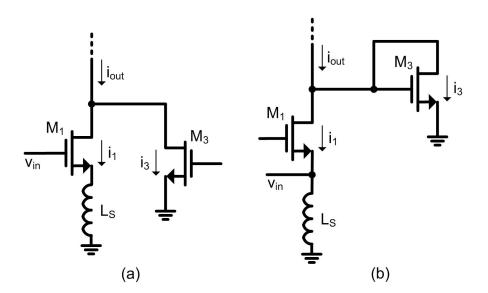

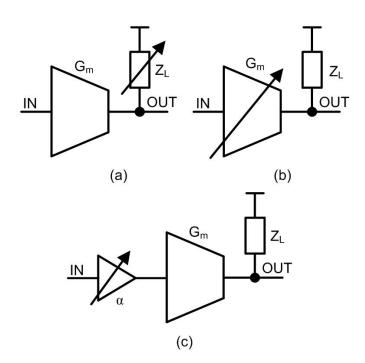

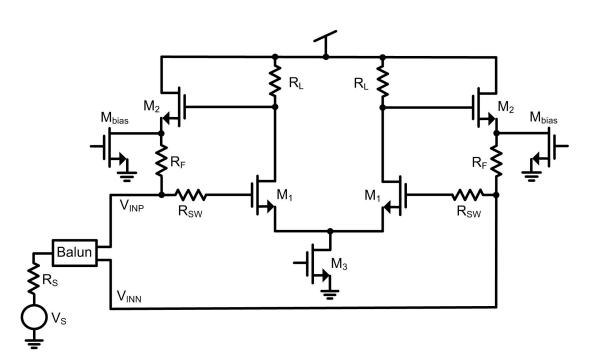

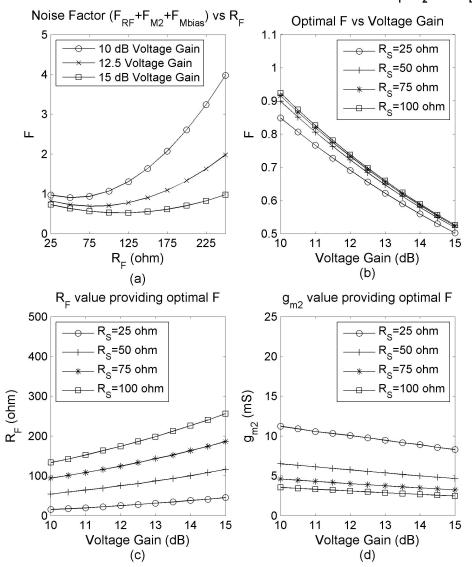

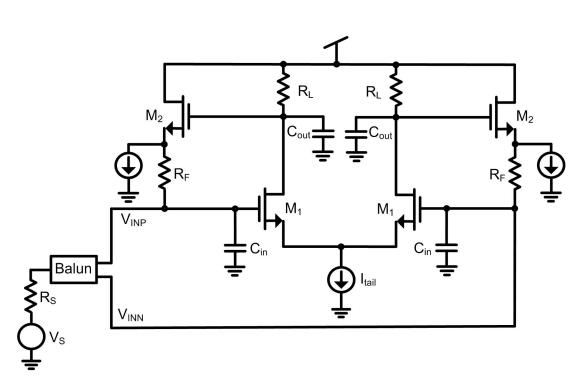

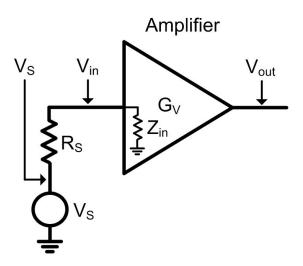

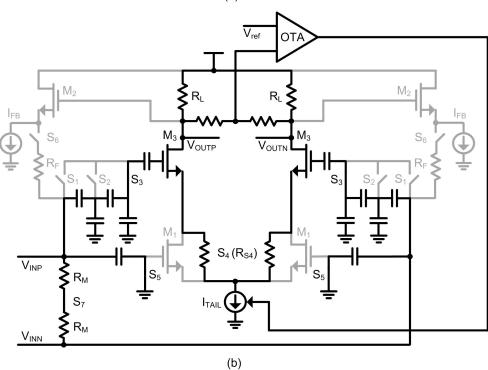

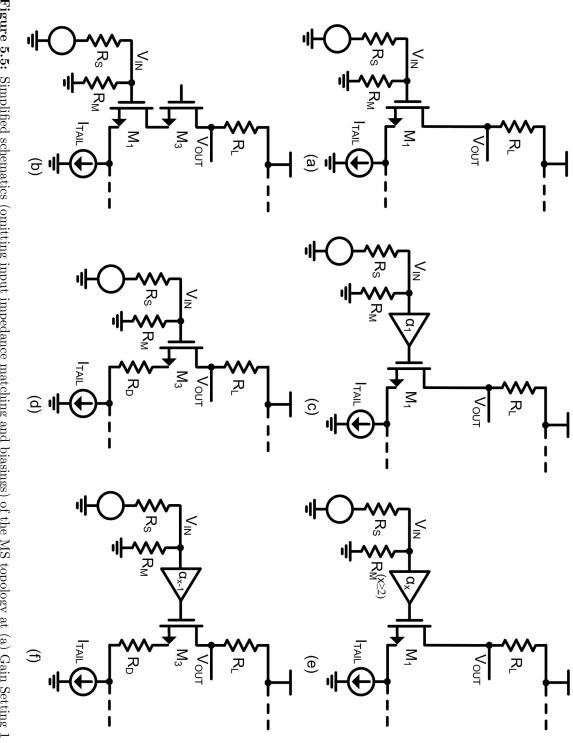

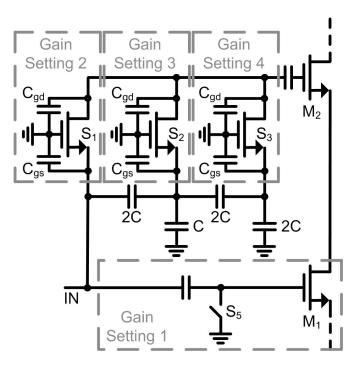

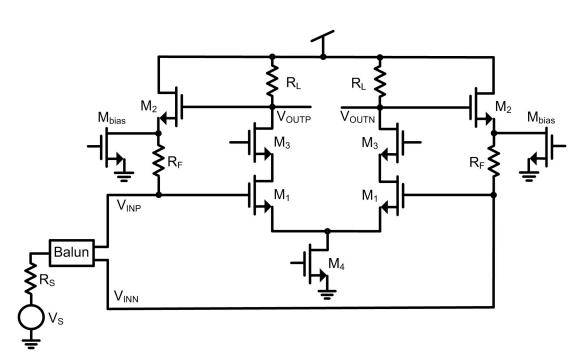

Mixers can be either active (they use a bias current) or passive (they use no biasing current). Passive mixers have losses but generally provide a better linearity than active topologies, whereas active topologies provide gain and thus a better overall front-end noise figure. Although passive mixers have no biasing current, they require large LO amplitudes to provide a large linearity, indirectly resulting in a considerable increase of the mixer power consumption. Thus, it cannot be considered that the passive mixer has no power consumption. Also, a passive mixer has losses. If these losses need to be compensated at later by adding gain using an amplifier, power consumption will be increased further.