# DESIGN OF A CONDITIONING CIRCUIT FOR MAGNETIC CMOS-MEMS SENSORS

A Master's Thesis

Submitted to the Faculty of the

Escola Tècnica Superior d'Enginyeria de

Telecomunicació de Barcelona

Universitat Politècnica de Catalunya

by

Claus Bauzà Alcover

In partial fulfilment of the requirements for the degree of MASTER IN ELECTRONIC ENGINEERING

Advisors: Josep Maria Sánchez Chiva,

Daniel Fernández

Barcelona, October 2017

# <u>Title of the thesis: Design of a Conditioning Circuit for Magnetic</u> **CMOS-MEMS Sensors**

### **Author:**

Claus Bauzà Alcover

### **Advisors:**

Josep Maria Sánchez Chiva

Daniel Fernández

### **Abstract**

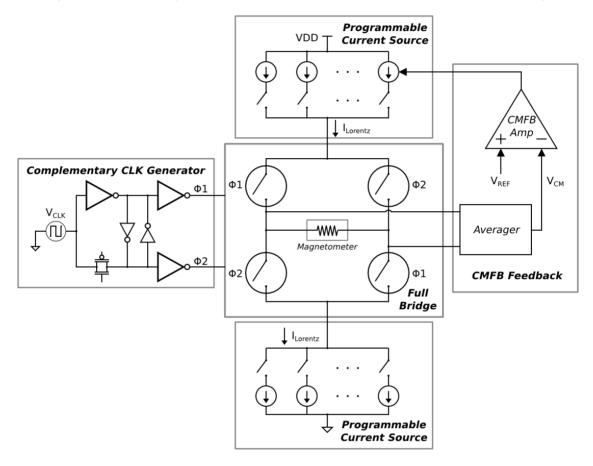

This thesis report describes the design process of two different analog circuits required to perform the readout of a CMOS-MEMS Magnetometer based on the Lorentz Force Effect.

The designed circuits are the Low Noise Amplifier (LNA) that performs the conditioning of the sensor response and the Programmable Floating Current Source needed to induce the Lorentz Force in the sensor. Both circuits are meant to be integrated on-chip with the magnetometer and fabricated with a 180 nm CMOS technology provided by Taiwan Semiconductor Manufacturing Company (TSMC).

The result of the design is a Fully Differential Operational Transconductance Amplifier based on a Folded Cascode Topology with 10 nV/ $\sqrt{\text{Hz}}$  of input referred noise and a Floating Current Source with a 3-bit programmability which allows different current values from 8  $\mu\text{A}$  to 1 mA. In the case of the LNA, the design is made at both schematic and layout level with a final area of 368  $\mu\text{m}$  x 136  $\mu\text{m}$ , which represents a 44% of the sensor's surface (615  $\mu\text{m}$  x 182  $\mu\text{m}$ ).

As for the Programmable Current Source, the design was made at schematic level and its estimated area is  $103 \mu m \times 103 \mu m$ , a 9.5% of the sensor's.

Furthermore, during the design of the differential LNA, a low consumption alternative to enhance the linearity of the Common Mode Feedback (CMFB) loop was found. With this approach, based on a source degeneration of the differential pair, an error amplifier with low consumption,  $53.3~\mu\text{A}$ , was achieved.

Finally, an optimal value for the degeneration resistor was found when linearizing the CMFB loop. As a result, a SFDR of 80dB was obtained.

### **Acknowledgements**

I owe my gratitude to all people who contributed in the realization of my master thesis. I would like to first thank my supervisors Daniel Fernández and Jordi Madrenas for giving me the opportunity of working in a field as interesting as CMOS MEMS and for their supervision and guidance during this Master Thesis.

Additionally, I would like to express my sincere gratitude to my daily supervisor Josep Maria Sánchez, since his dedication and assistance have been fundamental to deal with all the appearing issues of the project.

I also would like to thank my flatmates Xisco, Alberto, Carles and Martí, for all the funny moments we spent together.

And last but not least, my deepest thanks are dedicated to my parents, for their unconditional support and confidence during my studies and especially during this time in Barcelona.

# **Table of contents**

| Abstı  | ract   |                                                      | 1  |

|--------|--------|------------------------------------------------------|----|

| Ackn   | owle   | dgements                                             | 2  |

| Table  | e of c | ontents                                              | 3  |

| List o | of Fig | ures                                                 | 5  |

| List o | of Tal | oles                                                 | 8  |

| 1.     | Introd | luction                                              | 10 |

| 1.1    | 1. (   | Current State of CMOS MEMS                           | 10 |

| 1.2    | 2. [   | Description of the Magnetometer                      | 11 |

| 1.3    | 3. (   | Objectives of this Thesis                            | 12 |

| 2. I   | Read   | out Circuit                                          | 13 |

| 2.1    | 1. L   | NA Topology                                          | 13 |

| 2.2    | 2. (   | DTA Topology                                         | 16 |

| :      | 2.2.1  | Folded cascode topology                              | 16 |

| 2      | 2.2.2  | Gain and Unity Gain Frequency                        | 17 |

| 2      | 2.2.3  | Stability Analysis                                   | 19 |

| 2      | 2.2.4  | Noise                                                | 21 |

| 2      | 2.2.5  | Low-voltage current mirror                           | 23 |

| 2.3    | 3. (   | Common Mode Feedback                                 | 26 |

| 2      | 2.3.1  | Differential Amplifier                               | 27 |

| 2      | 2.3.2  | CMFB Loop Response                                   | 28 |

| 2      | 2.3.3  | Feed Forward Stabilization (Nulling Resistor)        | 30 |

| 2      | 2.3.4  | Source Degeneration (CMFB dynamic range enhancement) | 32 |

| 2.4    | 4. (   | OTA Characteristics after Design                     | 36 |

| 2.5    | 5. L   | ayout                                                | 40 |

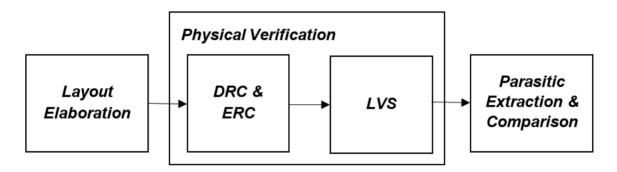

| 2      | 2.5.1  | Design Flow                                          | 40 |

| 2      | 2.5.2  | Mismatch Effects                                     | 41 |

| 2      | 2.5.3  | Matching Techniques                                  | 42 |

| 2      | 2.5.4  | Layout Result                                        | 45 |

| 2      | 2.5.5  | Post Layout Simulation                               | 47 |

| 3. I   | Progi  | ammable Floating Current Source                      | 48 |

| 3.1    | 1. (   | Current Source Description                           | 48 |

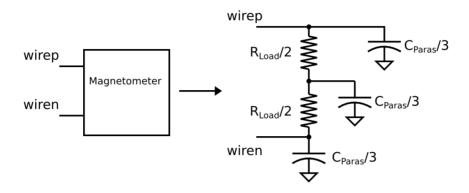

| ;      | 3.1.1  | Magnetometer Model                                   | 49 |

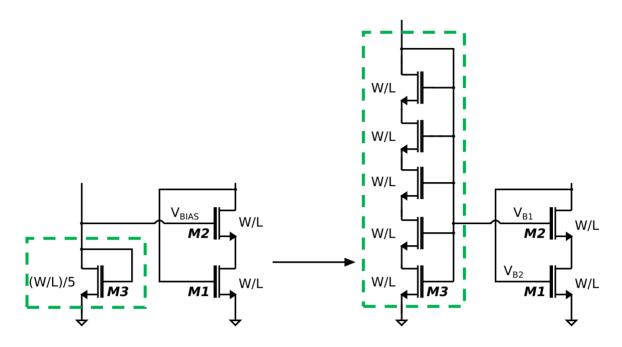

| 3.2    | 2. (   | Current Mirror Topology                              | 49 |

| 3.2.1.       | Low-voltage topology                                                | 49 |

|--------------|---------------------------------------------------------------------|----|

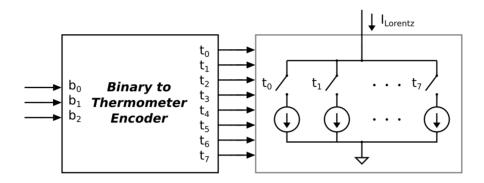

| 3.2.2.       | Programmability                                                     | 51 |

| 3.3. Co      | ommon Mode Feedback Amplifier                                       | 53 |

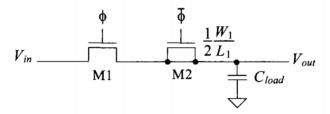

| 3.4. Sw      | vitch Sizing                                                        | 55 |

| 3.5. Tir     | ming Block                                                          | 57 |

| 3.5.1.       | Phase alignment between complementary signals                       | 59 |

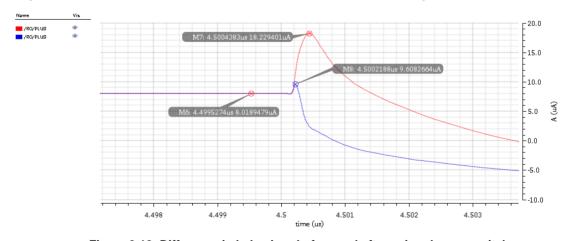

| 3.5.2.       | Zero Current                                                        | 60 |

| 3.6. Pro     | ogrammable Floating CS's Characteristics after Design               | 61 |

| 3.7. Are     | ea estimation                                                       | 65 |

| 4. Conclu    | sions and future development                                        | 67 |

| 4.1. Co      | onclusion                                                           | 67 |

| 4.2. Fu      | ture Work                                                           | 67 |

| Bibliography | y                                                                   | 68 |

| Appendices   | S                                                                   | 69 |

| 5. Derivat   | ion of expression for the CMFB's compensation network               | 69 |

|              | ion of the maximum differential amplitude for lineal behaviour of c | •  |

| Glossary     |                                                                     | 72 |

# **List of Figures**

| Figure 1.1: Market Growth of MEMS over the years expanding from the automotive in the wearables like smartphones [3]                                                                  | -       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Figure 1.2: Example of a CMOS MEMS Lorentz Force Magnetometer [5]                                                                                                                     | 11      |

| Figure 1.3: Frequency response of a Resonant System [6]                                                                                                                               | 12      |

| Figure 2.1: Half Bridge and Amplifier's configuration used to condition the magnet                                                                                                    | ometer  |

| Figure 2.2: Electric model of the magnetometer for the OTA design                                                                                                                     | 14      |

| Figure 2.3: Response of the LNA when sensing a magnetic field of B = 1mT with $I_{LC}$ 1mA and $V_{DC}$ = 1.65V                                                                       |         |

| Figure 2.4: Current provided the sensor due to charge variation when applying the I                                                                                                   |         |

| Figure 2.5: Folded Cascode Amplifier Used in the Design                                                                                                                               | 16      |

| Figure 2.6: DC current consumption at different parts of the OTA                                                                                                                      | 18      |

| Figure 2.7: Half circuit, with capacitances contributing to the non-dominant pole                                                                                                     | 20      |

| Figure 2.8: Schematic highlighting the main noise contributors                                                                                                                        | 21      |

| Figure 2.9: Low-Voltage Current Mirror Topology [10]                                                                                                                                  | 23      |

| Figure 2.10: Current mirror and reference for cascode transistors. Instead of lower aspect ratio by using narrower transistors, several transistors in series generates cascode bias. | ate the |

| Figure 2.11: PMOS transistors in series generating Vbias for all PMOS cascodes                                                                                                        | 25      |

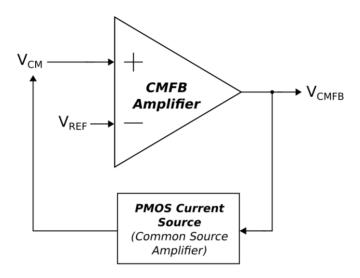

| Figure 2.12: Block Diagram of a CMFB                                                                                                                                                  | 26      |

| Figure 2.13: CMFB implemented with a Differential Amplifier                                                                                                                           | 27      |

| Figure 2.14: Current Sources acting as a Common Source Amplifier for V <sub>CMFB</sub>                                                                                                | 28      |

| Figure 2.15: Block Diagram of a CMFB using feed forward stabilization [13]                                                                                                            | 30      |

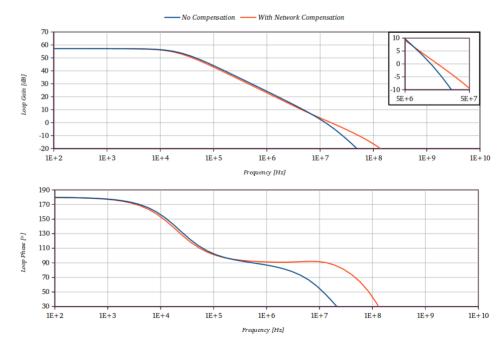

| Figure 2.16: Bode plot of the CMFB Loop before (blue) and after using competorange)                                                                                                   |         |

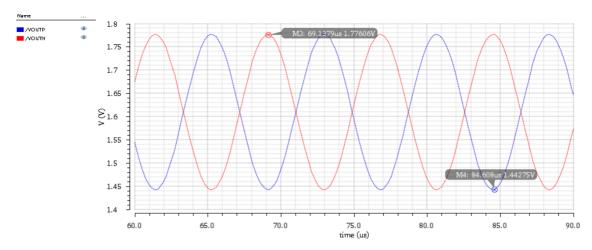

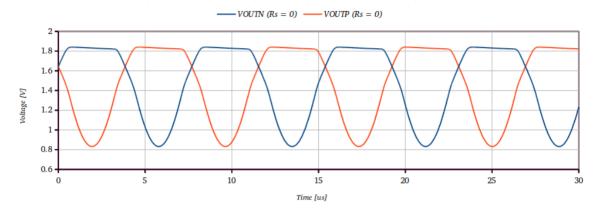

| Figure 2.17: CMFB distorts the Output Waveform                                                                                                                                        | 32      |

| Figure 2.18: A conventional NMOS differential pair and the one with source degen                                                                                                      |         |

| Figure 2.19: Output Waveform after adding source degeneration                                                                                                                         | 33      |

| Figure 2.20: Degradation of both Gain and GBW of the CMFB Loop when the resistor is higher. The resistance value was swept from 10k to 100k                                           |         |

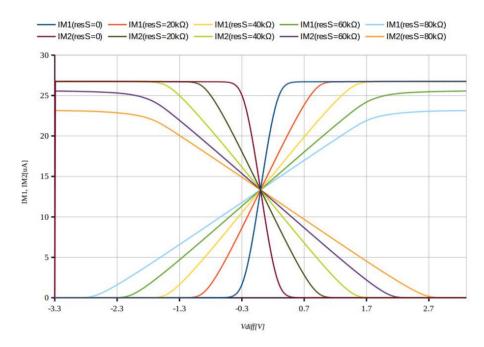

| Figure 2.21: Differential Pair Current with linearized response due to degeneration                                                                                                   | 34      |

| Figure 2.22: FFT of Input Signal (Single Ended Component). Fundamental tone at 1                                                                                                      |         |

| Figure 2.23: FFT of the amplifier output (single ended) for values of R <sub>Source</sub> 0kΩ and 57ks                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.24: SFDR obtained as a function of the R <sub>Source</sub>                                                                                                                                |

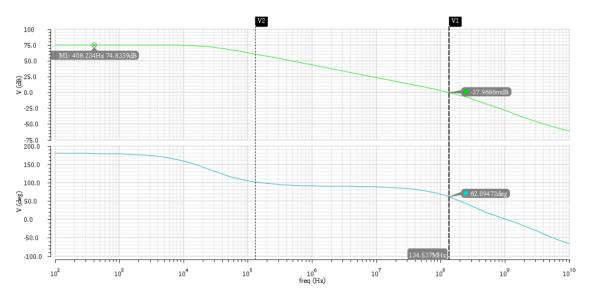

| Figure 2.25: Amplifier's gain and phase response vs frequency                                                                                                                                      |

| Figure 2.26: Complete schematic of the OTA3                                                                                                                                                        |

| Figure 2.27: Design Flow of a full custom Analog Layout4                                                                                                                                           |

| Figure 2.28: Group considered to apply matching techniques between transistors4                                                                                                                    |

| Figure 2.29: Matching Groups for the CMFB Amplifier4                                                                                                                                               |

| Figure 2.30: Example of interdigitated transistors A and B. Cases A and C show a interdigitation with common centroid whereas case B is an example of interdigitatio without common centroid [15]4 |

| Figure 2.31: Layout of the differential pair after interdigitation and applying th correspondent pattern to have common centroid                                                                   |

| Figure 2.32: Layout of the source degeneration applying the interdigitation and matchin pattern4                                                                                                   |

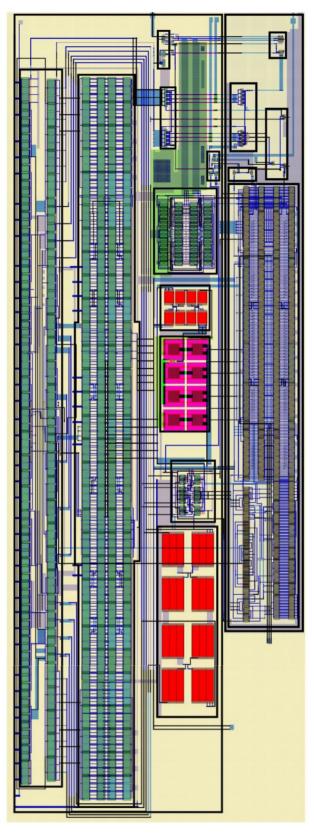

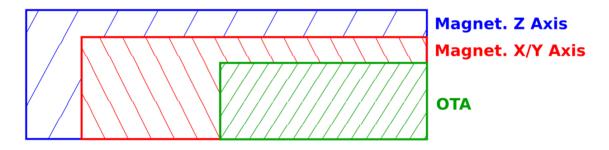

| Figure 2.33: Final Layout4                                                                                                                                                                         |

| Figure 2.34: Implemented floorplan when elaborating the layout4                                                                                                                                    |

| Figure 2.35: OTA Layout area compared with the area occupied by the sensors4                                                                                                                       |

| Figure 2.36: Output of the amplifier delivering 1Vpp of output at 130kΩ after post extractio simulation4                                                                                           |

| Figure 3.1: Block diagram implemented to design the Programmable Floating Currer Source4                                                                                                           |

| Figure 3.2: Schematic used to model the magnetometer4                                                                                                                                              |

| Figure 3.3: Schematic to generate biasing for the NMOS current sources (VB2) and the cascodes (VB2)5                                                                                               |

| Figure 3.4: Approach used to implement the programmable current source5                                                                                                                            |

| Figure 3.5: Programmable current source with NMOS transistors5                                                                                                                                     |

| Figure 3.6: Programmable current source with PMOS transistors5                                                                                                                                     |

| Figure 3.7: Binary to Thermometer encoder5                                                                                                                                                         |

| Figure 3.8: CMFB Amplifier5                                                                                                                                                                        |

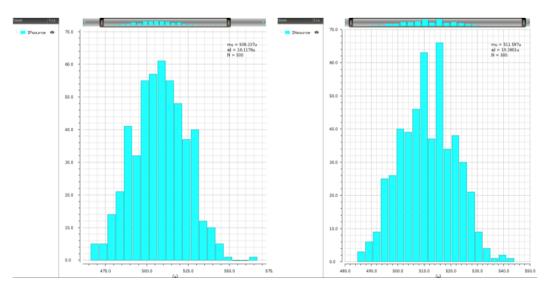

| Figure 3.9: Montecarlo Simulation considering only the programmable Current Source without CMFB control at 500uA. 5σ represents almost a 15% of the current driven by th programmable source       |

| Figure 3.10: Peaking reduction when reducing the area to implement switches5                                                                                                                       |

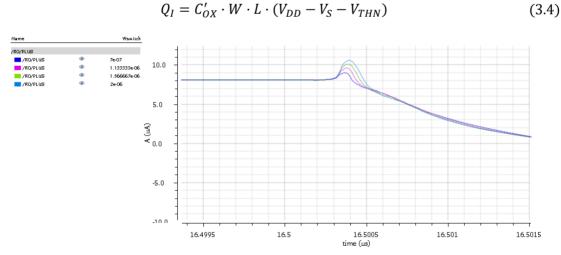

| Figure 3.11: Dummy switch M2 used to minimize charge injection at Vout [17]5                                                                                                                       |

| Figure 3.12: Difference in behaviour before and after using dummy switches5                                                                                                                        |

| Figure 3.13: Expected phases ph1 and ph2 obtained from the CLK signal5                                                                                                                             |

| Figure 3.14: Possible States for the Full Bridge when delivering a square current wavefor                                                                  |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.15: Timing Block Schematic                                                                                                                        | 58 |

| Figure 3.16: Schematic of the selector                                                                                                                     | 58 |

| Figure 3.17: Timing block output signals with aligned edges                                                                                                | 59 |

| Figure 3.18: Timing of the switches without edge alignment                                                                                                 | 59 |

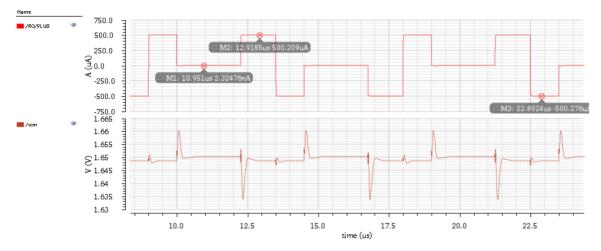

| Figure 3.19: Lorentz current at 500µA and zero current mode enabled. The current has intermediate steps by 0. Output DC voltage is still adjusted at 1.65V |    |

| Figure 3.20: Implemented approach to have Zero current in the waveform6                                                                                    | 30 |

| Figure 3.21: Current Source Schematic                                                                                                                      | 32 |

| Figure 5.1: Simplified version of the CMFB amplifier used to obtain the equations6                                                                         | 39 |

| Figure 6.1: Linear characteristic of a differential pair [8]                                                                                               | 71 |

# **List of Tables**

| Table 2.1: Sensor's parameters obtained from previously manufactured versions                                     | 14 |

|-------------------------------------------------------------------------------------------------------------------|----|

| Table 2.2: Table of Specs derived from the Sensor characteristics                                                 | 15 |

| Table 2.3: Transistor sizes for Folded Cascode Amplifier                                                          | 16 |

| Table 2.4: Size parameters and current required by the differential pair                                          | 18 |

| Table 2.5: PMOS cascode parameters after setting current                                                          | 19 |

| Table 2.6: OTA parameters after sizing the differential pair and the cascodes                                     | 19 |

| Table 2.7: Capacitances considered in the non-dominant pole and PM of the OTA                                     | 20 |

| Table 2.8: Flicker and Thermal contribution to the output referred noise of the rimportant transistors at 130 kHz |    |

| Table 2.9: Noise level achieved in the design                                                                     | 22 |

| Table 2.10: Sizes for the transistors of the biasing circuit for all NMOS current mirrors                         | 24 |

| Table 2.11: Sizes for the transistors of the biasing circuit for all PMOS cascodes                                | 25 |

| Table 2.12: Transistor sizes for Differential Amplifier used in CMFB                                              | 27 |

| Table 2.13: Expected locations of the second and third pole and parameters values uto estimate them               |    |

| Table 2.14: Expected parameters of β                                                                              | 29 |

| Table 2.15: Characteristics of the compensation network                                                           | 31 |

| Table 2.16: Main Parameters of the CMFB Response in the Nominal Corner a                                          |    |

| Table 2.17: Resistor value to implement source degeneration                                                       | 34 |

| Table 2.18: SFDR achieved with different R <sub>Source</sub>                                                      | 36 |

| Table 2.19: Pinnout of the OTA                                                                                    | 37 |

| Table 2.20: Specifications of the Folded Cascode OTA                                                              | 39 |

| Table 2.21: Matching pattern for differential pairs                                                               | 43 |

| Table 2.22: Matching pattern for current sources with their cascodes included inside pattern                      |    |

| Table 2.23: Matching pattern used for resistors and capacitors                                                    | 44 |

| Table 2.24: Dimensions of the designed OTA and the magnetometers                                                  | 46 |

| Table 2.25: Simulation results from post-extracted version of the OTA                                             | 47 |

| Table 3.1: Table of Specs for the Current Source                                                                  | 48 |

| Table 3.2: Electrical characteristics of the sensor used for simulation                                           | 49 |

| Table 3.3: Sizes for the transistors of the biasing circuit for all NMOS current mirrors                          | 50 |

| Table 3.4: Output current depending on the input binary code                                                      | 52 |

| Table 3.5: Transistor Sizes for the CMFB                                                                          | 53 |

| Table 3.6: Results of Montecarlo for different current values         | .54 |

|-----------------------------------------------------------------------|-----|

| Table 3.7: Switch Parameters and Voltage drop when delivering 1mA     | .56 |

| Table 3.8: Expected outputs of the timing block depending on the mode | .58 |

| Table 3.9: Pinnout of the Lorentz Current Source                      | .61 |

| Table 3.10: Specifications of the Lorentz Current Source              | .64 |

| Table 3.11: Data obtained from the area estimation                    | .66 |

### 1. Introduction

### 1.1. Current State of CMOS MEMS

accelerometer

for airbags

DRIE

process

During the last years, the use of MEMS for micro-scale sensors and actuators has grown up to a point in which they are now prevalent in our daily life [1]. Smart phones, automobiles, inkjet printers, planes, video consoles are just a few examples of common commercial application that include MEMS. Moreover, its market value is expected to reach 18.880 million U.S. dollars by 2022 [2].

Growing Market for MEMS Motion Sensors

# Automotive dominates Consumer Wearables IoT 1993 1994 1998 2006 2007 ADIADXL Bosch Bosch gryo Nintendo Wii Apple

Figure 1.1: Market Growth of MEMS over the years expanding from the automotive industry to wearables like smartphones [3]

controller

**iPhone**

for ESC

Micro-Electro-Mechanical Systems (MEMS) are micrometer-scale systems with both mechanical and electrical devices. Due to their reduced size and their electrical behaviour, one actual approach to fabricate them is using CMOS (Complementary Metal Oxide Semiconductor).

About CMOS, it is a mainstream technology since it is the predominant process used to fabricate integrated circuits (IC). Some advantages that MEMS could take from this technology are:

- The improvements in terms of yield and reliability that CMOS has acquired over the years.

- The possibility of integrating additional on-chip circuitry near the MEMS device too

[4].

When both MEMS and the electronics are fabricated with CMOS technology and are included inside the same chip, the term CMOS MEMS is often used to describe them [4].

Some examples of typical CMOS MEMS sensors are pressure sensors, inertial sensors, frequency reference devices [1] and magnetometers, which are the ones that we are considering for the design of our conditioning circuit.

The tradeoff in CMOS-MEMS is that in general it is not possible to modify the materials since manufacturers' purpose is to implement the electronic devices, not the micromechanical ones.

### 1.2. <u>Description of the Magnetometer</u>

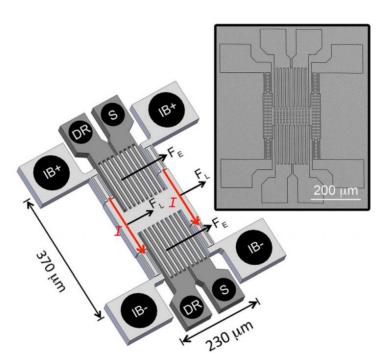

The magnetometer considered in this thesis can be regarded as a parallel-plate capacitor where one of the plates is fixed and the other is movable (Figure 1.2). Equation (1.1) shows the dependency with the distance between plates and their capacitance.

$$C = \frac{\varepsilon A}{z} \tag{1.1}$$

Figure 1.2: Example of a CMOS MEMS Lorentz Force Magnetometer [5].

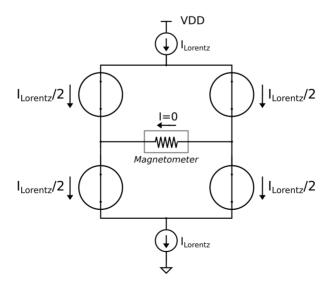

The Lorentz Force states that a charged particle moving at a given velocity in the presence of a magnetic field B experiences a force F. In our case, the moving particles are the electrons of the current flowing along the sensor's movable plate I, with length L. The resulting force is perpendicular to both the current and magnetic field.

$$\vec{F} = L\vec{I}_{Lorentz} x \vec{B} \tag{1.2}$$

When the Lorentz Force deforms the movable plate springs, the distance between plates changes, which at the same time causes a variation in the capacitance (as stated in equation (1.1)). Those variations can provide information about the applied magnetic field B.

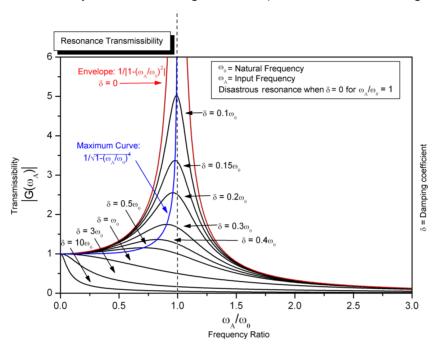

Furthermore, if the current that causes the Lorentz Force is applied periodically the movable plate acts as a mechanical resonator. For our application, this fact was interesting

because if the frequency of the Lorentz Force is similar to the natural frequency of the resonator, the changes in capacitance in front of the magnetic field are maximum.

In consequence we could say that at the resonance frequency, the sensor offers the maximum sensitivity in front of a magnetic field (behaviour similar to Figure 1.3).

Figure 1.3: Frequency response of a Resonant System [6]

From these assumptions, in order to work with the maximum possible sensitivity:

- The measurement of the capacitance variation is made in the AC domain.

- To tune the frequency of the Lorentz Force, the current that causes the Lorentz-Effect (I<sub>LORENTZ</sub>) should be AC and its frequency adjustable.

### 1.3. Objectives of this Thesis

The objective of this thesis is to design the electronics required by the sensor to:

- Perform the capacitive read-out.

- Provide the necessary current to cause the Lorentz-Effect.

For the read-out, a Low Noise Amplifier is used whereas a programmable floating source will provide the current for the Lorentz-Effect.

Both blocks are mostly analog and will be integrated on-chip along the sensor. Therefore the design will be made at transistor level and the results of this design will be the schematics and layout of both the LNA and the floating current source.

### 2. Readout Circuit

### 2.1. LNA Topology

This block is the responsible of reading the response of the CMOS-MEMS magnetometer and condition it to convert it in a signal more suitable for posterior processing systems.

To condition the sensor's response, a half Wheatstone bridge circuit and an amplifier are integrated on chip along with the sensor, as shown in Figure 2.1. The purpose consists in achieving a signal with better Signal to Noise Ratio (SNR) due to reduced parasitic capacitances at the interface nodes between the sensor and the LNA than in the case of using discrete components outside the chip. Hence, the noise is an important issue to consider in the design.

Figure 2.1: Half Bridge and Amplifier's configuration used to condition the magnetometer

### **Magnetometer Modelling**

The amplifier is designed specifically for this application. To determine the required specifications, a provided electric model of the sensor was used. Regarding this model, three main parameters are taken into account:

- The injected noise.

- The parasitic capacitance due to the plates that form the sensor.

- The current variation generated because of the magnetic field.

When the DC voltage across the sensor is kept constant, variations of the sensor capacitance are translated into a movement of charges that generates a current. This current is then measured by the LNA.

$$I_{Sense}(t) = \frac{dq_C(t)}{dt} = C(z)\frac{dU_C(t)}{dt} + U_C\frac{dC(t)}{dt} = V_{DC}\frac{dC(t)}{dt}$$

(2.1)

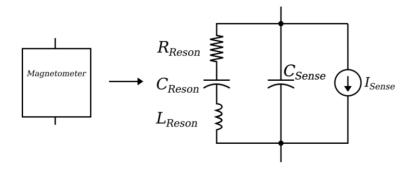

Thereby, it can be modelled as a fixed capacitance, an alternating current source to consider the charge variation and an additional RLC branch that represents the resonant behaviour of the sensor (see Figure 2.2). The current's amplitude depends on:

- The magnetic field measured at that moment, B.

- The amplitude of the current used to generate the Lorentz Force (I<sub>Lorentz</sub>).

- The DC voltage between the sensor plates.

$$I_{Sense}(t) = V_{DC} \cdot B \cdot I_{Lorentz} \cdot S \tag{2.2}$$

Where S is the sensor sensitivity, which depends on mechanical characteristics of the sensor.

Moreover, the sensor is a resonant one and its sensitivity turns out to be maximum at the resonant frequency. For our design, this resonant frequency is already characterized as 130 kHz. In consequence, we take this value as a constant when modelling the sensor.

In consequence, the output of the LNA should be a sinusoidal signal that behaves as indicated in equation (2.3), where  $C_f$  is the feedback capacitor.

$$V_{Out}(s) = \frac{I_{Sense}(s)}{sC_f}$$

(2.3)

|             | Sense<br>C [pF] | Parasitic<br>C [pF] | Brownian Noise $[nV/\sqrt{Hz}]$ | Current<br>Sensitivity<br>[pA/(µT·mA·V)] | Output Ref Noise $[nV/\sqrt{Hz}]$ | Conditions                                                      |

|-------------|-----------------|---------------------|---------------------------------|------------------------------------------|-----------------------------------|-----------------------------------------------------------------|

| X/Y<br>axis | 1.4             | 1.2                 | 77                              | 28.88                                    | 942.7                             | $V_{dc} = 1 V$ $C_{fb} = 100 fF$ $F_r = 130 kHz$                |

| Z<br>Axis   | 2               | 1.2                 | 332                             | 72.7                                     | 4054.5                            | $V_{dc} = 1V$ $C_{fb} = 100 \text{ fF}$ $F_r = 130 \text{ kHz}$ |

Table 2.1: Sensor's parameters obtained from previously manufactured versions

Figure 2.2: Electric model of the magnetometer for the OTA design

Figure 2.3: Response of the LNA when sensing a magnetic field of B = 1mT with  $I_{LORENTZ}$  = 1mA and  $V_{DC}$  = 1.65V

Figure 2.4: Current provided the sensor due to charge variation when applying the Lorentz Current

### **Required Specifications**

Taking into account the noise levels of the sensor, its operation frequency and the capacitances appearing in the circuit, the LNA specifications are detailed in Table 2.2.

| Specifications                    | Min  | Nom   | Max | Units          |

|-----------------------------------|------|-------|-----|----------------|

| Voltage Supply (V <sub>DD</sub> ) | -    | 3.3   | -   | V              |

| Common-Mode Voltage               | -    | 1.65  | -   | V              |

| Current Consumption               | -    | 200   | -   | uA             |

| Open-Loop Gain (130 kHz)          | 59   | 67    | -   | dB             |

| Phase Margin                      | 60   | 65    | -   | Degrees        |

| Unity Gain Bandwidth (GBW)        |      | -     | -   | MHz            |

| Opamp Load Capacitance            |      | 0.8   |     | pF             |

| Output PSRR+ (300 kHz and below)  |      | -65   | -   | dB             |

| Output PSRR- (300 kHz and below)  |      | -65   | -   | dB             |

| Output CMRR (300 kHz and below)   |      | -86   | -   | dB             |

| Output Swing                      | -    | 1.05  | -   | Vpp            |

| Opamp input referred noise        | _    | -     | 45  | nV/√ <i>Hz</i> |

| Slew Rate (300 kHz and below)     | 1.96 | 20.75 | -   | V/µs           |

Table 2.2: Table of Specs derived from the Sensor characteristics

### 2.2. OTA Topology

### 2.2.1. Folded cascode topology

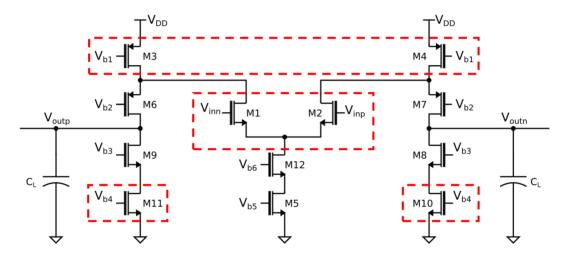

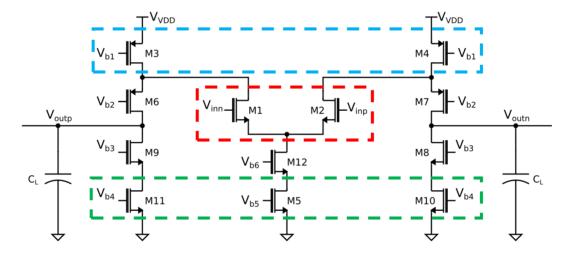

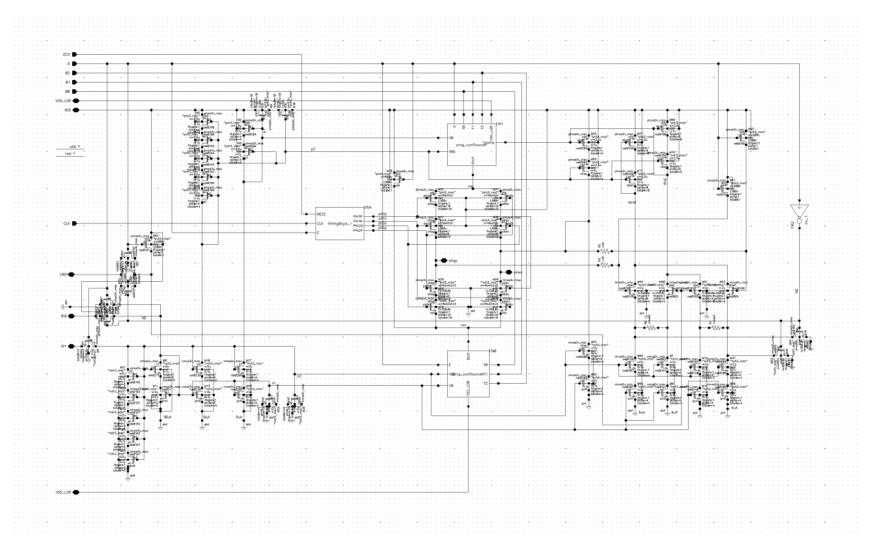

An Operational Transconductance Amplifier based on a folded cascode topology with fully differential input and output is chosen to amplify the response of the magnetometer.

The reasons are mainly the high gain that this topology can offer with a single stage, which reduces the compensation issues present in multi-stages topologies [7]. In addition, the folded cascode topology combined with the use of wide swing cascode current mirrors allows to have a high dynamic range at the output.

Apart of these aspects, the OTA has been designed to offer low noise and a wide GBW response with a reasonable current consumption. In order to reach the specifications, we need to understand which parameters can affect our stability, gain or unity gain bandwidth. For this reason, some expressions obtained from the Small Signal Analysis have been considered to design properly this OTA.

This topology includes a differential pair, two cascode pairs and two pairs of current sources as illustrated in Figure 2.5.

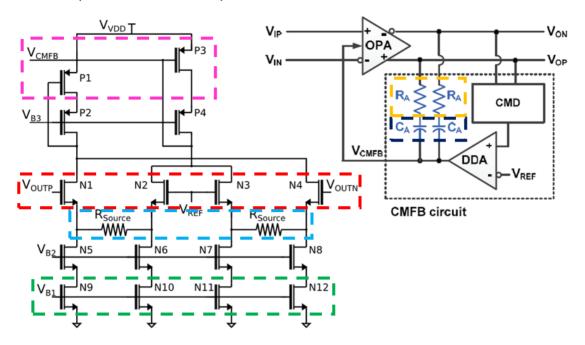

Figure 2.5: Folded Cascode Amplifier Used in the Design

| Differential Folded Cascode Amplifier |                |           |            |            |              |  |

|---------------------------------------|----------------|-----------|------------|------------|--------------|--|

| Instance                              | Туре           | Width[µm] | Length[µm] | Multiplier | Aspect Ratio |  |

| M1                                    | Native NMOS 3V | 3         | 1.2        | 32         | 80           |  |

| M2                                    | Native NMOS 3V | 3         | 1.2        | 32         | 80           |  |

| M5                                    | NMOS 3V        | 3         | 3          | 120        | 120          |  |

| M10                                   | NMOS 3V        | 3         | 3          | 96         | 96           |  |

| M11                                   | NMOS 3V        | 3         | 3          | 96         | 96           |  |

| M8                                    | NMOS 3V        | 3         | 3          | 24         | 24           |  |

| М9                                    | NMOS 3V        | 3         | 3          | 24         | 24           |  |

| М3                                    | PMOS 3V        | 2.2       | 0.8        | 156        | <i>4</i> 29  |  |

| M4                                    | PMOS 3V        | 2.2       | 0.8        | 156        | <i>4</i> 29  |  |

| M6                                    | PMOS 3V        | 2.2       | 0.8        | 24         | 66           |  |

| M7                                    | PMOS 3V        | 2.2       | 0.8        | 24         | 66           |  |

Table 2.3: Transistor sizes for Folded Cascode Amplifier

### 2.2.2. Gain and Unity Gain Frequency

As in any differential amplifier, the differential pair acts as a transconductor, converting a voltage difference at the input in a difference of currents between both branches.

However, since it is desired to have the output as a differential voltage and at the same time high gain, both currents are passed through a device which behaves as an active load (high resistance) AC [8]. This device is the cascoded current source.

$$A_V = g_{m1} \cdot R_{OUT} \tag{2.4}$$

$$R_{OUT} \approx ((r_{DS1}||r_{DS3}) \cdot r_{DS6} \cdot g_{m6})||(r_{DS11} \cdot g_{m9} \cdot r_{DS9})$$

(2.5)

Where  $g_{m1}$  and  $g_{m6}$  are the transconductances of the differential pair and the cascode stages and  $r_{DS1}$  and  $r_{DS6}$  the resistances offered by the differential pair and the cascode respectively [9].  $R_{DS9}$  and  $r_{DS11}$  are the resistances of the NMOS current source and cascode respectively and  $g_{m6}$  is the transconductance of the PMOS cascode stage.

As the cascode results in a large gain, when combined with the load capacitor  $C_L$  it limits the bandwidth of our amplifier and defines the dominant pole of the system.

$$BW = \frac{1}{2\pi R_{OUT} C_L} \tag{2.6}$$

Combining both expressions, and assuming that the non-dominant pole is far enough to be neglected, the Unity Gain Frequency can be obtained [10]:

$$GBW \approx \frac{g_{m1}}{2\pi C_L} \tag{2.7}$$

The conclusion that we could obtain from this expression is that the GBW is set mainly by the load capacitance and the differential pair. Therefore, the sizes of the differential pair and its biasing current will be determinant for the amplifier's GBW and should be the first part to set in the design.

Since the load capacitance will be caused by a buffer stage of 800 fF that drives the chip pads and the desired GBW is 120 MHz, the minimum transconductance offered by the differential pair should be at least  $g_{m1}$ =603.19  $\mu$ A/V.

However, to guarantee this condition even for the worst case corner, a higher transconductance was targeted when sizing the differential pair for the nominal case. Therefore, the final transconductance is set to 708.52  $\mu\text{A/V}$  which leads to a GBW of 136 MHz. The sizes and resulting parameters are indicated in Table 2.4 and Table 2.6, respectively.

| Differential Pair Parameter | Value  | Unit |

|-----------------------------|--------|------|

| <b>G</b> <sub>m1</sub>      | 708.52 | μA/V |

| Width                       | 96     | μm   |

| Length                      | 1.2    | μm   |

| W/L                         | 80     | -    |

| Diff. Pair Current (Iss)    | 100    | μΑ   |

Table 2.4: Size parameters and current required by the differential pair

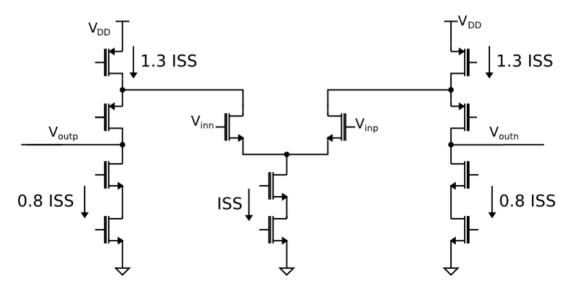

Finally, to size the folded cascode branches, it was intended that the PMOS cascode was as wide as possible in order to have a greater  $g_{m6}$  without increasing the current consumption too much.

When designing a folded cascode with NMOS transistors in the differential pair, it is recommended to set the current sources taking into account the extreme case where the differential pair consumes I<sub>SS</sub> completely from one of the branches.

To leave current still flowing through the folded cascode in this situation, the PMOS are designed to conduct 1.3 times I<sub>SS</sub> which leaves 0.8·I<sub>SS</sub> for the NMOS current source when the differential pair is equilibrated (see Figure 2.6).

On the opposite situation, if the differential pair has  $I_{SS}$  flowing completely at one side, the remaining current would be  $0.3 \cdot I_{SS}$ . Greater current factors could be chosen, however this option also leads to great consumptions.

Figure 2.6: DC current consumption at different parts of the OTA

By setting  $I_{SS}$  = 100  $\mu$ A, the cascode width at 52.8  $\mu$ m at its length at 0.8  $\mu$ m (aspect ratio 66), a  $g_{m6}$  = 543.4 $\mu$ A/V was achieved. With this value, the resulting gain is 74.83dB and the BW turns out to be 25.74 kHz.

Furthermore,  $g_{m6}$  is not only important for the gain. In section 2.2.3, it is explained how  $g_{m6}$  should be also as large as possible in order to enhance the stability of our amplifier. Therefore, increasing  $g_{m6}$  helps the design to reach both the gain and the Phase Margin specifications.

| OTA Parameter           | Value | Unit |

|-------------------------|-------|------|

| I <sub>SS</sub>         | 100   | μΑ   |

| I (PMOS Current Source) | 130   | μΑ   |

| I (NMOS Current Source) | 80    | μΑ   |

| <i>g</i> <sub>m6</sub>  | 543.4 | μA/V |

| Width                   | 52.8  | μm   |

| Length                  | 0.8   | μm   |

| W/L                     | 66    | -    |

Table 2.5: PMOS cascode parameters after setting current

| OTA Parameter | Value | Unit |

|---------------|-------|------|

| Gain at low f | 74.83 | dB   |

| Bandwidth     | 25.74 | kHz  |

| GBW           | 136   | MHz  |

Table 2.6: OTA parameters after sizing the differential pair and the cascodes

Regarding the rest of the parts of the amplifier, since a specific current mirror topology is being used (more details in section 2.2.5), a fixed relation between the PMOS cascode and its current source should be accomplished, so determining the size of the current source is immediate.

Finally, the NMOS branch of the folded cascode was the last part to size in the design. Since it does not take part in the signal path, its size should not be critical for the final GBW or PM. Therefore, only noise considerations have been applied when sizing this part.

### 2.2.3. Stability Analysis

Regarding the stability of our amplifier, a Phase Margin in open loop of at least 60° is required. Assuming that our amplifier is a system with only 2 poles, an approximate expression for the Phase Margin can be obtained (see expression (2.8)).

$$PM = 180^{\circ} - arctg\left(\frac{f_u}{f_{v1}}\right) - arctg\left(\frac{f_u}{f_{v2}}\right) \approx 90^{\circ} - arctg\left(\frac{f_u}{f_{v2}}\right)$$

(2.8)

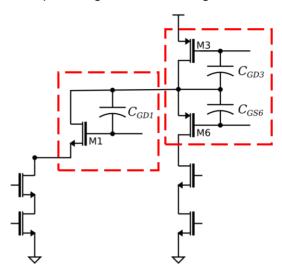

The stability gets better when the distance between the dominant pole and the nearest non dominant one is greater. In our case, the non-dominant pole is located at the drain of the transistors belonging to the differential pair, as shown in expression (2.9).

$$f_{p2} = \frac{g_{m6}}{2\pi C_X} \tag{2.9}$$

Where  $g_{m6}$  is the transconductance of the PMOS cascode, and  $C_X$  is the addition of the parasitic capacitance of the differential pair and the transistors of the PMOS current source and its cascode.

$$C_X = C_{GD1} + C_{GD3} + C_{GS6} (2.10)$$

The non-dominant pole should be located as far as possible from the dominant one to have a better stability. In consequence,  $g_{m6}$  should be large and  $C_X$  as small as possible.

Figure 2.7: Half circuit, with capacitances contributing to the non-dominant pole

Concerning the sizes of the differential pair and the current source, they should be as small as possible to have good stability. In principle, this requirement presents a conflict with the GBW (differential pairs tend to have large widths) and with the noise. As we will see in future chapters, low-noise transistors tend to have large sizes.

In consequence, a trade-off between all 3 specifications should be considered when sizing the differential pair, the PMOS current source and the PMOS cascode.

By fulfilling this trade-off and using the load capacitance to set the dominant pole, the required Phase Margin (PM) is achieved as shown in Table 2.7.

| OTA Parameter            | Value  | Unit    |

|--------------------------|--------|---------|

| <b>G</b> m6              | 543.4  | μA/V    |

| C <sub>GD1</sub>         | 36.51  | fF      |

| $C_{GD3}$                | 137.6  | fF      |

| C <sub>GS6</sub>         | 151    | fF      |

| Expected f <sub>nd</sub> | 266.43 | MHz     |

| PM                       | 62     | Degrees |

Table 2.7: Capacitances considered in the non-dominant pole and PM of the OTA

### 2.2.4. Noise

For the purpose of avoiding a SNR degradation of the signal provided by our sensor, having a low noise at the output was an essential feature to take into account in the design.

Since our amplifier works at 130 kHz, the criteria to minimize the electronic noise was achieving a level below the Brownian noise, which is the thermal contribution introduced by the capacitive sensor.

After setting the limit, which is 40 nV/ $\sqrt{\rm Hz}$ , the next steps consisted in identifying:

- The transistors of the design that have the largest noise contribution.

- Which types of noise present those transistors and how to minimize it.

Generally in folded cascode topologies, the output noise is mostly delivered by the transistors placed in current mirrors and differential pair. The contribution of transistors acting as cascodes is practically negligible [11].

Figure 2.8: Schematic highlighting the main noise contributors

Concerning the amplifier's noise, the most important contributions at 130 kHz are:

- Flicker Noise.

- Thermal Noise.

In the case of flicker noise, enlarging the area of the transistor is enough to reduce it. Increasing either the width or the length is a valid option for any case, as shown in equation (2.11).

$$\overline{V_{N,Out}^2} = \frac{K}{C_{OX}WL} \frac{1}{f} \tag{2.11}$$

Where  $C_{\text{OX}}$  is the gate oxide capacitance of the transistor and K is a constant dependent on device properties [7].

Regarding the thermal contribution, first we should consider the function performed by the transistor. If it is used as an active load (current mirror), it is interesting to have a low transconductance by using a low aspect ratio [10] (see equation (2.12)).

$$\overline{V_{N,out}^2} = 4kT\gamma g_m r_0^2 \tag{2.12}$$

Where k is the Boltzmann constant, T is the temperature,  $\gamma$  is a parameter that depends on the region of the transistor (2/3 if saturation) and  $r_0$  is the output resistance of the transistor.

On the other hand, for transistors used in differential pairs normally it is intended to achieve high transconductance to obtain larger gain. The reason is to minimize the input referred noise of the whole amplifier.

Despite all these considerations were taken into account, some trade-offs had to be reached in order to fulfil other specifications too:

- PMOS size had a critical impact in the stability of the amplifier and sizing them with low aspect ratios caused a worse performance from the stability point of view.

- In the NMOS case, since they are present in the signal path, their influence in the stability was not so important so it was possible to reduce the aspect ratio and setting large sizes.

- Finally, for the differential pair, native transistors were used since they offered a

lower noise level than the normal NMOS counterpart. They were sized as wide as

possible but excessive widths led to an increase of the parasitic capacitance in the

non-dominant pole, which resulted in a worse stability performance too.

| Instance | Output noise level $[nV/\sqrt{Hz}]$ | Contribution of total [%] |

|----------|-------------------------------------|---------------------------|

| M3       | 12.88                               | 26.27                     |

| M4       | 12.88                               | 26.27                     |

| M10      | 5.11                                | 4.15                      |

| M11      | 5.06                                | 4.05                      |

| M1       | 6.4                                 | 6.46                      |

| M2       | 6.4                                 | 6.46                      |

Table 2.8: Flicker and Thermal contribution to the output referred noise of the most important transistors at 130 kHz

From the final sizes of the design, it is expected to have the PMOS current sources as the largest contributors of noise inside our design. When obtaining the noise report of the design (provided in Table 2.8), this suspicion is confirmed indeed. Despite this fact, an input referred noise much lower than the specified one is achieved, as indicated in Table 2.9.

| Noise Parameter      | Value | Unit           |

|----------------------|-------|----------------|

| Input Referred Noise | 9.55  | $nV/\sqrt{Hz}$ |

Table 2.9: Noise level achieved in the design

The result is 4 times lower than the one specified. Apparently one could assume that this OTA is overdesigned from the noise point of view. However, the resulting transistors are sized considering other parameters like stability, gain, unity gain frequency that have resulted in a very low noise level at the end.

### 2.2.5. Low-voltage current mirror

As large output dynamic range was targeted for this application while having at the same time large output resistance in AC, a cascoded current source topology capable of working at low voltages of the output node was required.

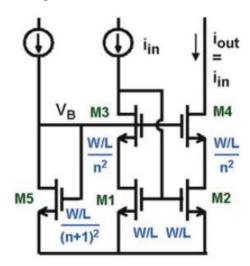

Hence, all current sources of the design have been implemented with the low-voltage topology depicted in the following schematic.

Figure 2.9: Low-Voltage Current Mirror Topology [10].

If proper biasing is applied to the cascode transistors, both M2 and M4 are in saturation only requiring a  $V_{OUT} > V_{OD}|_{M4} + V_{OD}|_{M2}$ , which is good enough for the desired 1  $V_{pp}$  at the output [10] for the 3.3V power supply.

The main drawback of this topology is that the biasing of the cascodes should be generated by another branch, which adds an extra current consumption. Moreover, a relationship between the cascode and the current source should be fulfilled in order to behave as a current mirror [10]:

$$\left|\frac{W}{L}\right|_{Cascode} = \frac{\left|\frac{W}{L}\right|_{CS}}{n^2} \qquad \left|\frac{W}{L}\right|_{Reference} = \frac{\left|\frac{W}{L}\right|_{CS}}{(n+1)^2}$$

(2.13)

In our case, n is 2. Therefore the aspect ratio of the cascodes are:

$$\left|\frac{W}{L}\right|_{Cascode} = \frac{\left|\frac{W}{L}\right|_{CS}}{4} \tag{2.14}$$

About the biasing voltage, it should be high enough to guarantee that the voltage drop across the cascode does not force the current mirror to enter into ohmic region. Therefore, the transistor generating the bias will have a smaller aspect ratio than the cascodes.

Making the same reasoning for the reference cascode, it should be 9 times larger than the transistors present in the current source. Even though this ratio should ensure that both transistors are in saturation, in our case the reference has an aspect ratio 12 times smaller to guarantee this saturation for variability that may occur in the circuit.

$$\left|\frac{W}{L}\right|_{Cascode} = \frac{\left|\frac{W}{L}\right|_{CS}}{12} \tag{2.15}$$

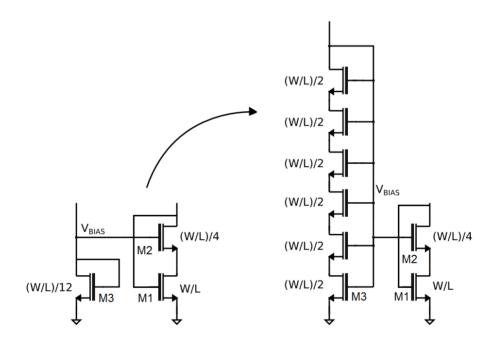

In addition, the biasing transistor was implemented by placing several transistors in series instead of shortening the width. This approach was taken in order to consider the body effect of the cascodes and achieve a better matching of the threshold voltage between the reference and the rest of cascodes.

Figure 2.10: Current mirror and reference for cascode transistors. Instead of lowering the aspect ratio by using narrower transistors, several transistors in series generate the cascode bias.

| Biasing circuit for Current Mirrors and Cascodes |          |                                                   |   |     |                          |  |  |

|--------------------------------------------------|----------|---------------------------------------------------|---|-----|--------------------------|--|--|

| Instance                                         | Туре     | Type Width[μm] Length μm] Multiplier Aspect Ratio |   |     |                          |  |  |

| Biasing for<br>Current                           | NMOS3V   | 3                                                 | 3 | 12  | 12                       |  |  |

| Mirror (M1)                                      | 74476667 | Ŭ                                                 | 0 | , 2 | ,,_                      |  |  |

| Cascode<br>(M2)                                  | NMOS3V   | 3                                                 | 3 | 3   | 3                        |  |  |

| Biasing for<br>Cascodes<br>(M3)                  | NMOS3V   | 3                                                 | 3 | 6   | 1(6parallel/6<br>series) |  |  |

Table 2.10: Sizes for the transistors of the biasing circuit for all NMOS current mirrors

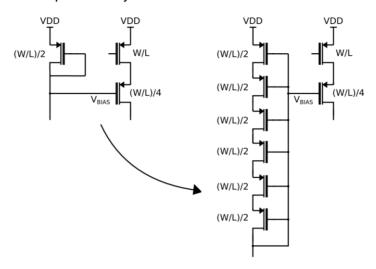

Regarding the PMOS transistors, the biasing voltage is generated in a similar way. The ratio between the cascodes and the current sources is the same. The biasing voltage of the current mirrors is provided by the CMFB.

Figure 2.11: PMOS transistors in series generating Vbias for all PMOS cascodes

| Biasing circuit for Current Mirrors and Cascodes |        |           |            |            |                        |

|--------------------------------------------------|--------|-----------|------------|------------|------------------------|

| Instance                                         | Type   | Width[µm] | Length[µm] | Multiplier | Aspect Ratio           |

| Biasing for                                      | PMOS3V | 2.2       | 0.8        | 4          | 0.6(4parallel/6series) |

| Cascodes                                         |        |           |            |            | •                      |

Table 2.11: Sizes for the transistors of the biasing circuit for all PMOS cascodes

### 2.3. Common Mode Feedback

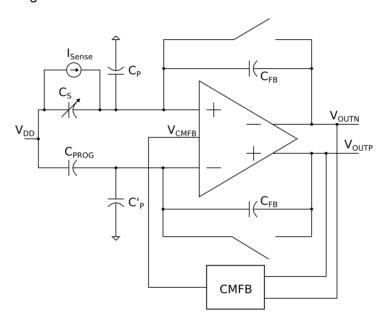

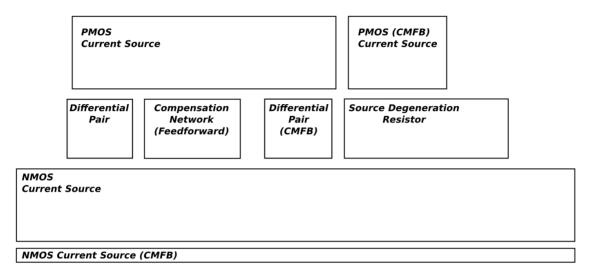

Since the output of the LNA is differential, a Common Mode Feedback Amplifier is required in order to fix the DC voltage at both outputs.

Figure 2.12: Block Diagram of a CMFB

Usually, the common mode of the output voltage is controlled using a negative feedback system that:

- Compares the common mode voltage of the outputs  $V_{\text{CM}}$  with a reference value  $V_{\text{RFF}}$ .

- The difference generates a voltage, V<sub>CMFB</sub>, which is returned to the main differential amplifier in order to adjust V<sub>CM</sub> and make it equal to V<sub>REF</sub> [12].

When returning  $V_{\text{CMFB}}$ , it is usually applied to an element of the biasing network in the main amplifier. In our case, the PMOS current sources, which act like a common source amplifier.

Both the CMFB amplifier and the common source provide gain to the negative feedback. The total gain of the loop is known as the open loop gain  $\beta$  and the higher it is, the lesser the error we have between  $V_{CM}$  and  $V_{REF}$ .

$$\beta = A_{DiffAmp} A_{CommonSource} \tag{2.16}$$

For our purposes, common mode regulation is required in order to have the amplifier working properly, but it is not necessary to achieve a very low error level since the measurement is made at AC to avoid the effects of offset and flicker noise.

### 2.3.1. Differential Amplifier

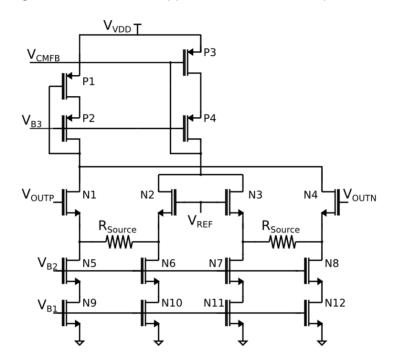

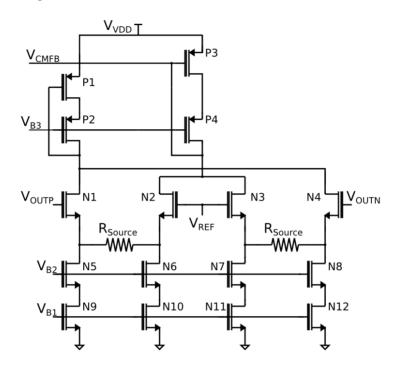

For our design, a Differential Amplifier is chosen to generate  $V_{\text{CMFB}}$  from the outputs of the main amplifier [12]. About this topology:

- The differential pairs perform the comparison between the reference voltage and the average of the outputs.

- The PMOS current mirrors convert the difference of currents in V<sub>CMFB</sub>.

- Source degeneration has been applied to the differential pairs.

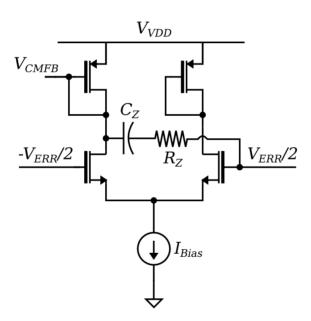

Figure 2.13: CMFB implemented with a Differential Amplifier

| CMFB's Differential Amplifier |                |           |            |            |              |

|-------------------------------|----------------|-----------|------------|------------|--------------|

| Instance                      | Туре           | Width[µm] | Length[µm] | Multiplier | Aspect Ratio |

| M1                            | Native NMOS 3V | 2         | 1.2        | 4          | 6.66         |

| <i>M</i> 2                    | Native NMOS 3V | 2         | 1.2        | 4          | 6.66         |

| <i>M</i> 3                    | Native NMOS 3V | 2         | 1.2        | 4          | 6.66         |

| M4                            | Native NMOS 3V | 2         | 1.2        | 4          | 6.66         |

| M5                            | NMOS 3V        | 3         | 3          | 4          | 4            |

| <i>M</i> 6                    | NMOS 3V        | 3         | 3          | 4          | 4            |

| <i>M7</i>                     | NMOS 3V        | 3         | 3          | 4          | 4            |

| M8                            | NMOS 3V        | 3         | 3          | 4          | 4            |

| M9                            | NMOS 3V        | 3         | 3          | 16         | 16           |

| M10                           | NMOS 3V        | 3         | 3          | 16         | 16           |

| M11                           | NMOS 3V        | 3         | 3          | 16         | 16           |

| M12                           | NMOS 3V        | 3         | 3          | 16         | 16           |

| P2                            | PMOS 3V        | 2.2       | 1          | 8          | 17.6         |

| P4                            | PMOS 3V        | 2.2       | 1          | 8          | 17.6         |

| P1                            | PMOS 3V        | 2.2       | 1          | 32         | 70.4         |

| P3                            | PMOS 3V        | 2.2       | 1          | 32         | 70.4         |

Table 2.12: Transistor sizes for Differential Amplifier used in CMFB

The main advantage of this topology is that large resistors, used sometimes to obtain the common-mode voltage, are avoided, since the differential pair is able to provide a measure for the average voltage and at the same time it provides a satisfactory accuracy depending on the gain of the Common Mode Loop.

On the other hand, the limited input range and nonlinearity of the differential pairs makes this topology suitable only for circuits with small voltage swing [12].

Because of the design's requirement of output dynamic range around 1  $V_{pp}$  and avoiding large resistors was a desirable feature, solving this range limitation was necessary. The techniques applied to enhance both characteristics will be explained in detail in section 2.3.4.

### 2.3.2. CMFB Loop Response

As shown in equation (2.16), the loop gain is provided by the CMFB amplifier and the PMOS current sources.

Therefore, the total open loop gain can be obtained by analysing each stage individually. Concerning the CMFB amplifier, its response can be approximated as a single pole system produced by the gate source capacitance of the PMOS current sources.

$$A_{CMFBAmp} = \frac{1}{2} \frac{g_{mPair}}{g_{mp}} \frac{1}{(1 + \frac{s}{g_{mp}/(2C_{GS})})}$$

(2.17)

Whereas in the common source amplifier, we should take into account 2 poles, one caused by the load capacitance and the other caused by the parasitic capacitances of the differential pair, the current source and the cascode of the main amplifier.

$$A_{CommonSource} = g_{CS}R_{OUT} \frac{1}{\left(1 + \frac{s}{1/(R_{OUT}C_L)}\right)\left(1 + \frac{s}{g_{m6}/C_X}\right)}$$

$$V_{CM}$$

Figure 2.14: Current Sources acting as a Common Source Amplifier for V<sub>CMFB</sub>

Joining both expressions the loop gain would result in a function with 3 poles as in equation (2.19).

$$\beta = \frac{\frac{1}{2}g_{mPair}NR_{OUT}}{\left(1 + \frac{s}{1/(R_{OUT}C_L)}\right)\left(1 + \frac{s}{g_{mp}/(2C_{GS})}\right)\left(1 + \frac{s}{g_{m6}/C_X}\right)}$$

(2.19)

Where N is the relationship between the aspect ratios in the PMOS transistors of the main amplifier and the PMOS of the CMFB amplifier and  $g_{mpair}$  is the transconductance of the differential pair used in the CMFB amplifier.

From here, the gain, GBW and the poles to consider for the stability of the feedback can be obtained.

$$Gain_{\beta} = \left(\frac{g_{mPair}}{g_{mp}}\right) (g_{mCS}R_{OUT}) = \frac{1}{2} g_{mPair} NR_{OUT}$$

(2.20)

$$GBW_{\beta} = \frac{1}{2\pi R_{OUT}C_L} \left(\frac{1}{2}g_{mPair}NR_{OUT}\right) = \frac{g_{mPair}N}{2\pi C_L}$$

(2.21)

$$f_{p1} = \frac{1}{2\pi R_{OUT}C_L}$$

$f_{p2} = \frac{g_{mp}}{4\pi C_{GS}}$   $f_{p3} = \frac{g_{m6}}{2\pi C_X}$  (2.22)

| Loop Parameter                               | Value | Unit       |

|----------------------------------------------|-------|------------|

| <b>G</b> <sub>mp</sub>                       | 301   | μA/V       |

| G <sub>mp</sub> C <sub>GS</sub>              | 860.7 | f <b>F</b> |

| $f_{p2}$                                     | 27.83 | MHz        |

| <b>G</b> <sub>m6</sub>                       | 501   | μA/V       |

| <i>g</i> <sub>m6</sub> <i>C</i> <sub>X</sub> | 325.1 | fF         |

| $f_{p3}$                                     | 264   | MHz        |

Table 2.13: Expected locations of the second and third pole and parameters values used to estimate them

| Loop Parameter  | Value | Unit |

|-----------------|-------|------|

| β Gain at low f | 58.42 | dB   |

| β GBW           | 18.26 | MHz  |

| $f_{p1}$        | 21.90 | kHz  |

Table 2.14: Expected parameters of β

The dominant pole turns out to be the one caused by the load capacitor as in the main amplifier. However, due to the presence of 3 poles, it is possible to have an unstable loop. Hence a compensation network may be required to deal with them.

Apart from the stability issues, due to both the large  $C_L$  and the use of linearization techniques (explained in chapter 2.3.3), the GBW of the common mode loop is reduced drastically. Therefore, it is expected to have a  $GBW_{CM}$  below the differential  $GBW_{Diff}$ . Despite having  $GBW_{CM} > GBW_{Diff}$  is usually a requirement for CMFB circuits, depending on the application it is possible to keep it below. Indeed, if it is not expected to have fast variations of the common mode voltage, this specification can be relaxed [10].

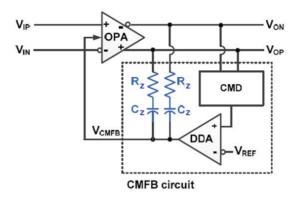

### 2.3.3. Feed Forward Stabilization (Nulling Resistor)

To ensure stability for the Loop Response, a compensation network has been added to the CMFB amplifier (see Figure 2.15). The main reason to use the feed forward compensation is that allows to enhance the stability of the loop without reducing the unity gain bandwidth drastically [13].

Figure 2.15: Block Diagram of a CMFB using feed forward stabilization [13].

Before using this compensation technique, the stability enhancement was only possible by reducing the GBW either by increasing  $C_L$  or using a bigger degeneration resistor  $R_S$ . With  $C_L$ =0.8 pF and  $R_S$ =57 k $\Omega$  a PM = 48° and a GBW around 12.5 MHz was achieved whereas using the feed forward stabilization allowed us to get a much better Phase Margin and Gain Bandwidth (PM = 84.54°, GBW = 22 MHz) with the same load and degeneration.

Figure 2.16: Bode plot of the CMFB Loop before (blue) and after using compensation (orange)

As depicted in Figure 2.16, the network causes a noticeable stability improvement with the PM going from 48° to 85°.

The network consists of a capacitor  $C_Z$ , which moves the dominant pole at a lower frequency and migrates the second pole at a higher frequency [13], and a Nulling Resistor  $R_Z$ , that includes an additional zero at higher frequencies, reducing the effect of the non-dominant pole and allowing an improvement of the Phase Margin of the Loop.

In our case, the second pole that affects our loop stability is the pole caused by the gate of the PMOS current sources. Therefore, the zero should be near this pole, which was located around 27 MHz.

When applied to the CMFB, its response can be approximated with expression (2.23).

$$\frac{v_{cmfb}}{v_{cm}} \approx \frac{1}{2} \frac{g_{mn}}{g_{mp}} \frac{1 + \left(R_Z + \frac{1}{g_{mn}}\right) C_z s}{\left(1 + \frac{s}{g_{mp}/(2C_{GS} + 2C_X)}\right) \left(1 + \frac{s}{1/(R_Z C_Z)}\right)}$$

(2.23)

Regarding the case without compensation, the network introduces an additional zero and a pole. Their locations can be estimated with equations (2.24) and (2.25). Their derivation is explained in section 5.

$$f_{Zero} = \frac{1}{2\pi \left(R_Z + \frac{1}{g_{mn}}\right)C_Z} \tag{2.24}$$

$$f_{Pole} = \frac{1}{2\pi R_Z C_Z} \tag{2.25}$$

Where  $g_{mn}$  is the transconductance of the differential pair used to compare the common mode voltage with the reference.

The final network characteristics are provided in table Table 2.15 as well as the final specifications for the CMFB loop after compensation.

| Network Element                 | Value  | Units      |

|---------------------------------|--------|------------|

| Network Capacitance Cz          | 200    | f <i>F</i> |

| Nulling Resistor R <sub>z</sub> | 5.36   | kΩ         |

| Effective g <sub>mn</sub>       | 29.85  | μA/V       |

| Expected Zero Location          | 20.19  | MHz        |

| Expected Pole Location          | 148.46 | MHz        |

Table 2.15: Characteristics of the compensation network

| CMFB Parameter         | Value | Unit    |

|------------------------|-------|---------|

| Loop Gain at (130 kHz) | 42.95 | dB      |

| Loop GBW               | 22.24 | MHz     |

| Loop PM                | 84.54 | Degrees |

| Consumption            | 53.3  | μΑ      |

Table 2.16: Main Parameters of the CMFB Response in the Nominal Corner after compensation

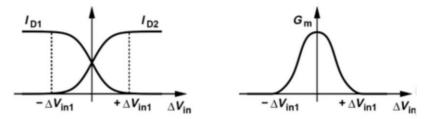

### 2.3.4. Source Degeneration (CMFB dynamic range enhancement)

As mentioned in previous sections, this topology has a problem with the input dynamic range and the linearity offered by the differential pair when applying large voltage swings.

Figure 2.17: CMFB distorts the Output Waveform

Both problems can be minimized:

- By reducing the aspect ratios (W/L) of the differential pair, which reduces the amplifier's gain.

- Increasing the current flowing through them [12], which causes a large consumption of the circuit.

The input range extension caused by the previous options can be calculated with equation (2.26) [8]. As long as the differential peak to peak voltage of the output is inside this range, the behaviour of the differential pair can be considered linear and the CMFB loop controls properly the common mode.

$$\Delta V_{INmax} = \sqrt{\frac{2I_{SS}}{\mu_n C_{OX}(W/L)}}$$

(2.26)

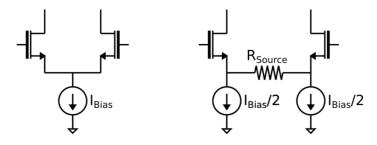

In our design an alternative approach was taken to resolve this issue without increasing the current consumption of the amplifier. This alternative consists in using a source degeneration in the amplifier (see Figure 2.18).

Figure 2.18: A conventional NMOS differential pair and the one with source degeneration

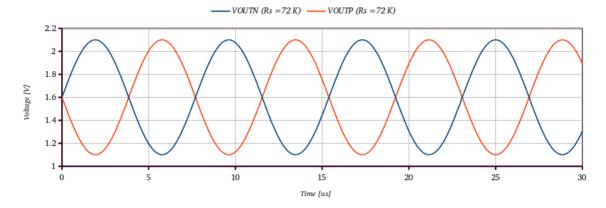

Figure 2.19: Output Waveform after adding source degeneration

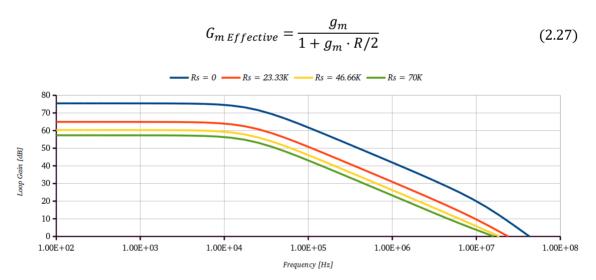

Adding a source degeneration degrades the gain of the amplifier and the GBW of the CMFB loop, but provides extra linearization in case that the previous approaches are not enough [14]. This gain degradation occurs due to the loss of transconductance in the differential pair introduced by the resistor, which can be modelled with the expression provided in equation (2.27). In consequence, a trade-off when choosing the resistor value should be reached.

Figure 2.20: Degradation of both Gain and GBW of the CMFB Loop when the source resistor is higher.

The resistance value was swept from 10k to 100k

When including the source degeneration, the maximum input range to work inside the linear region can be estimated from equation (2.28). The steps to obtain it are explained in chapter 6.

$$\Delta V_{INmax} = \sqrt{\frac{2I_{SS}}{\beta}} + \frac{R_S I_{SS}}{2} \tag{2.28}$$

From the equation, one can conclude with that the source degeneration, both the resistance and the bias current have a greater impact in the improvement of the input range than in the previous case.

| Network Element       | Value | Units |

|-----------------------|-------|-------|

| Resistor              | 57    | kΩ    |

| Expected Gm Effective | 29.85 | μA/V  |

Table 2.17: Resistor value to implement source degeneration

The effect over the currents in the differential pair is depicted in Figure 2.21. The larger the degenerating resistance, the wider the linear region of the differential pair.

Figure 2.21: Differential Pair Current with linearized response due to degeneration

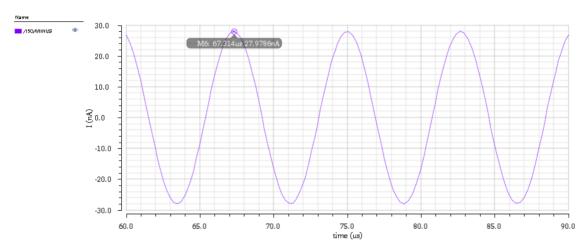

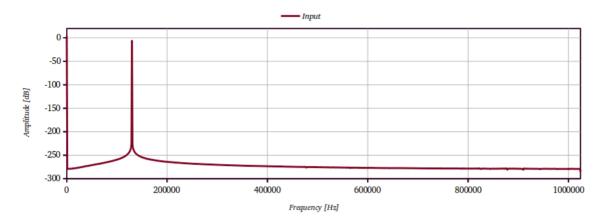

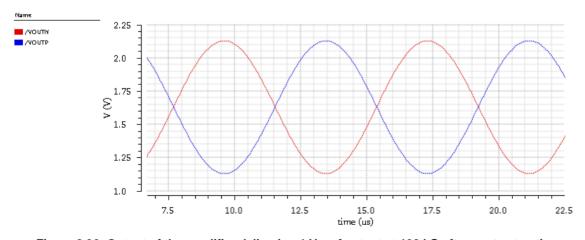

To characterize better the linearity improvement, a DFT of the amplifier output working as a feedback amplifier with gain 1 was made. At the input, a pure tone of 1  $V_{pp}$  at 130 kHz was set.

Despite the amplifier is working with differential signals, from the DFT point of view the signals are evaluated as single ended, due to the distortion caused by the CMFB loop is only noticeable if the output is evaluated single ended or from the common mode perspective.

Figure 2.22 shows the DFT of the input signal, which a single tone at 130 kHz (our fundamental frequency).

Figure 2.22: FFT of Input Signal (Single Ended Component). Fundamental tone at 130 kHz

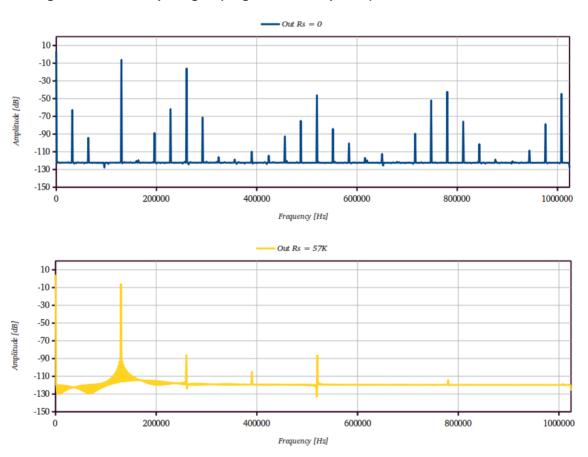

Figure 2.23: FFT of the amplifier output (single ended) for values of  $R_{Source}~0~k\Omega$  and 57  $k\Omega$

As it can be seen from the result, some harmonic tones appear (Figure 2.23) and when the resistor value is increased both the number of harmonic components and their amplitudes are reduced.

To quantify the improvement in linearity, the Spurious Free Dynamic Range was measured. Its definition is provided in equation (2.29).

$$SFDR = Amplitude_{Fundamental}(dB) - Amplitude_{Largest\ Spur}(dB)$$

(2.29)

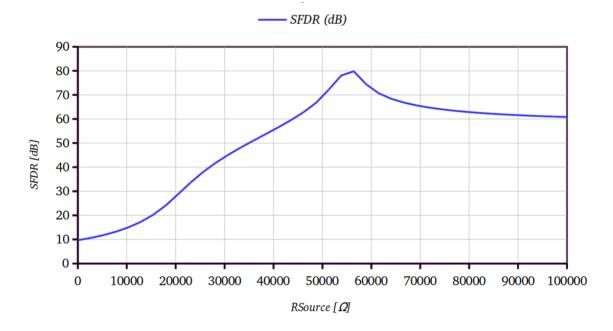

When calculating for different values of the source degeneration, an optimal SFDR of 80dB is found when  $R_S = 57~k\Omega$ . For upper values no further linearity improvement is obtained. For this reason this value is chosen to implement the source degeneration.

| Source Res [kΩ]         | SFDR [dB] |

|-------------------------|-----------|

| $R_S = 0$               | 9.68      |

| $R_{\rm S} = 35k\Omega$ | 50.05     |

| $R_{\rm S} = 57k\Omega$ | 79.79     |

Table 2.18: SFDR achieved with different R<sub>source</sub>

Figure 2.24: SFDR obtained as a function of the R<sub>Source</sub>

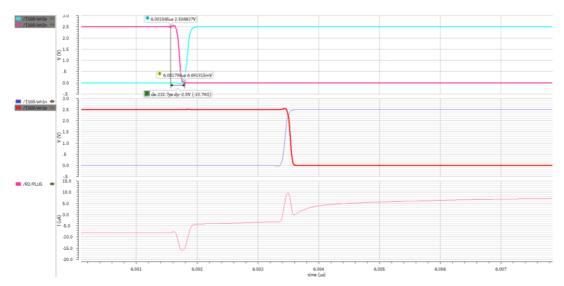

## 2.4. OTA Characteristics after Design

After the design, some of the general features are:

- Input referred noise below 11 nV/Hz.

- GBW larger than 120 MHz.

- Phase Margin of 62°.

- DC Open Loop Gain of 74.83 dB (60 dB at 130 kHz).

- Consumption of 320 µA when operating.

- Output Dynamic Range of 1.05 V<sub>pp</sub>.

- IP activation controlled by an Enable Pin.

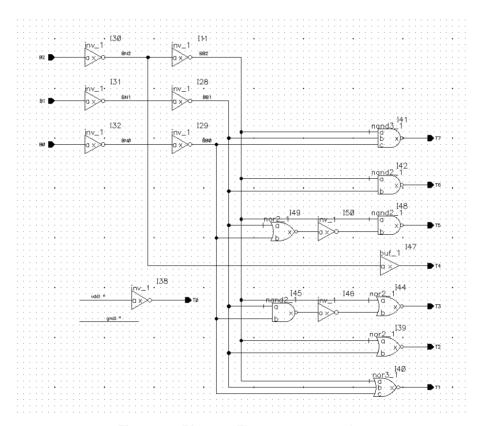

#### **General Enable Pin**

The designed OTA includes the possibility of disabling the amplifier. To do so, an Enable Pin E is provided. If E = '1', the OTA is operating whereas in the opposite case, the amplifier is shutoff.

When the amplifier is disabled, all the nodes of the circuit are driven to a fixed voltage ( $V_{DD}$  or GND). Therefore the current consumption of the circuit when disabled is practically null. However, it is not zero due to leakage and subthreshold currents that transistors offer even when they are supposed to be shutoff.

Figure 2.25: Amplifier's gain and phase response vs frequency

| PIN    | DESCRIPTION                  | Expected<br>Range<br>Value | SYMBOL                                |

|--------|------------------------------|----------------------------|---------------------------------------|

| VDD    | Supply Voltage               | 3.3V                       |                                       |

| VSS    | Ground                       | OV                         |                                       |

| E      | General Enable               | 0V – 3.3V                  |                                       |

| VINP   | Positive Input               | 1.55V –                    | [@instanceName]                       |

| VIIVE  | FOSILIVE ITIPUL              | 1.75V                      | Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z |

| VINN   | Negative Input               | 1.55V –                    |                                       |

| VIIVIV | rvegative iriput             | 1.75V                      | [@partName]                           |

| IZP1   | Current Reference 1          | 10uA                       | VINN VINN                             |

| IZP0   | Current Reference 0          | 10uA                       |                                       |

| VREF   | Ref Voltage for CMFB         | 1.65V                      | VINP                                  |

| VOUTP  | Positivo Output              | 1.15V –                    |                                       |

| VOOTP  | Positive Output              | 2.15V                      | VCM VCM                               |

| VOUTN  | Positive Output              | 1.15V –                    |                                       |

| VOOTIV | ι υδιίίν <del>ο</del> Ομίμαι | 2.15V                      | •                                     |

Table 2.19: Pinnout of the OTA

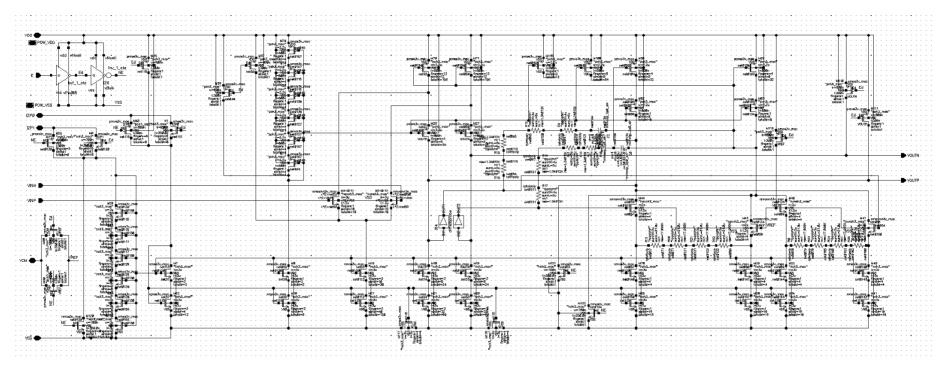

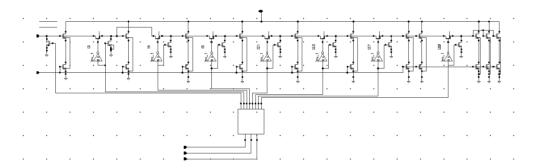

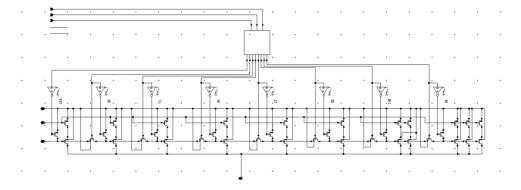

Figure 2.26: Complete schematic of the OTA

| PARAMETER        | CONDITIONS              | UNITS   | MIN          | TYP    | MAX    | COMMENTS                                                                                           |

|------------------|-------------------------|---------|--------------|--------|--------|----------------------------------------------------------------------------------------------------|

| Voltage Supply   |                         | V       |              | 3.3    |        |                                                                                                    |

| Ref Bias Current |                         | иA      |              | 10,00  |        |                                                                                                    |

| Current          | E = '1', OTA<br>Enabled | иA      | 299          | 307    | 315.7  | Simulated at T=[-25°C, 27°C,<br>75°C] for corners ff, ss, fs, sf and<br>100 Montecarlo Iterations. |

| Consumption      | E = '0', OTA Disabled   | pΑ      | 128.3        | 136    | 154.8  | Simulated at T=[-25°C, 27°C, 75°C] for corners ff, ss, fs, sf and 100 Montecarlo Iterations.       |

| Load Capacitor   |                         | pF      |              | 0.8    |        |                                                                                                    |

| GBW              |                         | MHz     | 119.6        | 135.5  | 150.8  | Simulated at T=[-25°C, 27°C, 75°C] for corners ff, ss, fs, sf and 100 Montecarlo Iterations.       |

| Gain_130k        |                         | dB      | 59.77        | 60.76  | 61.78  | Simulated at T=[-25°C, 27°C, 75°C] for corners ff, ss, fs, sf and 100 Montecarlo Iterations.       |

| PM               |                         | Degrees | 61.73        | 62.75  | 63.65  | Simulated at T=[-25°C, 27°C, 75°C] for corners ff, ss, fs, sf and 100 Montecarlo Iterations.       |

| InputNoise130k   |                         | nV√Hz   | 8.572        | 9.652  | 10.87  | Simulated at T=[-25°C, 27°C, 75°C] for corners ff, ss, fs, sf and 100 Montecarlo Iterations.       |

| CMRR_300K        |                         | dB      | 101.5        | 113.7  | 135.2  | Simulated at T=[-25°C, 27°C, 75°C] for corners ff, ss, fs, sf and 100 Montecarlo Iterations.       |

| PSRR+out_300K    |                         | dB      | -26.09       | -28.69 | -32.9  | Simulated at T=[-25°C, 27°C, 75°C] for corners ff, ss, fs, sf and 100 Montecarlo Iterations.       |

| PSRR-out_300K    |                         | dB      | -47.07       | -58.79 | -80.12 | Simulated at T=[-25°C, 27°C, 75°C] for corners ff, ss, fs, sf and 100 Montecarlo Iterations.       |

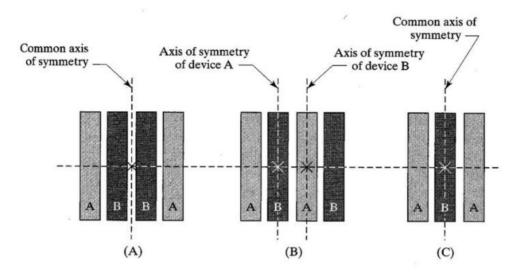

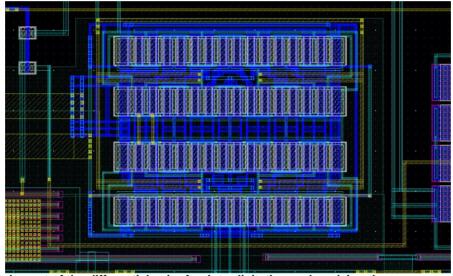

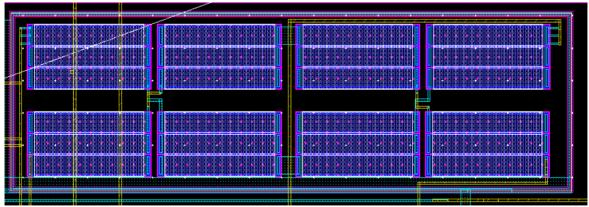

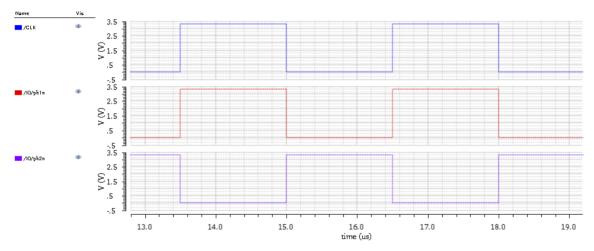

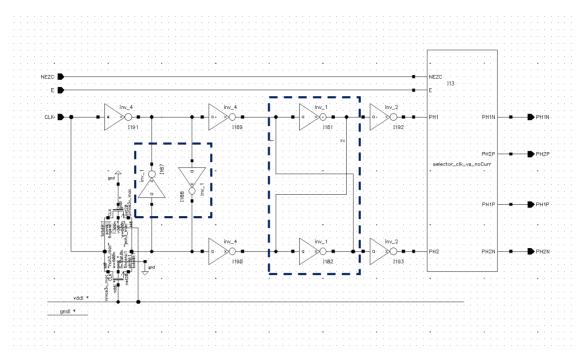

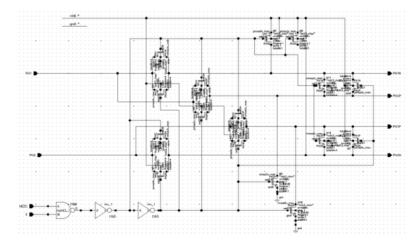

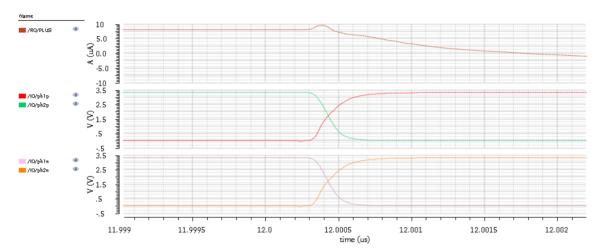

| Offset           |                         | mV      | 15.16E-<br>3 | 1.041  | 4.494  | Simulated at T=[-25°C, 27°C, 75°C] for corners ff, ss, fs, sf and 100 Montecarlo Iterations.       |