## Accelerating Scientific Applications on GPUs

Pau Farré Gonzalez

A thesis submitted in partial fulfilment for the degree of Master in Innovation and Research in Informatics High Performance Computing

in the

Facultat dínformàtica de Barcelona (FIB) Universitat Politècnica de Catalunya (UPC) - BarcelonaTech

Director: Daniel Jiménez Gonzalez Departament d'Arquitectura de Computadors (DAC)

July 4, 2016

# Contents

| Li | st of l | Figures                                   | 5  |

|----|---------|-------------------------------------------|----|

| Li | st of ] | Tables                                    | 7  |

| 1  | Intr    | oduction                                  | 9  |

|    | 1.1     | Document Organization                     | 10 |

| 2  | GPU     | U architecture and CUDA Programming Model | 11 |

|    | 2.1     | GPU architecture                          | 11 |

|    |         | 2.1.1 Memory hierarchy                    | 13 |

|    | 2.2     | Why CUDA                                  | 13 |

|    | 2.3     | The CUDA Programming Model                | 14 |

|    |         | 2.3.1 Kernels                             | 16 |

|    |         | 2.3.2 Thread hierarchy                    | 16 |

|    |         | 2.3.3 CUDA Memory Types                   | 16 |

| 3  | Exp     | erimental Setup and Methodology           | 19 |

| 4  | WA]     | RIS-Transport                             | 23 |

|    | 4.1     | Introduction                              | 23 |

|    | 4.2     | Application Structure                     | 24 |

|    | 4.3     | The WARIS Framework                       | 24 |

|    |         | 4.3.1 The stencil computation             | 25 |

|    |         | 4.3.2 Parallel stencil decomposition      | 26 |

|    | 4.4     | Initial profiling                         | 28 |

|    | 4.5     | The Advection Diffussion Reaction         | 29 |

|    | 4.6     | CUDA Implementation                       | 30 |

|    |         | 4.6.1 ADR Kernel                          | 31 |

|    |         | 4.6.2 Vsettling Kernel                    | 33 |

|    |         | 4.6.3 Other Kernels                       | 33 |

|    | 4.7     | Results                                   | 33 |

|    |         | 4.7.1 Final profiling with nvprof         | 33 |

|    |        | 4.7.2 CPU vs GPU Implementation                         | 35 |

|----|--------|---------------------------------------------------------|----|

| 5  | PEL    | E: Protein Energy Landscape Exploration                 | 39 |

|    | 5.1    | Introduction                                            | 39 |

|    | 5.2    | Application Structure                                   | 40 |

|    |        | 5.2.1 Local Perturbation                                | 40 |

|    |        | 5.2.2 Side-Chain Sampling                               | 41 |

|    |        | 5.2.3 Metropolis Acceptance Test                        | 41 |

|    | 5.3    | PELE Energy formula                                     | 41 |

|    | 5.4    | Initial Profiling                                       | 43 |

|    | 5.5    | CUDA Implementation                                     | 44 |

|    |        | 5.5.1 Non-bonding Energy                                | 44 |

|    |        | 5.5.2 Update Alphas                                     | 48 |

|    | 5.6    | Improving GPU programmability using CUDA Unified Memory | 50 |

|    |        | 5.6.1 Semi-automatic Memory Manager                     | 52 |

|    | 5.7    | Results                                                 | 54 |

|    |        | 5.7.1 GPU Accelerated Parts                             | 55 |

|    |        | 5.7.2 Global Results                                    | 57 |

| 6  | Con    | clusions & Future Work                                  | 61 |

|    | 6.1    | Conclusions                                             | 61 |

|    | 6.2    | Future Work                                             | 62 |

| Bi | bliogı | raphy                                                   | 63 |

| A  | Арр    | endix                                                   | 65 |

|    | A.1    | WARIS-Transport Governing Equations                     | 65 |

# **List of Figures**

| 2.1  | Pascal architecture [1].                                                                   | 11 |

|------|--------------------------------------------------------------------------------------------|----|

| 2.2  | SM in Pascal architecture [2]                                                              | 12 |

| 2.3  | Schematic GPU Memory hierarchy.                                                            | 14 |

| 2.4  | Automatic scalability [3]                                                                  | 15 |

| 2.5  | Thread hierarchy [3]                                                                       | 16 |

| 3.1  | Minotauro K80 node configuration.                                                          | 20 |

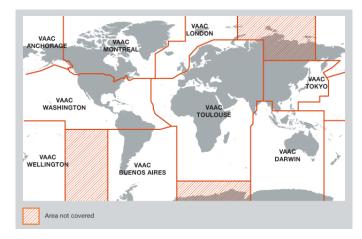

| 4.1  | Volcanic Ash Advisory Centers [4].                                                         | 23 |

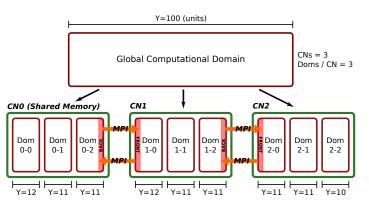

| 4.2  | WARIS computational domain distribution with MPI+pthreads [5]. (CN= Computational Node)    | 24 |

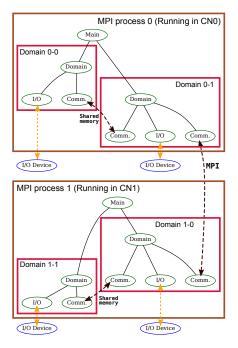

| 4.3  | WARIS communication between nodes [5]                                                      | 25 |

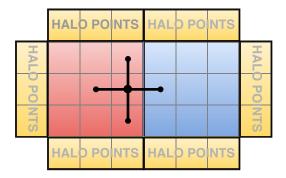

| 4.4  | A 2D 5p-stencil computation.                                                               | 26 |

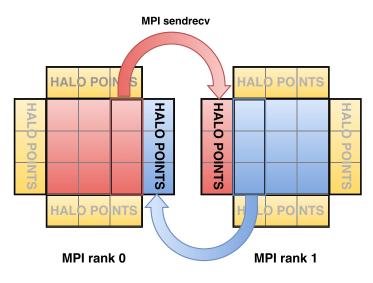

| 4.5  | Halo exchange between MPI ranks                                                            | 26 |

| 4.6  | <i>C</i> 13-p stencil                                                                      | 29 |

| 4.7  | U/V/W 12-p stencil                                                                         | 29 |

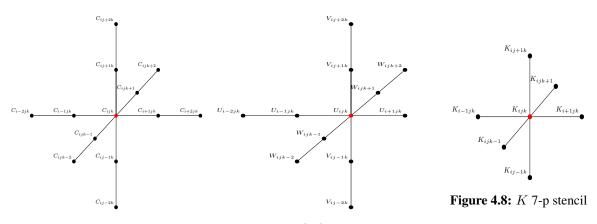

| 4.8  | $K$ 7-p stencil $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                               | 29 |

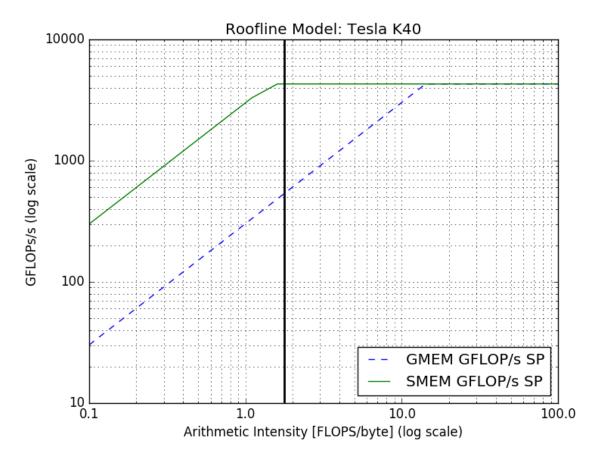

| 4.9  | Roofline Model of NVIDIA Tesla K40 with WARIS-Transport                                    | 30 |

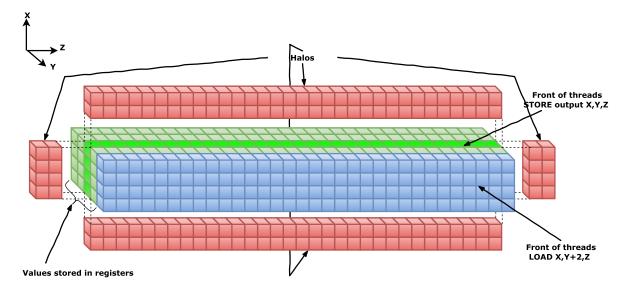

| 4.10 | ADR Kernel: Thread block with front of threads that read from gmem and store in registers. | 32 |

| 4.11 | ADR Kernel: Example of Thread $(i, j)$ computing output point $C_{x,y,z}$ .                | 32 |

| 4.12 | WARIS-Transport Strong Scalability for MPI+AVX (1 MPI rank/core) and MPI+OpenMP+AVX        |    |

|      | (1 MPI rank/node, 1 thread/core) implementations in MareNostrum. Caulle-0.05-8bin dataset  |    |

|      | (601x601x64 x 8)                                                                           | 35 |

| 4.13 | WARIS-Transport Strong Scalability for MPI+CUDA (1 MPI rank/GPU) implementation in         |    |

|      | Hulk and Minotauro. Caulle-0.05-8bin dataset (601x601x64 x 8).                             | 37 |

| 5.1  | Timescales of typical protein motions [6].                                                 | 39 |

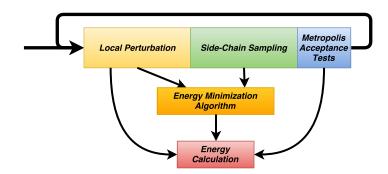

| 5.2  | PELE algorithm for one Monte Carlo step                                                    | 40 |

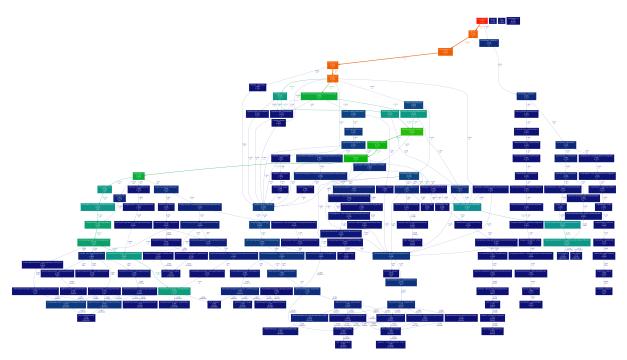

| 5.3  | Gprof Callgraph (O3)                                                                       | 43 |

| 5.4  | PELE Array of Structures(AOS)                                                              | 45 |

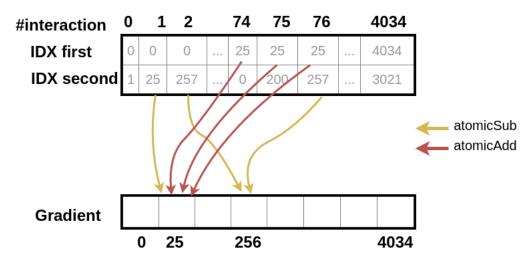

| 5.5  | Gradient update with atomics                                                               | 47 |

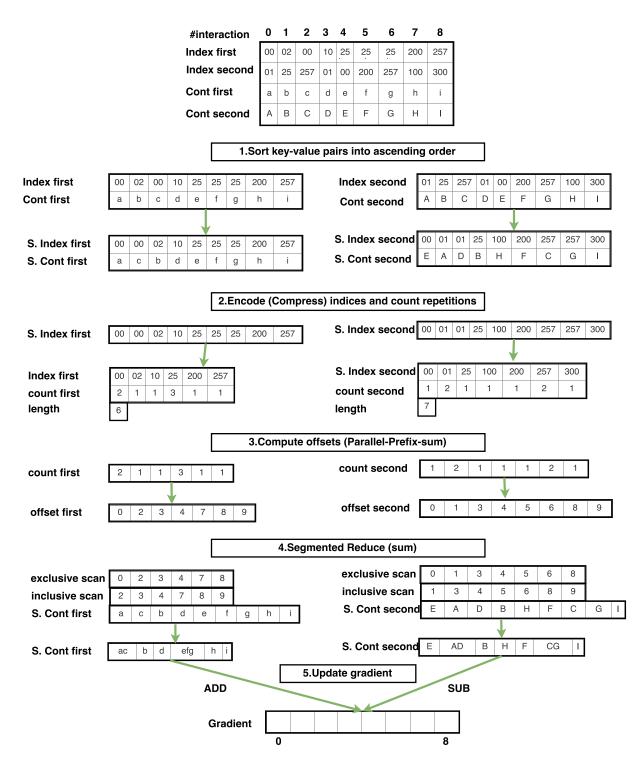

| 5.6  | Gradient update without atomics                                                            | 49 |

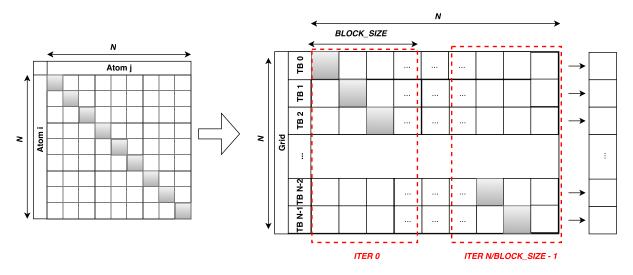

| 5.7  | Update Alphas Kernel 1 - $O(n^2)$ iteration space distribution with CUDA                   | 51 |

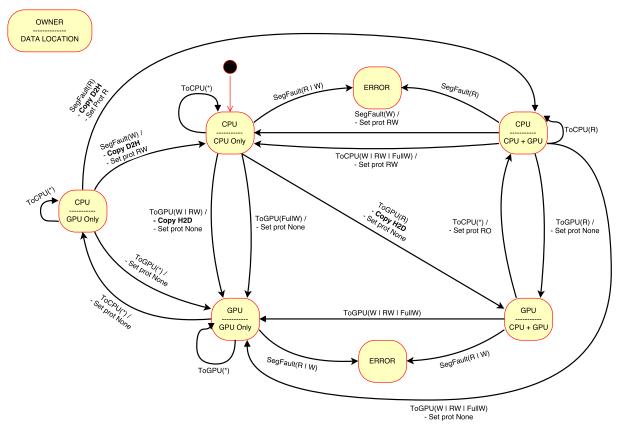

| 5.8  | SAMM memory coherence states.                  | 53 |

|------|------------------------------------------------|----|

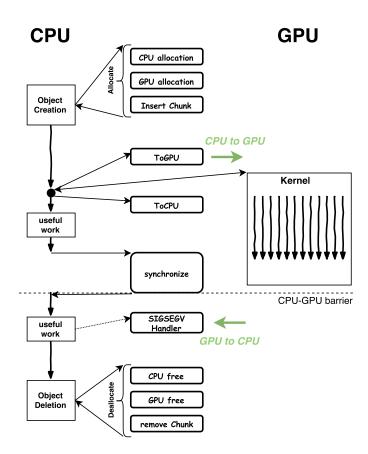

| 5.9  | SAMM use case.                                 | 54 |

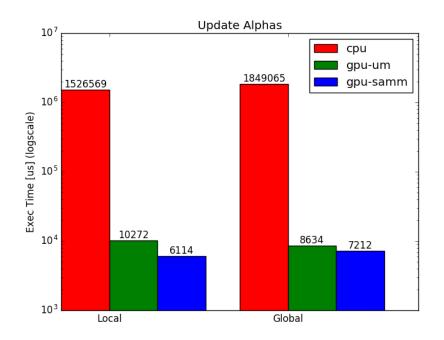

| 5.10 | UpdateAlphas in Minotauro (K80)                | 55 |

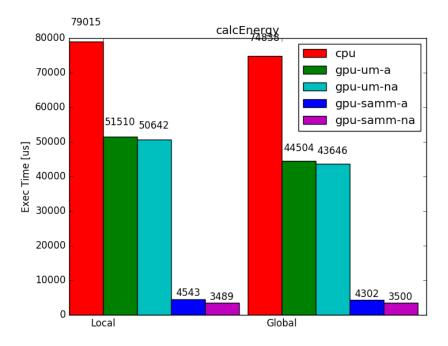

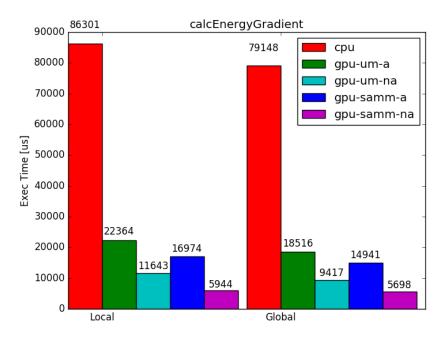

| 5.11 | calcEnergy in Minotauro (K80).                 | 56 |

| 5.12 | calcEnergyGradient in Minotauro (K80)          | 57 |

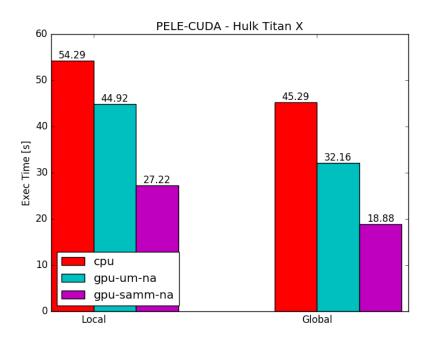

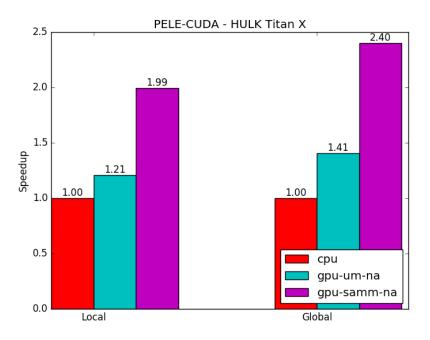

| 5.13 | Execution Time of PELE-CUDA in Hulk (Titan X). | 57 |

| 5.14 | Speedups of PELE-CUDA in Hulk (Titan X).       | 58 |

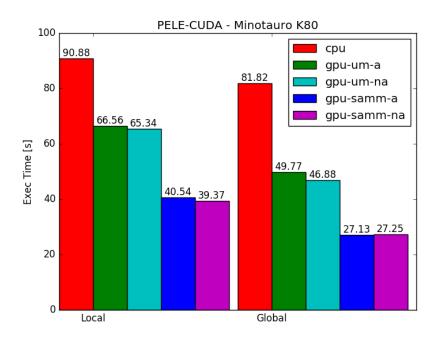

| 5.15 | Execution Time of PELE-CUDA in Minotauro (K80) | 58 |

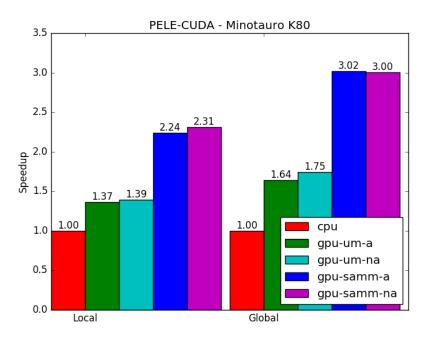

| 5.16 | Speedups of PELE-CUDA in Minotauro (K80)       | 59 |

# **List of Tables**

| 2.1 | GPU Architectures over time. Data taken from NVIDIA.                                      | 12 |

|-----|-------------------------------------------------------------------------------------------|----|

| 3.1 | Test machines with HW/node information                                                    | 19 |

| 3.2 | WARIS-Transport Compilation details.                                                      | 20 |

| 3.3 | PELE Compilation details.                                                                 | 20 |

| 4.1 | WARIS-Transport CPU profile using gprof in Minotauro (O3+AVX) and the Caulle-0.25-8bin    |    |

|     | 121x121x30 dataset                                                                        | 28 |

| 4.2 | Volcano Datasets.                                                                         | 33 |

| 4.3 | WARIS-Transport GPU profile with nvprof using 1 K80 in Minotauro. Caulle-0.25-8bin        |    |

|     | 121x121x64 dataset                                                                        | 34 |

| 4.4 | Speedups of most important kernels using 1 K80 in Minotauro. Caulle-0.25-8bin 121x121x64  |    |

|     | dataset                                                                                   | 35 |

| 4.5 | WARIS-Transport Execution Time for MPI+AVX (1 MPI rank/core) and MPI+OpenMP+AVX           |    |

|     | (1 MPI rank/node, 1 thread/core) implementations in MareNostrum. Caulle-0.05-8bin dataset |    |

|     | (601x601x64 x 8)                                                                          | 36 |

| 4.6 | WARIS-Transport Execution Time for MPI+AVX (1 MPI rank/core) and MPI+OpenMP+AVX           |    |

|     | (1 MPI rank/node, 1 thread/core) implementations in MareNostrum. Caulle-0.05-8bin dataset |    |

|     | (601x601x64 x 8)                                                                          | 36 |

| 5.1 | PELE CPU profile using gprof in Hulk and Global dataset.                                  | 44 |

| 5.2 | PELE Accelerated functions.                                                               | 44 |

## Chapter 1

## Introduction

All around the world, new Supercomputers are introducing accelerators as a way of improving performance and energy consumption, among which we can find GPUs.

One of the reasons that GPUs are being introduced in the HPC world is that their raw performance (FLOPS) and performance/watt (FLOPS/W) is higher than in CPUs, since GPUs were originally designed to do graphics, which is an inherently parallel workload.

GPUs have evolved into throughput-oriented devices with a high number of functional units, small caches, and high memory bandwidth to achieve high parallel performance. While CPUs have evolved into devices with high frequencies and a deep memory hierarchy to achieve high single-thread performance.

Unfortunately, adapting the software of a supercomputer is not an easy task. It takes months of work to develop new HPC applications. Therefore, instead of writing brand new applications for GPUs, the current trend is to adapt existing applications. Nevertheless this process is slow and painful due to current applications being already optimized for SMPs.

We think that GPU computing is beneficial to HPC applications because GPUs offer higher peak performance (FLOPS) and efficiency (FLOPS/W) than current CPUs. The reason for this is that GPUs having longer SIMD vector length than CPUs and having a memory hierarchy devoted to obtain the maximum memory throughput, GPUs are able to exploit more DLP than CPUs.

Not all programs can be ported to GPUs, but most HPC applications, are data parallel applications that could benefit from GPUs.

In-situ visualization in a GPU cluster is another reason for using GPUs. Actual GPU compute APIs are able to interact with GPU graphic APIs such as OpenGL exploiting memory locality in the GPU.

In this thesis we have analyzed and accelerated two large scientific applications used at the Barcelona Supercomputer Center (BSC). With this, we want to show how two complex applications can be efficiently ported to GPUs, enumerating the most important lessons learned. In addition, we have developed a mechanism to manage the coherency of CPU & GPU memories. Memory coherency is necessary because CPU and GPU have separated memories and coherency is not maintained by any hardware, therefore delegating this work to the programmer. Usually GPUs are not integrated in the same chip as CPUs, but sold as an external device plugged-in in a low-bandwidth interconnection network (typically PCI-express). Therefore a good memory management is key to achieve high performance in GPU applications.

The first application is a Computational Fluid Dynamics (CFD) application called WARIS-Transport developed in the Computer Applications (CASE) department and is a drop-in replacement for a well-

known application called FALL3D used for analyzing the transport and deposition of volcanic ashes.

In order to avoid the performance & programmability of maintaining CPU/GPU memory coherency, we opted to port all computations present in the iterative algorithm to the GPU.

CPU/GPU synchronization points act as a blocking operation in the CPU freezing offloading of work into the GPU and causing it to become idle when the synchronization point is reached. Therefore in order to feed the GPU with enough work and prevent stalls, in WARIS-Transport we minimized the amount of CPU/GPU synchronization points.

The second application is called PELE, a Molecular Conformation application with the Monte Carlo method (MC), originally developed at the Life Sciences (LIFE) department of BSC.

This application is significantly bigger than WARIS-Transport and the computation pattern cannot be completely offloaded to the GPU.

For this case we decided to use an automatic memory manager to ease the programmability of CPU/GPU memory coherency in a partially accelerated application. We present a Semi-Automatic Memory Manager (SAMM) to manage copies between CPU and GPU, which outperforms the automatic memory manager provided by NVIDIA, called Unified Memory (UM).

### 1.1 Document Organization

In chapter 2 we discuss NVIDIA GPU architecture features and the current evolution of performance between different NVIDIA HPC-class GPUs. Also we explain the CUDA programming model.

In chapter 3 we introduce the experimental set-up and methodology followed in this thesis.

In chapter 4 we present WARIS-Transport. We show implementation details, GPU development strategy and we give a comparison between the CPU and GPU implementation.

In chapter 5 we present PELE. In this chapter, a description of the application structure is provided. We also introduce each accelerated part with GPUs. In this application we propose using Unified Memory (UM) to manage CPU and GPU coherence. Also, and to increase performance, we propose a Semi-Automatic Memory Manager (SAMM). A comparison between the original implementation, and the GPU implementation with NVIDIA UM and SAMM is provided.

Chapter 6.1 concludes this thesis with the conclusions and lessons learned we extract from our work.

## Chapter 2

# GPU architecture and CUDA Programming Model

### 2.1 GPU architecture

In the past, Graphics Processing Units (GPUs) were focused exclusively on graphics processing, but since the unification of Vertex shader and Pixel shader units in a single, programmable computing unit, GPUs are able to efficiently execute data-parallel general purpose computations.

For simplicity, we will use the CUDA/NVIDIA nomenclature since it's the system used in this work. A GPU typically contains a number of highly multi-threaded vector computing cores named streaming multiprocessors (SMs), a front-end that distributes work between all the SMs, and DRAM. For instance, in Figure 2.1 we can see a schematic GPU layout of the newest NVIDIA GPU architecutre, *Pascal*.

Figure 2.1: Pascal architecture [1].

Each of these SMs (shown in Figure 2.2) contains several vector pipelines that issue instructions that execute on vector functional units (CUDA cores). Each SM also contains a large register file, a small L1

data cache, a shared memory, and a specialized cache for textures that can also be used to store read-only data.

| M    |                    |            |            |          |            |         | Instructi | on Cache |         |            |           |          |            |          |     |

|------|--------------------|------------|------------|----------|------------|---------|-----------|----------|---------|------------|-----------|----------|------------|----------|-----|

|      |                    | 1          | nstructio  | on Buffe | r          |         |           |          |         |            | nstructi  | on Buffe | r          |          |     |

|      |                    |            | Warp So    | heduler  |            |         |           |          |         |            | Warp So   | cheduler |            |          |     |

|      | Dispato            |            |            |          |            | ch Unit |           |          | Dispato |            |           |          |            | tch Unit |     |

|      |                    | Regist     | er File (3 | 32,768 x | 32-bit)    |         |           |          |         | Regist     | er File ( | 32,768 x | 32-bit)    |          |     |

| Core | Core               | DP<br>Unit | Core       | Core     | DP<br>Unit | LD/ST   | SFU       | Core     | Core    | DP<br>Unit | Core      | Core     | DP<br>Unit | LD/ST    | SFU |

| Core | Core               | DP<br>Unit | Core       | Core     | DP<br>Unit | LD/ST   | SFU       | Core     | Core    | DP<br>Unit | Core      | Core     | DP<br>Unit | LD/ST    | SFU |

| Core | Core               | DP<br>Unit | Core       | Core     | DP<br>Unit | LD/ST   | SFU       | Core     | Core    | DP<br>Unit | Core      | Core     | DP<br>Unit | LD/ST    | SFU |

| Core | Core               | DP<br>Unit | Core       | Core     | DP<br>Unit | LD/ST   | SFU       | Core     | Core    | DP<br>Unit | Core      | Core     | DP<br>Unit | LD/ST    | SFU |

| Core | Core               | DP<br>Unit | Core       | Core     | DP<br>Unit | LD/ST   | SFU       | Core     | Core    | DP<br>Unit | Core      | Core     | DP<br>Unit | LD/ST    | SFU |

| Core | Core               | DP<br>Unit | Core       | Core     | DP<br>Unit | LD/ST   | SFU       | Core     | Core    | DP<br>Unit | Core      | Core     | DP<br>Unit | LD/ST    | SFU |

| Core | Core               | DP<br>Unit | Core       | Core     | DP<br>Unit | LD/ST   | SFU       | Core     | Core    | DP<br>Unit | Core      | Core     | DP<br>Unit | LD/ST    | SFU |

| Core | Core               | DP<br>Unit | Core       | Core     | DP<br>Unit | LD/ST   | SFU       | Core     | Core    | DP<br>Unit | Core      | Core     | DP<br>Unit | LD/ST    | SFU |

|      | Texture / L1 Cache |            |            |          |            |         |           |          |         |            |           |          |            |          |     |

|      | Te                 | x          |            |          | т          | ex      |           |          | Те      | ex         |           |          | 1          | Tex      |     |

|      |                    |            |            |          |            | 6       | 4KB Shar  | ed Memo  | ry      |            |           |          |            |          |     |

Figure 2.2: SM in Pascal architecture [2]

GPUs execute using a Single Instruction Multiple Thread (SIMT) model where threads are grouped in fixed-length sets of threads (i.e., *warps*). All threads within a warp (32 in NVIDIA GPUs) execute in lock-step the same instruction on different data in parallel. Each vector pipeline is able to handle several in-flight warps and has a scheduler that selects the warp to be executed in each cycle. This helps GPUs hide long latency operations by switching to another warp on a cache miss.

| Architecture            | Tesla       | Fermi       | Kepler    | Maxwell   | Pascal     |

|-------------------------|-------------|-------------|-----------|-----------|------------|

| Year                    | 2008        | 2009        | 2012      | 2014      | 2016       |

| Register File Size / SM | 32 KB       | 128 KB      | 256 KB    | 256 KB    | 256 KB     |

| L1 size & Shared / SM   | 16 KB       | 48 KB       | 48 KB     | 96 KB     | 64 KB      |

| FP32 CUDA cores / SM    | 8           | 32          | 192       | 128       | 64         |

| FP64 CUDA cores / SM    | 1           | 8           | 64        | 4         | 32         |

| FP64:FP32 Ratio         | 1:8         | 1:4         | 1:3       | 1:32      | 1:2        |

| GPU Card                | Tesla C1060 | Tesla M2090 | Tesla K40 | Tesla M40 | Tesla P100 |

| #SMs                    | 30          | 16          | 15        | 24        | 56         |

| #FP32 Cuda cores        | 240         | 512         | 2880      | 3072      | 3584       |

| #FP64 Cuda cores        | 30          | 128         | 960       | 96        | 1792       |

| Peak FP32 GFLOPs        | 622         | 2660        | 5040      | 6844      | 10608      |

| Peak FP64 GFLOPs        | 77          | 665         | 1680      | 213       | 5304       |

| TDP                     | 187         | 225         | 235       | 250       | 300        |

| FP32 GFLOPs/W           | 3.32        | 11.82       | 21.44     | 27.36     | 35.36      |

| FP64 GFLOPs/W           | 0.41        | 2.95        | 7.14      | 0.85      | 17.68      |

Table 2.1: GPU Architectures over time. Data taken from NVIDIA.

In Table 2.1, in the upper part, we can observe a summary of the available resources per SM for the different CUDA architectures. And in the bottom part we see the most powerful single-chip HPC-class GPU from the each architecture<sup>1</sup> shown in the upper part.

NVIDIA has tree ways of improving performance (FLOPs) and efficiency (FLOPs/W) generation after generation. The first one is to scale the number of functional units (CUDA cores) per SM, increasing vector-level parallelism (e.g, from Tesla to Fermi and from Fermi to Kepler architectures, see FP32 CUDA cores/SM in Table 2.1). The second way is to scale the number of SMs, increasing TLP (e,g, from Kepler to Maxwell and from Maxwell to Pascal, see #SMs in Table 2.1). The third one is to scale the number of critical resources inside an SM, like the amount of shared memory or the register file size. Having more resources allows having more work in-flight, achieving more MLP and therefore, throughput.

For some HPC applications, support for double precision is mandatory to achieve good accuracy. Therefore, GPUs for HPC have to have a good FP64:FP32 ratio. As we can see in Table 2.1, the FP64:F32 ratio has improved from 1:8 in the first generation<sup>2</sup> to 1:2 in latest architecture coming this year. The exception is the Maxwell architecture. Maxwell was supposed to be released with 16nm integration scale (instead of 28nm like Kepler), but manufacturing problems forced NVIDIA to redesign the architecture for 28nm, prioritizing good FP32 performance over FP62 since their graphics market mainly demands high FP32 performance.

#### 2.1.1 Memory hierarchy

The Memory hierarchy of a GPU is designed to provide throughput at the expense of memory latency. Therefore, GPU memory hierarchies tend to have small general-purpose caches and high memory bandwidth to feed all SMs. Since GPUs have been dedicated for years to do graphics, today we can still find specialized caches like the texture cache or the constant cache. In some situations, specialized caches like the texture cache or the constant cache.

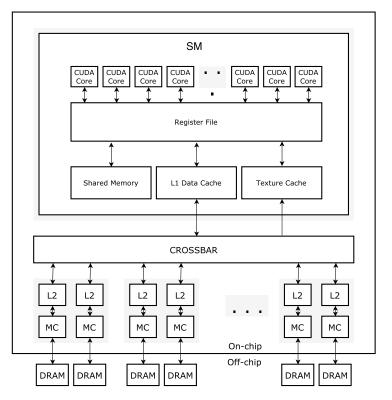

At the bottom of Figure 2.3, we can find the off-chip DRAM, often implemented with faster GDDR5 memory. Each DRAM chip is interfaced through a private on-chip memory controller (MC). Then, each MC talks to its L2 cache slice, which is connected to an interconnection network (usually represented as a crossbar). In the other side of the crossbar we can find all shared multiprocessors (SM) (only one represented for simplicity).

Each SM contains a instruction cache, a L1 data cache, a Texture-cache (TC) for read-only data, a shared memory and a big register file shared by all CUDA cores. Usually the register file is bigger than the other caches combined (see Table 2.1).

### 2.2 Why CUDA

We selected CUDA over other GPU programming models because it has a faster development and interesting features that we will explain in this section.

<sup>&</sup>lt;sup>1</sup>NVIDIA classifies their GPUs in relation to the segment of market are made for, for instance, *GeForce* are for gaming, *Quadro* for professional rendering, *Tegra* for low-power chips like mobile phones and tablets and *Tesla* GPUs are for HPC and workstations where double precision is required. But *Tesla* is also the name of the first GPU generation that supported CUDA. Therefore don't confuse the Tesla architecture from the upper part of Figure 2.1 with the Tesla HPC GPUs in the lower part of Figure 2.1.

<sup>&</sup>lt;sup>2</sup>Originally, Tesla architecture (G80) didn't have support for double precision (Compute Capability 1.1 and 1.2), but in the second revision with the GT200 gpu-core they added double precision support (Compute Capability 1.3).

Figure 2.3: Schematic GPU Memory hierarchy.

GPUs have evolved over time and new capabilities that are good for HPC are added. For instance, page migration in newer Pascal GPUs. In a standardized language like OpenCL, whenever there is a big feature that does not conform to the standard, a new revision of the standard has to be made. This may suppose months of discussions, after which hardware manufacturers may decide to not to support the new functionality. In contrast, NVIDIA (having full control of the language) frequently adds new functionalities to CUDA when new GPU architectures are released. CUDA offers high performance and better programmability, while OpenCL offers portability between GPU manufacturers.

From the programmer point of view, CUDA is easier to write because CUDA programmers usually write code with the CUDA runtime API, which provides higher level of abstraction than the CUDA driver API, which is equivalent to OpenCL. Also CUDA is easier than other languages like SIMD intrinsics. Since CUDA is a C++ extension, it supports templates (but not the STL). Also, unlike OpenCL, CUDA kernels are translated into device instructions at compile time, making it easier to catch errors at compile time instead of at run-time.

CUDA offers a more complete software stack including things like GPU-side debuggers, GPU profilers (command line and visual), disassemblers, also use GPU accelerated libraries like the CUDA math library, cuBLAS, cuFFT, cuDNN, cuSPARSE, cuRAND, cuSOLVER, Thrust, nvGRAPH or CUB.

### 2.3 The CUDA Programming Model

NVIDIA's GPU architecture is coupled with a programming model that extends C/C++ to write highperformance SIMT parallel programs. A CUDA program contains functions that are executed on the CPU, and functions that are executed in the GPU (i.e, *kernels*). CPU code needs to make sure that data is available in the GPU memory before executing a kernel that accesses it. This is performed via explicit memory transfers that move data through the PCI Express interconnect. In CUDA 6.0, NVIDIA introduced an automatic memory manager called Unified Memory (UM), where the CUDA runtime is in charge of copying data from CPU to GPU automatically (and from GPU to CPU at synchronization points).

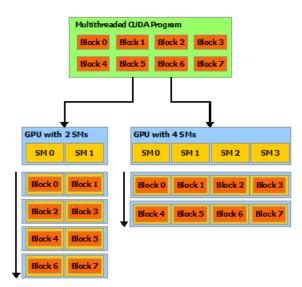

A kernel is defined as a multi-dimensional (up to 3D) *grid* of parallel tasks called *thread blocks* that execute the same function (i.e., SPMD model). Each thread block can be scheduled on any available Shared Multiprocessor (SM), in any order, concurrently or sequentially. In fig 2.4 we show an example of the automatic scalability of the CUDA programming language. Suppose a kernel with 8 thread-blocks, if we execute this kernel in a GPU with 4 SMs each SM will execute 2 thread-blocks, and in a GPU with 2 SMs each SM will execute 4 thread-blocks. If we assume fix time to compute each thread block in a SM across the two GPUs, then scaling up the number of SMs will have a positive effect on performance without the programmer having to rewrite anything.

Therefore a CUDA program can be transparently executed in any number of SMs. This property makes the CUDA programming model truly scalable, and allows CUDA programs to be launched on both low-power (mobile) GPUs like the Tegra K1 (1 SM) and GPUs with dozens of SMs like the new Tesla P100 with 56 SMs.

Figure 2.4: Automatic scalability [3]

This intrinsic scalability property is due to the inherent independence between computations in different thread blocks.

To exploit memory locality inside the thread block, CUDA provides access to shared memory, which acts as a cache managed by the programmer. There are also warp-level intrinsics that allow fast communication among threads in a warp without having to use shared memory (e.g., *shuffle intrinsics*).

Kernel execution and DMA transfer operations are asynchronously pushed by CPUs to the GPU using queues of commands called CUDA *streams*. Operations enqueued onto a stream are executed in order, but operations from different streams may be executed in parallel. To help programmers write CUDA programs while not caring about streams, the programming language defines a *default stream* (or stream zero) that is used by default when no other stream is specified (e.g. when using synchronous *cudaMemcpy* or when no stream is provided when launching a kernel).

This default stream has the property of serializing all other operations in other streams. Since asynchronous operation is key in order to overlap CPU and GPU computations or even GPU memory transfers and GPU kernel execution, using multiple streams is necessary to achieve maximum performance in a CUDA program.

### 2.3.1 Kernels

Kernels are C++ functions defined with the *\_\_global\_\_* specifier. A CUDA kernel can call other functions that have the *\_\_device\_\_* specifier, but a kernel cannot call functions executed in the CPU (functions with *\_\_host\_\_* specifier).

If *dynamic parallelism* is supported by the GPU, then a GPU kernel is able to launch other kernels without going to the CPU. This allows the GPU to generate more work without having CPU intervention. This functionality is available after CUDA 5.0 and for GPUs with compute capability<sup>3</sup> 3.5 or greater.

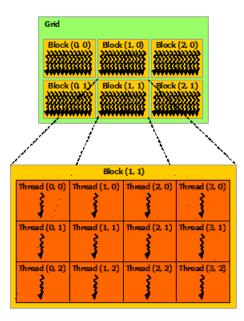

### 2.3.2 Thread hierarchy

Threads in a CUDA kernel are organized in a 3D hierarchy to form a one-dimensional, two-dimensional or three-dimensional grid of threads called thread block. Also, as a second layer, threads blocks can be organized in a one-dimensional, two-dimensional or three-dimensional grid of thread blocks. In Figure 2.5, we can see an example 2D grid of 2D thread blocks.

Figure 2.5: Thread hierarchy [3].

This enables CUDA programs to easily map threads into 1D/2D/3D problems. For higher conventionalities, programmers have to rely in sequential *for* constructs.

### 2.3.3 CUDA Memory Types

CUDA threads have access to several memory spaces:

<sup>&</sup>lt;sup>3</sup>Compute Capability (CC) is the term used by NVIDIA to classify GPU architectures and their capabilities

- Global memory: Memory resident in GPU Main memory (GDDR) and cached in L2 (L1 caching enabled with compile flags).

- Local memory: Per-thread memory used to store register spills and stack memory. Cached in L1/L2 and physically resident in GPU Main memory (GDDR).

- Shared memory: Per-thread-block memory with high bandwidth used to share data between threads in a thread block (akin to local store in other architectures).

- Texture memory: Read-only memory, allocated in the off-chip memory used by global memory but accessed by dedicated hardware (Texture Functional Units) and cached in the texture cache. Also provides data filtering and interpolation by hardware.

- Constant memory: Read-only memory cached in the constant cache that presents benefits when all threads in a warp load the same data. Usually is implemented using Texture reads, therefore it uses the texture pipeline and is allocated in global memory.

## Chapter 3

## **Experimental Setup and Methodology**

This work has been performed mainly in a GPU server called *Hulk*, see Table 3.1. Also to compare the performance, other machines like *Minotauro* or *MareNostrum* have been used.

Hulk initially had four Tesla K40, GPUs that have been used in the first part of this thesis (WARIS-Transport), then the GPUs were upgraded to GeForce Titan X, which implement the later GPU architecture available (Maxwell). In both cases all GPUs are connected to the same PCI-e root complex which enables peer-to-peer communications without CPU intervention.

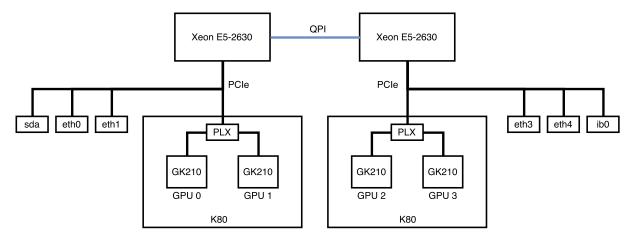

On the other hand Minotauro (see Figure 3.1) has two NVIDIA Tesla K80 per node. A K80 is a dual-pci-slot GPU that contains two GK210, that has double register file size than a K40 (512 KB/SM vs 256 KB/SM) but in exchange has less SMs per GPU (13 SMs instead of 15) and is programmed as two different GPUs from CUDA. Each GK210 has 12 GB of GDDR5 for a total of 24 GB per K80 card. Since CUDA exposes each GK210 as one "GPU K80", in this document we will show Minotauro as having 4 K80 GPUs per node.

|               | MareNostrum III    | Minotauro             | Hulk (WARIS)      | Hulk (PELE)     |

|---------------|--------------------|-----------------------|-------------------|-----------------|

| CPU           | Intel Xeon E5-2670 | Intel Xeon E5-2630 v3 | Intel Core i7-482 | 0K              |

| Architecture  | Sandy Bridge       | Haswell               | Ivy Bridge-E      |                 |

| Freq          | 2.60GHz            | 2.40GHz               | 3.7GHz            |                 |

| Cache size    | 20480 KB           | 20480 KB              | 10240 KB          |                 |

| #cores/socket | 8                  | 8                     | 8                 |                 |

| #sockets/node | 2                  | 2                     | 1                 |                 |

| GPU card      | -                  | Tesla K80             | Tesla K40         | GeForce Titan X |

| GPU Arch.     | -                  | Kepler                | Kepler            | Maxwell         |

| #GPUs/card    | -                  | 2                     | 1                 | 1               |

| #cards/node   | -                  | 2                     | 4                 | 4               |

| #GDDR/GPU     | -                  | 12 + 12 GB            | 12 GB             | 12 GB           |

| RAMM          | 32 GB DDR3         | 128 GB DDR4           | 64 GB DDR3        |                 |

| DISC          | GPFS + SSD         | GPFS + SSD            | 1TB HDD           |                 |

Table 3.1: Test machines with HW/node information.

WARIS-Transport (see Table 3.2), requires MPI implementations to support MPI\_THREAD\_MULTIPLE in order to allow multiple threads calling MPI at the same time. CUDA 7.5 was used, and the compilation flags were set to *-O3 -march=native*. In PELE (see Table 3.3) was compiled using a combination of

Figure 3.1: Minotauro K80 node configuration.

g++-4.9.3 and nvcc. In both cases, *gprof* was used as the CPU profiler and nvprof as the GPU profiling tool.

|              | Marenostrum    | Minotauro         | Hulk              |

|--------------|----------------|-------------------|-------------------|

| MPI wrapper  | impi-5.1.2.150 | openmpi-1.6.5-mt  | mvapich-2.0-mt    |

| CPU compiler | icc-13.0.1     | gcc-4.9.1         | gcc-4.9.3         |

| GPU compiler |                | nvcc-7.5.17       | nvcc-7.5.17       |

| CFLAGS       | -O3            | -O3 -march=native | -O3 -march=native |

| Dependences  |                | Version           |                   |

| HDF5         | 1.8.12         | 1.8.12            | 1.8.15            |

| PNETCDF      | 1.7.0          | 1.7.0             | 1.6.0             |

| NETCDF       | 4.3.3.1        | 4.3.3.1           | 4.3.3.1           |

| SZIP         | 2.1            | 2.1               | 2.1               |

Table 3.2: WARIS-Transport Compilation details.

|              | Minotauro         | Hulk              |

|--------------|-------------------|-------------------|

| CPU compiler | g++-4.9.3         | g++-4.9.3         |

| GPU compiler | nvcc-7.5.17       | nvcc-7.5.17       |

| CUDA Runtime | 7.5               | 7.5               |

| CXXFLAGS     | -O3 -march=native | -O3 -march=native |

| Dependences  | Ver               | sion              |

| BLAS         | 1.0               | 3.6.0             |

| LAPACK       | 3.3.1             | 3.6.0             |

| BOOST        | 1.57              | 1.58              |

| cryptopp     | 5.6.2             | 6.0.0             |

| jsoncpp      | 1.7.2             | 1.7.2             |

| wjelement    | 1.0               | 1.0               |

Table 3.3: PELE Compilation details.

To measure results in WARIS-Transport we used the internal timer that WARIS Framework uses that reports the total executing time of the application. Then, as only one execution in the CPU can take hours we decided to only run 4 executions of each WARIS-Transport implementation and then report the mean of those executions.

In PELE to report the execution time we used */usr/bin/time -f=%e* to calculate the elapsed time of each execution and then calculate the average execution time.

Chapter 4

## WARIS-Transport

### 4.1 Introduction

WARIS-Transport is a high-performance implementation (written in C) of a well-known industry standard application for volcanic ash transport simulation named FALL3D which is already in production in the Buenos Aires VAAC [7].

In 2010 the Eyajfajallajokull volcano (in Iceland) erupted causing a major disruption of the European airspace: more than the 48% of the flights were canceled provoking 1.3 billion euros cost to airline industry.

Figure 4.1: Volcanic Ash Advisory Centers [4].

The goal of WARIS-Transport is to do forecasting of atmospheric transport and deposition of volcanic ashes. This type of application is mainly used by the 11 Volcanic Ash Advisory centers (see Figure 4.1), that are in charge of monitoring volcanic eruptions and help airliners redirect their flights to avoid the ash clouds of volcanic eruptions.

WARIS-Transport sits on top of the WARIS framework, a Barcelona Supercomputing Center (BSC) in-house multi-purpose framework focused at solving scientific problems using Finite Differences (FD).

WARIS-Transport can be classified as an Earth Simulation application that does Computational Fluid Dynamics (CFD) computations using FD on structured meshes.

### 4.2 Application Structure

Algorithm 1 shows the control flow of typical FD applications using structured meshes. The first step is to divide the computational domain into smaller chunks that will be allocated to each CPU. Time is discretized in  $\Delta$  steps. For each step, input data is read (from disk or memory, etc..) and *injected* into the structured mesh (line 4). If necessary this data is pre-processed (line 5). Then boundary conditions have to be applied to ensure correctness (line 6). For all discretized points a computation called *stencil* is performed (line 8). This step is the most computationally expensive of the whole algorithm. If the domain has been distributed using MPI, in line 10 overlap points between neighbor domains (from different MPI ranks) are exchanged otherwise communication is done via shared memory. To finalize (if necessary) data is post processed and written to disk.

|               | thm 1 General control flow structure of a generic FD code.    |                  |

|---------------|---------------------------------------------------------------|------------------|

| 1: <b>p</b> i | rocedure WARIS                                                |                  |

| 2:            | Structured mesh Domain decomposition                          |                  |

| 3:            | for $t = time_{start}$ to $time_{end}$ in $\Delta t$ steps do | ⊳ Loop over time |

| 4:            | Read input for t                                              |                  |

| 5:            | Pre-process input                                             |                  |

| 6:            | Apply boundary conditions                                     |                  |

| 7:            | for all discretized points do                                 |                  |

| 8:            | Stencil computation                                           |                  |

| 9:            | end for                                                       |                  |

| 10:           | Exchange overlap points between neighbour domains             |                  |

| 11:           | Post-process output                                           |                  |

| 12:           | Write output for t                                            |                  |

| 13:           | end for                                                       |                  |

| 14: <b>er</b> | ld procedure                                                  |                  |

### 4.3 The WARIS Framework

WARIS [5] is an in-house BSC framework aimed at solving finite differences problems. The goal of this framework is to reuse as much as possible code from different FDM problems and optimizations, and to, facilitate the adaptation to new hardware and devices.

Figure 4.2: WARIS computational domain distribution with MPI+pthreads [5]. (CN= Computational Node)

Figure 4.3: WARIS communication between nodes [5].

The WARIS framework uses a combination of MPI to distribute work between nodes, and posix threads to fully occupy a compute node. In Figure 4.2 we see an example problem of 100 units decomposed in three MPI ranks with three threads each, for a total of nine threads working on the whole problem. The WARIS framework tries to exploit the SMT capabilities of CPUs by creating multiple pthreads per MPI rank, eventually oversubscribing the node. Each MPI rank has a master thread that controls the shared memory domains (see Figure 4.3), and each shared memory domain contains a compute thread, two communication threads and a IO thread.

#### 4.3.1 The stencil computation

Stencil computations are the computations that perform the time propagation in FD simulations.

Typical stencils work with one, two or three dimensional grids. In each time-step, the stencil updates all grid elements using the neighboring elements as a pattern. This computational pattern, is called *the stencil* and largely depends on the shape of the PDE formula. (e.g., in Algorithm 2 we can observe a two dimensional 5 point stencil)

```

Algorithm 2 A stencil example: 2D 5p-stencil.1: procedure STENCIL(unew, u)2: for i = halo_size to sizex - halo_size do3: for j = halo_size to sizey - halo_size do4: unew_{i,j} = u_{i,j} + u_{i+1,j} + u_{i-1,j} + u_{i,j+1} + u_{i,j-1}5: end for6: end for7: end procedure

```

In Figure 4.5, we can observe the data dependences of the stencil shown in Algorithm 2 using a 3x6 grid. In this case, the 5-point stencil has one data dependence up, down, right and left, therefore the grid has some exterior elements called *halos* that are maintained to fulfill data dependences.

Figure 4.4: A 2D 5p-stencil computation.

### 4.3.2 Parallel stencil decomposition

Parallel stencil implementations using MPI (like the one used in WARIS-Transport) introduce the problem of managing data dependences between neighboring ranks. Those neighboring points are usually called *halos*, and have to be communicated between MPI ranks at each step to ensure correct execution. In Figure 4.4 we can observe an example of a 2D stencil parallelization using two MPI ranks. Firstly, each MPI rank computes his own piece of halos, then while MPI halo communication is ongoing the rest of the stencil is compute achieving an overlap in time between MPI communication and execution.

Figure 4.5: Halo exchange between MPI ranks

WARIS-Transport solves a general transport equation, also called General Advection Diffusion Reaction Equation in a cartesian (x,y,z) grid using FD (for a more in-depth discussion of WARIS-Transport equations see Appendix A).

Therefore, the WARIS framework follows the typical FD algorithm but with specific computations related to the problem at hand. In Algorithm 3 (a more detailed version of Algorithm 1), we can observe the general algorithm of WARIS-Transport. Basically, the application starts reading meteorological (line 4) and configuration data (line 2 and 3) and time is discretized (line 4). Then, the main loop starts. As long as the the eruption is ongoing, source injection data is read from meteorological database (line 14) and the term is scaled by a factor (line 15). After that (and if there is the need to update the meteorological information) meteorological data is read from the meteorological database (in NetCDF format) and several

meteorological computations are launched (from line 18 to 29). Then, boundary conditions are applied and the advection-diffusion-sedimentation function is launched for each particle class in line 32. To finalize, several post-process calculations are done (lines 35 to 38).

| Alg | orithm 3 WARIS-Transport Algorithm [8].                                                        |

|-----|------------------------------------------------------------------------------------------------|

| 1:  | procedure WARIS-TRANSPORT                                                                      |

| 2:  | Read particle properties from granulometry file                                                |

| 3:  | Read time and configuration variables from input file                                          |

| 4:  | Read meteo database and grid data from NetCDF file                                             |

| 5:  | Compute grid increments                                                                        |

| 6:  | Compute time-lag between the time origin of the database and the time origin of the input data |

| 7:  | Allocate memory arrays                                                                         |

| 8:  | Read topography from meteo file                                                                |

| 9:  | Compute scaling factor                                                                         |

| 10: | Read output strategy                                                                           |

| 11: | for $t = time_{start}$ to $time_{end}$ in $\Delta t$ steps do $\triangleright$ Loop over time  |

| 12: | if $source\_time \leqslant t$ then                                                             |

| 13: | for $p = particle_0$ to $particle_n$ do                                                        |

| 14: | Read the source term from source file $(S^{np})$                                               |

| 15: | Scale source term $(S_*^{np})$                                                                 |

| 16: | end for                                                                                        |

| 17: | end if                                                                                         |

| 18: | if $meteo\_time <= time$ then                                                                  |

| 19: | Read meteorological variables from the meteo file. $(u_{x,y,z}, T, p, etc.)$                   |

| 20: | Update meteo_time                                                                              |

| 21: | Initialize boundary conditions                                                                 |

| 22: | Compute horizontal and vertical diffusion coefficients $(K_{x,y,z})$                           |

| 23: | for $p = particle_0$ to $particle_n$ do                                                        |

| 24: | Compute the terminal settling velocity $(V_{sj})$                                              |

| 25: | end for                                                                                        |

| 26: | Compute scaled quantities                                                                      |

| 27: | Calculate the critical time step ( $\Delta t$ ).                                               |

| 28: | AllReduce of $\Delta t$                                                                        |

| 29: | end if                                                                                         |

| 30: | Set the boundary conditions $(C)$                                                              |

| 31: | for $p = particle_0$ to $particle_n$ do                                                        |

| 32: | Calculate ADS stencil (move in time) $(C^{t+1})$ $\triangleright$ Most expensive part          |

| 33: | Exchange overlap points between neighbor domains                                               |

| 34: | end for                                                                                        |

| 35: | Compute ground accumulation of ash $(C_{accu})$                                                |

| 36: | Compute mass lost at boundaries                                                                |

| 37: | AllReduce of mass lost                                                                         |

| 38: | Mass balance correction                                                                        |

| 39: | Output results $C_{t+1}$                                                                       |

| 40: | End time step. Swap input $(C^t)$ and output matrices $(C^{t+1})$                              |

| 41: | end for                                                                                        |

| 42: | end procedure                                                                                  |

Another remarkable point of WARIS-Transport is that particles of different granularities are discretized in different standardized particle sizes (named *particulate matter* or PM). Therefore, stencil computations

working with particles of different granularities are independent of each other, enabling concurrent stencil computations.

## 4.4 Initial profiling

To assert the total execution time of each part shown in Algorithm 3 we profiled WARIS-Transport using *gprof*. The initial profiling (for one MPI process) is shown in Table 4.1. The application was compiled with -O3 and with AVX enabled (meaning it's not a naive sequential implementation). The dataset used is from the Cordón-Caulle volcano with dimensions 121x121x30 and 8 particle types.

| %     | Time (s) | #calls    | Name                         |

|-------|----------|-----------|------------------------------|

| 79.81 | 6778.74  | 54648     | device_maingrid_adv          |

| 6.62  | 561.89   | 236012920 | device_gama                  |

| 5.79  | 491.71   | 6831      | device_mass                  |

| 2.49  | 211.12   | 236012920 | device_vsettling             |

| 2.31  | 196.41   | 40986     | device_abc_zgnc              |

| 2.04  | 172.89   | 6831      | device_divcorr               |

| 0.44  | 37.21    | 6831      | device_groundaccum           |

| 0.25  | 20.95    | 65        | device_meteo_vsettling       |

| 0.10  | 8.07     | 66        | device_prepare_io            |

| 0.04  | 3.75     | 65        | device_stabdt                |

| 0.03  | 2.78     | 65        | device_meteo_scale           |

| 0.02  | 1.97     | 390       | device_abc_mirror            |

| 0.02  | 1.28     | 528       | device_cutflevel             |

| 0.01  | 1.16     | 65        | device_meteo_precompute      |

| 0.01  | 0.85     | 390       | device_permvolume            |

| 0.01  | 0.48     | 65        | device_meteo_setvdrydep      |

| 0.01  | 0.47     | 147507893 | device_fEIDX                 |

| 0.01  | 0.46     | 147507897 | device_fMIIDX                |

| 0.00  | 0.38     | 65        | device_meteo_divu            |

| 0.00  | 0.31     | 1         | eapd_transport_read_meteo    |

| 0.00  | 0.13     | 65        | device_meteo_hdiffusion      |

| 0.00  | 0.13     | 65        | device_meteo_vdiffusion      |

| 0.00  | 0.10     | 29501615  | device_fFIDX                 |

| 0.00  | 0.08     | 6831      | device_src                   |

| 0.00  | 0.08     | 1         | device_init_fields           |

| 0.00  | 0.08     | 29501615  | device_fIDX                  |

| 0.00  | 0.04     |           | device_fMIDX                 |

| 0.00  | 0.03     | 65        | device_meteo_terrvel         |

| 0.00  | 0.02     | 20493     | eap_phase_proc               |

| 0.00  | 0.01     | 6831      | device_maingrid              |

| 0.00  | 0.01     | 6831      | eapd_transport_prepare_meteo |

| 0.00  | 0.01     | 6831      | eapd_transport_src           |

| 0.00  | 0.01     | 65        | eapd_transport_read_source   |

| 0.00  | 0.01     | 11        | eapd_transport_meteo         |

**Table 4.1:** WARIS-Transport CPU profile using *gprof* in Minotauro (O3+AVX) and the Caulle-0.25-8bin 121x121x30 dataset.

As expected, the ADR calculation in function device\_maingrid\_adv is the most expensive part of the

application, with 79.81% of the execution time. The second most expensive function is the aggregate of *device\_meteo\_vsettling* with their children, *device\_vsettling* and *device\_gamma* with an aggregated time of 9.36%. Other important functions are the absorbing boundary conditions (*device\_abc*) with a 2.31% and *device\_divcorr* wiht a 2.04%.

### 4.5 The Advection Diffussion Reaction

As we have seen in section 4.4, the most important part in terms of execution time is the advection-diffusion reaction function (ADR).

The ADR function computes a 3D stencil over a Cartesian grid.

ADR computes the transported quantity (C) in a  $\Delta t$  step, the algorithm reads the fluid velocities in each component (V(x, y, z), V(x, y, z) and W(x, y, z)), the turbulent diffusion coefficients ( $K_x(x, y, z)$ ,  $K_y(x, y, z)$ ,  $K_z(x, y, z)$ ) and the source term (S(x, y, z)).

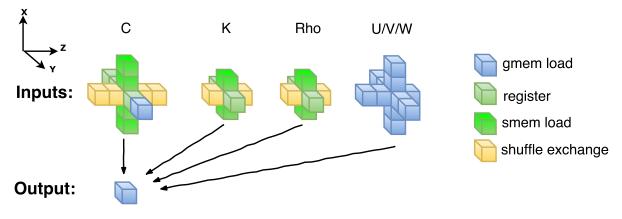

The overall ADR stencil computation is equivalent to a 3D 13-point stencil for C (Figure 4.6) plus a 3D 12-point stencil for W (Figure 4.7) plus a 3D 7-point stencil for each K (Figure 4.8).

**Figure 4.6:** *C* 13-p stencil

Figure 4.7: U/V/W 12-p stencil

The arithmetic intensity is the ratio of floating operations (in FLOPs) done in a piece of data versus the cost it takes to bring all necessary data through the memory hierarchy (in bytes). Applications with lower arithmetic intensity (measured in FLOPs/byte) will be more prone to be limited by the memory subsystem (therefore called memory-bound), than applications with high arithmetic intensity, that will be limited by the amount of computational power available in the hardware (typically the number of CUDA cores in the case of NVIDIA GPUs).

In fact, we can estimate if a naive ADR implementation would be compute bound or memory bound. Knowing that the ratio of input:output points is 32:1, and this is 128 bytes/point in single precision, and a naive implementation of ADR would have 250 floating point operations (FLOPs) per output point). We can compute the arithmetic intensity of a naive ADR kernel as  $\frac{250FLOPs}{128bytes} = 1.95\frac{FLOPs}{byte}$  which puts ADR in the upper band of stencils (stencils typically have 0.1~1.0 FLOPs/byte).

A Roofline Performance Model [9] is a visually intuitive way of bounding the performance achieved by a code in a certain architecture. In Figure 4.9 we can observe the roofline model of a Tesla K40, where the dashed blue line represents the theoretical performance limit using global memory (288 GB/s), the solid green line represents the theoretical performance limit using only shared memory (aggregated bandwidth of 2860.8 GB/s). The vertical black line represents the arithmetic intensity projection of the ADR kernel.

In Tesla K40 the peak performance in single precision is 5040 GFLOPs, therefore kernels with less than  $\frac{5,04x10^{12}FLOP/s}{3,09x10^{11}byte/s} \approx 16 \frac{FLOPs}{byte}$  arithmetic intensity will be memory bound. Since 1.95 < 16, we can estimate that our naive implementation of the ADR kernel would be memory-bound. Therefore a good memory management is key to achieve peak performance in ADR computations.

Figure 4.9: Roofline Model of NVIDIA Tesla K40 with WARIS-Transport

### 4.6 CUDA Implementation

In this section we present the CUDA implementation we have done. Based on the profiling previously done, we have ported to CUDA the ADR and vsettling kernels. Then, after some post-analysis we decided to reduce the number of memory copies between CPU & GPU by moving all remaining computations to the GPU.

At the end we end up with all major computations implemented in the GPU, improving the overall execution time. One MPI rank per GPU was used, therefore getting a multi-GPU implementation scaling the number of MPI ranks with the benefit that the WARIS framework is in charge of distributing the correct data between neighbors (GPUs).

Implementing just the ADR computation in the GPU and executing the rest in the CPU had two problems from the performance point of view:

- 1. Overheads. Although we accelerate the ADR kernel, CPU to GPU and GPU to CPU copies have to be performed to maintain the data coherent across the CPU & GPU domain. This is necessary to ensure that functions using the results from the ADR kernel have correct inputs.

- 2. Ideally (without counting the previous overheads) the achieved performance is bounded by the amount of parallelized task. Applying Amdahl's law, if we were to accelerate ADR by an  $\infty$  factor, we would get a maximum speedup of:

$$Speedup_{ADR-ideal} = \lim_{s \to \infty} \frac{1}{(1 - 0.7981) + \frac{0.7981}{s}} = \frac{1}{1 - 0.7981} = 4.95x$$

Therefore, we decided to accelerate not only ADR, but all major non-IO computations with GPU kernels, in part, to minimize data movement from CPU & GPU and to enable greater speedups in this application.

Some computations are independent and can be done in parallel thus we used multiple CUDA streams to enable concurrent execution in the GPU.

### 4.6.1 ADR Kernel

To accelerate the ADR stencil with CUDA some of the techniques from Micikevicius et. al. [10] were used. All threads in a thread-block cooperate to compute the stencil using several techniques like register tiling, where data is loaded from global memory into registers, and is moved from register to register until is no longer needed, and shared memory to increase overall performance.

The ADR kernel uses a 2D thread-block decomposition mapped into the XZ plane.

The first optimization we used is to declare all read only pointers as *const\_restrict\_*, helping the compiler to further optimize the code. In Kepler or later architectures, this optimization enables reading from the texture pipeline (and the texture cache) without having to use texture objects. In memory-bound kernels, optimizations like this one are very important because it improves the overall memory bandwidth available to every thread from GPU main memory since you are exploiting the L1-L2 bus for read-write data and the Texture Cache-L2 bus for read-only data (see 2.3).

In a stencil, each point is visited by several threads, then to reuse data between threads we used shared memory. But when loading from global memory to shared memory we have to face the problem of loading the stencil neighboring points (or halos), being the two major solutions:

Given a 2D thread block of (x, y) threads:

- A) Allocate a shared memory region of  $(x + 2 * halo\_size, y + 2 * halo\_size)$  elements and then make the exterior threads in a thread-block load halos from global memory to shared memory. Then the stencil computations is done entirely with data resident in shared memory.

- B) Allocate a shared memory region of (x, y) elements and then read stencil halos from global memory while inner points are read from shared memory.

In our implementation the second scheme is used because it's simpler since we don't have to load those points into shared memory.

Another key point when writing CUDA kernels is that general performance highly depends of the number of thread blocks in flight in the SM. This is measured with a metric called *occupancy*. The

Figure 4.10: ADR Kernel: Thread block with front of threads that read from gmem and store in registers.

maximum number of thread blocks in a SM is a function of different SM resources like the register usage, shared memory usage and block size shape because those resources are shared between all threads in a SM.

Therefore optimized the number of registers used in this kernel, including not using register tiling for all input volumes, for instance, we use register tiling for C, K and Rho but volumes U, V and W are loaded directly from global memory to save registers. Because sometimes small changes in register usage (for instance from 33 to 32) means that instead of 8 resident thread blocks, 16 thread blocks can be scheduled, improving occupancy and performance.

In Figure 4.10 we can observe a graphic representation of all data required to compute a slice of Y. We make use of colors to help understand the Figure. At each iteration of Y, the front of threads (blue color) loads input values of two Y slices forward (Y + 2) from global memory into registers.

Then each thread performs a register tiling and store X, Y, Z data into shared memory.

Finally threads in the same warp (Z dimensions) exchange data using *shuffle intrinsics*. If no neighbor is available then halos are read directly from global memory. In Y dimensions, data is read from shared memory. Again if no neighbor is available, data is read directly from global memory.

**Figure 4.11:** ADR Kernel: Example of Thread (i, j) computing output point  $C_{x,y,z}$ .

In figure 4.11 we can observe a more detailed view for a thread. Inputs for volumes C, K, Ro and

U/V/W are read to produce a unique output point of C. Given the amount of 3D volumes this kernel has to load from memory, we were forced to load U/V/W volumes from global memory to not use too much registers and not to hurt performance.

#### 4.6.2 Vsettling Kernel

The second most important function in WARIS-Transport is *device\_gama* + *device\_vsettling* that accounts for a total of 6.62% + 2.49% + 0.25% = 9.36% of the original application. This function calculates the particle settling velocity  $v_s$  where particles settle down at their terminal velocity. For calculating  $v_s$  this formula is used:

$$v_s = \sqrt{\frac{4g(\rho p - \rho \alpha)d}{3C_d \rho \alpha}} \tag{4.1}$$

Where  $\rho_a$  and  $\rho_{\alpha}$  denote air and particle density, respectively, d is the particle-equivalent diameter, and  $C_d$  is the drag coefficient calculated using the GANSER [11] formula.

Unfortunately in WARIS-Transport, the GANSER formula is implemented as an iterative process that tries to converge to the best possible  $v_s$ . This is not optimal in GPU code, because introduces *thread divergence*<sup>1</sup> because some threads converge before than others. But to maintain correctness between CPU & GPU the same algorithm had to be implemented in the GPU.

Therefore the vsetting kernel was implemented using one thread per particle, where each thread has to iterate to find the best  $v_s$  for the particle assigned to it. As an optimization, read-only data was declared as  $const * \_restrict\_$  to let the compiler use texture cache while writes go to the L2 cache.

#### 4.6.3 Other Kernels

To minimize CPU&GPU copies copies all non-IO computations were implemented as CUDA Kernels in the GPU. This includes functions present in the main loop such as *device\_mass*, *device\_divcorr*, *device\_groundaccum*, all meteorologic functions *device\_meteo\_\*\** and some parts of *device\_prepare\_io*.

### 4.7 Results

The datasets used in this section are shown in Table 4.2. The Caulle-0.25 dataset is the same used in the initial profiling and is used again for the GPU profiling in section 4.7.1. The Caulle-0.05 dataset has bigger resolution and is used fro the CPU vs GPU evaluation in section 4.7.2.

| Dataset Name | Size           | #particles | # Total nodes |

|--------------|----------------|------------|---------------|

| Caulle-0.25  | 121 x 121 x 30 | 8          | 3.5M          |

| Caulle-0.05  | 601 x 601 x 64 | 8          | 184.9M        |

### 4.7.1 Final profiling with nvprof

In Table 4.3 we can observe the profiling of all GPU kernels using the Caulle-0.25-8bin 121x121x30 dataset, the same used on the initial profiling. We should warn to the reader that this profiling only

<sup>&</sup>lt;sup>1</sup>In SIMT programs we say that we have thread divergence when not all threads in a warp take the same branch condition (in an if/else statement), then each part has to be replayed with the correspondent threads.

| %     | Total Time | #Calls | Kernel Avg. Time | Name                                 |

|-------|------------|--------|------------------|--------------------------------------|

| 67.06 | 101.386s   | 54648  | 1855.30 us       | device_maingrid_adv_kernel           |

| 10.66 | 16.1217s   | 520    | 31003.00 us      | device_meteo_vsettling_kernel        |

| 4.75  | 7.18898s   | 54648  | 131.55 us        | device_divcorr_kernel                |

| 3.75  | 5.67294s   | 54648  | 103.81 us        | device_abc_zgnc_top_kernel           |

| 3.35  | 5.05788s   | 54648  | 92.55 us         | device_abc_zgnc_bottom_kernel        |

| 3.17  | 4.79063s   | 54648  | 87.66 us         | device_mass_voldepmass_kernel        |

| 2.14  | 3.23239s   | 54648  | 59.14 us         | device_abc_zgnc_right_kernel         |

| 1.17  | 1.76681s   | 54648  | 32.33 us         | device_abc_zgnc_left_kernel          |

| 0.90  | 1.36253s   | 3120   | 436.71 us        | device_abc_mirror_kernel             |

| 0.67  | 1.01662s   | 54648  | 18.60 us         | device_groundaccum_kernel            |

| 0.52  | 792.51ms   | 54648  | 14.50 us         | device_mass_outmass_bottom_kernel    |

| 0.32  | 476.80ms   | 54648  | 8.72 us          | device_abc_zgnc_front_kernel         |

| 0.26  | 386.79ms   | 54648  | 7.07 us          | device_abc_zgnc_back_kernel          |

| 0.24  | 363.79ms   | 520    | 699.59 us        | device_stabdt_kernel                 |

| 0.19  | 282.81ms   | 54648  | 5.17 us          | device_mass_outmass_leftright_kernel |

| 0.13  | 202.23ms   | 54648  | 3.70 us          | device_src_kernel                    |

| 0.13  | 197.19ms   | 164141 | 1.20 us          | [CUDA memset]                        |

| 0.13  | 191.89ms   | 62328  | 3.07 us          | [CUDA memcpy HtoD]                   |

| 0.10  | 157.02ms   | 520    | 301.95 us        | device_meteo_scale_part2_kernel      |

| 0.10  | 156.96ms   | 198    | 792.72 us        | device_io_accum_c2_idx_kernel        |

| 0.10  | 155.48ms   | 528    | 294.46 us        | device_cutflevel_kernel              |

| 0.05  | 76.511ms   | 21416  | 3.57 us          | [CUDA memcpy DtoH]                   |

| 0.04  | 58.662ms   | 66     | 888.81 us        | device_io_accum_c2_idx_kernel        |

| 0.02  | 29.548ms   | 264    | 111.92 us        | device_io_accumz_kernel              |

| 0.01  | 21.758ms   | 65     | 334.74 us        | device_meteo_precompute_kernel       |

| 0.01  | 18.899ms   | 520    | 36.34 us         | device_meteo_vdrydep_kernel          |

| 0.01  | 15.101ms   | 65     | 232.32 us        | device_meteo_scale_part1_kernel      |

| 0.01  | 7.7082ms   | 65     | 118.59 us        | device_meteo_divu_kernel             |

| 0.00  | 3.3987ms   | 462    | 7.35 us          | device_io_thick_b_kernel             |

| 0.00  | 2.5924ms   | 65     | 39.88 us         | device_meteo_terrvel_kernel          |

| 0.00  | 1.4124ms   | 65     | 21.72 us         | device_meteo_vdiffusion_const_kernel |

| 0.00  | 1.3494ms   | 65     | 20.76 us         | device_meteo_hdiffusion_const_kernel |

| 0.00  | 484.98us   | 66     | 7.34 us          | device_io_thick_a_kernel             |

| 0.00  | 325.15us   | 66     | 4.92 us          | device_io_thick_c_kernel             |

| 0.00  | 261.27us   | 65     | 4.01 us          | device_meteo_prate_kernel            |

**Table 4.3:** WARIS-Transport GPU profile with *nvprof* using 1 K80 in Minotauro. Caulle-0.25-8bin 121x121x64dataset.

accounts for the execution time of kernels in the GPU and therefore is not representative of the time spent in the CPU.

We can see that *device\_maingrid\_adv\_kernel* is responsible for the 67.06% of executing time in the GPU, a little bit less than the original 78.81% in Table 4.1. One possible explanation to this change is that our ADR kernel is more optimized than other kernels and therefore the relative weight of ADR is diminished.

Another important thing to remark is how huge device\_meteo\_vsettling\_kernel is with respect to the other kernels; only 520 calls and accounts for 10% of the exec time. Another important thing we achieved is that memory coherency operations (shown as *CUDA memcpy HtoD* and *CUDA mempcy DtoH*)

represents less than a 0.18% of GPU executing time.

| Seq. Time (s) | Kernel Time (s) | Kernel Speedup | Name                   |

|---------------|-----------------|----------------|------------------------|

| 6778.74       | 101.38          | 66.86          | device_maingrid_adv    |

| 793.96        | 16.12           | 49.25          | device_meteo_vsettling |

| 491.71        | 5.86            | 83.85          | device_mass            |

| 196.41        | 16.57           | 11.85          | device_abc_zgnc        |

| 172.89        | 7.18            | 24.07          | device_divcorr         |

| 37.21         | 1.01            | 36.62          | device_groundaccum     |

We also calculated the speedups achieved for each CUDA kernel (see table 4.4) compared to their original implementation (compiled with *gcc* and flags -O3 and AVX vectorization enabled).

Table 4.4: Speedups of most important kernels using 1 K80 in Minotauro. Caulle-0.25-8bin 121x121x64 dataset.

### 4.7.2 CPU vs GPU Implementation

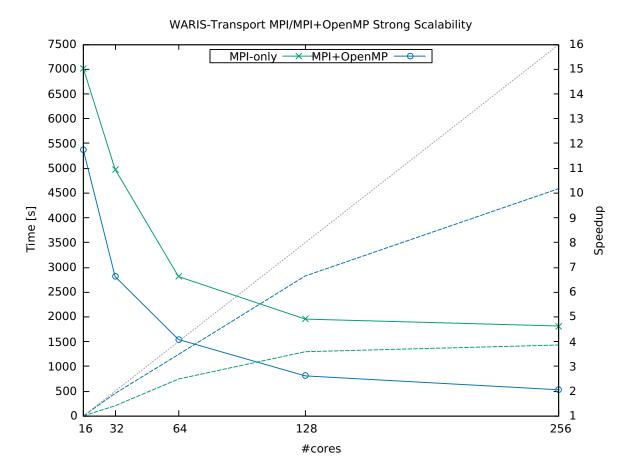

**Figure 4.12:** WARIS-Transport Strong Scalability for MPI+AVX (1 MPI rank/core) and MPI+OpenMP+AVX (1 MPI rank/node, 1 thread/core) implementations in MareNostrum. Caulle-0.05-8bin dataset (601x601x64 x 8).

In Figure 4.12 we show the execution time (solid lines) and speedups (dashed lines) of the two CPU implementations. The biggest dataset available from the Cordón-Caulle volcano (601x601x64 x 8). Since a WARIS-Transport sequential execution with the biggest dataset in MareNostrum was expected to last +24h, we considered a dual-socket MareNostrum node (two Intel Xeon CPU E5649, 8+8 cores) as the speedup baseline.

|        | Marenostrum                    |                |  |

|--------|--------------------------------|----------------|--|

| #cores | Intel Xeon CPU E5649 @ 2.53GHz |                |  |

|        | MPI-only                       | MPI+OpenMP     |  |

|        | Execution Time (Speedup)       |                |  |

| 16     | 7015.67 (1.00)                 | 5368.19 (1.00) |  |

| 32     | 4978.05 (1.41)                 | 2812.86 (1.91) |  |

| 64     | 2812.71 (2.49)                 | 1541.76 (3.48) |  |

| 128    | 1954.16 (3.59)                 | 806.81 (6.65)  |  |

| 256    | 1815.24 (3.86)                 | 527.38 (10.18) |  |

**Table 4.5:** WARIS-Transport Execution Time for MPI+AVX (1 MPI rank/core) and MPI+OpenMP+AVX (1 MPI rank/node, 1 thread/core) implementations in MareNostrum. Caulle-0.05-8bin dataset (601x601x64 x 8).

All implementations have been compiled with AVX vectorization (intrinsics). The first implementation only uses MPI with 1 MPI rank/core to scale from a two socket node (16 cores) to 16 dual-socket nodes (256 cores). The second implementation uses MPI+OpenMP (+AVX) to exploit all parallelism available. In this case we use only 1 MPI rank/node and 1 OpenMP thread/core. For completeness, in Table 4.5 we show the exact execution time and speedup achieved. We believe that the performance difference is due to the fact that WARIS framework creates 5 POSIX threads per MPI rank (Master, IO, CommUp, CommDown and Computation). Then the MPI-only implementation suffers from over-subscription (more threads than cores).

We can see that the MPI-only implementation scales slowly, and the parallel efficiency (rated as  $Par_{eff} = \frac{Speedup}{Speedup_{ideal}}$ ) falls to 70% with just 32 cores (2 nodes). We also see that the MPI+OpenMP scales better since with 16 nodes (256 cores) we still see execution time improvements but the parallel efficiency falls to 63,61%.

|       | Hulk                     | Minotauro      |  |

|-------|--------------------------|----------------|--|

| #GPUs | Tesla K40                | Tesla K80      |  |

|       | MPI+GPU                  |                |  |

|       | Execution Time (Speedup) |                |  |

| 1     | 2917.76 (1.00)           | 4192.43 (1.00) |  |

| 2     | 1632.70 (1.79)           | 1999.26 (2.09) |  |

| 3     | 1027.88 (2.84)           | 1492.30 (2.81) |  |

| 4     | 809.44 (3.61)            | 1026.86 (4.08) |  |

**Table 4.6:** WARIS-Transport Execution Time for MPI+AVX (1 MPI rank/core) and MPI+OpenMP+AVX (1 MPI rank/node, 1 thread/core) implementations in MareNostrum. Caulle-0.05-8bin dataset (601x601x64 x 8).

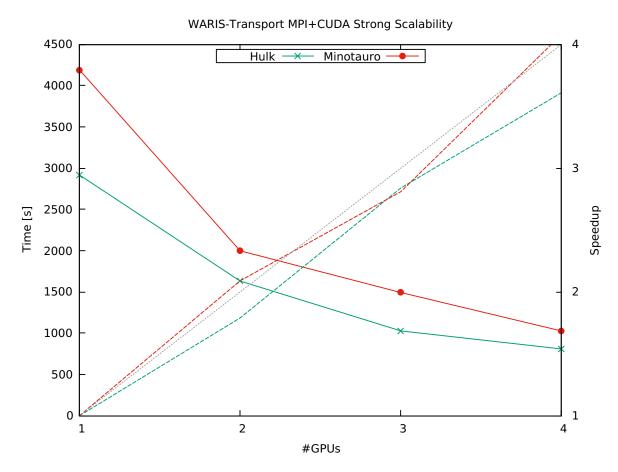

In Figure 4.13 we show the execution time (solid lines) and speedups (dashed lines) of the same GPU implementation in Hulk and Minotauro. The GPU implementation uses 1 GPU/MPI rank. Since Hulk is limited to 4 GPUs, we only used 1 Minotauro node (that contains 4 Tesla K80). Again, we provide a Table 4.6 with the exact execution time and speedup achieved. We observe that Hulk with a K40 (GK110B) is faster than Minotauro with a K80 (GK210), in part this could be explained by the fact that a GK210 has 13 SMs while a GK110B has 15 SMs (15% performance). In Hulk, the GPU implementation scales up to 4 Tesla K40 with a parallel efficiency that stays at an acceptable rate of 90% with 4 GPUs. In Minotauro, the GPU implementation also scales up to 4 Tesla K80. We observe superlinear speedup that can be an effect of GPU caches.

**Figure 4.13:** WARIS-Transport Strong Scalability for MPI+CUDA (1 MPI rank/GPU) implementation in Hulk and Minotauro. Caulle-0.05-8bin dataset (601x601x64 x 8).

If we compare the CPU and GPU implementations from Table 4.5 and Table 4.6 we can observe that an execution with 4 Tesla K40 (809.44 seconds) runs as fast as 8 MareNostrum III nodes (2x Intel Xeon CPU E5649 @ 2.53GHz) (806.81 seconds).

## Chapter 5

# PELE: Protein Energy Landscape Exploration

## 5.1 Introduction

Macro-molecular understanding of proteins is a complex task that requires long simulation times. The most widely used method is Molecular dynamics (MD), which models the molecular interactions at the atom level. MD uses empirical approximations of forces that are later integrated in time to obtain the movement of the macro-molecule. Examples of MD applications are AMBER [12], NAMD [13] or GROMACS [14].

The problem of MD simulations is that they are sensitive to the problem size and to the total time of the propagation.

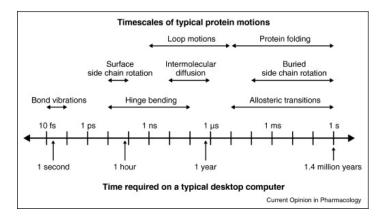

Figure 5.1: Timescales of typical protein motions [6].

In Figure 5.1 we can see the timescales required to do MD simulations. Feasible simulations are in the order of nanoseconds per day, making simulations of the order of milliseconds expensive and simulations on the scale of seconds almost impossible. To overcome this problem, researchers use statistical sampling (Monte Carlo) to get rid of the integration in time of MD applications and randomize the protein movements, achieving faster simulations.

Protein Energy Landscape Exploration (PELE [15]) is a bio-informatics application that simulates the conformation of a protein-drug interaction using a Monte Carlo algorithm. PELE generates and propagates changes in a protein-ligand system by generating a series of protein conformation positions with similar minimum energy which are combined into a trajectory by the researcher. The objective of PELE is to accelerate molecular conformation to be able to simulate difficult protein phenomenons that are hard to simulate in classical MD. To that purpose, PELE uses Monte Carlo, energy minimization algorithms and rotamer libraries for further energy minimization.

## 5.2 Application Structure

Figure 5.2: PELE algorithm for one Monte Carlo step.