# An environment for the automatic verification of digital circuits

Author: Javier de San Pedro Martín

Supervisors:

Jordi Cortadella Fortuny

Josep Carmona Vargas

Dept. de Llenguatges i Sistemes Informàtics

Facultat d'Informàtica de Barcelona

#### DADES DEL PROJECTE

Títol del projecte: An environment for the automatic verification

of digital circuits

Nom de l'estudiant: Javier de San Pedro Martín

Titulació: Enginyeria Informàtica

Crèdits: 37,5

Director: Jordi Cortadella Fortuny

Codirector: Josep Carmona Vargas

Departament: Llenguatges i Sistemes Informàtics

#### MEMBRES DEL TRIBUNAL (nom i signatura)

President: Jordi Petit Silvestre

Vocal: Carina Gibert Oliveras

Secretari: Jordi Cortadella Fortuny

## QUALIFICACIÓ

Qualificació numèrica:

Qualificació descriptiva:

Data:

#### Abstract

The aim of this project is to implement a system for the automatic verification of digital circuits written in a high-level hardware description language (Verilog), to be potentially used to assist a electronic design automation course.

It is desirable for students to be able to acquire experience with any given HDL by trying to design actual, but low complexity, circuits. However, it might not be feasible for teachers to evaluate all of the students exercises. On the other hand, giving sample test inputs and outputs is not an exhaustive method of verification that might allow hidden defects in the circuit design to go by undetected. And publishing working model circuit designs for each of the problems defeats the purpose of allowing the students to be creative in their solutions.

Therefore, we present a system where the course teachers or administrators will publish a list of problems (specifications for either sequential or combinational circuits – What should the circuit do? What are its inputs? Outputs?), along with sample correct HDL implementations of such specifications (that will not be shown to the student). Students will be able to log into the system, search for a suitable problem adjusted to their current skill level, download its specification, and try to implement it, using their favorite environment and simulation tools for the selected HDL. They might test their designs with their own test benches.

When they are comfortable enough with their design, they will be able to submit it to the system, which will model an automaton of both the student circuit and the teacher provided working one, and then compare them both, in a few seconds time. The student will then be able to see instantly if their circuit matches the specification, or if it does not. In the latter case, the system might provide an example input signals trace that causes the student's circuit to fail, at the discretion of the course administrator.

In order the reduce the scope of the work, Verilog has been selected as the HDL of choice for the project. We will not support any other HDL. Also, we will use the existing Icarus Verilog software and Jutge.org platform.

# Contents

| 1 | Bac | kground                                 | 4         |  |  |

|---|-----|-----------------------------------------|-----------|--|--|

|   | 1.1 | 1.1 Hardware Description Languages      |           |  |  |

|   |     | 1.1.1 Verilog                           | 7         |  |  |

|   |     |                                         | 12        |  |  |

|   | 1.2 | Model checking                          | 15        |  |  |

|   |     | 1.2.1 Symbolic Model Checking           | 17        |  |  |

|   |     | 1.2.2 Computation Tree Logic            | 18        |  |  |

|   |     | 1.2.3 NuSMV                             | 19        |  |  |

|   | 1.3 | Jutge.org                               | 22        |  |  |

|   | 1.4 | Previous work                           | 26        |  |  |

| 2 | Des | ign 2                                   | 29        |  |  |

|   | 2.1 | Goals                                   | 29        |  |  |

|   | 2.2 | Verilog to NuSMV conversion             | 32        |  |  |

|   |     | 2.2.1 Analysis                          | 32        |  |  |

|   |     | 2.2.2 Data model                        | 37        |  |  |

|   |     | 2.2.3 Algorithm                         | 38        |  |  |

|   | 2.3 | Jutge.org driver                        | 42        |  |  |

|   |     | 2.3.1 Circuit equivalence checking      | 45        |  |  |

| 3 | Imp | elementation                            | <b>48</b> |  |  |

|   | 3.1 | The tgt-nusmy converter                 | 48        |  |  |

|   |     | 3.1.1 Data layer                        | 49        |  |  |

|   |     | 3.1.2 Main processing                   | 50        |  |  |

|   |     | 3.1.3 Library of Parameterized Modules  | 55        |  |  |

|   | 3.2 | The Circuit Verifier Jutge.org driver   | 57        |  |  |

|   |     | 3.2.1 Problem preparation               | 57        |  |  |

|   |     | 3.2.2 Submission and correction process | 59        |  |  |

| 4            | Res   | ${ m ults}$                               | <b>62</b>  |

|--------------|-------|-------------------------------------------|------------|

|              | 4.1   | Use of the converter                      | 62         |

|              |       | 4.1.1 Examples                            | 63         |

|              |       | 4.1.2 Performance and resource usage      | 66         |

|              | 4.2   | Sample student interaction                | 68         |

|              | 4.3   | Creating a new problem                    | 74         |

| 5            | Con   | nclusions                                 | <b>7</b> 6 |

|              | 5.1   | Personal conclusions                      | 76         |

|              | 5.2   | Cost study                                | 77         |

|              | 5.3   | Future work                               | 79         |

|              |       | 5.3.1 Model readability enhancements      | 79         |

|              |       | 5.3.2 Additional language features        | 80         |

|              |       | 5.3.3 Multiple clocks                     | 80         |

|              |       | 5.3.4 More relaxed circuit specifications | 81         |

|              |       | 5.3.5 Better output messages              | 82         |

|              |       | 5.3.6 VHDL support                        | 82         |

| Bi           | bliog | graphy                                    | 83         |

| $\mathbf{G}$ | ossa  | ry                                        | 85         |

| $\mathbf{A}$ | Lan   | guage support                             | 87         |

| $\mathbf{B}$ | Env   | ironment setup                            | 89         |

# Chapter 1

# Background

## 1.1 Hardware Description Languages

A Hardware Description Language (HDL) is basically a computer language whose main mission is to convey the description of an electronic circuit.

Hardware description languages are older than what usually expected. It is widely regarded that the first language considered an HDL was the Instruction Set Processor (ISP) [1], in use since the early 70s. It was created as a way to describe the design of existing commercial processors, and, in fact, the PDP-11/45 Processor Handbook had such description in ISP [2]. Processors were becoming increasingly complex with time and old school schematics failed to provide a way to understand the design through all the meaningless noise.

Thus, the main goal of ISP was to allow for easier human comprehension of the design of larger processors. The language had many different layers of detail so that, by looking at the higher levels, what the processor did was clear to human readers. But by looking at the lower level, repetitive details, it was possible to unambiguously implement a machine identical to the one described up to the gate level.

There is no mention at all at how the actual addition is done on the counter described in listing 1.1: just an addition operator. However, clarity has improved greatly, and the intentions of the circuit designer are more clear to the reader. When the Start switch is pressed, since its on the right side of an evoke ( $\Rightarrow$ ) operation, the evaluation of the action sequence at its right side is started, and the accumulator register A is cleared. Analogously, the counter is incremented when the Increment switch is pressed.

```

Register Declarations

A \setminus Accumulator < 0.7>

Console Switches

Start.on;

Increment.on;

Interpreter

Console.activity := (Start.on \Rightarrow A \leftarrow 0);

(Increment.on \Rightarrow A \leftarrow A + 1);

```

Listing 1.1: An eight-bit digital counter in ISP

The counter snippet is also an example of why existing imperative languages could not really be used without modification as HDLs, as seen on listing 1.2.

```

char a;

for (;;) {

if (Start) {

a = 0;

}

if (Increment) {

a = a + 1;

}

}

```

Listing 1.2: Same counter in C99

On the C version, detection of both the Start and Increment buttons is sequential, that is, pressing both switches at the same time has a well-defined behavior. That is not the case on real hardware, which is essentially fully parallel. Therefore, HDLs have to take into account concurrency as a core feature of the language.

In fact, on the ISP example, the ; operator is actually a parallel composition operator: **both** statements happen at the same time. Accordingly, if the operator manages to press both front console switches at the same time, both action sequences will run, and the counter will try to reset and increment itself at the same time: the result is undefined <sup>1</sup>.

This is a fundamental concept of HDLs. In effect, the following is also

<sup>&</sup>lt;sup>1</sup>A physical design implementing such counter using a multiplexer would probably have a defined behavior though (it would either Reset or Increment). However, both designs would be valid according to what was specified in the HDL.

well defined on ISP, and virtually any HDL:

```

A \leftarrow B \; ; \; B \leftarrow A

```

On a classical imperative language, one would expect both A and B to get the original value of B. On ISP, the A and B registers contents would be swapped. If one really desires to get the imperative behaviour back, the following ISP construct would cause it:

```

A \leftarrow B; NEXT B \leftarrow A

```

With ISP-like languages, a computer instruction set could be described in a quite high level:

```

Branches and Subroutines Calling:

JMP \Rightarrow (PC \leftarrow D);

BR \Rightarrow (PC \leftarrow PC + offset);

BEQ \Rightarrow (Z \leftarrow (PC \leftarrow PC + offset));

...

```

Listing 1.3: Snippet from the PDP-11 manual[2]

Of course, it was soon realized that by adding a bit of computer-parsable structure to the language, it could be fed to simulation software and *simulate* the computer. In fact, the description of a processor in ISP already looked much like a software implementation of an interpreter for the instruction set from such processor – and there were already such simulators. Statements concerning the delays of gates were added to the language, so that simulation was more realistic (see the PREVIOUS function at [1]).

From that, the next logical step would have been for the ISP to be actually used as source to build the computer it represented, by an automated process instead of a laborious manual process. Such a process was already envisioned for at least "limited design activities" [1] in the 70s, but not for the entire circuit.

However, this changed in the 80s, with the introduction of several new, more well-defined HDLs (Abel, Verilog, VHDL, ...) as well as synthesis tools for some of them.

These days, both VHDL and Verilog share a first place in developer mind share, with many other recent additions far behind but slowly gaining acceptance (like SystemC). Most commercial synthesis tools provide support for both VHDL and Verilog, with the differences between each of them disappearing after new versions of the languages appear. Despite that, Verilog is usually regarded as a less verbose language, easier to become acquainted with than VHDL.

#### 1.1.1 Verilog

Like ISP, Verilog was also initially designed as a simulation language by then Automated Integrated Design Systems <sup>2</sup> in the early 80s. It was quickly marketed with the introduction of the Verilog-XL simulator in 1985. At around the same time, however, the United States Department of Defense was busy designing another HDL (VHDL) they would use to precisely describe the many ASICs they were sourcing from external companies, as reconstructing them from the technical manuals when the original company was long gone started to become unfeasible.

Since the Department of Defense planned to release the language specifications to the general public without any usage restrictions, Gateway believed designers would quickly favor it versus then proprietary Verilog. Therefore, on 1991 the Verilog language specification was also made freely available, and on 1994 it was proposed as the IEEE standard 1364.

Verilog has a syntax that is clearly modeled upon C's, except for the Pascal-influenced Begin, End used as block delimiters instead of the C curly brackets.

#### Structural Verilog

On Verilog, the core concept is the *module*, which can be seen as something akin to a digital circuit *component*. Much like a real world component, a module can contain other modules – even many copies of a single module, each of them called *instances*. Also, like a real world component, modules have *ports*, wires that connect the internals of the module with other components outside the module. In order to instance a component, the programmer has to indicate which wires each to connect to each of the ports in the component.

<sup>&</sup>lt;sup>2</sup>now Gateway Design Automation, one of the largest EDA companies

```

module nor3 (out, in1, in2, in3);

input in1, in2, in3;

output out;

wire or_of_123, or_of_12;

not final_not (out, or123);

or or_123 (or_of_123, or_of_12, in3);

or or_12 (or_of_12, in1, in2);

endmodule

```

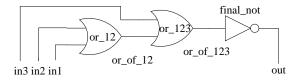

Figure 1.1: An implementation of a 3-input NOR gate using two OR and one NOT gate.

As seen on the above figure, the syntax actually resembles that of the original K&R C[3]. It is declaring a module named nor3, with out, in1, in2, in3 as ports. Where on a K&R function declaration one would write the type information for each of arguments, on a Verilog we declare whether the ports are inputs or outputs, a restriction that will be enforced by the synthesizer to both users of the module as well as its internals.

The nor3 module is built using one instance of the not module (the instance being called final\_not), and two instances of the or module (called or\_12 and or\_123), as per the following diagram:

Figure 1.2: An example synthesized circuit for the NOR3 module.

The module also contains two wire declarations, or\_of\_12 and or\_of\_123. While the first or has the 1st and 2nd inputs connected directly, there would be no way to connect the output of that or with the or\_123 that has the 3rd module input and the result of the previous or gate as inputs. Therefore, we need to declare an intermediate wire, internal to the module, that will connect both pins.

Buses are a way to aggregate multiple related wires so that many of them can be connected easily (same way a designer would combine them on a diagram instead of drawing many wires). On Verilog, this is done by specifying both the least and most significant indexes of the bus in the wire declaration:

Listing 1.4: A sample module with buses

Buses should not be confused with *arrays*, which are another kind of aggregation. Arrays are often used to implement memories, as most synthesizers allow for selection of individual items inside an array to be made with non-constant indices (i.e. using addresses coming from outside the module). Such restriction is though usually applied to buses. On the other hand, buses allow for selection of more than one item simultaneously, a feature not available while using arrays.

The language also offers an alternate syntax to implement the *nor3* module (seen at figure 1.1), where instead of explicit module instantiations, we use a shorter *continuous assignment* expression to instantiate all the required gates and realize the necessary connections:

```

module nor3 (out, in1, in2, in3);

input in1, in2, in3;

output out;

assign out = ~(in1 | in2 | in3);

endmodule

```

Listing 1.5: A less-verbose implementation of a 3-input NOR

Expressions inside continuous assignments can use the standard set of C-like operators (see table 1.1 on page 10), as well as numeric literals with a specific syntax (<size>'<base=d(ec),h(ex),b(in),o(ct)><number> - 3'd10 is decimal number 10 represented using 3 bits).

Care must be taken while using continuous assignments as a very short expression can be synthesized into thousands of gates, e.g. an arithmetic division of 64-bit buses. Moreover, undriven nets (not connected to the output of any gate) have the value  $\mathbf{x}$  (unknown), which is propagated along each operand using such value as input, causing problems if not accounted for.

| Operator  | Description                                | Example            |

|-----------|--------------------------------------------|--------------------|

|           | Bit access (to individual bits             | wire = bus[2];     |

|           | from a bus)                                | bus2 = bus[1:0];   |

| {}        | Bit concatenation (aggregates in-          | bus = $\{wire1,$   |

|           | dividual wires to create a bus)            | wire2};            |

| + - * / % | Unsigned arithmetic (can work              | bus = bus1 + bus2; |

|           | on buses; output is a bus of the           |                    |

|           | same width)                                |                    |

| > >= < <= | Unsigned relational (can work on           | wire = bus1 <=     |

|           | buses but returns a single bit)            | bus2;              |

| ! &&      | Logical (treat buses as <i>true</i> if any | flag = flag1       |

|           | of its bits is 1; return a single bit)     | flag2;             |

| ~ &       | Bitwise operations                         | busres = bus1      |

| (xor)     | -                                          | bus2;              |

| == !=     | Equality tests                             | wire = bus1 ==     |

|           | <u> </u>                                   | bus2;              |

| &   ~& ~  | Reduction (works on each of the            | nand = ~& bus;     |

|           | bits of a vector, returning a single       |                    |

|           | bit)                                       |                    |

| << >>     | Logical shift                              | buso = busi << 3;  |

| <<< >>>   | Arithmetic shift                           | buso = busi >>> 1; |

| ? :       | Conditional (ternary operator)             | res = cond ?       |

|           | , , , , , , , , , , , , , , , , , , ,      | iftrue : iffalse;  |

Table 1.1: List of Verilog operators[4]

#### Behavioral Verilog

Verilog is divided into two subsets: structural and behavioral Verilog. All of the above examples have been about structural Verilog, which virtually maps 1:1 to a gate-level description of a circuit. The other subset, behavioral, greatly simplifies the design of sequential circuits. While designers could model such circuits using flip-flop modules alone, Verilog offers an higher-level way to do it, the always block (called an always process in technical terminology).

An always block contains a set of instructions that are to be executed continually and perpetually. Commonly, this set of instructions starts with a list of events to wait for (like the rising edge of the clk signal in listing 1.6) plus a block of instructions to be executed when the event is signaled.

```

module dff (clk, q, d);

input clk, d;

output q;

reg r;

always @(posedge clk) begin

r <= d;

end

assign q = r;

endmodule</pre>

```

Listing 1.6: A simple D flip-flop implementation

Nevertheless, this is not mandatory, and an always process could have no conditions to wait on – thus always executing continually –, or could even have multiple secondary sets of events to wait after the primary one is signaled.

Assignments (<=) can appear on those instructions, but only *regs* can appear on the left side. All Verilog operators (see table 1.1) can be used on the right side – only bit access and concatenation can be used on the left side.

Similarly to ISP (see section 1.1 on page 4), such assignments are done in parallel: firstly, all of the right sides are evaluated, then the results written.

Like ISP, Verilog has a way to force an assignment to be done sequentially, by using the = operator instead of <=. However, this is usually frowned upon as it makes synthesis harder and the synthesized circuit larger.

Apart from the assignment instruction, control structures like if and while are found in the language, with the usual C syntax (except the use of Begin and End instead of curly braces). Of special interest is Verilog's case control structure,

#### Non synthesizable Verilog

Verilog has also many other features that do not map nicely to physical circuits, and are thus usually used to enhance the use of Verilog as a simulation language. For example, the initial statement, which runs code as soon as the simulation is started; or delays, which prolong the time between the evaluation of the right part and the record of the result on the left part and can be used on the same places the syntax allows wait for event (②) controls

(it is, after all, an event -x time has passed).

For example, this functionality is used to implement a module that simulates both the reset and clock signals:

```

module clkgen(clk, rst);

output clk, rst;

reg clk, rst;

// Alternate the clock every simulation cycle

always #1 clk <= ~clk;

initial begin

clk <= 0;

rst <= 0;

// Delay 50 simulation cycles, then raise rst

#50 rst <= 1;

// Delay 50 extra sim. cycles, then clear rst

#50 rst <= 0;

end

endmodule</pre>

```

Listing 1.7: A clock generation simulation-only module

Many extensions have been made to the language since its IEEE standardization on 1995. On 2001, the more modern ISO C-like syntax for declaring modules was adopted by the IEEE standard (as on listing 1.8), along with signed arithmetic operators and many additions to the system *tasks* library (which could be described as a set of functions and procedures useful in a simulation environment, like fprintf).

```

module nor3 (output out, input in1, input in2, input

in3);

assign out = ~(in1 | in2 | in3);

endmodule

```

Listing 1.8: The nor3 module in even shorter Verilog-2001 accepted syntax

### 1.1.2 Icarus Verilog

Icarus Verilog is one of the many available simulation and synthesis tools for the Verilog language. It is free and open source software, licensed under the GPL and openly developed under the guidance of its original designer, Stephen Williams, who started it around the 1990s. [5]

The design of the application is heavily modular. The frontend application (*iverilog*) accepts a backend as a command line configuration parameter. The frontend application will virtually only parse the source code. The backend has to do any synthesis work or code generation if required. Therefore, Icarus Verilog is both able to handle synthesis work, for example by using the *fpga* backend, or simulation, by using the *vvp* backend (a lower-level simulation program that is also included with the Icarus Verilog distribution).

The process used by the software is well-defined:

- 1. Source preprocessing: done by ivlpp. Handles all the Verilog language preprocessor statements.

- 2. Source parsing: done by the *ivl* frontend using the well-known Flex and Bison parser generators. Generates an abstract syntax tree.

- 3. Design elaboration: the syntax tree is converted into an elaborated design. This is a tree-like representation of the program itself, not the source. A Module root class would have each of its ports, wires, always and initial blocks as direct children.

- 4. Functors: from this point on, the process is guided by the user selected backend, which contains a set of functors small graph filters, whose input is a graph and each generate a slightly modified graph. For example, a synthesis backend might want to use the synth2 functor, that, among many other functionalities, generates a D flip-flop for each assignment inside an always block with a inferred clock signal, then removes such assignment from the tree.

- On the other hand, a simulation backend might want to use the *cprop* functor, which, as its name indicates, implements a constant propagation optimization pass.

- 5. Code generation: the backend is once again called after all processing has been done so that it can massage the resulting graph into an appropriate format. If all the synthesis functors have been called, the graph could now be printed in order to get a gate-level diagram of the design.

Backends, called *targets* in Icarus Verilog, are composed of both a text file indicating the functors to be run as well as the actual executable code (in the form of a standard shared object or dynamic link library) to run at the code generation stage. A public C API is available so that the targets can explore the elaborated design tree (after functors have been applied): it is a simple object-oriented set of accessor functions to *opaque pointers* to nodes

from the graph.

```

/* Opaque pointer to a builtin logic/gate device. */

typedef struct ivl_net_logic_s *ivl_net_logic_t;

/* All of the builtin logic types. */

typedef enum ivl_logic_e {

IVL_LO_AND

IVL_LO_NAND

6,

IVL_LO_NOR

8,

IVL_LO_NOT

9,

IVL_LO_OR

= 12,

} ivl_logic_t;

/* Gets the type of a logic device. */

extern ivl_logic_t ivl_logic_type(ivl_net_logic_t net);

/* Gets the device connected to a certain pin of this

* logic device. */

extern ivl_nexus_t ivl_logic_pin(ivl_net_logic_t net,

unsigned pin);

```

Listing 1.9: A brief snippet of the public target API

Since this project implements a Icarus Verilog target, this API will be used extensively.

While the current stable release of Verilog, at the time of writing this document, is 0.9.3, from the 0.9.x series of releases, we have decided to use 0.8.7 for this project instead because:

- The 0.8.x series is an evolution of the older Icarus Verilog codebase, which has mostly working synthesis support. However, it lacks support for most features from the newer language standards as well as some less used functionality from the current standard [6]. There will be no new features developed for this branch, only bugfixes. In spite of that, there is still some unofficial work done on it.

- The 0.9.x series are an huge improvement on language support and performance over the older series. Unfortunately, compatibility with the existing 0.8.x targets was broken, as well as the synthesis features, which did not work as well as with the 0.8 series.

- The future 0.10.x was initially expected to have mostly new features, like SystemVerilog, Analog Verilog or even VHDL support in the frontend. Nonetheless, no new work in the synthesis backend due to lack

of interest. However, the recent increasing interest in the 0.8.x series might change that.

A typical simulation session with the Icarus Verilog toolchain might be the following:

Figure 1.3: An example simulation session with Icarus Verilog

## 1.2 Model checking

When testing a complex concurrent system, for example, a large circuit designed using Verilog, and save for basic human evaluation which is slow and prone to errors, virtually the only other method that has been used is simulation, as described on the previous section.

However, simulation has its own share of problems. It is not exhaustive; it largely depends on the skill of whoever writes the test cases, which means it still largely requires human intervention. Thus, it is a lengthy process, and does not usually achieve 100% coverage of the system functionalities under test.

This is not desirable; we want to develop a system that is as automated as possible.

There is an alternate way. A circuit can be modeled as a finite state machine; after all, a idealized logical digital circuit has a few elements storing actual state information, like latches and flip-flops. All those elements compose the state variables of the model, and from the combinational logic we can deduce the rules that control transitions between states.

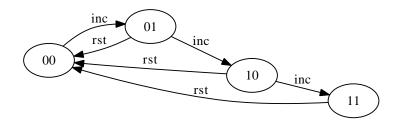

After such state machine model has been created, and since it is a finite model, we can verify certain properties. For example, we can ask if on all possible states, property P holds. Or if it holds only on states that can be directly reached from state S, and property  $\neg P$  holds on all others, where such property can be, in a example related to the state machine show on figure 1.4, 'is the counter zero?'.

We can easily implement a system checking such properties by representing the state machine as a graph like the one in 1.4, and from then on,

Figure 1.4: A two-bit counter modeled as a state machine

enumerating all the states, checking if property P applies to all of them. Enumerating all the states directly reachable from state S as well as indirectly reachable is just a matter of examining the graph connectivity.

If the system can reach a state T where property P does not hold but should according to what was described by the user, it is also easy by the checker to emit the path it had to take to reach from the initial state to T. In consequence, the user not only knows the system does not satisfy the properties it was asked for, but also the chain of states that brings it to the error condition.

Thus, one could check correctness of a system by specifying the right set of properties or specifications to check for, and then run the automated model checker. As a subbranch of such verifications, we find *equivalence checking*, where the correctness of a system is asserted by comparing it with a system that is known to be correct.

Even so, the checker system has to build a graph with all of the states of the system, which means the problem quickly gets out of hand as the number of the states increases. On a digital circuit, the maximum number of states is usually  $2^n$  where n is the accumulated size of all the state-storing elements in the circuit (flip-flops and latches).

As a consequence, while 2 bits of information means the system has 4 states (as the counter described on figure 1.4), 16 bits of information means the system has 65, 536 states, and more than four billions for a mere 32 bits of information – the well-known powers of two sequence, appropriately named the *state explosion* problem.

17

#### 1.2.1 Symbolic Model Checking

On 1992, SMV[7] was introduced, which pioneered Symbolic Model Checking: an approach to model checking that was to solve the state explosion problem by using boolean formulas to represent sets and relations between states and avoid ever having to construct the entire state graph.

This was mostly accomplished by the use of *Binary Decision Diagrams*. Those structures are used to represent boolean functions (of the kind  $\{True, False\}^k \rightarrow \{True, False\}$ , i.e. functions that work over a vector of boolean values and return a single boolean result, like AND, OR, ...gates) in an efficient form.

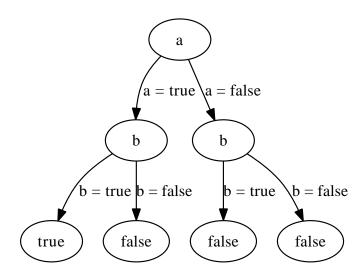

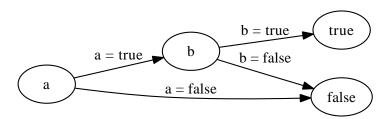

For example, if we were to build a (non-optimized) decision diagram for a classical AND-gate (defined as  $and: a, b \to a \land b$ ):

Figure 1.5: Binary decision diagram for the AND function

It can be seen that evaluating the *and* function from the diagram is just a matter of starting from the root and taking the proper path. However, the interesting aspect of BDDs is that they can be reduced into *Shared Reduced Ordered Binary Decision Diagrams*, like the one on figure 1.6.

After reduction, the diagrams are more efficiently stored. However, doing the actual reduction is a hard problem by itself (in truth, NP-Complete[8]), as it might require finding the proper ordering of all the decision branches so as to be able to create the minimal canonical version of it.

Figure 1.6: Reduced binary decision diagram for the AND function

A state model can be represented with boolean functions – whether the system is in a certain state or not can be modeled as vector of booleans, and in fact, if we are modeling a logical circuit, the entire state information from the sequential circuit is actually this vector of booleans. With that in mind, transitions between states can be modeled by a boolean function that takes two such state boolean vectors (and the current input state), and returns a boolean value indicating whether from the first state and with that input the system will jump to the second.

Kenneth L. McMillan's PhD. thesis[7] concentrated on developing a working model checker (SMV) that was capable of handling many more states than traditional checkers of the era – by using BDDs – and introduced algorithms to perform many operations on boolean functions represented as BDDs, like the union and intersection operations, allowing much of the property checking that was previously done on the state graph to be calculated without such an expensive data structure.

# 1.2.2 Computation Tree Logic

When defining properties to be checked on a state model, it was proposed that a formal logic system – like the ones used by philosophers – could be used to represent properties such as the ones described on section 1.2: 'do all the states reachable from S hold property P?'.

Computation Tree Logic (CTL) is one of the existing temporal logics, whose usage was introduced by Pnueli[9] in 1977 and which we will use extensively during this project as it is enough for our requirements.

On CTL, apart from the usual logical operators  $(\land, \lor, \neg, \ldots)$ , one can find a series of operators formed from combining a set of affixes (see table 1.2) forming a finite set of operators with a well defined meaning.

| Prefix | Meaning | Description                                           |

|--------|---------|-------------------------------------------------------|

| A      | Always  | For all the transitions from the current state $S$    |

| E      | Exists  | At least in one transition from the current state $S$ |

|        |         |                                                       |

|        |         |                                                       |

| Suffix | Meaning | Description                                           |

| Guffix |         |                                                       |

|        |         | <del>-</del>                                          |

Table 1.2: The main affixes forming CTL operators

For example, a specification consisting of AG P would mean that the specification we want to check is that "for all the transitions from the current state S, P is true in all reachable states", where S, the current state, is the initial state. Thus, we want to check that P holds for all the states.

On the other hand, EF (P  $\vee$  Q) would mean that "At least in one transition from the current state S,  $P \vee Q$  is true in a reachable state". That is, from the initial state, there is at least one path to a state T where either property P or Q will be true.

Many more advanced combinations can be created using those operators. For instance, AG (P  $\land$  (EX Q)) would mean that for all states, property P holds and a way exists to directly reach a state where property Q also holds.

One could think for example that P is a safety enforcement property ('the system is not stuck' and that Q would mean 'the system is off'. We would be enforcing that there is no state where the system is stuck and that from every state we can immediately reach a state where the system is off – after model checking, we can now be sure we would be able to shut such a complex system down.

A description on how to implement CTL checking in a symbolic model checker can be found at [7].

#### 1.2.3 **NuSMV**

NuSMV[10] is a descendant of the original SMV tool developed in 1992 by Kenneth McMillan[7]. Thus, it is a Symbolic Model Checker implementation as described on section 1.2.1. One of the best known and fastest model checkers, it is under continuous development, and since the release of version

2 of the program, also open source software under the copy-left LGPL 2 license

The latest stable version as of the writing of this report was 2.5.2.

Like most other model checking tools, it defines its own language by which to define the finite state model. The language is much more featured than a simple states list plus a dump of the state transitions, as the easiness of how complex systems where converted into finite state models was greatly priced.

On the NuSMV language, like on Verilog, the core concept is the module. Inside modules, *state variables* can be find – those represent the actual state information, and are defined under the VAR section inside the NuSMV module.

```

MODULE counter(i,rst)

VAR

c : 0..3;

ASSIGN

init(c) := 0;

next(c) := case

rst : 0;

i : c + 1;

TRUE : c;

esac:

```

Listing 1.10: The model whose state graph is show on figure 1.4

In the example on listing 1.10, we have defined a counter model with a state variable c whose type is a integer in the range between 0 and 3 inclusive. This is syntactic sugar for hiding the actual state machine: NuSMV will convert this type into raw boolean variables representing the states behind the scenes.

NuSMV has a handful of built-in types, listed in table 1.3.

State transitions are represented in the ASSIGN sections, with two clauses. The init(var) := value statement assigns the initial state for the state variable – otherwise, it is left undefined, and the checker will have to consider all states as potential initial states. In the example, the initial state for the counter is zero.

The next(var) := expr statement is the one that models the actual transition, by indicating that the value of var in the next state will be the

```

Typeboolean(ranged integer)a..b (ranged integer)(enumeration)word[n] (boolean vector of size n)array a..b of (vector of any type)

```

Table 1.3: NuSMV language built-in types

result of evaluating expr – which can reference var so that the value in the current state can be used (as well as the values of all other state variables and inputs).

In the example, one of NuSMV's most complex operators is used: the case switch. It checks each of the conditions on the left side, and returns a value that is the result of evaluating the right side of the first condition that is true.

Thus, the model will return to the initial (zero) state when rst is true, increment the counter when i is true and do not switch state at all if none of the previous conditions was true.

We have referenced the rst and i identifiers, which are from *input* parameters of the module – declared on the module header, and must be assigned actual values when instantiating the module.

To understand how those work, we must first know how NuSMV handles modules during the loading of the state machine model: NuSMV merges all of the module instantiations into a single flat one, as seen on the following snippet:

```

- Source

-Flat

MODULE main ()

MODULE main()

VAR

VAR

b: boolean;

b: boolean;

i: 3..4;

i: 3..4;

instance1_t:

instance1:

mymodule(b);

boolean;

instance2:

instance2_t:

mymodule(i);

boolean:

MODULE mymodule (in)

ASSIGN

VAR

\mathbf{next}(instance1_t) :=

t: boolean;

ASSIGN

\mathbf{next}(instance2_t) :=

\mathbf{next}(t) := in;

i ;

```

Thus, formal module arguments get textually replaced with the actual argument, like if modules were a convoluted form of C-like macro expansion. While this means we have polymorphic modules for free, whose arguments are dynamically typed, care must be taken not to do type-specific operations on the formal parameters if we can not guarantee callers will always pass in the correct type (in the above snippet, a type error will appear on next(instance2\_t) because i, an integer, cannot be casted implicitly into a boolean.

NuSMV also offers one last piece of syntactic sugar: the DEFINE statement. This acts much like an actual macro, except it is scoped to the module where it was defined. Defines are sometimes used as a output parameters, as parent modules can reference to such macros via the usual module.name notation.

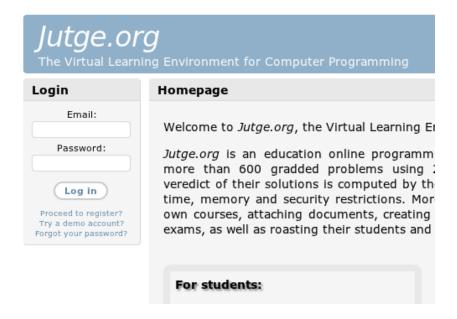

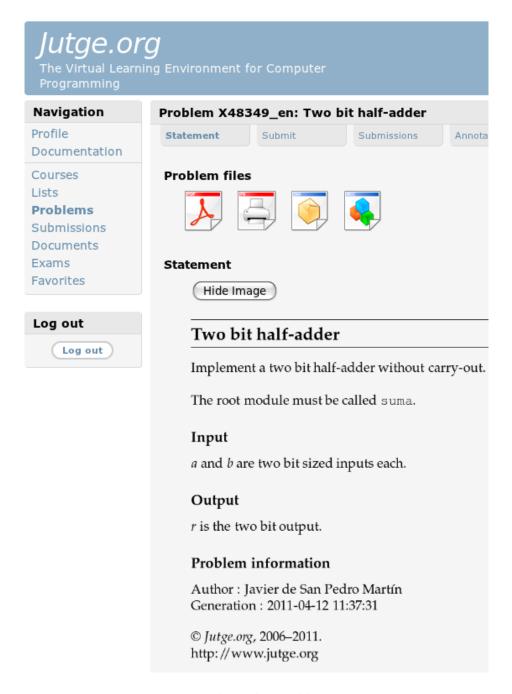

## 1.3 Jutge.org

From the Jutge.org homepage [11]:

"Jutge.org is an educational online programming judge where students can try to solve more than 600 graded problems using 20 different programming languages. The verdict of their solutions is computed by the Judge using exhaustive data sets run with time, memory and security restrictions. Moreover, instructors can use it to create their own courses, attaching documents, creating lists of problems, assignments, contests and exams, as well as roasting their students and tutors."

The software was created by Jordi Petit, Salvador Roura, and other researchers from the *Technical University of Catalonia* (UPC), initially as a way to help the evaluation tasks for the UPC Programming Contest, where around 200 contestants enrolled.

However, the idea of using the Jutge.org codebase to change the way the existing UPC introductory programming course was handled soon appeared.

Before Jutge.org, students were evaluated by their ability to write algorithms in a pseudo-code partially defined by the course staff. Since it was thought that a programming course should be graded by letting students actually program, in front of a computer, the evaluation model was changed with more frequent tests and an automated evaluation system behind the scenes allowing students to get feedback from their code as soon as possible.

Up to 250 simple C++ introductory problems were created for the use with the Jutge.org system [12].

Later on, Jutge.org was made available to a greater audience by publishing it on the www.jutge.org site. Thus, the current system was born, used widely at more than six programming courses from UPC [11]. It is also freely available to use by both students from other colleges – with a public set of problems from some of the UPC courses –, as well as interested instructors willing to allow their students use the Jutge.org system.

Use of the web application requires prior registration – name, email address, and birth year. This way, users get personalized views after logon, with the system remembering problems they have already successfully solved, their favorite compiler, enrolled courses, and so on. However, for quick checks there is a demo account everyone can use.

| ${f Verdict}$            | Description                                  |

|--------------------------|----------------------------------------------|

| Accepted $(AC)$          | Program is correct and output matches that   |

|                          | of known-good solution.                      |

| Wrong Answer $(WA)$      | The program output does not match the        |

|                          | known-good solution.                         |

| Execution Error $(EE)$   | The program crashed or was too slow.         |

| Compilation Error $(CE)$ | The compiler failed to build the program.    |

| Internal Error (IE)      | Verification failed in some unspecified way. |

Table 1.4: The important Jutge.org verdicts

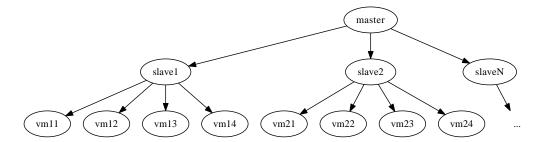

The Jutge.org system is written mostly using the PHP<sup>3</sup> language. However, some maintenance scripts are written in Python <sup>4</sup>. The system uses public, open source compilers to support each of the many available languages (for example, it uses the GNU Compiler Collection<sup>5</sup> to support C and C++).

The main web server uses the Apache<sup>6</sup> HTTP Server running under Ubuntu<sup>7</sup>. Corrections (which might involve running completely untrusted

<sup>&</sup>lt;sup>3</sup>http://www.php.net

<sup>&</sup>lt;sup>4</sup>http://www.python.org/

<sup>&</sup>lt;sup>5</sup>http://gcc.gnu.org/

<sup>&</sup>lt;sup>6</sup>http://www.apache.org/

<sup>&</sup>lt;sup>7</sup>http://www.ubuntu.com/

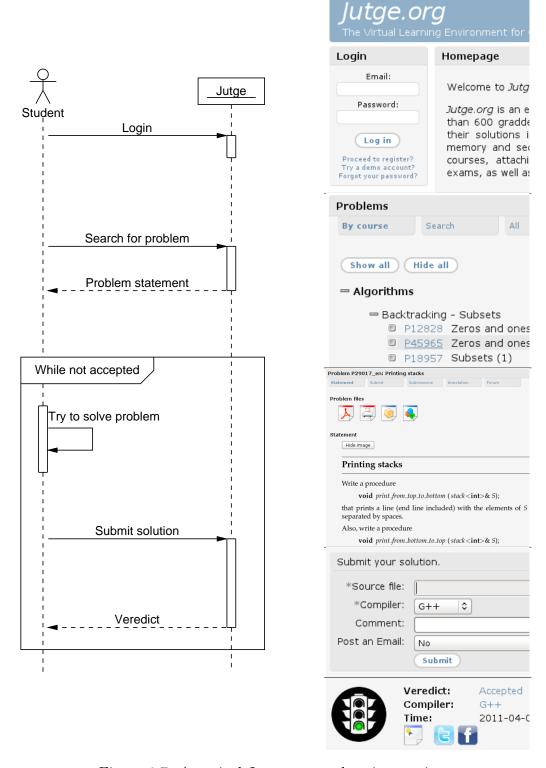

Figure 1.7: A typical Jutge.org student interaction

1.3. JUTGE.ORG 25

executable code coming from the student) are made in virtual machines, of which there might be several (up to four) per physical machine. Each virtual machine is rebooted after a few corrections are made, so that potentially unwanted state information – like compiler generated temporary files – is deleted. Submissions are evenly distributed between each of the virtual machines.

Figure 1.8: The Jutge.org architecture.

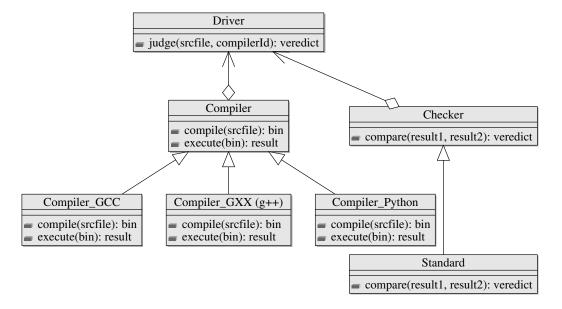

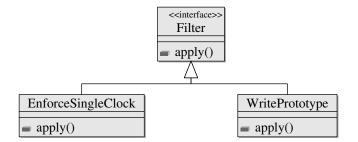

Figure 1.9: Jutge.org's Standard driver high-level class diagram

So far, Jutge.org was mostly used for imperative languages, like C, C++, Java, Python, or Perl. The support for each of these languages is abstracted under what is called a *Compiler* – a Python script that wraps the necessary scripts to launch the compiler and execute the compiled program. After the program is executed, its results are compared using a special *Checker* – that

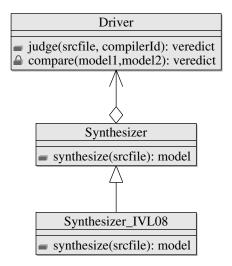

can ensure the execution results of the student submitted program match that of the teacher made program. The entire process is wrapped under what is called a *Driver*, as seen on figure 1.9.

Compilers can thus reuse the testing functionality by providing the generic layer with the execution results (its standard output). At the same time, we can reuse most of the existing web user interface while discarding the code that assumes programs are executable and its textual output is to be compared – our circuit models are not.

Thus, it makes sense for Jutge.org to be used in this project.

#### 1.4 Previous work

While there has been work done in the context of this project, we do not know of any public similar web environment. However, we will briefly look at similar Verilog formal verification tools.

Automatic formal verification of Verilog is not a new concept. In fact, there are already many available commercial solutions that implement formal equivalence checking, as listed on Xilinx's <sup>8</sup> commercial support site [13] for interested customers:

Synopsys Formality http://www.synopsys.com

Cadence Conformal http://www.cadence.com

Prover eCheck http://www.prover.com

Obviously, a commercial solution was not of interest since we would not be able to adapt it to our needs. All of the solutions are more oriented to verification as part of the development process during the different stages of a typical Field-Programmable Gate Array (FPGA) implementation flow, while on the other hand our solution must concentrate on a single implementation stage and should instead verify equivalence between different HDL implementations made by different authors.

While we did not have access to any of these tools, it is expected that such tools can do equivalence checking of multi-million gate designs in a fraction of the time needed for simulation[13] – from days or weeks to mere hours –

$<sup>^8\</sup>mathrm{Xilinx}$  is one of the biggest FPGA manufacturers, with a large stake on the electronic circuit design tools market

while also providing 100% testing coverage.

#### Confluence

Among the fewer free tools, specially interesting is *InFormal*, a open source tool developed by *Confluent* (no longer in existence) as part of their *Confluence* HDL language.

Confluence was a new HDL that would fix many of the limitations in Verilog and VHDL. However, it was not fully intended to replace Verilog, and in fact, one of the features Confluence had was its ability to emit Verilog code from a hardware description on its own language.

This was done by the fnf tool[14], which would work on the output of the Confluence synthesizer (thus, it would work on a list of nets) and from that output a structural Verilog equivalent – in a very low level fashion, as all of the high-level information that could be used to build a easier-to-read behavioral Verilog equivalent was already lost in the synthesis process.

In order to be able to do different kinds of formal verification, fnf was also able to write a NuSMV model file the same way it could output a Verilog source file: from a netlist.

Considering that and the fact that a conversion process from the Icarus Verilog synthesized output and the format used by fnf exists, this software also presented a way to transform Verilog source files into NuSMV models, which is what was packaged under the *InFormal* name as a way to aid formal verification of existing designs.

#### However,

- The software is no longer being maintained and is hard to find, and it worked only with older versions of NuSMV and Icarus.

- Since it works on a netlist level, the NuSMV models it generated would be hard to read as many of the high-level information that cannot be conveyed into a netlist is lost.

For example, all Verilog instantiations would be combined into a single large module in the destination NuSMV file, with all of the state variables merged in between with random names. Even the simplest of the circuits would generate into a enormous source file virtually impossible to understand by a human.

As verification of what the converter does is clearly one of our goals, our project shall integrate more with Icarus itself so that the system is able to access more information about the original Verilog source file, thus producing more readable NuSMV models that can be understood by a human, and even reused into other NuSMV models.

# Chapter 2

# Design

#### 2.1 Goals

The main objective of the project, as stated on the abstract, will be to implement a software system for the automatic verification of circuits written in Verilog, comparing their behavior to that of a known-good circuit using model checking.

#### This requires:

- 1. A system where teachers can store problem definitions and known-good circuits and students can download problem statements and upload their own answers in Verilog.

- 2. Automatic conversion of Verilog source files into equivalent state machine models.

- 3. Verification of whether the known-good model and the student's model behave equally.

#### We have decided that:

• We will use the existing Jutge.org environment as the website where teachers will upload problems and students will get its statements from, as well as the system where students will submit their solutions.

As per section 1.3 on page 22, Jutge.org has well-tested support for a very similar use case (exchanging Verilog circuits for computer programs in imperative languages) and is modular enough for the requirements of this project.

- NuSMV (see section 1.2.3 on page 19) will be used to perform the symbolic checking of the models.

- For the conversion of Verilog source files into models, we will develop our own Verilog to NuSMV solution, using Icarus Verilog (section 1.1.2 on page 12) as frontend. Icarus will do the parsing and initial synthesis of the design, greatly simplifying the work to be done.

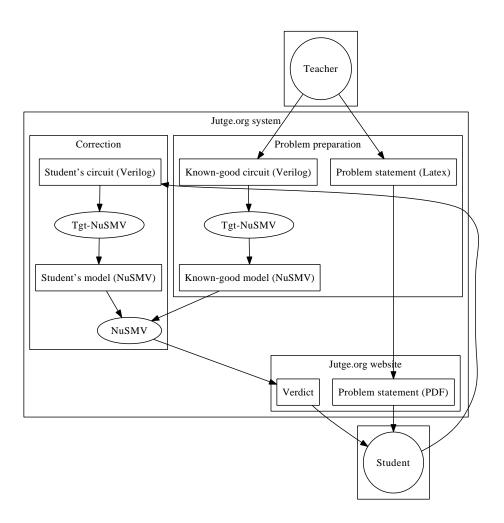

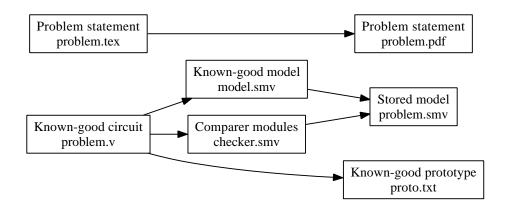

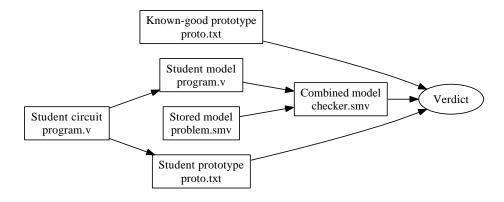

Figure 2.1: A brief look at the entire process

Following is thus the resolved list of project objectives:

1. Implement a Icarus Verilog 0.8 synthesis target that generates a NuSMV model (*tgt-nusmv* item on figure 2.1).

2.1. GOALS 31

• The most common features of the synthesizable subset from the Verilog language should be supported. We believe such a subset will allow for the most interesting problems to be solved.

- The generated models should be readable to improve verifiability by a human. Ideally, it might keep a bit of the structure from the original Verilog source file.

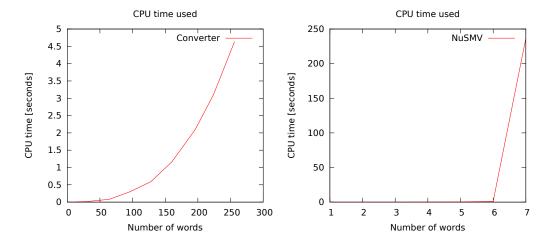

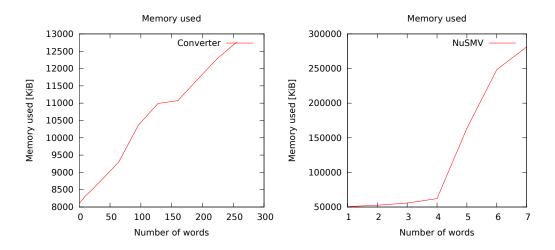

- The converter must be reasonably fast so that it can be used interactively, in a typically configured server machine.

- The generated models should also be able to be validated automatically in a reasonable time. The converter should avoid statements or NuSMV features that cause delays in the validation.

- 2. Implement a Jutge.org driver to allow for the upload and verification of Verilog circuits using the models generated by the previous tool (the *correction* system as seen on figure 2.1), as well as the necessary problem preparation routines required for the correct function of the driver (problem preparation on figure 2.1).

- The system should be fully integrated under the existing Jutge.org infrastructure. All involved components should be able to work on its servers, and the end user interface should be similarly usable.

- Human intervention in the entire student submission process should be kept to a minimum.

- Allow for integration with other languages in the future, like VHDL.

- The system will be available online so it has to be safe and reliable.

- 3. Create a small set of sample problems to test the system.

- A *problem* should consist of a brief statement and a known-good circuit to formally compare it to student submitted circuits.

- 4. Write the required project documentation and the project report.

The project work is clearly structured in two separate parts: the conversion process, and the integration with the existing Jutge.org infrastructure. We will keep this distinction for the rest of this report.

# 2.2 Verilog to NuSMV conversion

The most important part of this project is the software converting a Verilog circuit into a NuSMV model. That is, convert something like this:

```

module counter(clk, rst, i, r);

input clk, rst;

input i;

output reg [1:0] r;

always @(posedge clk)

if (rst)

r <= 0;

else if (i)

r <= r + 1;

endmodule</pre>

```

Listing 2.1: A 2 bit counter with reset

Into something like this, which is very similar to the counter example in the NuSMV tutorial[15], albeit slightly optimized and with a reset signal:

```

MODULE counter(i, rst)

VAR

value: word[2];

ASSIGN

next(value) := case

rst : 0;

i : value + 1;

TRUE : value; — Default case

```

Listing 2.2: Manually generated model for circuit in listing 2.1

## 2.2.1 Analysis

During the first part of the analysis, we will evaluate the work Icarus Verilog is doing before invoking our target, as described at section 1.1.2 on page 12, assuming its input source file is the one on listing 2.1.

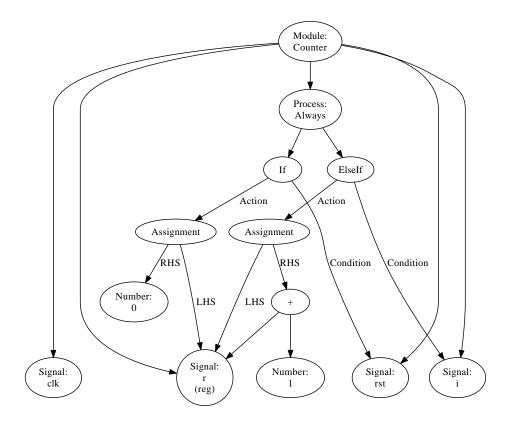

After the design elaboration stage, without any synthesis done at all (just parsing and initial elaboration), the generated graph (figure 2.2 on page 33) looks very much like an Abstract Syntax Tree (AST) – a tree representing the

Figure 2.2: Counter module elaborated design (without synthesis)

syntactic structure of the source code – and far from a real circuit. Working from this stage would require to handle all kinds of Verilog processes, primitives and operators by ourselves, which would be a huge amount of work.

Therefore, we will also configure Icarus Verilog do synthesis before invoking our target.

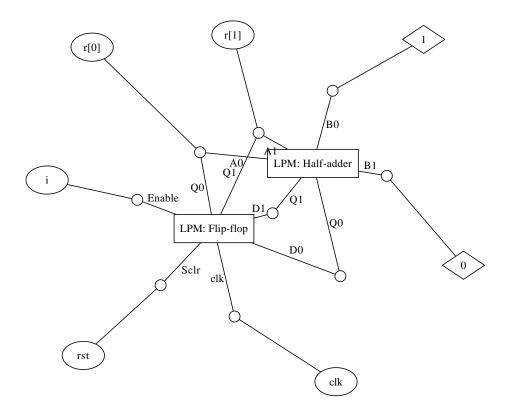

After enabling the *synth2*, *synth* and *syn-rules* functors, the graph that comes out from the synthesis process (figure 2.3 on page 34) looks quite different – resembling an actual circuit.

It is actually an *hypergraph*, where edges can connect an unlimited number of nodes – the same way a single cable can connect multiple electronic components – but represented as a multigraph, with each hyperedge being represented as a new node (a *nexus*) where all of the vertices the hyperedge connected are instead connected to the nexus.

• The ellipse shaped nodes are **signals** – the name Icarus Verilog gives

Figure 2.3: Counter module elaborated design (with synthesis)

for named nets on a module. All of the input and output ports in the original module appear as signals on the design graph.

Therefore, it is possible to accurately known what each input and output port is connected to.

• The box nodes are parametrized modules (from a Library of Parametrized Modules or LPM, thus usually known as **LPMs**). This is a quite important concept. The library contains already synthesized modules that do from the simplest of the tasks (like a multiplexer, or a decoder) to encapsulate some of the more difficult components (multipliers, divisors...). All sequential circuits synthesized by Icarus are based on two key LPMs: the D flip-flop and the D Latch.

The modules are said to be *parametrized* in that each of them has a set of configurable parameters – for example, a half-adder LPM will have a *width* configurable parameter that specifies the size of its operands. As many LPMs as required can be instantiated for any given design.

LPMs are expected to be synthesized by the code generation stage because it is assumed an usual FPGA will have some builtin components that will match with those of the Library. In which case, it is clearly desirable to use those versus a fully synthesized version that might expand to hundreds of gates. As NuSMV has lots of operands that nicely match some of the LPMs, this is also useful to us.

See table 2.1 on page 42 for the full list of LPMs used in Icarus Verilog 0.8.

- The diamond shaped nodes are **constants**. Since this a digital circuit, there is only two of them: 1 and 0. If a port from a component is always set to 1, or to 0, it will be connected to the adequate constant node.

- Not appearing in the example graph **logic gates**. Those are like LPMs except they are simpler and only have one output port (but can have 1, 2, or more input ports, as required).

As they store no information, logic gates can be represented with truth tables.

• The small circles are the **nexus**. Those are circuit interconnection points. Each of the edges connected a to a nexus convey that the correspondent electronic component pins are all of them interconnected via a cable.

These vertices are the way Icarus Verilog represents hyperedges on the elaborated design graph.

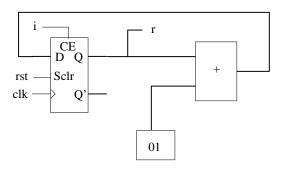

To continue with the example, we can find two LPMs on figure 2.3, which for clarity we have created a gate-level diagram of it on figure 2.4.

1. A half-adder, LPM\_ADD, with three two-bit ports:

| Name                | Description    | Connected to                                |

|---------------------|----------------|---------------------------------------------|

| $\overline{A1, A0}$ | First operand  | To the current value of the counter $(r)$ . |

| B1, B0              | Second operand | To digital 0, 1 respectively.               |

| Q1, Q0              | Result         | To the input $(D)$ of the flip-flop.        |

It is obvious that the half-adder is the component that increments the counter value – adding 01 to it.

the half-adder, as well as the

r signal.

| Name             | Description                     | Connected to                   |

|------------------|---------------------------------|--------------------------------|

| $\overline{clk}$ | Clock                           | To the clk signal.             |

| Enable           | Chip Enable                     | To the $i$ signal. Therefore,  |

|                  |                                 | the flip-flop only gets set as |

|                  |                                 | long as $i$ is raised.         |

| Sclr             | Synchronous clear: for every    | Connected to the rst input     |

|                  | clock cycle this pin is active, | port of the main module.       |

|                  | the flip-flop resets to zero.   |                                |

| D1, D0           | Flip-flop input                 | To the output of the half-     |

|                  |                                 | adder module.                  |

| Q1, Q0           | Flip-flop output                | To one of the inputs from      |

#### 2. A D flip-flop, LPM\_FF, with the following ports:

Figure 2.4: Gate-level diagram of the synthesized counter module

The amount of features a target would have to handle at this level is much smaller than with previous stages: the size of the library of parametrized modules size is reasonably small, and there are not many other kinds of nodes to be handled.

In fact, one important aspect stands up at this point from the elaborated design: in a sequential circuit, all of the circuit state information will be stored in either Flip-flop or Latch LPMs, easing the task of extracting this information in order to build the state machine model.

Thus, this is the point at the pipeline where the converter implemented in this will start its work.

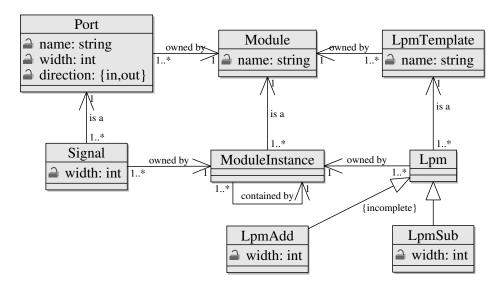

### 2.2.2 Data model

In order to improve readability, we would like the modules in the generated models to map 1:1 to Verilog modules (including input and output ports). Therefore, we need a data model to store the module definition and port structure, as well as store instances of both other modules, *LPMs* and logic gates.

This model will be built from information given by Icarus, and will be used to perform fast lookups of required data – owners of signals, all instances of a module, etc – which will be required during the conversion process.

Figure 2.5: High-level class diagram of the data model

As seen on figure 2.5, we will keep the Module as the most important component of the model. However, we will keep a distinction between a definition Module and its potentially multiple instances ModuleInstancies.

A module definition will have links to the definitions of its ports (Port), its referenced LPM definitions (LpmTemplate), and to the module definitions referenced as part of the instance declarations inside it. Analogously, a module instance (ModuleInstance) will link to the actual port instances (Signals, as seen on the elaborated design graph), LPM instances (Lpm), and each of the instantiated submodules.

Lpm is an abstract class. Each of the different LPMs from the library will have its own specialization in order to handle the differences between port configurations among the different LPMs.

The actual logical connections between LPMs, instances, etc. will be known by keeping references from our data model to the Icarus elaborated design graph.

## 2.2.3 Algorithm

With all in mind, we can start building the NuSMV model.

For each Verilog module m in the input source file:

- 1. Create a new NuSMV module m', whose identifier will be the same as the name of m.

- 2. Enumerate the input ports of m those will be the input variables of the NuSMV module m' <sup>1</sup>.

- 3. Enumerate all the child module instances of m and owned LPMs and instantiate them as state variables in the NuSMV module m'.

When writing the definition of module m', we have to provide the actual input parameters for each module instantiated by m. In the synthesized Verilog module m, connections were made for each of the ports (both input and output) that appear on the elaborated design graph.

Therefore, to generate expressions for the actual parameters the algorithm will need to traverse the elaborated design graph, starting from the input port edge until we find a device that is driving this signal and that we can express as a NuSMV expression. For example, a constant value (a literal), or a input signal of the module m – for which we can generate the expression "signalname" since we can safely assume NuSMV will know how to evaluate it as the signal name will be a valid identifiers in the scope of the module m'. We just introduced them as input parameters of m' in the previous step.

A more detailed explanation of the above process is as follows.

Assuming that:

• m is the Verilog module instance from which we are currently trying to create its equivalent NuSMV module m'.

$<sup>^{1}</sup>$ Clock signals are handled separately – see section 5.3.3 on page 80

• a is the edge in the design graph representing the input signal corresponding to the parameter we want to generate an expression for.

The expression generation algorithm we will use is:

- (a) Let A be the set of all the other edges a's nexus is directly connected to (not a itself). Abstractly, A is now the set of all edges that used to represent a single hyperedge from the elaborated design graph.

- (b) If any b in A is:

- Connected to a *const*/literal.

- An input signal of m.

- An output signal from any of the direct child instances of m (including LPMs).

Then we are done. We know that the expression is either a literal or a trivial one in the form of childmoduleinstance.port or inputsignalname, both being valid in the scope of m'.

- (c) If any b in A is connected to the output of a logic gate l, then the result is an expression of the form  $x_1$  op  $x_2$  op ... op  $x_n$  where

- $x_i$  is the result of recursively applying this algorithm but with a being the node correspondent to input i of l.

- op is the NuSMV operator equivalent to l (i.e. if l is an and gate, the equivalent operator would be &).

- (d) Otherwise, this port was not connected to any component driving it. This is most probably a mistake in the input Verilog circuit, so the system should warn the user.

- 4. Enumerate all the output ports and add them as NuSMV defines in the DEFINE section of m'.

Use the same expression generator algorithm as described above to construct the correct expressions for each of the output ports, but using this output port as starting edge a.

The elaborated design graph of the Verilog module that is the source of the NuSMV module generated in listing 2.3 can be seen in figure 2.3.

As an example, we will describe the steps made by the algorithm for the conversion of this module:

```

MODULE counter(i, rst) — The input ports

VAR

— Child module instances and LPMs

ff: lpm_ff(add.Q, i, rst);

add: lpm_add(ff.Q, 0b2_01);

DEFINE

— Output ports

r := ff.Q;

```

Listing 2.3: Sample of module generated using the above rules

1. The algorithm creates the NuSMV module counter from the Verilog module counter, the input parameters being the input ports of the Verilog module.

```

| MODULE counter(i, rst)

```

- 2. It also creates the ff and add instantiations, as they are instanced by the source Verilog module.

- 3. The ff instance of lpm\_ff has three input ports:

- $D^2$ : If we follow the D edge on graph in figure 2.3, we see that it is connected directly to the Q output of the half-adder module. This is the output port of a direct child of counter, and thus, according to the algorithm, we generate the expression add.Q and use it as actual parameter for the ff instance.

- *Enable*: connected to the i signal, which is an input port of counter. Therefore, the expression is i.

- rst: connected to the rst input port. The expression is rst.

After all the actual parameters have been determined, the state variable definition is written into the NuSMV file:

```

ff: lpm_ff(add.Q, i, rst);

```

<sup>&</sup>lt;sup>2</sup>In the design, both D and Q are a two bit buses. Since D0 and D1 are symmetrical, the same reasoning works for any of them. For simplicity we will consider them both as single-digit only.

- 4. The add instance of lpm\_add has two input ports:

- A: by the elaborated design graph, we can see that there are two other ports with connectivity to this signal: Q of ff, and A of add. The latter is discarded as it is not a literal, input of counter, output of a child of counter, or a logic gate it is an input of a child module, add. The former is accepted as it is an output port of the child module ff.

Thus, the algorithm chooses ff.Q as expression.

• B: connected to a *const*. We convert the literal into the appropriate NuSMV literal expression: 0b2\_01.

The resulting state variable is defined as follows:

```

add: lpm_add(ff.Q, 0b2_01);

```

5. In the DEFINE section, we list the output ports of the counter module. There is only one output port, r, which, per the elaborated design graph, is connected to both add. A and ff.Q. As in the previous step, the expression generation algorithm decides to use ff.Q.

```

r := ff.Q;

```

Note thus that the modules generated by this algorithm will follow a set of rules:

- Each of the Verilog module input ports will be mapped to a NuSMV module parameter.

- Each Verilog module output port will be mapped to a NuSMV module definition/alias. Thus, parent modules can refer to those by using the very readable instancename.port syntax that was referenced in the above algorithm.

Assuming the lpm\_ff and lpm\_add modules are already defined somewhere else (which they can entirely be done manually, considering the entire library consists of a handful of such modules – see table 2.1), the model on listing 2.3 is already a perfectly working equivalent of that we shown on listing 2.2 on page 32.

Ergo, the conversion process is done.

| $_{ m LPM}$                                                       | Description     |

|-------------------------------------------------------------------|-----------------|

| ADD                                                               | Full/Half-Adder |

| $\mathrm{CMP}_{-}\mathrm{EQ},\mathrm{GE},\mathrm{GT},\mathrm{NE}$ | Comparators     |

| DECODE                                                            | Decoder         |

| DEMUX                                                             | Demultiplexer   |

| DIVIDE                                                            | Divider         |

| FF                                                                | Flip-flop       |

| LATCH                                                             | Latch           |

| MOD                                                               | Modulus         |

| MULT                                                              | Multiplier      |

| MUX                                                               | Multiplexer     |

| SHIFTL, SHIFTR                                                    | Shifters        |

| SUB                                                               | Subtracter      |

| RAM                                                               | Memory          |

Table 2.1: List of LPMs

## 2.3 Jutge.org driver

The other half of this project is to build a Jutge.org driver for Verilog circuit verification, as stated on the goals. By building a driver, we will be able to leverage the work done by the Jutge.org authors and obtain a complete web frontend that satisfies our requisites – and we can concentrate on the actual verification part instead of creating Web frontend code managing problem lists, queuing, submitting solutions, etc.

In fact, the input to the driver will be the student's raw submitted code, and the output will be a *verdict* that the Jutge.org frontend will properly format and display to the student.

Thus, the external user interaction with the system will be exactly that of the original Jutge.org (see figure 1.7 on page 24), albeit with the necessary modifications to problem presentation (as for obvious reasons the statements from circuit problems will be formatted differently) as well as results viewing (since we have both different potential verdicts along with different diagnostics for each verdict).

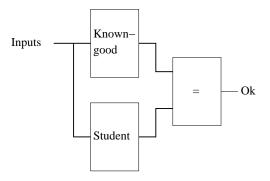

The driver will, from two Verilog source files, one coming from the student, and the other a known-good circuit coming from the teacher, run the Verilog-to-NuSMV converter on both source files to get two NuSMV models. Then, the two NuSMV models will be combined so that a unique state machine with a single "outputs match" output is created, and the NuSMV

application will be run on this model to perform the verification using CTL logic. Depending on the result of each of these stages, a verdict is given back to the student.

See figure 2.1 on page 30 for a visual representation of the internal work-flow.

We will call this driver  $\mathbf{cv}$ , which stands for *circuit verifier*. The class structure of it will be mostly identical to that of the existing Jutge.org driver, std – whose class diagram can be seen on figure 1.9 on page 25.

Unlike the *std* driver, which has to compare the outputs after running both the student and the known-good programs, our driver will always use NuSMV to check if both models match and has no need to perform any additional checking on them. Therefore, all of the different *Checker* classes have been removed from the structure.

On the other hand, we might want to add support for future languages (and thus synthesizers) in the future, so we decided to add an abstraction similar to the *Compiler* class from the original driver: the *Synthesizer* class, with one single realization – the one for Icarus Verilog 0.8, which we will call IVL08. The class diagram detailing all the relationships can be seen on figure 2.6.

Figure 2.6: cv driver architecture overview

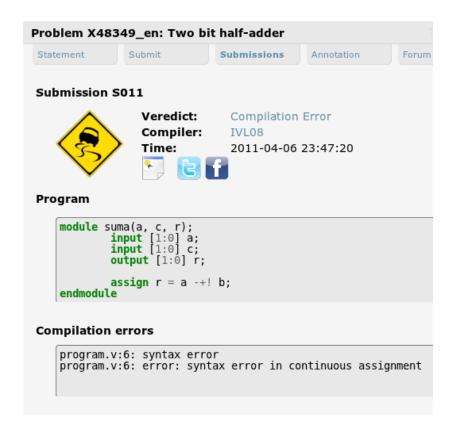

The process for the main judge function shall be (assuming the selected compiler is IVL08):

1. Launch Icarus Verilog with tgt-nusmv as target for both circuit files. Use result error codes to check if there was a synthesis error in the student file. If there was, verdict is *Compilation Error*: output the compilation error messages.

We have now built the equivalent NuSMV model for both circuits.

- 2. Ensure that both the student's and the known-good circuit externals interface is consistent: that is, both have the same inputs, outputs, module names, etc. If they are not consistent, verdict is also *Compilation Error*. An error message should tell the student what the correct interface is.

- 3. Combine both generated circuit models into a single model so that

- All inputs by the same name are connected to the same source in both models (both the known-good and the student circuit will received the same stimulus during verification).

- A comparator on the output will output whether the output from both circuits matches or not, as in the following figure:

Figure 2.7: Modeled circuit

The definition of what exactly is considered a match is left open depending on the problem definition, as described on the next section.

4. Use NuSMV to check if, in the combined circuit model built above, there is a sequence of input signals that will cause Ok to be zero.

If such input sequence exists, verdict is *Wrong Answer* – emit the full sequence that causes the student circuit to produce an output that is not equal to that of the known-good.

#### 5. Otherwise, verdict is *All Correct*.

Hence, our project has four potential causes for emitting a negative verdict – notwithstanding internal errors – which we have mapped into three existing Jutge.org verdicts <sup>3</sup> to minimize the amount of work to do on the Web frontend. Also, as per the goals, our project will give different information back to the student for certain verdicts as listed on table 2.2.

| Verdict      | Description                  | Extra information            |

|--------------|------------------------------|------------------------------|

| Accepted     | Source file was synthesized  | _                            |

|              | and the synthesized circuit  |                              |

|              | matched the required spec-   |                              |

|              | ifications.                  |                              |

| Compilation  | Source file was not valid    | List of error messages from  |

| Error        | Verilog.                     | the synthesizer.             |

|              | or                           |                              |

|              | The interface of the Verilog | List of differences from the |

|              | module did not match that    | known-good interface.        |

|              | of the known-good one.       |                              |

| Wrong Answer | Source file was synthe-      | Example of input signals se- |

|              | sized, but resulting cir-    | quence causing the circuit   |

|              | cuit did not match prob-     | to give an output that does  |

|              | lem specifications.          | not match the output the     |

|              | -                            | known-good circuit would     |

|              |                              | give.                        |

Table 2.2: All possible verdicts from the circuit verifier driver

## 2.3.1 Circuit equivalence checking