Exploració per autor "Moretó Planas, Miquel"

Ara es mostren els items 48-67 de 129

-

gem5 + rtl: A framework to enable RTL models inside a full-system simulator

López Paradís, Guillem; Armejach Sanosa, Adrià; Moretó Planas, Miquel (Association for Computing Machinery (ACM), 2021)

López Paradís, Guillem; Armejach Sanosa, Adrià; Moretó Planas, Miquel (Association for Computing Machinery (ACM), 2021)

Text en actes de congrés

Accés obertIn recent years there has been a surge of interest in designing custom accelerators for power-efficient high-performance computing. However, available tools to simulate low-level RTL designs often neglect the target system ... -

GMX: Instruction set extensions for fast, scalable, and efficient genome sequence alignment

Doblas Font, Max; Lostes Cazorla, Oscar; Aguado Puig, Quim; Cebry, Nicholas; Fontova Muste, Pau; Batten, Christopher; Marco Sola, Santiago; Moretó Planas, Miquel (Association for Computing Machinery (ACM), 2023)

Doblas Font, Max; Lostes Cazorla, Oscar; Aguado Puig, Quim; Cebry, Nicholas; Fontova Muste, Pau; Batten, Christopher; Marco Sola, Santiago; Moretó Planas, Miquel (Association for Computing Machinery (ACM), 2023)

Text en actes de congrés

Accés obertSequence alignment remains a fundamental problem in computer science with practical applications ranging from pattern matching to computational biology. The ever-increasing volumes of genomic data produced by modern DNA ... -

Graph partitioning applied to DAG scheduling to reduce NUMA effects

Sánchez Barrera, Isaac; Casas, Marc; Moretó Planas, Miquel; Ayguadé Parra, Eduard; Labarta Mancho, Jesús José; Valero Cortés, Mateo (Association for Computing Machinery (ACM), 2018)

Sánchez Barrera, Isaac; Casas, Marc; Moretó Planas, Miquel; Ayguadé Parra, Eduard; Labarta Mancho, Jesús José; Valero Cortés, Mateo (Association for Computing Machinery (ACM), 2018)

Comunicació de congrés

Accés obertThe complexity of shared memory systems is becoming more relevant as the number of memory domains increases, with different access latencies and bandwidth rates depending on the proximity between the cores and the devices ... -

HLS-based HW/SW co-design of the post-quantum classic McEliece cryptosystem

Kostalabros, Vatistas; Ribes González, Jordi; Farràs Ventura, Oriol; Moretó Planas, Miquel; Hernández Luz, Carles (Institute of Electrical and Electronics Engineers (IEEE), 2021)

Kostalabros, Vatistas; Ribes González, Jordi; Farràs Ventura, Oriol; Moretó Planas, Miquel; Hernández Luz, Carles (Institute of Electrical and Electronics Engineers (IEEE), 2021)

Text en actes de congrés

Accés obertWhile quantum computers are rapidly becoming more powerful, the current cryptographic infrastructure is imminently threatened. In a preventive manner, the U.S. National Institute of Standards and Technology (NIST) has ... -

How can we improve energy efficiency through user-directed vectorization and task-based parallelization?

Caminal, Helena; Caballero, Diego; Cebrián, Juan M.; Ferrer, Roger; Casas, Marc; Moretó Planas, Miquel; Martorell Bofill, Xavier; Valero Cortés, Mateo (Barcelona Supercomputing Center, 2015-05-05)

Caminal, Helena; Caballero, Diego; Cebrián, Juan M.; Ferrer, Roger; Casas, Marc; Moretó Planas, Miquel; Martorell Bofill, Xavier; Valero Cortés, Mateo (Barcelona Supercomputing Center, 2015-05-05)

Text en actes de congrés

Accés obertHeterogeneity, parallelization and vectorization are key techniques to improve the performance and energy efficiency of modern computing systems. However, programming and maintaining code for these architectures poses a ... -

Improving cache Behavior in CMP architectures throug cache partitioning techniques

Moretó Planas, Miquel (Universitat Politècnica de Catalunya, 2010-03-19)

Moretó Planas, Miquel (Universitat Politècnica de Catalunya, 2010-03-19)

Tesi

Accés obertThe evolution of microprocessor design in the last few decades has changed significantly, moving from simple inorder single core architectures to superscalar and vector architectures in order to extract the maximum available ... -

Improving predication efficiency through compaction/restoration of SIMD instructions

Barredo Ferreira, Adrián; Cebrián González, Juan Manuel; Moretó Planas, Miquel; Casas, Marc; Valero Cortés, Mateo (Institute of Electrical and Electronics Engineers (IEEE), 2020)

Barredo Ferreira, Adrián; Cebrián González, Juan Manuel; Moretó Planas, Miquel; Casas, Marc; Valero Cortés, Mateo (Institute of Electrical and Electronics Engineers (IEEE), 2020)

Text en actes de congrés

Accés obertVector processors offer a wide range of unexplored opportunities to improve performance and energy efficiency. However, despite its potential, vector code generation and execution have significant challenges, the most ... -

Improving scalability of task-based programs

Brumar, Iulian; Casas, Marc; Moretó Planas, Miquel (Barcelona Supercomputing Center, 2015-05-05)

Brumar, Iulian; Casas, Marc; Moretó Planas, Miquel (Barcelona Supercomputing Center, 2015-05-05)

Text en actes de congrés

Accés obertIn a multi-core era, parallel programming allows further performance improvements, but with an important programmability cost. We envision that the best approach to parallel programming that can exceed the programability, ... -

Intelligent adaptation of hardware knobs for improving performance and power consumption

Ortega Carrasco, Cristobal; Álvarez Martí, Lluc; Casas, Marc; Bertran, Ramon; Buyuktosunoglu, Alper; Eichenberger, Alexandre; Bose, Pradip; Moretó Planas, Miquel (Institute of Electrical and Electronics Engineers (IEEE), 2021-01-01)

Ortega Carrasco, Cristobal; Álvarez Martí, Lluc; Casas, Marc; Bertran, Ramon; Buyuktosunoglu, Alper; Eichenberger, Alexandre; Bose, Pradip; Moretó Planas, Miquel (Institute of Electrical and Electronics Engineers (IEEE), 2021-01-01)

Article

Accés obertCurrent microprocessors include several knobs to modify the hardware behavior in order to improve performance, power, and energy under different workload demands. An impractical and time consuming offline profiling is ... -

iQ: an efficient and flexible queue-based simulation framework

Roca, Damian; Nemirovsky, Daniel; Casas, Marc; Moretó Planas, Miquel; Valero Cortés, Mateo; Nemirovsky, Mario (Institute of Electrical and Electronics Engineers (IEEE), 2017)

Roca, Damian; Nemirovsky, Daniel; Casas, Marc; Moretó Planas, Miquel; Valero Cortés, Mateo; Nemirovsky, Mario (Institute of Electrical and Electronics Engineers (IEEE), 2017)

Text en actes de congrés

Accés obertConventional system simulators are readily used by computer architects to design and evaluate their processor designs. These simulators provide reasonable levels of accuracy and execution detail but suffer from long ... -

ITCA: Inter-Task Conflict-Aware CPU accounting for CMP

Luque, Carlos; Moretó Planas, Miquel; Cazorla Almeida, Francisco Javier; Gioiosa, Roberto; Valero Cortés, Mateo (2010)

Luque, Carlos; Moretó Planas, Miquel; Cazorla Almeida, Francisco Javier; Gioiosa, Roberto; Valero Cortés, Mateo (2010)

Text en actes de congrés

Accés obertChip-MultiProcessors (CMP) introduce complexities when accounting CPU utilization to processes because the progress done by a process during an interval of time highly depends on the activity of the other processes it is ... -

ITCA: Inter-Task Conflict-Aware CPU accounting for CMPs

Luque, Carlos; Moretó Planas, Miquel; Cazorla, Francisco; Gioiosa, Roberto; Buyuktosunoglu, Alper; Valero Cortés, Mateo (IEEE Computer Society, 2009)

Luque, Carlos; Moretó Planas, Miquel; Cazorla, Francisco; Gioiosa, Roberto; Buyuktosunoglu, Alper; Valero Cortés, Mateo (IEEE Computer Society, 2009)

Text en actes de congrés

Accés obertChip-MultiProcessor (CMP) architectures are becoming more and more popular as an alternative to the traditional processors that only extract instruction-level parallelism from an application. CMPs introduce complexities ... -

ITCA: inter-task conflict-aware CPU accounting for CMPs

Luque, Carlos; Moretó Planas, Miquel; Cazorla Almeida, Francisco Javier; Gioiosa, Roberto; Buyuktosunoglu, Alper; Valero Cortés, Mateo (IEEE Computer Society Publications, 2009)

Luque, Carlos; Moretó Planas, Miquel; Cazorla Almeida, Francisco Javier; Gioiosa, Roberto; Buyuktosunoglu, Alper; Valero Cortés, Mateo (IEEE Computer Society Publications, 2009)

Text en actes de congrés

Accés restringit per política de l'editorial -

libPRISM: an intelligent adaptation of prefetch and SMT levels

Ortega, Cristobal; Moretó Planas, Miquel; Casas, Marc; Bertran, Ramon; Buyuktosunoglu, Alper; Eichenberger, Alexandre; Bose, Pradip (Association for Computing Machinery (ACM), 2017)

Ortega, Cristobal; Moretó Planas, Miquel; Casas, Marc; Bertran, Ramon; Buyuktosunoglu, Alper; Eichenberger, Alexandre; Bose, Pradip (Association for Computing Machinery (ACM), 2017)

Text en actes de congrés

Accés obertCurrent microprocessors include several knobs to modify the hardware behavior in order to improve performance under different workload demands. An impractical and time consuming offline profiling is needed to evaluate the ... -

Microarchitectural design-space exploration of an in-order RISC-V processor in a 22nm CMOS technology

Doblas Font, Max; Wright, Andrew; Sonmez, Nehir; Moretó Planas, Miquel; Arvind (European Network of Excellence on High Performance and Embedded Architecture and Compilation (HiPEAC), 2021)

Doblas Font, Max; Wright, Andrew; Sonmez, Nehir; Moretó Planas, Miquel; Arvind (European Network of Excellence on High Performance and Embedded Architecture and Compilation (HiPEAC), 2021)

Comunicació de congrés

Accés obertThe purpose of this paper is to explore the trade-offs between IPC and maximum clock frequency in an in-order processor design. This work evaluates the impact on the performance and frequency of different pipeline ... -

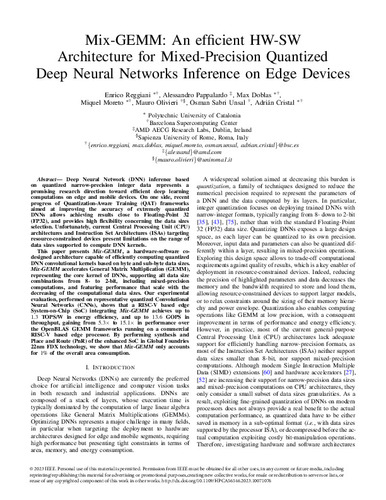

Mix-GEMM: An efficient HW-SW architecture for mixed-precision quantized deep neural networks inference on edge devices

Reggiani, Enrico; Pappalardo, Alessandro; Doblas Font, Max; Moretó Planas, Miquel; Olivieri, Mauro; Unsal, Osman Sabri; Cristal Kestelman, Adrián; Barcelona Supercomputing Center (Institute of Electrical and Electronics Engineers (IEEE), 2023)

Reggiani, Enrico; Pappalardo, Alessandro; Doblas Font, Max; Moretó Planas, Miquel; Olivieri, Mauro; Unsal, Osman Sabri; Cristal Kestelman, Adrián; Barcelona Supercomputing Center (Institute of Electrical and Electronics Engineers (IEEE), 2023)

Text en actes de congrés

Accés obertDeep Neural Network (DNN) inference based on quantized narrow-precision integer data represents a promising research direction toward efficient deep learning computations on edge and mobile devices. On one side, recent ... -

MLP-aware dynamic cache partitioning

Moretó Planas, Miquel; Cazorla Almeida, Francisco Javier; Ramírez Bellido, Alejandro; Valero Cortés, Mateo (Institute of Electrical and Electronics Engineers (IEEE), 2007)

Moretó Planas, Miquel; Cazorla Almeida, Francisco Javier; Ramírez Bellido, Alejandro; Valero Cortés, Mateo (Institute of Electrical and Electronics Engineers (IEEE), 2007)

Comunicació de congrés

Accés obertThe limitation imposed by instruction-level parallelism (ILP) has motivated the use of thread-level parallelism (TLP) as a common strategy for improving processor performance. TLP paradigms such as simultaneous multithreading ... -

Modeling and optimizing NUMA effects and prefetching with machine learning

Sánchez Barrera, Isaac; Black-Schaffer, David; Casas, Marc; Moretó Planas, Miquel; Stupnikova, Anastasiia; Popov, Mihail (Association for Computing Machinery (ACM), 2020)

Sánchez Barrera, Isaac; Black-Schaffer, David; Casas, Marc; Moretó Planas, Miquel; Stupnikova, Anastasiia; Popov, Mihail (Association for Computing Machinery (ACM), 2020)

Text en actes de congrés

Accés obertBoth NUMA thread/data placement and hardware prefetcher configuration have significant impacts on HPC performance. Optimizing both together leads to a large and complex design space that has previously been impractical to ... -

Mont-Blanc 2020: Towards scalable and power efficient European HPC processors

Armejach Sanosa, Adrià; Brank, Bine; Cortina Guardia, Jordi; Dolique, François; Hayes, Timothy; Ho, Nam; Lagadec, Pierre-Axel; Lemaire, Romain; López Paradís, Guillem; Marliac, Laurent; Moretó Planas, Miquel; Marcuello Pascual, Pedro; Pleiter, Dirk; Tan, Xubin; Derradji, Said (Institute of Electrical and Electronics Engineers (IEEE), 2021)

Armejach Sanosa, Adrià; Brank, Bine; Cortina Guardia, Jordi; Dolique, François; Hayes, Timothy; Ho, Nam; Lagadec, Pierre-Axel; Lemaire, Romain; López Paradís, Guillem; Marliac, Laurent; Moretó Planas, Miquel; Marcuello Pascual, Pedro; Pleiter, Dirk; Tan, Xubin; Derradji, Said (Institute of Electrical and Electronics Engineers (IEEE), 2021)

Text en actes de congrés

Accés obertThe Mont-Blanc 2020 (MB2020) project has triggered the development of the next generation industrial processor for Big Data and High Performance Computing (HPC). MB2020 is paving the way to the future low-power European ... -

Multicore resource management

Nesbit, Kyle J.; Smith, James E.; Moretó Planas, Miquel; Cazorla, Francisco; Ramírez Bellido, Alejandro; Valero Cortés, Mateo (2008-06)

Nesbit, Kyle J.; Smith, James E.; Moretó Planas, Miquel; Cazorla, Francisco; Ramírez Bellido, Alejandro; Valero Cortés, Mateo (2008-06)

Article

Accés obertCurrent resource management mechanisms and policies are inadequate for future multicore systems. Instead, a hardware/software interface based on the virtual private machine abstraction would allow software policies to ...