Exploració per autor "Cristal Kestelman, Adrián"

Ara es mostren els items 75-94 de 129

-

LEGaTO: Low-energy, secure, and resilient toolset for heterogeneous computing

Salami, Behzad; Parasyris, Konstantinos; Cristal Kestelman, Adrián; Unsal, Osman Sabri; Martorell Bofill, Xavier; Carpenter, Paul Matthew; De la Cruz Martínez, Raul; Bautista Gomez, Leonardo; Jiménez González, Daniel; Álvarez Martínez, Carlos; Nabavilarimi, Seyed Saber; Madonar Soria, Sergi (Institute of Electrical and Electronics Engineers (IEEE), 2020)

Salami, Behzad; Parasyris, Konstantinos; Cristal Kestelman, Adrián; Unsal, Osman Sabri; Martorell Bofill, Xavier; Carpenter, Paul Matthew; De la Cruz Martínez, Raul; Bautista Gomez, Leonardo; Jiménez González, Daniel; Álvarez Martínez, Carlos; Nabavilarimi, Seyed Saber; Madonar Soria, Sergi (Institute of Electrical and Electronics Engineers (IEEE), 2020)

Text en actes de congrés

Accés obertThe LEGaTO project leverages task-based programming models to provide a software ecosystem for Made in-Europe heterogeneous hardware composed of CPUs, GPUs, FPGAs and dataflow engines. The aim is to attain one order of ... -

LEGaTO: towards energy-efficient, secure, fault-tolerant toolset for heterogeneous computing

Cristal Kestelman, Adrián; Unsal, Osman S.; Martorell, Xavier; Carpenter, Paul Matthew; de la Cruz, Raul; Bautista Gomez, Leonardo; Jimenez, Daniel; Alvarez, Carlos; Salami, Behzad; Madonar, Sergi; Pericàs, Miquel; Trancoso, Pedro; von dem Berge, Micha; Billung-Meyer, Gunnar; Krupop, Stefan; Christmann, Wolfgang; Klawonn, Frank; Mihklafi, Amani; Becker, Tobias; Gaydadjiev, Georgi; Salomonsson, Hans; Dubhashi, Devdatt; Port, Oron; Etsion, Yoav; Nowack, Vesna; Fetzer, Christof; Hagemeyer, Jens; Jungeblut, Thorsten; Kucza, Nils; Kaiser, Martin; Porrmann, Mario; Pasin, Marcelo; Schiavoni, Valerio; Rocha, Isabelly; Göttel, Christian; Felber, Pascal (Association for Computing Machinery (ACM), 2018-05-08)

Cristal Kestelman, Adrián; Unsal, Osman S.; Martorell, Xavier; Carpenter, Paul Matthew; de la Cruz, Raul; Bautista Gomez, Leonardo; Jimenez, Daniel; Alvarez, Carlos; Salami, Behzad; Madonar, Sergi; Pericàs, Miquel; Trancoso, Pedro; von dem Berge, Micha; Billung-Meyer, Gunnar; Krupop, Stefan; Christmann, Wolfgang; Klawonn, Frank; Mihklafi, Amani; Becker, Tobias; Gaydadjiev, Georgi; Salomonsson, Hans; Dubhashi, Devdatt; Port, Oron; Etsion, Yoav; Nowack, Vesna; Fetzer, Christof; Hagemeyer, Jens; Jungeblut, Thorsten; Kucza, Nils; Kaiser, Martin; Porrmann, Mario; Pasin, Marcelo; Schiavoni, Valerio; Rocha, Isabelly; Göttel, Christian; Felber, Pascal (Association for Computing Machinery (ACM), 2018-05-08)

Comunicació de congrés

Accés obertLEGaTO is a three-year EU H2020 project which started in December 2017. The LEGaTO project will leverage task-based programming models to provide a software ecosystem for Made-in-Europe heterogeneous hardware composed of ... -

Leveraging FPGAs to accelerate the query processing of SQL-based databases

Salami, Behzad; Unsal, Osman; Cristal Kestelman, Adrián (Barcelona Supercomputing Center, 2017-05-04)

Salami, Behzad; Unsal, Osman; Cristal Kestelman, Adrián (Barcelona Supercomputing Center, 2017-05-04)

Text en actes de congrés

Accés obert -

Machine learning performance prediction model for heterogeneous systems

Nemirovsky, Daniel; Arkose, Tugberk; Unsal, Osman; Cristal Kestelman, Adrián; Valero Cortés, Mateo (Barcelona Supercomputing Center, 2017-05-04)

Nemirovsky, Daniel; Arkose, Tugberk; Unsal, Osman; Cristal Kestelman, Adrián; Valero Cortés, Mateo (Barcelona Supercomputing Center, 2017-05-04)

Text en actes de congrés

Accés obert -

MAPC: memory access pattern based controller

Hussain, Tassadaq; Palomar Pérez, Óscar; Unsal, Osman Sabri; Cristal Kestelman, Adrián; Ayguadé Parra, Eduard; Valero Cortés, Mateo (Institute of Electrical and Electronics Engineers (IEEE), 2014)

Hussain, Tassadaq; Palomar Pérez, Óscar; Unsal, Osman Sabri; Cristal Kestelman, Adrián; Ayguadé Parra, Eduard; Valero Cortés, Mateo (Institute of Electrical and Electronics Engineers (IEEE), 2014)

Text en actes de congrés

Accés restringit per política de l'editorialTraditionally, system designers have attempted to improve system performance by scheduling the processing cores and by exploring different memory system configurations and there is comparatively less work done scheduling ... -

MAPC: memory access pattern based controller

Hussain, Tassadaq; Palomar Pérez, Óscar; Unsal, Osman Sabri; Cristal Kestelman, Adrián; Ayguadé Parra, Eduard; Valero Cortés, Mateo (Institute of Electrical and Electronics Engineers (IEEE), 2014)

Hussain, Tassadaq; Palomar Pérez, Óscar; Unsal, Osman Sabri; Cristal Kestelman, Adrián; Ayguadé Parra, Eduard; Valero Cortés, Mateo (Institute of Electrical and Electronics Engineers (IEEE), 2014)

Text en actes de congrés

Accés restringit per política de l'editorialTraditionally, system designers have attempted to improve system performance by scheduling the processing cores and by exploring different memory system configurations and there is comparatively less work done scheduling ... -

Mathematical representation of the Hardware Round-Robin Scheduler analytical model for single-ISA heterogeneous architectures

Nemirovsky, Daniel; Markovic, Nikola; Unsal, Osman Sabri; Valero Cortés, Mateo; Cristal Kestelman, Adrián (Barcelona Supercomputing Center, 2015-05-05)

Nemirovsky, Daniel; Markovic, Nikola; Unsal, Osman Sabri; Valero Cortés, Mateo; Cristal Kestelman, Adrián (Barcelona Supercomputing Center, 2015-05-05)

Text en actes de congrés

Accés obert -

Memory controller for vector processor

Hussain, Tassadaq; Palomar, Oscar; Unsal, Osman Sabri; Cristal Kestelman, Adrián; Ayguadé Parra, Eduard (Springer, 2018-11)

Hussain, Tassadaq; Palomar, Oscar; Unsal, Osman Sabri; Cristal Kestelman, Adrián; Ayguadé Parra, Eduard (Springer, 2018-11)

Article

Accés obertTo manage power and memory wall affects, the HPC industry supports FPGA reconfigurable accelerators and vector processing cores for data-intensive scientific applications. FPGA based vector accelerators are used to increase ... -

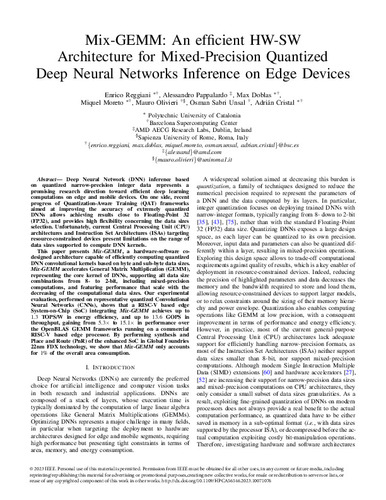

Mix-GEMM: An efficient HW-SW architecture for mixed-precision quantized deep neural networks inference on edge devices

Reggiani, Enrico; Pappalardo, Alessandro; Doblas Font, Max; Moretó Planas, Miquel; Olivieri, Mauro; Unsal, Osman Sabri; Cristal Kestelman, Adrián; Barcelona Supercomputing Center (Institute of Electrical and Electronics Engineers (IEEE), 2023)

Reggiani, Enrico; Pappalardo, Alessandro; Doblas Font, Max; Moretó Planas, Miquel; Olivieri, Mauro; Unsal, Osman Sabri; Cristal Kestelman, Adrián; Barcelona Supercomputing Center (Institute of Electrical and Electronics Engineers (IEEE), 2023)

Text en actes de congrés

Accés obertDeep Neural Network (DNN) inference based on quantized narrow-precision integer data represents a promising research direction toward efficient deep learning computations on edge and mobile devices. On one side, recent ... -

MoRS: An approximate fault modelling framework for reduced-voltage SRAMs

Yuksel, Ismail Emir; Salami, Behzad; Ergin, Oguz; Unsal, Osman Sabri; Cristal Kestelman, Adrián (2022-06)

Yuksel, Ismail Emir; Salami, Behzad; Ergin, Oguz; Unsal, Osman Sabri; Cristal Kestelman, Adrián (2022-06)

Article

Accés obertOn-chip memory (usually based on Static RAMs-SRAMs) are crucial components for various computing devices including heterogeneous devices, e.g, GPUs, FPGAs, ASICs to achieve high performance. Modern workloads such as Deep ... -

Nebelung: execution environment for transactional OpenMP

Milovanovic, M; Ferrer, Roger; Gajinov, Vladimir; Unsal, Osman Sabri; Cristal Kestelman, Adrián; Ayguadé Parra, Eduard; Valero Cortés, Mateo (2008-06)

Milovanovic, M; Ferrer, Roger; Gajinov, Vladimir; Unsal, Osman Sabri; Cristal Kestelman, Adrián; Ayguadé Parra, Eduard; Valero Cortés, Mateo (2008-06)

Article

Accés restringit per política de l'editorialFuture generations of Chip Multiprocessors (CMP) will provide dozens or even hundreds of cores inside the chip. Writing applications that benefit from the massive computational power offered by these chips is not going to ... -

NEMsCAM: A novel CAM cell based on nano-electro-mechanical switch and CMOS for energy efficient TLBs

Seyedi, Azam; Karakostas, Vasileios; Cosemans, Stefan; Cristal Kestelman, Adrián; Nemirovsky, Mario; Unsal, Osman (Institute of Electrical and Electronics Engineers (IEEE), 2015-07-10)

Seyedi, Azam; Karakostas, Vasileios; Cosemans, Stefan; Cristal Kestelman, Adrián; Nemirovsky, Mario; Unsal, Osman (Institute of Electrical and Electronics Engineers (IEEE), 2015-07-10)

Text en actes de congrés

Accés obertIn this paper we propose a novel Content Addressable Memory (CAM) cell, NEMsCAM, based on both Nano-electro-mechanical (NEM) switches and CMOS technologies. The memory component of the proposed CAM cell is designed with ... -

Object oriented execution model (OOM)

Markovic, Nikola; Nemirovsky, Daniel; González Blanco, Ruben; Unsal, Osman Sabri; Valero Cortés, Mateo; Cristal Kestelman, Adrián (INRIA, 2011)

Markovic, Nikola; Nemirovsky, Daniel; González Blanco, Ruben; Unsal, Osman Sabri; Valero Cortés, Mateo; Cristal Kestelman, Adrián (INRIA, 2011)

Text en actes de congrés

Accés obertThis paper considers implementing the Object Oriented Programming Model directly in the hardware to serve as a base to exploit object-level parallelism, speculation and heterogeneous computing. Towards this goal, we present ... -

On the resilience of deep learning for reduced-voltage FPGAs

Givaki, Kamyar; Salami, Behzad; Hojabr, Reza; Tayaranian, S. M. Reza; Khonsari, Ahmad; Rahmati, Dara; Gorgin, Saeid; Cristal Kestelman, Adrián; Unsal, Osman Sabri (Institute of Electrical and Electronics Engineers (IEEE), 2020)

Givaki, Kamyar; Salami, Behzad; Hojabr, Reza; Tayaranian, S. M. Reza; Khonsari, Ahmad; Rahmati, Dara; Gorgin, Saeid; Cristal Kestelman, Adrián; Unsal, Osman Sabri (Institute of Electrical and Electronics Engineers (IEEE), 2020)

Text en actes de congrés

Accés obertDeep Neural Networks (DNNs) are inherently computation-intensive and also power-hungry. Hardware accelerators such as Field Programmable Gate Arrays (FPGAs) are a promising solution that can satisfy these requirements for ... -

On the Resilience of RTL NN Accelerators: Fault Characterization and Mitigation

Salami, Behzad; Unsal, Osman S.; Cristal Kestelman, Adrián (IEEE, 2019-02-21)

Salami, Behzad; Unsal, Osman S.; Cristal Kestelman, Adrián (IEEE, 2019-02-21)

Comunicació de congrés

Accés obertMachine Learning (ML) is making a strong resurgence in tune with the massive generation of unstructured data which in turn requires massive computational resources. Due to the inherently compute and power-intensive structure ... -

On the selection of adder unit in energy efficient vector processing

Ratkovic, Ivan; Palomar Pérez, Óscar; Stanic, Milan; Unsal, Osman Sabri; Cristal Kestelman, Adrián; Valero Cortés, Mateo (Institute of Electrical and Electronics Engineers (IEEE), 2013)

Ratkovic, Ivan; Palomar Pérez, Óscar; Stanic, Milan; Unsal, Osman Sabri; Cristal Kestelman, Adrián; Valero Cortés, Mateo (Institute of Electrical and Electronics Engineers (IEEE), 2013)

Text en actes de congrés

Accés restringit per política de l'editorialVector processors are a very promising solution for mobile devices and servers due to their inherently energy-efficient way of exploiting data-level parallelism. Previous research on vector architectures predominantly ... -

Out-of-order commit processors

Cristal Kestelman, Adrián; Ortega, Daniel; Llosa Espuny, José Francisco; Valero Cortés, Mateo (Institute of Electrical and Electronics Engineers (IEEE), 2004)

Cristal Kestelman, Adrián; Ortega, Daniel; Llosa Espuny, José Francisco; Valero Cortés, Mateo (Institute of Electrical and Electronics Engineers (IEEE), 2004)

Text en actes de congrés

Accés obertModern out-of-order processors tolerate long latency memory operations by supporting a large number of in-flight instructions. This is particularly useful in numerical applications where branch speculation is normally not ... -

PAMS: pattern aware memory system for embedded systems

Hussain, Tassadaq; Sönmez, Nehir; Palomar Pérez, Óscar; Unsal, Osman Sabri; Cristal Kestelman, Adrián; Ayguadé Parra, Eduard; Valero Cortés, Mateo; Gursal, Shakaib A. (Institute of Electrical and Electronics Engineers (IEEE), 2015)

Hussain, Tassadaq; Sönmez, Nehir; Palomar Pérez, Óscar; Unsal, Osman Sabri; Cristal Kestelman, Adrián; Ayguadé Parra, Eduard; Valero Cortés, Mateo; Gursal, Shakaib A. (Institute of Electrical and Electronics Engineers (IEEE), 2015)

Text en actes de congrés

Accés obertIn this paper, we propose a hardware mechanism for embedded multi-core memory system called Pattern Aware Memory System (PAMS). The PAMS supports static and dynamic data structures using descriptors and specialized memory ... -

ParaDIME: Parallel distributed infrastructure for minimization of energy for data centers

Rethinagiri, Santhosh Kumar; Palomar Pérez, Óscar; Sobe, Anita; Yalcin, Gulay; Knauth, Thomas; Titos Gil, Rubén; Prieto, Pablo; Schneegaß, Malte; Cristal Kestelman, Adrián; Unsal, Osman Sabri; Felber, Pascal; Fetzer, Christof; Milojevic, Dragomir (2015-11-01)

Rethinagiri, Santhosh Kumar; Palomar Pérez, Óscar; Sobe, Anita; Yalcin, Gulay; Knauth, Thomas; Titos Gil, Rubén; Prieto, Pablo; Schneegaß, Malte; Cristal Kestelman, Adrián; Unsal, Osman Sabri; Felber, Pascal; Fetzer, Christof; Milojevic, Dragomir (2015-11-01)

Article

Accés obertDramatic environmental and economic impact of the ever increasing power and energy consumption of modern computing devices in data centers is now a critical challenge. On the one hand, designers use technology scaling as ... -

Physical vs. physically-aware estimation flow: case study of design space exploration of adders

Ratkovic, Ivan; Palomar Pérez, Óscar; Stanic, Milan; Unsal, Osman Sabri; Cristal Kestelman, Adrián; Valero Cortés, Mateo (Institute of Electrical and Electronics Engineers (IEEE), 2014)

Ratkovic, Ivan; Palomar Pérez, Óscar; Stanic, Milan; Unsal, Osman Sabri; Cristal Kestelman, Adrián; Valero Cortés, Mateo (Institute of Electrical and Electronics Engineers (IEEE), 2014)

Text en actes de congrés

Accés restringit per política de l'editorialSelecting an appropriate estimation method for a given technology and design is of crucial interest as the estimations guide future project and design decisions. The accuracy of the estimations of area, timing, and power ...