**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (<a href="www.tesisenred.net">www.tesisenred.net</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) service has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading and availability from a site foreign to the TDX service. Introducing its content in a window or frame foreign to the TDX service is not authorized (framing). This rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author

# Enhancing the Efficiency and Practicality of Software Transactional Memory on Massively Multithreaded Systems

Gökçen Kestor

Department of Computer Architecture

Universitat Politècnica de Catalunya

A thesis submitted for the degree of Doctor of Philosophy

February, 2013

| Yesterday is history. Tomorrow is a mystery. call it "The Present". | Today is a gift. That's why we  — Alice Morse Earle |

|---------------------------------------------------------------------|-----------------------------------------------------|

| Our greatest glory is not in never falling, but                     | in rising every time we fall  — Confucius           |

|                                                                     |                                                     |

#### Abstract

Chip Multithreading (CMT) processors promise to deliver higher performance by running more than one stream of instructions in parallel rather than by increasing the processor's frequency. CMT processors come with different architectures: Chip Multi-Processor (CMP), Simultaneous Multi-Threading (SMT), or a combination of them. To exploit CMT's capabilities, users have to parallelize their applications. Unfortunately, the complexity of parallel programming and the difficulty of writing efficient and correct code limit the effective use of these systems.

Transactional Memory (TM) is one of programming models that aims at simplifying synchronization by raising the level of abstraction, breaking the connection between semantic atomicity and the means by which that atomicity is achieved. Programmers indicate atomic section in the source code without explicitly locking individual shared memory locations. An underlying TM system executes such transactions concurrently whenever possible, generally by means of speculation – optimistic but checked execution, roll-backing when conflicts arise. While TM is a promising programming model to simplify synchronization among parallel threads, there are still important challenges that must be addressed to make TM more practical and efficient in mainstream parallel programming. This dissertation presents work towards improving the practicality of TM across three dimensions.

The first challenge addressed is that of making the evaluation of TM proposals more solid with realistic TM benchmarks and being able to run the same benchmarks on different STM systems. As researchers work to develop robust, mature STM, it becomes increasingly important to be able to effectively and fairly compare STM designs with benchmarks that are representative of real-world applications. To address this challenge, we first

introduce a benchmark suite, RMS-TM, a comprehensive benchmark suite to evaluate hardware and software TM implementations. RMS-TM consists of seven applications from the Recognition, Mining and Synthesis (RMS) domain that are considered representative of future workloads for multi-core systems. RMS-TM features current TM research issues such as nesting, I/O and system calls inside transactions, while also providing a mix of short and long transactions with small/large read and write sets with low/medium/high contention rates. On the other hand, most STM systems were implemented as user-level libraries: the programmer was expected to manually instrument not only transaction boundaries, but also individual loads and stores within transactions. This library-based approach was adequate for early experiments with micro-benchmarks, but it becomes increasingly tedious and error prone for larger applications. The use of different library interfaces in different research groups has also made it difficult to share applications across groups, or to make reliable performance comparisons. To enable researches to perform an "apples-to-apples" comparison, we then develop a software layer that allows researchers to test the same applications with interchangeable STM back ends.

The second challenge addressed is that of enhancing performance and scalability of TM applications running on aggressive multi-core/multi-threaded processors. Performance and scalability of current TM designs do not always meet the programmer's expectation, especially at scale. This is especially true for STM designs, where the overhead of instrumentation and transactions' management severely limits application's performance at large scale. To overcome this limitation, we propose a new STM design,  $STM^2$ , based on an assisted execution model in which time-consuming TM operations are offloaded to auxiliary threads while application threads optimistically perform computation. Surprisingly, our results show that is often more convenient to use additional processing elements to support computation rather than performance computation:  $STM^2$  provides, on average, speedups between 1.8x and 5.2x (and up to 12.8x) over state-of-the-art STM systems. Moreover, we notice that assisted-execution systems may show low processor utilization. In order to alleviate this problem and to increase the efficiency of  $STM^2$ , we

enriched  $STM^2$  with a runtime mechanism that automatically and adaptively detects application and auxiliary threads' computing demands and dynamically partition hardware resources between the pair. In order to bias the allocation of hardware resources in favor of computing intensive application threads or overloaded auxiliary threads, we leverage the hardware thread prioritization mechanism implemented in POWER machines. This dynamic mechanism further improves  $STM^2$ 's performance (up to 85% over the standard  $STM^2$  design) and efficiency.

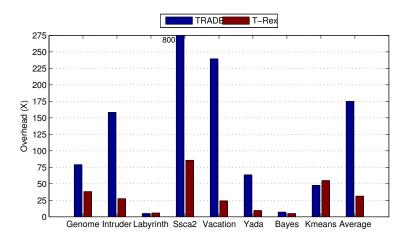

The third challenge addressed is that of defining a notion of what it means for a TM program to be correctly synchronized. Since TM has reached a maturity level and several STM and HTM implementations are available, it is important to provide debugging tools that automatically check the correctness of C/C++ TM programs. The current definition of transactional data race requires all transactions to be totally ordered "as if" serialized by a global lock, which limits scalability of TM designs. To remove this constraint, we first propose to relax the current definition of transactional data race to allow a higher level of concurrency. Based on this relaxed definition, we propose the first practical race detection algorithm for C/C++ applications, namely TRADE, and implement the corresponding race detection tool. Then, we introduce a new definition of transactional data race that is more intuitive, transparent to the underlying TM implementation, can be used for a broad set of C/C++ TM programs, enables a wide range of implementation techniques to be used. Based on this new definition, we proposed T-Rex, an efficient and scalable race detection tool for C/C++ TM applications. Using TRADE and T-Rex, we have discovered subtle transactional data races in widely-used STAMP applications which have not been reported in the past. Our experiments also show that T-Rex is order or magnitude faster than TRADE, which increase programmer productivity.

### Acknowledgements

I would like to thank my advisors, Osman Unsal, Adrian Cristal and Mateo Valero, for their sincere help and support during my graduate studies. They are not only technically solid researchers but also kind advisors.

I would also like to thank other professors who have been greatly influential to me during my Ph.D study. First, I am truly grateful to Tim Harris and Serdar Tasiran who have helped and advised me during a very decisive part of this work. I am also sincerely thankful to Michael L. Scott who guided me in the dark and taught me a lot about research and working discipline.

Without the love and support of my family, this would have been a very hard journey. They have guided me with their priceless wisdom and have always prayed for me with their heartfelt love. I thank my sister, Gokben, for giving me strength when I felt hopeless and disappointed and my mother, Serpil, without whom I would not be the person that I am today.

I would also like to thank my great friend Gulay for many years of true friendship, and for believing in me and encouraging me in this winding road. We exchanged ideas about technical problems and shared a fun time while having awesome coffees. I only regret that I did not spend more time with her.

It is the luck of my lifetime to meet Ilker and Justine and to have them as my friends. Many thanks for loyal friendship and all the unforgettable times we have spent together.

My love, my heart, my husband Roberto. Ever since I met him, my life has changed to be better, happier and brighter. I promise that I will do whatever it takes to protect a blessed life of ours. Thank him so much to support me each step of the way during my graduate studies.

# Contents

| Ι        | Int                    | roduc   | ction                                | 1          |

|----------|------------------------|---------|--------------------------------------|------------|

| 1        | Intr                   | oduct   | cion                                 | 3          |

|          | 1.1                    | The I   | Difficulty of Parallel Programming   | <br>3      |

|          | 1.2                    | Trans   | sactional Memory and Challenges      | <br>4      |

|          | 1.3                    | Contr   | ributions                            | <br>6      |

|          | 1.4                    | Organ   | nization                             | <br>8      |

|          | 1.5                    | Public  | cations                              | <br>8      |

| <b>2</b> | Tra                    | nsactio | onal Memory                          | 11         |

|          | 2.1                    | TM P    | Programming Model                    | <br>11     |

|          |                        | 2.1.1   | Semantics                            | <br>12     |

|          |                        | 2.1.2   | Programming                          | <br>13     |

|          | 2.2                    | Imple   | ementation Options                   | <br>16     |

|          |                        | 2.2.1   | Eager and Lazy Data Versioning       | <br>16     |

|          |                        | 2.2.2   | Eager and Lazy Conflict Detection    | <br>17     |

|          |                        | 2.2.3   | Software and Hardware                | <br>19     |

|          |                        | 2.2.4   | Commonly Used STMs                   | <br>21     |

| II       | C                      | ompre   | ehensive Evaluation of TM Systems    | <b>2</b> 5 |

| 3        | $\mathbf{R}\mathbf{M}$ | S-TM    | I Benchmark Suite                    | 27         |

|          | 3.1                    | Introd  | duction                              | <br>27     |

|          | 3.2                    | The T   | Transactification Process            | <br>29     |

|          |                        | 3.2.1   | Pre-Transactification Phase          | <br>29     |

|          |                        |         | 3.2.1.1 Static Pre-Transactification | <br>30     |

|   |      |         | 3.2.1.2   | Dynamic Pre-Transactification           | 32 |

|---|------|---------|-----------|-----------------------------------------|----|

|   |      | 3.2.2   | Transact  | tification Phase                        | 33 |

|   |      |         | 3.2.2.1   | STM Implementation                      | 33 |

|   |      |         | 3.2.2.2   | HTM Implementations                     | 34 |

|   | 3.3  | RMS-    | TM Over   | view                                    | 35 |

|   | 3.4  | Evalua  | ation     |                                         | 36 |

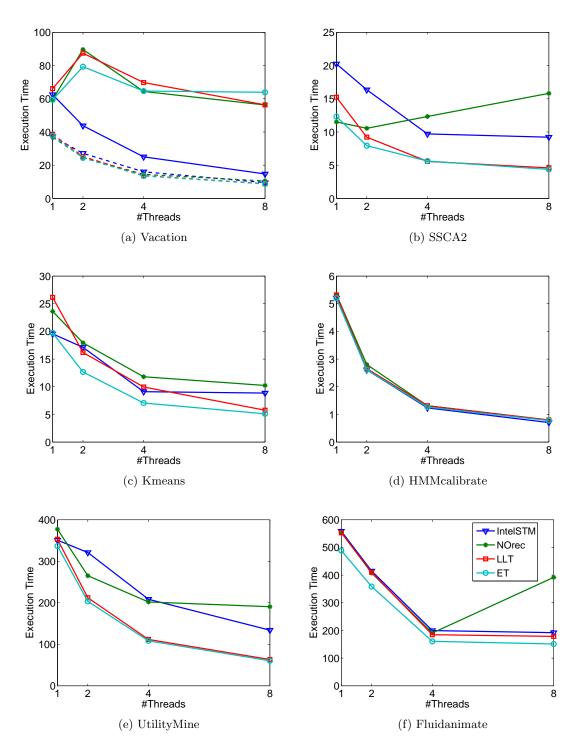

|   |      | 3.4.1   | Intel ST  | M Results                               | 36 |

|   |      |         | 3.4.1.1   | Transactional Behavior                  | 37 |

|   |      |         | 3.4.1.2   | Performance Analysis                    | 38 |

|   |      | 3.4.2   | EazyHT    | M Results                               | 40 |

|   |      |         | 3.4.2.1   | Transactional Behavior                  | 41 |

|   |      |         | 3.4.2.2   | Performance Analysis                    | 42 |

|   |      | 3.4.3   | Scalable  | TCC Results                             | 43 |

|   |      |         | 3.4.3.1   | Transactional Behavior                  | 43 |

|   |      | 3.4.4   | Compar    | ison of RMS-TM and STAMP                | 44 |

|   | 3.5  | Relate  | ed Work . |                                         | 46 |

|   | 3.6  | Conclu  | usions    |                                         | 48 |

| 4 | Inte | erchang | geable B  | Back Ends for STM Compilers             | 49 |

|   | 4.1  | Introd  | uction    |                                         | 49 |

|   | 4.2  | Design  | and Imp   | plementation                            | 51 |

|   |      | 4.2.1   | Draft Sp  | pecification for TM in C++              | 51 |

|   |      | 4.2.2   | Intel AE  | BI Overview                             | 52 |

|   |      | 4.2.3   | Design I  | Details                                 | 54 |

|   | 4.3  | Exper   | imental S | etup                                    | 55 |

|   | 4.4  | Exper   | imental R | Results                                 | 57 |

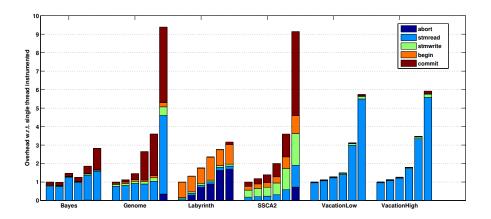

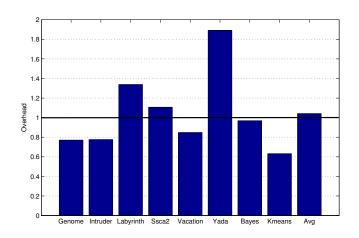

|   |      | 4.4.1   | Overhea   | d Analysis of Automatic Instrumentation | 57 |

|   |      | 4.4.2   | Back-en   | d Comparisons                           | 59 |

|   | 4.5  | Relate  | ed Work . |                                         | 64 |

|   | 4.6  | Concl   | usions    |                                         | 65 |

| II | ΙΙ  | Design and Implementation of a High Performance STM              | 1     |    | 67  |

|----|-----|------------------------------------------------------------------|-------|----|-----|

| 5  | STI | M <sup>2</sup> : A Parallel STM for High Performance SMT Systems |       |    | 69  |

|    | 5.1 | Introduction                                                     |       |    | 69  |

|    | 5.2 | Motivation                                                       |       |    | 72  |

|    | 5.3 | $STM^2$ Design and Implementation                                |       |    | 73  |

|    |     | 5.3.1 Application/Auxiliary Thread Synchronization               |       |    | 76  |

|    |     | 5.3.2 Writing to a shared memory location                        |       |    | 77  |

|    |     | 5.3.3 Reading from a shared memory location                      |       |    | 79  |

|    | 5.4 | Experimental Setup                                               |       |    | 80  |

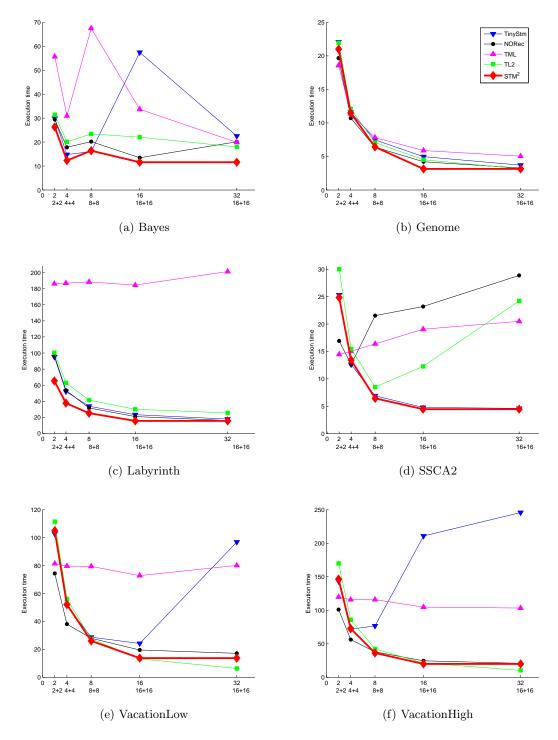

|    | 5.5 | Experimental Results                                             |       |    | 81  |

|    | 5.6 | Related Work                                                     |       |    | 87  |

|    | 5.7 | Conclusion                                                       |       |    | 88  |

| 6  | Enk | ancing the Performance of Assisted Execution Runtime Sy          | rsto: | mı | 2   |

| U  |     | ough Hardware/Software Techniques                                | 500   |    | 91  |

|    | 6.1 | Introduction                                                     |       |    | 91  |

|    | 6.2 | Hardware resource partitioning                                   |       |    | 93  |

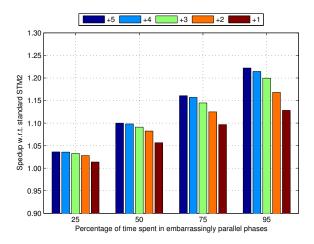

|    | 6.3 | Static Fine-Grained resource partitioning                        |       |    | 95  |

|    |     | 6.3.1 Embarrassingly parallel phases                             |       |    | 96  |

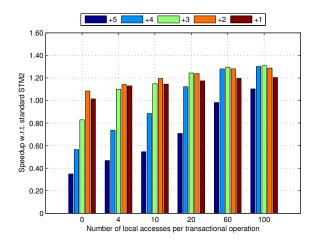

|    |     | 6.3.2 Load imbalance inside transactions                         |       |    | 99  |

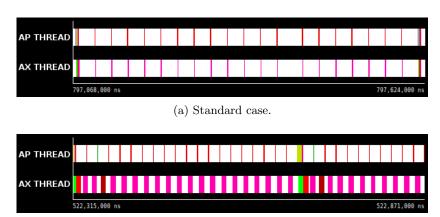

|    |     | 6.3.2.1 Overloaded application threads                           |       |    | 100 |

|    |     | 6.3.2.2 Overloaded auxiliary threads                             |       |    | 102 |

|    | 6.4 | Adaptive Fine-Grained resource partitioning                      |       |    | 106 |

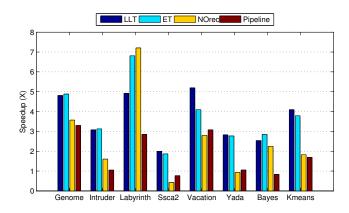

|    | 6.5 | Experimental results                                             |       |    | 112 |

|    |     | 6.5.1 Eigenbench                                                 |       |    | 113 |

|    |     | 6.5.2 STAMP applications                                         |       |    | 114 |

|    | 6.6 | Related work                                                     |       |    | 119 |

|    | 6.7 | Conclusions                                                      |       |    | 120 |

| IV | <i>'</i> C | Correctness Semantics for TM applications                 | 123   |

|----|------------|-----------------------------------------------------------|-------|

| 7  |            | ADE: Precise Dynamic Race Detection for Scalable Transact | ional |

|    | Me         | emory Systems                                             | 125   |

|    | 7.1        | Introduction                                              | 125   |

|    | 7.2        | Background                                                | 128   |

|    | 7.3        | Preliminaries                                             | 130   |

|    |            | 7.3.1 Strict Transactional Happens-Before Relation        | 130   |

|    |            | 7.3.2 Relaxed Transactional Happens-Before Relation       | 131   |

|    | 7.4        | Transactional Race Detection Algorithms                   | 135   |

|    |            | 7.4.1 s-TRADE Race Detection Algorithm                    | 136   |

|    |            | 7.4.2 TRADE Race Detection Algorithm                      | 138   |

|    |            | 7.4.3 Extensions                                          | 142   |

|    | 7.5        | Design and Implementation                                 | 143   |

|    |            | 7.5.1 Binary instrumentation Framework                    | 143   |

|    |            | 7.5.2 TRADE Instrumentation State and Code                | 143   |

|    | 7.6        | Evaluation                                                | 146   |

|    | 7.7        | Related Work                                              | 152   |

|    | 7.8        | Conclusions                                               | 153   |

| 8  |            | Rex: A Dynamic Race Detection Tool for C/C++ Transact     |       |

|    | Me         | mory Applications                                         | 155   |

|    | 8.1        | Introduction                                              | 155   |

|    | 8.2        | Motivation                                                | 157   |

|    | 8.3        | Preliminaries                                             | 160   |

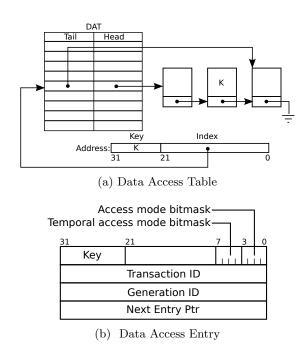

|    | 8.4        | Design and Implementation                                 | 164   |

|    |            | 8.4.1 Threads Data Access Table                           | 164   |

|    |            | 8.4.2 Non-Transactional Memory Accesses                   | 165   |

|    |            | 8.4.3 Transactional Memory Accesses                       | 166   |

|    |            | 8.4.4 <i>T-Rex</i> Race Detection                         | 167   |

|    | 8.5        | Experimental results                                      | 170   |

|    |            | 8.5.1 <i>T-Rex</i> Race Detection Coverage                | 170   |

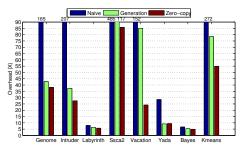

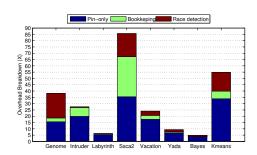

|    |            | 8.5.2 Overhead analysis                                   | 173   |

|    | 8.6        | Conclusions                                               | 175   |

## Contents

| $\mathbf{V}$ | Conclusions              | 177 |

|--------------|--------------------------|-----|

| 9            | Conclusions              | 179 |

| $\mathbf{A}$ | TRADE correctness proofs | 185 |

# List of Figures

| 2.1 | Lock-based vs. TM-based Programming                                                     | 13 |

|-----|-----------------------------------------------------------------------------------------|----|

| 2.2 | Nesting: The transaction within swap() is nested within the outer trans-                |    |

|     | action by the program control flow                                                      | 14 |

| 2.3 | Example code for the use of "retry" primitive: If the retry statement is                |    |

|     | reached, the transaction is aborted and re-executed                                     | 16 |

| 2.4 | Type of Used Transactions in Programming Languages                                      | 19 |

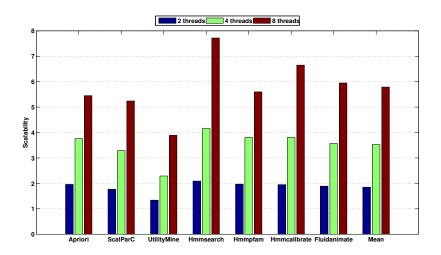

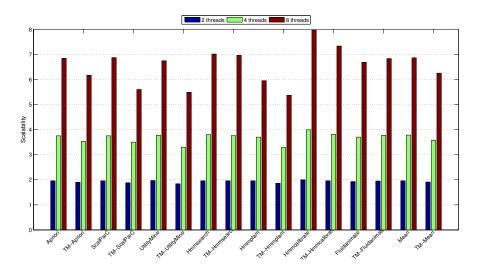

| 3.1 | Scalability of the lock-based applications, with the largest data sets,                 |    |

|     | normalized to single-threaded lock execution time                                       | 32 |

| 3.2 | Scalability of the lock-based and TM-based applications, with the largest               |    |

|     | data sets, normalized to single-threaded lock and TM execution time,                    |    |

|     | respectively, with Intel STM                                                            | 39 |

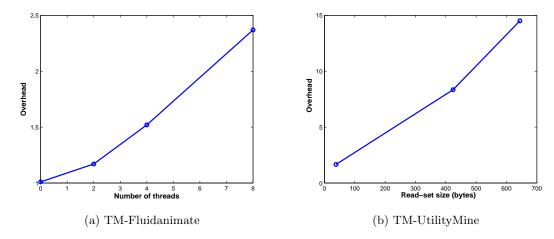

| 3.3 | Runtime overhead of $\mathit{TM-Fluidanimate}$ and $\mathit{TM-UtilityMine}$            | 40 |

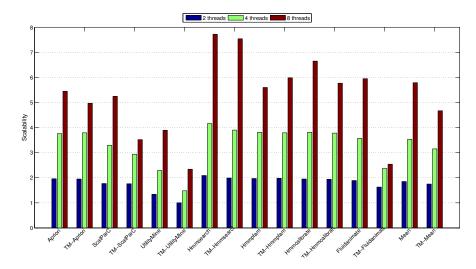

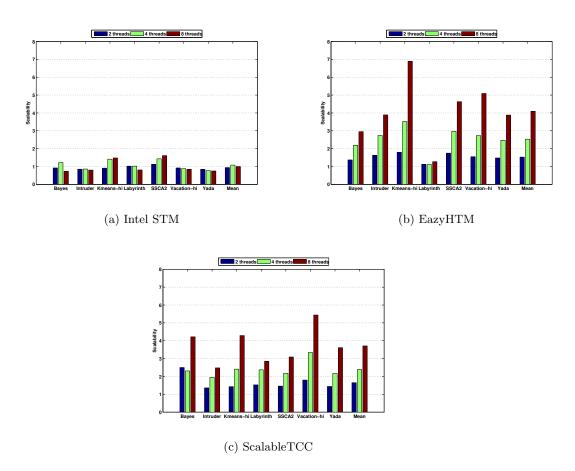

| 3.4 | Scalability of the lock-based and TM-Based applications normalized to                   |    |

|     | single-threaded lock and TM execution time, respectively, using EazyHTM.                | 42 |

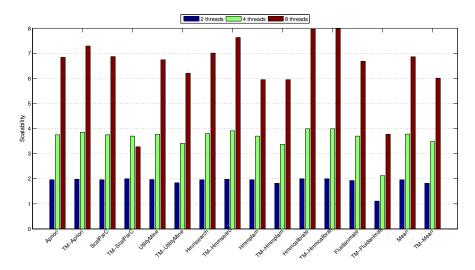

| 3.5 | Scalability of the lock-based and TM-based applications normalized to                   |    |

|     | single-threaded lock and TM execution time, respectively, with Scal-                    |    |

|     | ableTCC                                                                                 | 44 |

| 3.6 | Scalability of the STAMP applications normalized to single-threaded $\operatorname{TM}$ |    |

|     | execution time                                                                          | 45 |

| 4.1 | Automatic read/write instrumentation of a simple TM program                             | 53 |

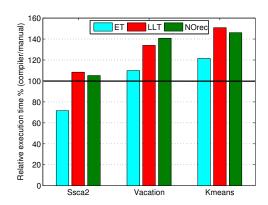

| 4.2 | Execution time of compiler-instrumented code, relative to manually in-                  |    |

|     | strumented code, for single-threaded STAMP applications                                 | 58 |

|     |                                                                                         |    |

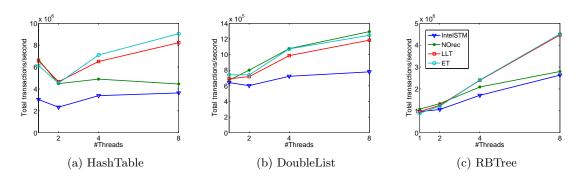

| 4.3 | Throughput results for the microbenchmarks. Y axis shows total number              |

|-----|------------------------------------------------------------------------------------|

|     | of transactions per second: higher is better                                       |

| 4.4 | Scalability results for STAMP and RMS-TM 62                                        |

| 5.1 | TinySTM per-transaction overhead breakdown for STAMP applications                  |

|     | with respect to instrumented single thread version                                 |

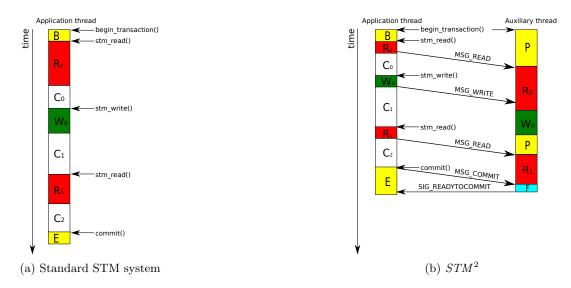

| 5.2 | $STM^2$ offloads time-consuming STM operations to sibling hardware threads. 74     |

| 5.3 | Pseudo-code for application and auxiliary thread STM write                         |

| 5.4 | Pseudo-code for application and auxiliary thread STM read 79                       |

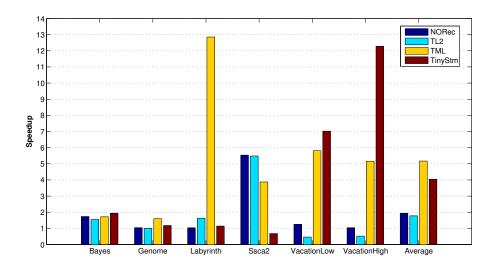

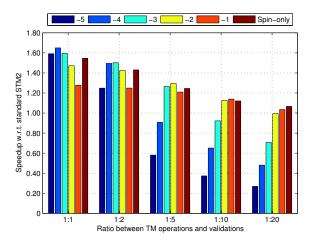

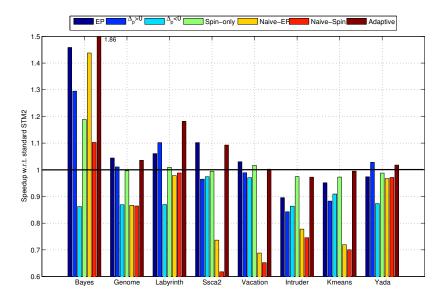

| 5.5 | Performance comparison of different STMs with STAMP benchmarks $82$                |

| 5.6 | Speedups of $STM^2$ over tested STMs for STAMP applications using the              |

|     | same amount of hardware resources (32 hardware threads) 83                         |

| 6.1 | Performance impact of reducing the priority of auxiliary threads when              |

|     | varying the percentage of time spent performing embarrassingly parallel            |

|     | computation and the value of $\Delta_p$                                            |

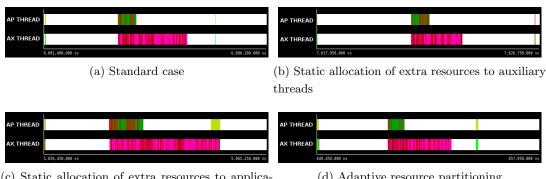

| 6.2 | Frequently idle auxiliary threads within a transaction                             |

| 6.3 | Performance impact of reducing the priority of auxiliary threads in pres-          |

|     | ence of load imbalance within transactions (overloaded application threads). $101$ |

| 6.4 | Execution trace of overloaded auxiliary threads                                    |

| 6.5 | Performance impact of increasing the priority of overloaded auxiliary              |

|     | threads when varying the number of read-set validations per transac-               |

|     | tional operation and $\Delta_p$                                                    |

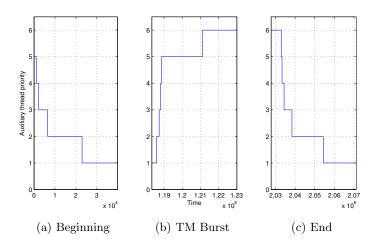

| 6.6 | Irregular transactions with bursts of transactional operations. In this            |

|     | example Eigenbench executes a burst of transactional operations in the             |

|     | middle of the transaction                                                          |

| 6.7 | The adaptive solution automatically changes the value of $AxT_p$ accord-           |

|     | ing to the structure of the transaction and the computing demand of                |

|     | application and auxiliary threads                                                  |

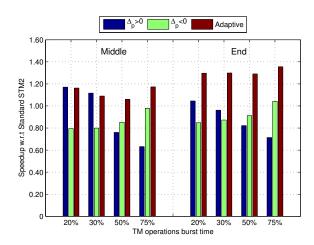

| 6.8 | Performance of static (best values among all combinations) and adap-               |

|     | tive solutions for application with not-uniform transaction structure and          |

|     | varying size/position of burst of shared accesses                                  |

| 6.9 | Performance impact of static (best values among all combinations) and              |

|     | adaptive solutions for STAMP applications                                          |

| 6.10 | Labyrinth's transactions: alternation of a large local computation phase     |     |

|------|------------------------------------------------------------------------------|-----|

|      | (white in the figure) with a burst of transactional operations (colored      |     |

|      | bars) at the end                                                             | 117 |

| 7.1  | Does ready=true imply that Thread 2 sees data=42?                            | 129 |

| 7.2  | Speedup of STAMP applications with various STMs                              | 132 |

| 7.3  | This program has a transactional data race, as Thread1 and Thread2           |     |

|      | may access x concurrently                                                    | 133 |

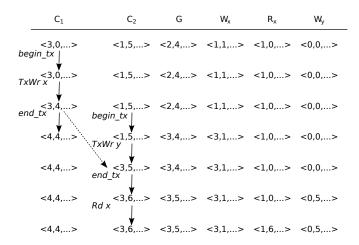

| 7.4  | Example trace for the program in Figure 7.3 running on an STM that           |     |

|      | implements SGLA. No strict transactional data races detected                 | 138 |

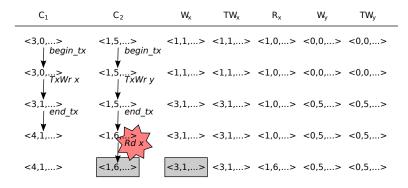

| 7.5  | Example trace for the program in Figure 7.3 running on an STM that           |     |

|      | does not implement SGLA semantics. HB detects a transactional data           |     |

|      | race in a given execution                                                    | 141 |

| 7.6  | Implementation of the TRADE algorithm                                        | 144 |

| 7.7  | SSCA2 code snapshot                                                          | 147 |

| 7.8  | TRADE runtime overhead over s-TRADE                                          | 148 |

| 8.1  | This program is intuitively racy but a race detection tool based on re-      |     |

|      | laxed transactional data race definition produces different results accord-  |     |

|      | ing to thread interleaving: if Thread 2 fully executes before Thread 1       |     |

|      | then the tool does not detect any transactional data races in a given        |     |

|      | execution                                                                    | 158 |

| 8.2  | Initially shared = true and $x$ = 0. This program is intuitively correct     |     |

|      | but may result in incorrect behavior, depending on the underlying STM        |     |

|      | $implementation. \ . \ . \ . \ . \ . \ . \ . \ . \ . \$                      | 159 |

| 8.3  | T- $Rex$ bookkeeping data structures: a) per-thread DAT; b) entry in the     |     |

|      | per-thread DAT                                                               | 165 |

| 8.4  | $T	ext{-}Rex$ overall overhead and overhead breakdown for STAMP applications | 172 |

| 8.5  | Comparing TRADE and $T$ - $Rex$ execution overhead over native execu-        |     |

|      | tion with TL2                                                                | 174 |

# List of Tables

| 3.1 | Applications that pass the Static Pre-Transactification step             | 30  |

|-----|--------------------------------------------------------------------------|-----|

| 3.2 | Percentage of time spent inside critical sections with respect to total  |     |

|     | parallel time for the lock-based applications. The data sets used are    |     |

|     | appended to the application name                                         | 31  |

| 3.3 | Basic TM characteristics (with eight threads) of the RMS-TM applica-     |     |

|     | tions, with Intel STM                                                    | 37  |

| 3.4 | Percentage of time spent inside atomic blocks with respect to total par- |     |

|     | allel time for RMS-TM applications                                       | 38  |

| 3.5 | Configuration of the simulated system                                    | 41  |

| 3.6 | Transactional behavior of the RMS-TM applications with eight threads,    |     |

|     | with EazyHTM                                                             | 41  |

| 3.7 | Transactional behavior of the RMS-TM applications with eight threads,    |     |

|     | with ScalableTCC                                                         | 43  |

| 4.1 | Abort Rates (percentage of all dynamic transaction instances that abort) |     |

|     | for 2, 4 and 8 threads                                                   | 59  |

| 6.1 | Hardware thread priority levels in the IBM POWER7 processor              | 94  |

| 7.1 | Number of transactional data races detected by TRADE and s-TRADE         |     |

|     | without and with bug-injection. $*Intruder$ crashed because of the in-   |     |

|     | jected bug.                                                              | 146 |

| 7.2 | STAMP applications' characteristics                                      | 150 |

| 7.3 | Performance comparison between TRADE running on LLT and s-TRADE          | ı   |

|     | running on Pipeline. Time in seconds                                     | 151 |

|     |                                                                          |     |

### List of Tables

| 8.1 | Number of detected transactional data races for STAMP applications for          |     |

|-----|---------------------------------------------------------------------------------|-----|

|     | the original version and a version with synthetic bugs injected. ${}^*Intruder$ |     |

|     | crashed because of the injected bug                                             | 170 |

| 8.2 | STAMP applications' characteristics                                             | 173 |

# Part I

# Introduction

Multi-core systems have the potential for significant performance improvements, but the complexity of parallel programming and the difficulty of writing efficient and correct code limit the effective use of these systems. New programming models have been proposed to ease the development of parallel applications that perform well on multi-core architectures. Transactional Memory (TM) is one of such programming models that enables programmers to perform multiple memory operations atomically without worrying about the complexity issues associated with other programming models such as locks. Chapter 1 summarizes the thesis' contributions by highlighting the new research directions taken and the main results. Chapter 2 provides the necessary background on transactional memory: its definition, properties, implementation details and design trade-offs.

## Chapter 1

# Introduction

The performance of microprocessors has been continuously improving over the years thanks to advances in manufacturing technologies. In recent years, however, conventional techniques for improving single-threaded performance have begun hitting fundamental challenges such as the limited amount of instruction-level parallelism (ILP) [159] and the undesirable levels of power consumption caused by increasing clock frequencies [7].

In response, processor manufactures have shifted to Chip Multi-threading processors (CMTs) [56, 90, 107]. Multiple simpler processor cores in CMT systems promise to deliver higher performance by running more than one stream of instructions in parallel (thread-level parallelism (TLP)) in a power-efficient manner [124]. CMT processors may come with different architectures: Chip Multi-Processor (CMP), Simultaneous Multi-Threading (SMT), or a combination of them. With wide availability of CMTs, the burden of achieving scalable performance on CMTs has now been placed on programmers who must deal with the complexity of parallel programming to take the advantages of multiprocessors/multithreading.

## 1.1 The Difficulty of Parallel Programming

To increase parallelism on CMTs, programmers should create and synchronize several parallel tasks. For shared memory systems, the synchronization of parallel tasks is commonly handled by lock-level synchronization primitives. These primitives guarantee mutually exclusive shared memory accesses among all parallel tasks in the system.

Unfortunately, parallel programming with locks is quite difficult due to the tradeoff between programming simplicity and scalability of the performance [72]. While adding coarse-grained locks to a program is relatively straightforward, it may drastically degrade performance since it introduces unnecessary serialization points during the execution. On the other hand, while fine-grained locking permits greater concurrency, its programming complexity is significantly higher, which even not result in a better performance than an equivalent coarse-grained version. The higher programming complexity may also cause various problems such as deadlock, convoying, or priority inversion [96].

### 1.2 Transactional Memory and Challenges

Transactional Memory [72] (TM) is a programming model to simplify synchronization by raising the level of abstraction, breaking the connection between semantic atomicity and the means by which that atomicity is achieved. Programmers indicate atomic sections in the source code (e.g., using language constructs such as atomic blocks, or using macros such as BEGIN\_TRANSACTION and END\_TRANSACTION) without explicitly locking individual shared memory locations. An underlying TM system executes such transactions concurrently whenever possible, generally by means of speculation—optimistic but checked execution, with rollback and retry when conflicts arise. There have been significant efforts to develop hardware (HTM) [42, 63], software (STM) [39, 43, 133] or hybrid TM systems [40, 91, 114].

While TM is a promising programming model to simplify the synchronization among parallel threads, there are still main important challenges that must be addressed to make TM more practical and efficient in mainstream parallel programming. First, realistic TM benchmarks and additional auxiliary software should be provided to make the evaluation of TM proposals more solid. Current benchmarks used to analyze the TM proposals do not include realistic applications that address ongoing TM research issues such as handling nested transactions, I/O operations, system and library calls inside transactions, and that provide the potential for straightforward comparison against locks. Thus, it is important to understand performance bottlenecks of TM on real applications and enable TM researchers to conduct their research by using changeling benchmarks. Moreover, most STM systems were implemented as user-level libraries:

the programmer was expected to manually instrument not only the transaction boundaries, but also individual loads and stores within the transactions. This library-based approach was adequate for early experiments with micro-benchmarks, but it becomes increasingly tedious and error prone for larger applications [37]. The use of different library interfaces in different research groups has also made it difficult to share applications across groups, or to make reliable performance comparisons: experiments with different versions of the application source code inevitably raise the questions of fairness and confidence. For C++ on the x86 architectures, significant steps in this direction have been made by compilers from Intel, the University of Dresden, and the GNU Project, which aim to accept the same application programming interface (API) and target the same runtime application binary interface (ABI). Unfortunately, these three compilers currently connect to only two main STM libraries (SkySTM [95] and TinySTM [133]). In the interest of greater interoperability, it is important to make works on STM systems compatible with recent compilers.

Second, it is essential to design a TM system for high performance, aggressive multithreading systems. Most STM systems, so far, suffer from poor performance because the overhead introduced by the STM runtime system outweighs the performance gain achieved by the parallelism [24]. Some authors report drastic slow-downs when using STM (e.g., only breaking even with optimized sequential code after using 8 cores [24]). Even state-of-the-art TM systems typically require at least two threads to achieve performance that matches the performance of the optimized sequential code [39, 68]. To achieve the best possible performance on systems with the increasing number of cores/threads, it is significantly important to reduce STM runtime overhead and use all available resources effectively.

Third, TM should be supported with software development tools and integrated environment to help programmers debug and analyze TM applications. Perhaps the most important among these is race detection tools. A race condition occurs when a program's execution contains concurrent two accesses to the same memory location where at least one of the accesses is a write. Race conditions are particularly problematic because they typically cause problems only on certain rare interleavings, making them extremely difficult to detect, reproduce, and eliminate. Thus, it is crucial to support TM programmers by providing race detection tools.

#### 1.3 Contributions

In this dissertation, we present studies conducted towards improving the efficiency and practicality of STM across three dimensions that we explain below. Specifically, this dissertation makes the following contributions:

#### 1. Comprehensive evaluation of TM systems

First, we introduce RMS-TM, a Transactional Memory benchmark suite composed of seven real-world applications from the Recognition, Mining and Synthesis (RMS) domain [86, 87]. In addition to featuring current TM research issues such as nesting and I/O and system calls inside transactions, the RMS-TM applications also provide a mix of short and long transactions with small/large read and write sets with low/medium/high contention rates. These characteristics, as well as providing lock-based versions of the applications, make RMS-TM a useful TM benchmark suite. Our experiments show that RMS-TM is scalable, which is useful for evaluating TM designs on high core counts. Second, to allow TM research groups to run each other's code and to perform apples-to-apples comparisons of implementation alternatives, we have implemented a "shim" library [81], which adapts the word-based "back end" libraries of the Rochester STM suite to the common ABI. This work makes the Rochester STM back ends available, for the first time, to programs written with language-level transactions. We also describe experience at both the ABI and API levels, and present performance comparisons relative to the Intel standard back end.

### 2. Design and Implementation of a high performance STM

We have designed a novel parallel STM implementation, namely Software Transactional Memory for Simultaneous Multi-threading systems (STM<sup>2</sup>) pronounced as STM-squared [82]. STM<sup>2</sup> reduces the runtime overheads by offloading read-set validation, bookkeeping, transaction state management and conflict detection to an auxiliary thread running on a sibling core/hardware thread, i.e., a processing element that shares some levels of hardware resource (like the L1 or L2 cache) with the application thread. Application threads optimistically perform their computation with minimal support from the underlying STM system. All synchronization and STM management operations are performed by the paired auxiliary threads.

This means that application threads experience minimal overhead. Auxiliary threads, instead, validate read-sets, maintain transaction states and detect conflicts in parallel with the application threads' computation. We exploit the fact that, on modern multi-core processors, sets of cores can share L1 or L2 caches. This lets us achieve closer coupling between the application thread and the auxiliary thread (when compared with a traditional multi-processor systems). We show that our approach outperforms several well-known STM implementations for various TM applications. In particular,  $STM^2$  shows speedups between, on average, 1.8x and 5.2x over the tested STM systems with peaks up to 12.8x. Finally, we propose an approach to effectively partition processor resources between application and auxiliary threads in  $STM^2$  [83, 84]. In order to bias the allocation of hardware resources in favor of computing intensive application threads or overloaded auxiliary threads, we leverage the hardware thread prioritization mechanism implemented in POWER machines. Our experiments show that effective hardware resource partitioning performs, in general, better than the original  $STM^2$ , up to 86% performance improvement.

#### 3. Providing Correctness Semantics for TM applications

We propose a novel and precise race detection algorithm for TM applications, namely TRADE that is based on a weakened definition of the happens-before relation and does not pose design constraints on the underlying STM system [88]. As a result, our algorithm can be used with a broader set of high-performance, scalable TM systems. Based on this definition, we implement a race detection tool for C/C++ TM applications. Our experiments reveal that TRADE precisely detects transactional data races. However, tools based on happens-before come with different kinds of issues such as high overhead, sensitivity to compiler and hardware optimizations and high dependency on the thread interleaving produced by the scheduler. In order to deal with those problems, we refine the definition of transactional data race and propose T-Rex [85]. T-Rex presents a new definition of transactional data race that follows the programmer's intuition of racy accesses, is independent of thread interleaving, can accommodate popular STM designs, and allows common programming idioms. We also compared T-Rex runtime

overhead to a race detection tool based on happens-before algorithm. Our results show that T-Rex is considerably faster than TRADE.

### 1.4 Organization

The rest of this thesis is organized as follows: Chapter 2 briefly reviews Transactional Memory. Chapter 3 presents RMS-TM benchmark suite and our methodology to choose candidate TM benchmarks from a set of real-world applications. Chapter 4 describes our "shim" library implementation which targets a fair comparison among several proposed STM systems. Chapter 5 describes the design of  $STM^2$  and provides in-depth details of our current implementation. Moreover, it shows the performance numbers of  $STM^2$  over tested STMs. Chapter 6 details our adaptive resource partitioning proposal with the POWER7 hardware thread priority mechanism and its impact on  $STM^2$ . Chapter 7 and Chapter 8 describes our transactional race detection algorithms based on a weakened definition of the happens-before relation and the definition that follows the programmers intuition of racy accesses, respectively. Finally, Chapter 9 concludes this dissertation.

#### 1.5 Publications

- G. Kestor, O. Unsal, A. Cristal and M. Valero, Transactifying Lock-Based RMS Applications, HiPEAC International Summer School on Advanced Computer Architecture and Compilation for Embedded Systems (ACACES), Poster Section, July, 2008, L'Aquila, Italy.

- G. Kestor, S. Stipic, O. Unsal, A. Cristal and M. Valero, RMS-TM: A Transactional Memory Benchmark for Recognition, Mining and Synthesis Applications, The 4th ACM SIGPLAN Workshop on Transactional Computing (TRANSACT), February 2009, Raleigh, NC.

- 3. G. Kestor, V. Karakostas, O. Unsal, A. Cristal, I. Hur and M. Valero, RMS-TM: A Comprehensive Benchmark Suite for Transactional Memory Systems (Best Paper Award), The 2nd ACM International Conference on Performance Engineering (ICPE), March 2011, Karlsruhe, Germany.

- 4. G. Kestor, L. Dalessandro, A. Cristal, M. L. Scott and O. Unsal, Interchangeable Back Ends for STM Compilers, The 6th ACM SIGPLAN Workshop on Transactional Computing (TRANSACT), June 2011, San Jose, CA.

- G. Kestor, R. Gioiosa, T. Harris, A. Cristal, O. Unsal, M. Valero and I. Hur, STM2: A Parallel STM for High Performance Simultaneous Multi-Threading Systems, The 20th IEEE International Conference on Parallel Architectures and Compilation Techniques (PACT), October 2011, Galveston Island, TX.

- G. Kestor, R. Gioiosa, O. Unsal, A. Cristal and M. Valero, Enhancing the Performance of Assisted Execution Runtime Systems., The 17th Architectural Support for Programming Languages and Operating Systems (ASPLOS), Poster Section, March 2012, London, UK.

- G. Kestor, R. Gioiosa, O. Unsal, A. Cristal and M. Valero, Hardware/Software Techniques for Assisted Execution Runtime Systems, The 2nd Workshop on Runtime Environments, Systems, Layering and Virtualized Environments (RE-SoLVE), March 2012, London, UK.

- 8. G. Kestor, R. Gioiosa, O. Unsal, A. Cristal and M. Valero, Enhancing the Performance of Assisted Execution Runtime Systems through Hardware/Software Techniques, 26th ACM/SIGARCH International Conference on Supercomputing (ICS), June 2012, Venice, Italy.

- 9. I. Kuru, H. S. Matar, A. Cristal, G. Kestor and O. S. Unsal, PaRV: Parallelizing Runtime Detection and Prevention of Concurrency Errors, The 3th International Conference on Runtime Verification (RV), Sep 2012, Istanbul, Turkey.

## Chapter 2

# Transactional Memory

In this chapter we first describe the Transactional Memory programming model and then we compare TM to classical lock-based programming model, highlighting pros and cons of each. Finally, we conclude the chapter by reviewing the implementation options of TM systems.

### 2.1 TM Programming Model

While innovations in process technology increase the number of transistors on a die, the performance gains achieved from more complex cores and larger caches diminish. Therefore, chips with multiple cores have quickly become a de-facto standard. Multicore systems have the potential for significant performance improvements, but the complexity of parallel programming and the difficulty of writing efficient and correct code limit the effective use of these systems.

New programming models have been proposed to ease the development of parallel applications that perform well on multi-core architectures. Transactional Memory (TM) [46, 66, 72] allows programmers to mark compound statements in parallel programs as atomic (in C++, \_\_transaction), with the expectation that the underlying run-time implementation will execute such transactions concurrently whenever possible, generally by means of speculation—optimistic but checked execution, with rollback and retry when conflicts arise. The principal goal of TM is to simplify synchronization by raising the level of abstraction, breaking the connection between semantic atomicity and the means by which that atomicity is achieved. Secondarily, TM has the potential

to improve performance, most notably when the practical alternative is coarse-grained locking.

#### 2.1.1 Semantics

Transactions have been used in database systems for a long time [51, 127]. In the database world, a transaction consists of a list of operations on the database explicitly declared by the programmer. These operations can be performed in an arbitrary order and do not take permanent effects until the transaction is committed. If there are conflicts caused by other transactions that are concurrently modifying the same data sets, the transaction may be aborted (rolling back its effects) and restarted. TM programming model is based on the same principles and aims to abstract away the complexity of parallel programming from the programmer.

TM systems provide the following properties, which are also referred as ACI properties:

- Atomicity: A transaction encloses a group of instructions to be executed in an atomic way, which means that transactions either complete these instructions in their entirety or behave as if they had never happened.

- Consistency: Transactions may execute in unpredictable orders, which may lead to an incorrect program execution. A TM system should schedule transactions logically so that their final effect is equivalent to performing transactions serially.

- *Isolation:* The execution of transactions performed on shared data does not affect the result of transactions executed concurrently.

Blundell et al. [15, 106] introduced the terms "weak isolation" and "strong isolation". TM systems with weak isolation guarantee transactional atomicity only among transactions, i.e., accesses to shared memory locations within transactions appear as atomic operations to other transactions. TM systems with support for strong isolation, instead, also guarantee transactional semantics between transactional and non-transactional code, hence normal non-transactional accesses are serialized by the TM with any concurrent transactions. Many Hardware TM implementations naturally provide strong isolation, and there has been substantial progress in developing STMs that support strong isolation [2, 140, 143]. Strong isolation facilitates parallel programming

```

HashTable htA, htB;

HashTable htA, htB;

void move(int key)

void move(int key)

int r;

int r;

mutex_lock();

atomic

//acquire the lock

{ //start the transaction

r = HashTableRemove(htA, key);

r = HashTableRemove(htA, key);

HashTableInsert (htB ,key,r);

HashTableInsert(htB,key,r);

mutex_unlock();

//release the lock

//end the transaction

}

}

(a) Lock-based programming

(b) TM-based programming

```

Figure 2.1: Lock-based vs. TM-based Programming

for programmers by shifting the management of transactional and non-transactional memory accesses from the programmer to the system: non-transactional accesses are ordered with transactional accesses in a sequential schedule. However, strong isolation requires extra instrumentation barriers that introduce large runtime overhead, especially on STM designs.

#### 2.1.2 Programming

When using TM, programmers replace locks with new language constructs such as transaction{A}: this construct executes the statements included in the block of instructions labeled as A, as a single transaction. Figure 2.1 illustrates how the atomic constructs can be used in pseudocode. The code in Figure 2.1a shows a possible lock-based implementation of a program that attempts to remove a key from a hash table and add the key to another hash table. Using locks, the programmer explicitly forces all threads to execute any operation between acquiring and releasing the lock serially. Only one thread at a time is allowed to perform any operation on the hash tables. Writing a parallel program as shown in Figure 2.1a is straightforward since the kind of locking used is a coarse-grained lock (we will see later that the price to pay in order to obtain this simplicity is low speedup and, thus, poor scalability).

In Figure 2.1b shows the same algorithm but this time the program uses the aforementioned atomic statement instead of explicit locking. The function calls to

```

HashTable htA, htB; \\ shared Hash tables

int swap(HashTable ht, int key, int newVal)

{

atomic

{

int r = HashTableRemove(ht,key);

HashTableInsert (ht ,key,newVal);

}

return r;

}

...

atomic

{

int x = swap(htA, key, y);

HashTableInsert (htB, key, x);

}

```

Figure 2.2: Nesting: The transaction within swap() is nested within the outer transaction by the program control flow. All modifications performed by swap and the outer transaction are executed as one larger transaction; When the transaction in swap() commits, its changes appear in the outer transaction and not globally visible until the outer transaction commits.

HashTableRemove() and HashTableInsert() in the transaction should be performed atomically with respect to other threads, as if they were done in a single execution step. Unlike the lock-based implementation, the transactional implementation lets all the threads call the functions concurrently as long as they work on different entries of the HashTable but any updates on the hash tables become visible only when the transaction commits.

Moreover, transactions provide better scalability than the equivalent lock-based implementation as long as the data-access patterns allow transactions to execute concurrently. Firstly, transactions let two or more threads read the same variable concurrently while basic locking mechanisms do not. This problem can be solved with special read-/write locks which allow multiple concurrent readers at the same time. However, the cost of this improvement is completely on the programmer, who has to make more effort while implementing the algorithm. Secondly, transactions allow concurrent read and write operations to different variables. This is equivalent to write a lock-based program using fine grained locking and provide concurrent accesses to disjoint variables. Again,

with locks, the burden is completely on the programmers. Moreover, beside being a difficult task, the risk of introducing bugs, such as deadlocks, increases.

Summarizing, transactions enable concurrent read accesses to the same memory location and concurrent read and write accesses to disjoint variables while providing the simplicity of coarse-grained locking and achieving the performance that can be obtained by fine-grained locking. The example in Figure 2.1b illustrates these properties: two threads can read the hash-table buckets concurrently and perform a move operation concurrently from different hash-table buckets.

Besides the basic TM primitives intended to start and stop transactions and to annotate memory accesses as transactional accesses, there are advanced TM primitives provided by some TM systems. Nested transactions (see Figure 2.2) allow programmers to create a transaction inside another transaction. The simplest way to support transactional nesting is the flattening model which encloses all transactions in the outermost transaction. With flat nesting a conflict in an inner transaction forces all its ancestors to abort. Closed and open nesting transaction models try to solve this problem. With the closed nesting model [116], nested transactions commit or abort on exit: if a nested transaction commits, its effects become visible only to its parent transaction. If the transaction aborts, its effects are discarded but the parent transaction stays alive. After that, the aborted nested transaction can be re-executed independently from its parent. Open nesting models [120] have more concurrency as compared to closed nesting models: when an open nested transaction commits, all the other transactions can see its updates immediately and continue their work with the new data earlier, without delaying until the outer transaction commits. This may explore more concurrency when shared resources are simultaneously accessed by several large transactions.

Another advanced TM primitive is the "retry": this primitive enables waiting on multiple conditions such as the "select" system call described in the POSIX standard. Figure 2.3 demonstrates the use of the retry primitives where a thread attempts to find an available data item from a collection of lists. If all of the lists are empty, then the retry statement is executed, which aborts and restarts the transaction.

```

atomic

{

for (int i=0; i<NUM_LIST; i++)

{

int e;

if (!list[i].empty())

{

e = list[i].get_element();

}

return e;

}

retry;

}</pre>

```

Figure 2.3: Example code for the use of "retry" primitive: If the retry statement is reached, the transaction is aborted and re-executed.

# 2.2 Implementation Options

The key mechanisms of TM systems are data versioning and conflict detection. TM systems must simultaneously manage multiple versions of data while the transactions are still active. In order to achieve this goal, new data versions created by transactional writes are isolated from the rest of the system by maintaining either an undo-log or a write-buffer. When the transaction commits, the new version becomes globally visible. On the other hand, if the transaction aborts, the old version of data remains to be the visible one.

In order to provide a conflict detection, memory accesses in a transactions must be tracked. If a conflict is detected between two transactions, one of them aborts and either restores the old versions of its data from the undo-log or discards its write-buffer, depending on the approach used for data versioning.

### 2.2.1 Eager and Lazy Data Versioning

As mentioned before, the goal of data versioning in TM systems is to manage different versions of data in a memory and to perform actions when a transaction commits or aborts. More specifically, the data versioning system updates the memory locations with the new values produced by a transaction atomically when the transaction commits. If the transaction aborts, the data versioning system discards the new version of

data safely.

There are two types of data versioning: eager and lazy data versioning, which can be summarized as follows:

- Eager versioning [115] stores transactional write accesses to memory as a new version as soon as possible, and buffers the old version in an undo-log. If the transaction commits, there is no further action required to make the new versions visible. If the transaction aborts, the eager versioning introduces some delay to restore the old versions of data from the undo-log to the memory.

- Lazy versioning [43] writes all the new data versions in a write-buffer until the transaction commit phase starts. If the transaction commits, the new versions are copied from the write-buffer to the memory. If the transaction aborts, no further action on the data structures is required and the write-buffer is simply discarded. Unlike eager versioning, lazy versioning introduces delay on the transaction commit phase, since it needs to update the memory locations with the latest version of the data.

# 2.2.2 Eager and Lazy Conflict Detection

In order to decide whether a conflict between transactions occurs, TM systems track memory accesses through a read-set and a write-set per transaction. The read-set includes addresses read by the transaction and the write-set contains memory addresses written by the transaction. A conflict happens when two transactions access the same address and one of them is a write operation. In particular, conflict detection relies on comparing the read- and write-set of each transaction with all the other read- and write-sets. A conflict is detected when a variable in the write-set of a transaction is also in any set of other transactions.

There are two types of conflict detections: eager and lazy.

• Systems with **eager conflict detection** check for conflicts as transactions read and write a memory location. Read and write operations are allowed to complete only when they do not cause any conflicts. Under eager conflict detection, conflicts are detected before the end of the transaction so that they can be handled as soon as possible. Resolving conflicts in an early stage reduces the amount of work lost

by aborting transactions. However, the performance of eager conflict detection system depend on which technique is used to resolve conflicts.

• The other technique is lazy conflict detection: this approach assumes that conflicts among transactions are rare, thus this technique delays conflict detections to the end of the transaction. While executing a transaction, all the read and write operations are allowed without performing any control. Before committing, the transaction is validated by comparing the read/write sets against the read/write sets of other transactions. If there are no read-write or write-write conflicts, the transaction commits and all temporary data are stored to memory. Lazy conflict detection does not introduce overhead to each read and write as eager conflict detection does, since it postpones all the checks until the end of the transaction.

TM systems can detect conflicts at various granularities. Word-level granularity (the smallest possible granularity) provides the highest accuracy but might introduce excessive overhead to track and compare read- and write-sets. This overhead is reduced as the granularity of the conflict detection strategy increases, though the risk of incurring false conflicts increases too. False conflicts are generally undesirable because they might cause more transactions to abort although no real conflicts have actually occurred, which degrades the performance. Cache-line-level granularity provides a good trade-off between the false conflicts and the runtime overhead of conflict detection: this design choice divides the memory addresses into a finite set of strips and each strip is mapped to memory locations by using a hash function. The risk of of false conflicts might still be high, depending on the cache line size. Object-level detection is an alternative, intended to be used by object oriented applications. Depending on the size of the object, it may reduce the overhead in terms of time (to compare the read sets and the write sets) and space (to track the read sets and the write sets) needed for conflict detection. With this approach, false conflicts only occur when two transactions perform write operations on two different fields of an object. Comparing the three approaches, the word-level granularity is the one with the highest precision and the highest overhead (in terms of both time and space) while the object-level granularity provides the lowest overhead but has a high false conflict risk. The cache-line-level granularity resides between the other two approaches in terms of overhead and the false conflict rate. Unlike the object-level granularity, the cache-line- and word-level

```

int foo(int arg)

{

//begin the transaction

atomic

{

temp_1 = stmRead(a);

temp_2 = temp_1 + 1;

a++;

stmWrite(a,temp_2);

} //end the transaction

(a) Implicit Transaction

(b) Explicit Transaction

```

Figure 2.4: Type of Used Transactions in Programming Languages

granularity conflict detection systems are not language-level entities, which results in more programming effort to reduce the number of conflicts.

#### 2.2.3 Software and Hardware

Researchers have proposed several different implementations of transactional memory classified into Software Transactional Memory (STM), Hardware Transactional Memory (HTM) and Hybrid Transactional Memory. Software TM systems [5, 43, 65, 67, 70, 71, 104, 133, 135] implement transactional memory entirely in software. An STM implementation instruments all shared memory reads and writes inside atomic sections by using read and write barriers. The instrumentation can be inserted by a compiler in an implicit way (see Figure 2.4a) [35, 138]. In an explicit way, the programmer uses a set of low-level APIs to manually annotate memory accesses in transactions, as shown in Figure 2.4b [23, 43, 104, 133]. As mentioned before, tracking the shared memory accesses is essential for data versioning and conflict detections.

In STM Systems, each transaction has a transaction descriptor that describes the transaction's state which consists of the read/write set (including transaction records), the undo-log (for eager versioning) or the write-buffer (for lazy versioning). Moreover, the transaction's descriptor might include additional data to handle nested transaction with partial rollback. With eager versioning, the write barrier acquires a lock on the transaction record corresponding to the memory location to be updated, then an old value from this memory location is added to the undo-log and then the memory location content is updated with the new value. With lazy versioning, the new value is stored

to the write-buffer with the write barrier; if the transaction commits, the transaction acquires all lock on the all needed transaction records and store all new values from the write-buffer to the memory. In order to detect conflicts among transactions, conflict detection techniques compare version numbers of transaction records in transactions' read/write sets. If a conflict is detected, STM systems provide effective conflict resolution schemes such as stalling one of the transactions or aborting one transaction selected randomly and re-executing the aborted transaction later.

STM systems also provide flexible transactional semantics such as nested transactions with partial rollback. Moreover, STM implementations can accommodate modern language features (e.g., garbage collection (GC), exception handling) and useful tools (e.g., debugger, performance analyzers). However, in general, they incur performance degradation due to the instrumentation required for transactional memory accesses.

Hardware TM systems [10, 27, 62, 72, 115, 131, 155] do not need code instrumentation in the atomic section to manage data versioning and track conflicts, instead, they use a set of instructions in the Instruction Set Architecture (ISA) to provide a low-level transactional interface. In order to guarantee a good performance, it is crucial to cope with data versioning and conflict detection by using hardware resources. Since there is no need to instrument any code, HTM systems are also able to handle more general cases than STM, such as two versions of the same function called from inside transactions or outside of the transaction.

Caches implement data versioning by storing transactional read and write operations to either an undo-log (for eager versioning) or a write-buffer (for lazy versioning). With eager versioning, before performing a new cache line write, the cache line and its address are added to the undo-log by performing additional cache writes. If the transaction aborts, the undo-log must be restored to a memory. With lazy versioning systems, a cache line write is added to the write-buffer with the W tracking bit set, which indicates that there is an ongoing write operation. If the transaction aborts, the write-buffer is flushed without performing any validation. If the transaction commits, the data in the write-buffer becomes visible to other transactions and the TM system resets all the W bit for each cache line involved in the transaction.

Cache coherence protocols provide communication between read sets and write sets to detect conflicts. With the eager conflict detection mechanism, when a transaction performs a read or a write access, the processor sends a request to the corresponding cache line. A conflict is detected if there is any copy of the cache line with the R (read) or W (write) bit set by any processors. The lazy conflict mechanism uses the same coherence message protocol but send all the requests from the write set when the transaction commits.

Even though hardware TM systems offer superior performance, they exhibit additional challenges. Managing data versioning and tracking conflicts transparently by using cache hierarchies and cache coherency protocols are not trivial. Besides that, a long transaction can lead to *cache overflow* since there is a limited space to store all the information related to read/write sets tracking, write buffering and undo logging. Moreover, their restricted semantics do not support transactional language constructs such as deeply nested transactions with partial rollback, blocking primitives and interrupts.

An alternative approach to blend the performance of HTM with the flexibility of STM is Hybrid Transactional Memory [40, 91, 114]. In Hybrid transactional memory implementations, transactions start in the HTM mode, if the HTM system fails due to an excessive resource requirement, the transactions are roll-backed and restarted in the STM mode. Therefore, they are faster than Software TM systems but slower than Hardware TM systems.

There are hundreds of millions of multi core machines already in the field. We believe that, for the sake of backward compatibility, emerging TM-based programming models will need to be implemented in software on these machines. Moreover, a growing consensus holds that STM will be needed as a "fall-back" mechanism when hardware transactions fail due to buffer space limitations, interrupts, or other transient or deterministic causes [36, 42, 91, 144].

## 2.2.4 Commonly Used STMs

Throughout the dissertation, we use and compare various STM implementations. In the following we summarize the main design choices, characteristics and trade-offs of these popular STMs.

**TL2** is an STM that implements a lazy data versioning [43]. A transaction begins by reading the value t in a global "clock." Ownership records (orecs), found by address hashing, indicate the last time at which one of the corresponding location was modified. If a transaction encounters a location that was written after t, it assumes it is

inconsistent, aborts, and retries. At commit time, the transaction locks the orecs for all locations that need to be modified, checks to make sure that all of the locations it read still have a timestamp earlier than t, increments the global time, stores the new time into all the locked orecs, writes out all the updates, and then unlocks the orecs.

**TinySTM** implements an eager conflict detection along with an eager versioning system with extendable timestamps [133]. Extendable timestamps avoid false positives in which a transaction is aborted despite having seen a consistent view of memory. If a transaction encounters a location that was written after start time t, it checks to see whether any previously read location has been modified since t. If not, it re-reads the global clock and continues, pretending it started at this new time t' instead of t.

TL2 and TinySTM do not support safe privatization. Both require additional code (and nontrivial overhead, not included in our experiments) for correct execution of programs in which data transitions back and forth between shared and private state [105].

RSTM suite includes a variety of STM algorithms, some of which have several variants. The selection of an STM library can be handled simply by re-compiling the code with a different back end. Among the word-based back ends, TML, LLT, ET, NOrec and Pipeline reflect popular but divergent points in the STM design space. These STMs are briefly described below.

- TML is an eager conflict detection, eager versioning system with a single sequence lock [92]. TML allows concurrent read-only transactions with no logging overhead, but only one system-wide writer is allowed. This approach is effective in workloads where reads are the common case. However, using a single sequence lock without logging means that conflict detection is extremely conservative: any writer conflicts with any other concurrent transaction.

- LLT is a canonical lazy versioning STM implementation patterned after TL2 [43].

- ET starts with the basic LLT infrastructure, adds the ability to operate in both eager conflict detection/eager versioning and eager conflict detection/lazy versioning mode, and adds extendable timestamps as in TinySTM [133].

- NOrec [39], like LLT, is a lazy versioning system: it delays the resolution of conflicts until a transaction is ready to commit. It uses a single sequence lock [92], however, rather than ownership records to serialize commit and write-back. A

transaction checks, after each read, to see if any writer has committed since start time t; if so, it performs value-based validation [123] to see if its prior reads, if performed right now, would return the values previously seen; if so, as in ET, it reads a new start time from the global clock and continues. Writers can speculate in parallel, but only one can commit at a time. This serialization ultimately limits scalability, but the simplicity of the system yields surprisingly good performance for up to a few dozen cores. Moreover, NOrec is inherently privatization safe.

• Pipeline extends ET with lazy conflict detection/lazy versioning and it adds the start time linearization approach proposed by Menon et al. [110] to provide single global lock atomicity (SGLA) in Java. SGLA is a basic, pragmatic semantics, where a program is required to behave "as if" transactions were protected by a single global lock. Although SGLA simplifies the design, implementation and testing of STM systems, the implementation of SGLA semantics reduces the scalability because it requires total ordering among all transactions in the system.

# Part II

# Comprehensive Evaluation of TM Systems

As researchers work to develop robust, mature STM, it becomes increasingly important to be able to effectively and fairly compare STM designs with benchmarks that are representative of real-world applications. Chapter 3 describes RMS-TM, a comprehensive benchmark suite to evaluate (hardware and software) TM implementations. RMS-TM consists of several applications from the RMS domain that are considered representative of future workloads for multi-core systems. Moreover, researchers should be able to share applications, compilers, and run times among groups, and to be able to modify one layer of the system stack while keeping the others constant, for "apples-to-apples" comparison. To this extent, we developed a software layer that allows researchers to test the same applications with interchangeable STM back ends (Chapter 4).

# Chapter 3

# RMS-TM Benchmark Suite

# 3.1 Introduction

Muultiple Software TM (STM) [70, 104, 133, 135] and Hardware TM (HTM) implementations [27, 62, 115, 155] have been proposed in the literature. Although some of implementations have reached maturity level, there are still open research issues, in addition to performance, such as handling nested transactions, I/O operations, system and library calls inside transactions. Moreover, performance comparison of TM-based applications against their equivalent lock-based versions is crucial for the justification of further research in this area as well as for convincing the industry to implement TM systems in commercial products. One major aspect of performing functional and performance evaluation of TM systems is the development of an emerging TM benchmark suite.