**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (<u>www.tesisenxarxa.net</u>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (<u>www.tesisenred.net</u>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (<u>www.tesisenxarxa.net</u>) service has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading and availability from a site foreign to the TDX service. Introducing its content in a window or frame foreign to the TDX service is not authorized (framing). This rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author

# Programming, Debugging, Profiling and Optimizing Transactional Memory Programs

Ferad Zyulkyarov Departament d'Arquitectura de Computadors Universitat Politècnica de Catalunya - BarcelonaTech

> A thesis submitted for the degree of *Doctor of Philosophy* June 1, 2011

I would like to dedicate this thesis to my mother who always supported me in my studies and taught me to love the science.

# Acknowledgements

I would like to thank my advisors Mateo Valero, Osman Unsal and Adrian Cristal for their guidance and support during my studies. Without their help I would not be able to make these research contributions and at all understand what indeed research is. In equal way, I would like to acknowledge and thank Tim Harris who in fact has been like my external advisor. During my PhD Tim was providing me with invaluable support on Bartok, helping me in writing papers, and above all he was a constant source of inspiration.

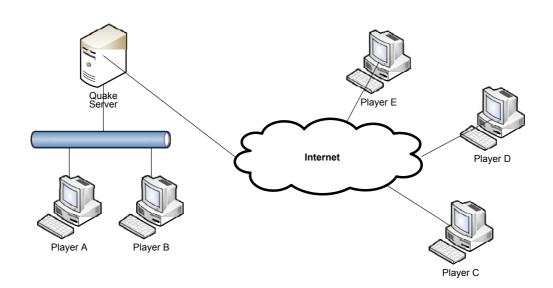

I would like to thank Eduard Ayguadé for his advice on transactifying the Quake game. Transactification of the Quake game server constitutes large part of my thesis and also it has motivated the other ideas in my PhD work.

I would like to specially thank Mateo Valero for his involvement in the procedures that have allowed this thesis become a reality. Also, I would like to acknowledge his dedication and continuous effort for making BSC a platform of research excellence from which I was benefiting in various ways.

Of course, many thanks go to my friends Srdjan Stipic, Sasa Tomic, Valdimir Gajinov, Vesna Smiljkovic, Javier Arias, Nehir Sonmez, Otto Pflucker, Adria Armejach, Oriol Prat, Oriol Arcas, Neboyjsa Miletic, Gokcen Kestor, Gulay Yalcin, Vasilis Karakostas, Milovan Djuric, Milan Stanic, Tim Hayes, Ivan Radkovic, Nikola Bezanic, Vladimir Marjanovic, Nikola Markovic. Surely without them this dissertation would not be complete and the time during my PhD would not be that great fun. Last but not least I would like to acknowledge the institutions which has been directly or indirectly supporting my PhD work. For the completion of this work I have used resources provided to me by my employer, the Barcelona Supercomputing Center (BSC-CNS), and by the Department of Computer Architecture at the Universitat Politécnica de Catalunya-BarcelonaTech, where I have pursued my PhD.

Several institutions have provided additional funding for this project. I was supported by the FI scholarship from the Catalan Government. This work was supported by the cooperation agreement between the Barcelona Supercomputing Center – National Supercomputer Facility and Microsoft Research, by the Ministry of Science and Technology of Spain and the European Union (FEDER funds) under contract TIN2007-60625, by the European Network of Excellence on High-Performance Embedded Architecture and Compilation (HiPEAC) and by the European Commission FP7 project VELOX (216852).

### Abstract

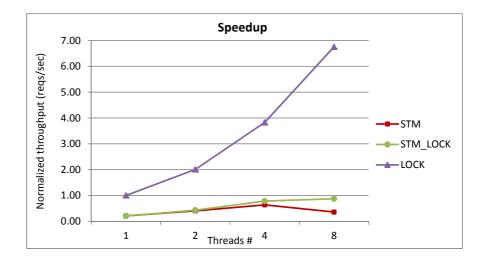

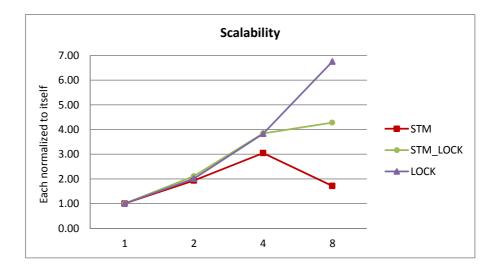

The shift from developing powerful monolithic CPUs to a less powerful but multi-core CPUs made developers to rethink their approach of writing programs. Programmers cannot anymore expect that their programs will execute faster on the next generation CPUs unless their programs are parallel. For many years, researchers have been seeking for various solutions to make parallel programming for shared memory architectures easier and also efficient. Transactional Memory (TM) is one such potential solution. In TM synchronizing access to shared data is simpler than locks. The programmer defines the critical sections using atomic blocks and the underlying TM implementation automatically executes the enclosed instructions atomically and in isolation. In contrast, when using locks, the programmer manually implements the atomicity and isolation for the shared data. In addition, when conflicts are rare, the speculative execution of atomic blocks promises to deliver performance which is comparable to efficient lock-based implementations. To answer the questions "Is programming applications using atomic blocks easier than locks?" and "Is the performance of TM competitive with locks?" we have developed a real TM application - AtomicQuake. To implement Atomic-Quake, as a base we used a parallel lock-based Quake game server and replaced all lock-based critical sections with atomic blocks. We have found out that developing applications with atomic blocks would be easier than locks but the performance of STMs should be improved. In addition, the experience of developing AtomicQuake revealed unsought problems which showed that TM is not yet ready for use in production quality software. Some of these problems were related to

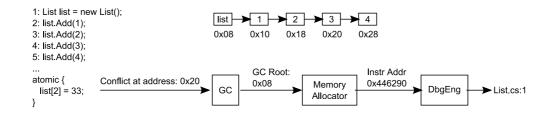

the language level integration of TM and other problems related to the lack of TM support in the software development tools such as debuggers and profilers. While developing AtomicQuake it was extremely difficult to debug errors and almost impossible to profile the TM relevant bottlenecks. This last problem motivated us to investigate how to extend current debuggers to debug TM applications and appropriate profiling techniques that would reveal the bottlenecks in the TM applications. We have introduced three new approaches to debug TM applications. First, the user can debug at the level of atomic blocks. In this approach, an atomic block is treated as a single instruction and the implementation details of the atomic blocks, weather TM or lock inference, are hidden to the user. Second, the user can debug at the level of transactions. In this approach, the implementation of **atomic** blocks is assumed to be TM and the user can step inside atomic blocks and examine the TM state. Third, the user can manage the TM state at debug time which is analogues to the mechanisms how one can change the CPU state. Also, we have introduced new abstractions such as debug time atomic blocks and TM watch points. Debug time atomic blocks let the user create and remove atomic blocks at debug time. We have implemented our ideas in an extension for WinDbg debugger and the ahead-of-time C# to x86 Bartok compiler.

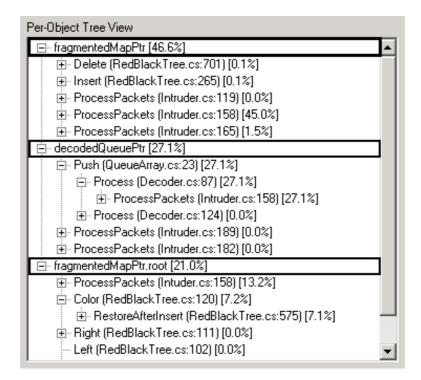

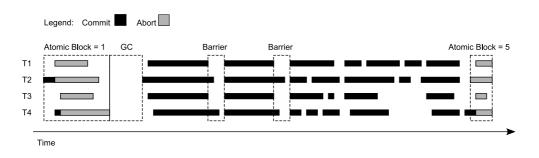

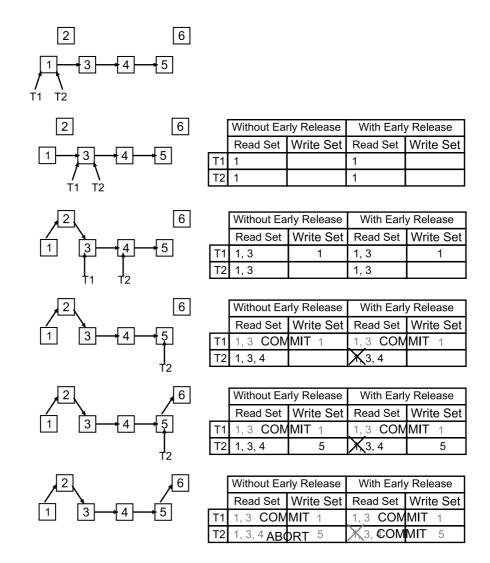

To profile TM applications we have introduced new techniques that provide in-depth and comprehensive information about the wasted work caused by aborting transactions. We have explored three directions: (i) techniques to identify multiple conflicts from a single program run, (ii) techniques to describe the data structures involved in conflicts by using a symbolic path through the heap, rather than a machine address, and (iii) visualization techniques to summarize which transactions conflict most. To demonstrate the effectiveness of these techniques we have built a standalone profiling tool and a lightweight profiling framework for the Bartok compiler. The profiling framework processes the data offline or during garbage collection thus having minimal probe effect (less than 1%) and overhead (less than 14%).

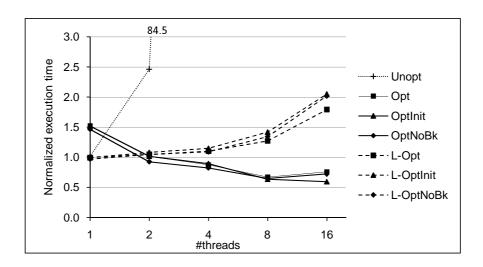

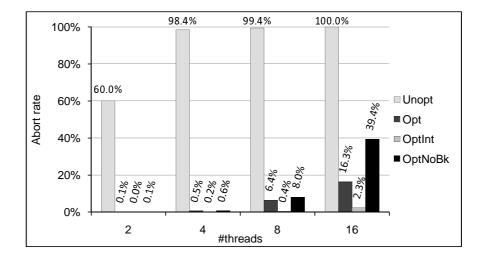

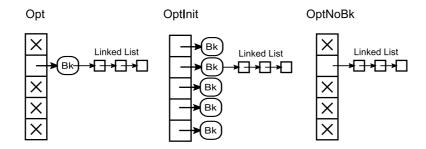

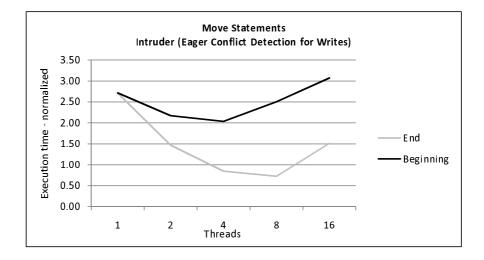

Using the profiling tool we have analyzed and optimized several applications from the STAMP benchmark suite. The profiling techniques effectively revealed TM-specific bottlenecks such as false conflicts and contentions accesses to data structures. The discovered bottlenecks were subsequently eliminated with TM-specific optimizations which target is to reduce the number of aborts and wasted work incurred by these aborts. Among the optimization highlights are the transaction checkpoints which reduced the wasted work in Intruder with 40%, decomposing objects to eliminate false conflicts in Bayes, early release in Labyrinth which decreased wasted work from 98% to 1%, using less contentions data structures such as chained hashtable in Intruder and Genome which have higher degree of parallelism.

# Contents

| 1        | Intr | oduction                                                                                              | 1 |

|----------|------|-------------------------------------------------------------------------------------------------------|---|

|          | 1.1  | Thesis Statement                                                                                      | 3 |

|          | 1.2  | Contributions                                                                                         | 5 |

|          | 1.3  | Publications                                                                                          | 7 |

|          | 1.4  | Research Context                                                                                      | 9 |

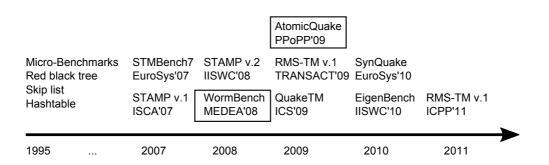

|          |      | 1.4.1 AtomicQuake                                                                                     | 9 |

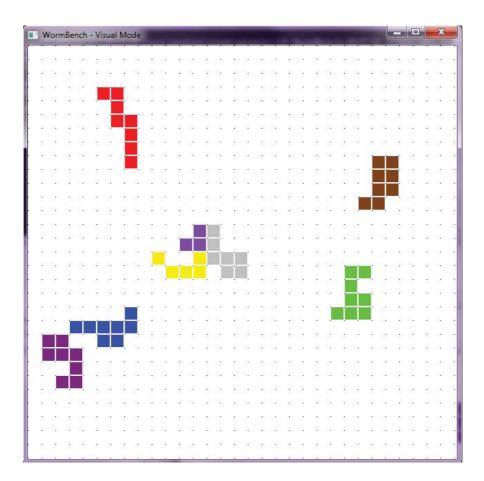

|          |      | 1.4.2 WormBench $\ldots$ 1                                                                            | 2 |

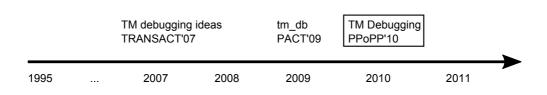

|          |      | 1.4.3 Debugging                                                                                       | 2 |

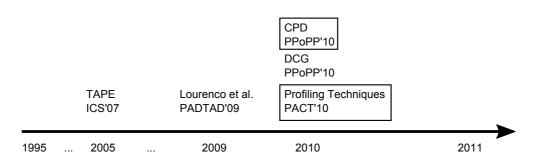

|          |      | 1.4.4 Profiling                                                                                       | 4 |

|          | 1.5  | Outline                                                                                               | 6 |

| <b>2</b> | Bac  | kground - Transactional Memory                                                                        | 9 |

|          | 2.1  | Language Constructs                                                                                   | 0 |

|          | 2.2  | Design and Operation                                                                                  | 3 |

|          |      | 2.2.1 Interface                                                                                       | 4 |

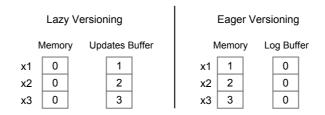

|          |      | 2.2.2 Data Versioning                                                                                 | 5 |

|          |      | 2.2.3 Conflict Detection                                                                              | 6 |

|          |      | 2.2.4 Conflict Resolution $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 2$          | 8 |

|          |      | 2.2.5 Commit                                                                                          | 8 |

|          |      | 2.2.6 Abort                                                                                           |   |

|          | 2.3  | Additional Functionality                                                                              | 9 |

|          | -    | 2.3.1 Nested Transactions                                                                             |   |

|          |      | 2.3.2     Transaction Checkpointing     3                                                             |   |

|          |      | 2.3.2       Humsdetton Checkpointing       3         2.3.3       Abstract Nested Transactions       3 |   |

|          |      | 2.3.4       Transaction Scheduling       3                                                            |   |

|          |      |                                                                                                       | 9 |

|   |     | 2.3.5  | Strong v  | vs. Weak Isolation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 34$                      | E      |

|---|-----|--------|-----------|-----------------------------------------------------------------------------------------------|--------|

|   |     | 2.3.6  | Handlin   | g Irrevocable Actions                                                                         | ;<br>) |

|   |     | 2.3.7  | Early R   | elease $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 35$             | )      |

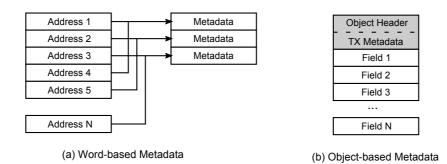

|   | 2.4 | Imple  | mentation | us $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 37$                 | 7      |

|   |     | 2.4.1  | Software  | e Transactional Memory $\ldots \ldots \ldots \ldots \ldots 37$                                | 7      |

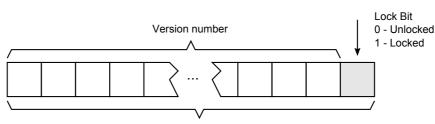

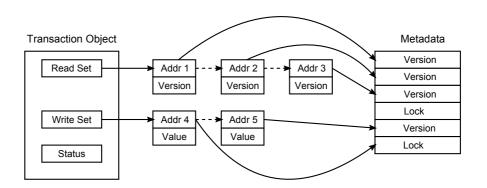

|   |     |        | 2.4.1.1   | TL2                                                                                           | ;      |

|   |     |        | 2.4.1.2   | Bartok-STM                                                                                    | )      |

|   |     | 2.4.2  | Hardwar   | re Transactional Memory 44                                                                    | E      |

|   |     | 2.4.3  | Hybrid '  | Transactional Memory                                                                          | )      |

|   | 2.5 | Summ   | ary       |                                                                                               | )      |

| 3 | Dor | alonin | a Ducana  | ma with Atomia Ploaks and Transportional Mar                                                  |        |

| J | ory | elopin | g r togra | ${ m Ams} { m with Atomic Blocks} { m and Transactional Mem-} 46$                             |        |

|   | 3.1 | Motiv  | ation     | 47                                                                                            |        |

|   | 3.2 |        |           | 48                                                                                            |        |

|   | 3.3 |        |           |                                                                                               |        |

|   | 0.0 |        | -         | Overview                                                                                      |        |

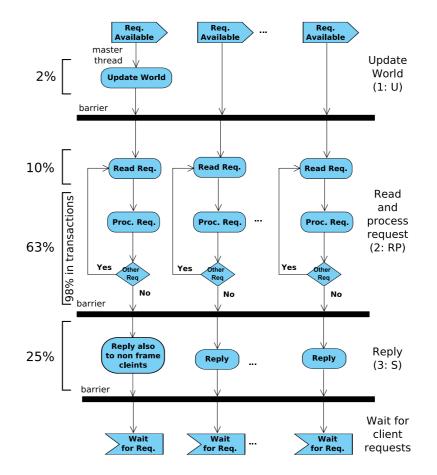

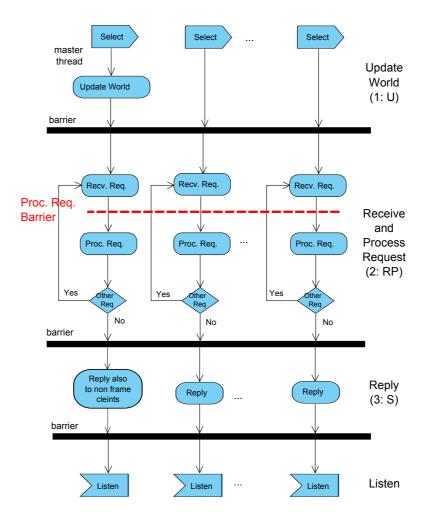

|   |     |        | 3.3.1.1   | Parallel Quake                                                                                |        |

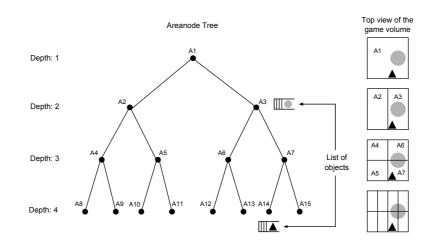

|   |     |        | 3.3.1.2   | Shared Data Structures                                                                        |        |

|   |     | 3.3.2  | Using T   | ransactions $\ldots \ldots 61$ |        |

|   |     |        | 3.3.2.1   | Where Transactions Fit                                                                        | 2      |

|   |     |        | 3.3.2.2   | Non-Block-Structured Critical Sections 65                                                     | ý      |

|   |     |        | 3.3.2.3   | Thread Private Storage                                                                        | 5      |

|   |     |        | 3.3.2.4   | Condition Synchronization                                                                     | 3      |

|   |     |        | 3.3.2.5   | IO and Irrevocability Inside Transactions 68                                                  | 3      |

|   |     |        | 3.3.2.6   | Error Handling Inside Transactions 69                                                         | )      |

|   |     |        | 3.3.2.7   | Privatization                                                                                 | 2      |

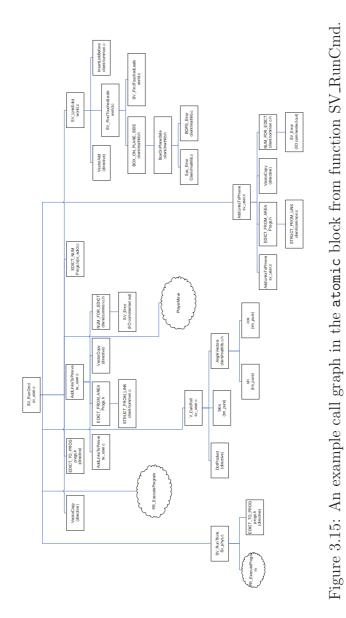

|   |     |        | 3.3.2.8   | Call Graph Structure in Atomic Blocks 73                                                      | \$     |

|   |     | 3.3.3  | Experim   | nental Results                                                                                | )<br>) |

|   |     |        | 3.3.3.1   | Experimental Methodology                                                                      | )      |

|   |     |        | 3.3.3.2   | Application Characteristics                                                                   | ,      |

|   |     |        | 3.3.3.3   | Per-Atomic Block Characteristics                                                              | )      |

|   | 3.4 | Worm   | Bench .   |                                                                                               | )      |

|     | 3.4.1                                                                                                              | Requirements for a Synthetic TM Workload 84                                                                                                                                                                                                                                                                                 | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                                                                                    | 3.4.1.1 Synchronization Problems                                                                                                                                                                                                                                                                                            | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |                                                                                                                    | 3.4.1.2 Metrics                                                                                                                                                                                                                                                                                                             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

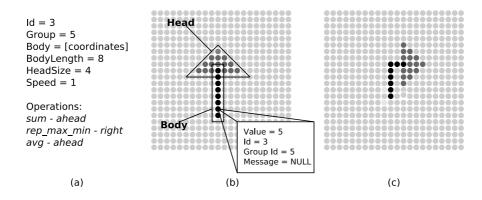

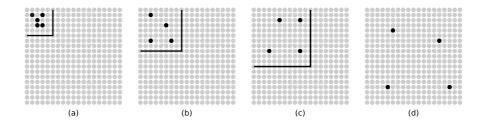

|     | 3.4.2                                                                                                              | Design and Implementation                                                                                                                                                                                                                                                                                                   | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 3.4.3                                                                                                              | Runtime Characteristics                                                                                                                                                                                                                                                                                                     | C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

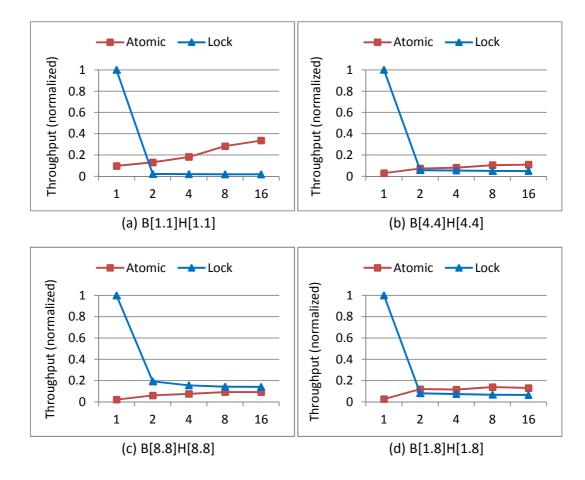

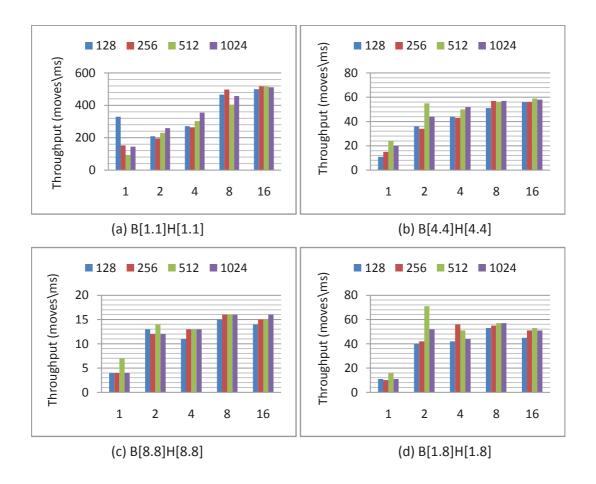

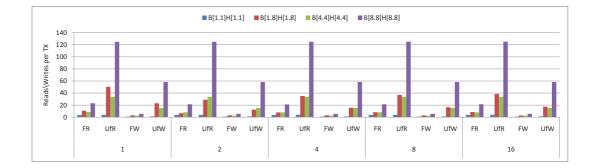

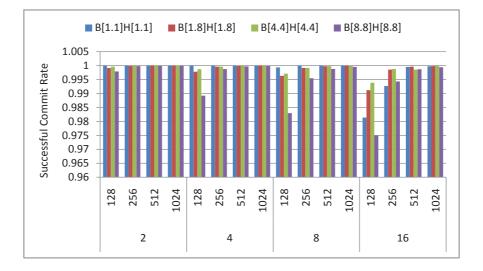

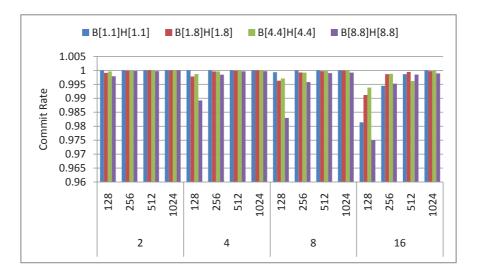

|     | 3.4.4                                                                                                              | Experimental Analysis                                                                                                                                                                                                                                                                                                       | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |                                                                                                                    | 3.4.4.1 Description of the Run Configurations 9                                                                                                                                                                                                                                                                             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |                                                                                                                    | $3.4.4.2  \text{Results}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  9$                                                                                                                                                                                                                                        | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 3.4.5                                                                                                              | Modeling a TM Application                                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.5 | Portin                                                                                                             | $g \text{ STAMP} \dots \dots$                                                                                                                                                                                         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.6 | Summ                                                                                                               | $ary \dots \dots$                                                                                                                                                                                                     | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DI  | •                                                                                                                  | 10                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |                                                                                                                    | -                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |                                                                                                                    |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |                                                                                                                    |                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.3 | 0                                                                                                                  | -                                                                                                                                                                                                                                                                                                                           | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.3.1                                                                                                              |                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.3.2                                                                                                              |                                                                                                                                                                                                                                                                                                                             | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.3.3                                                                                                              | Internal Breakpoints                                                                                                                                                                                                                                                                                                        | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.3.4                                                                                                              | Probe Effect and Overhead                                                                                                                                                                                                                                                                                                   | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.4 | Debug                                                                                                              | gging at the Level of Atomic Blocks                                                                                                                                                                                                                                                                                         | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.4.1                                                                                                              | Stepping Over Atomic Blocks                                                                                                                                                                                                                                                                                                 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.4.2                                                                                                              | Stepping Inside Atomic Blocks                                                                                                                                                                                                                                                                                               | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.5 | Debug                                                                                                              | gging at the Level of Transactions $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 120$                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.5.1                                                                                                              | Transaction Events $\ldots \ldots 122$                                                                                                                                                                                           | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.6 | Debug                                                                                                              | g-Time Transaction Management                                                                                                                                                                                                                                                                                               | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.6.1                                                                                                              | Debug-Time Transactions $\ldots \ldots 124$                                                                                                                                                                                                                  | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

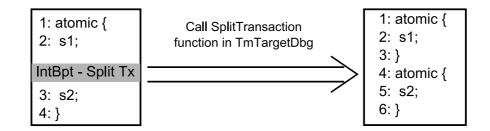

|     | 4.6.2                                                                                                              | Splitting Atomic Blocks                                                                                                                                                                                                                                                                                                     | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.6.3                                                                                                              | Modifying Transactional State                                                                                                                                                                                                                                                                                               | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.7 | Summ                                                                                                               | $ary \dots \dots$                                                                                                                                                                                                     | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

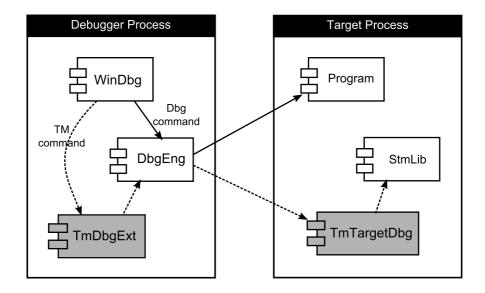

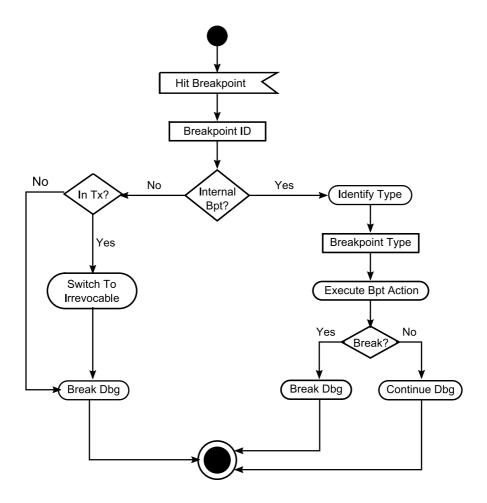

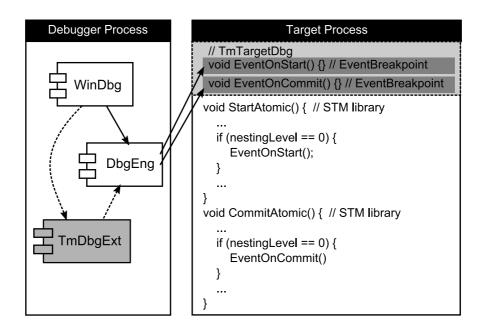

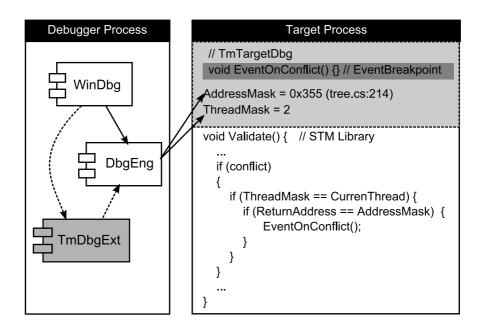

|     | <ul> <li>3.6</li> <li>Deb</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul> | 3.4.2 $3.4.3$ $3.4.3$ $3.4.4$ $3.4.4$ $3.4.4$ $3.5$ Portin $3.6$ Summ $4.1$ Motiv $4.2$ Relate $4.3$ Design $4.3.1$ $4.3.2$ $4.3.1$ $4.3.2$ $4.3.1$ $4.3.2$ $4.3.1$ $4.3.2$ $4.3.1$ $4.3.2$ $4.3.1$ $4.3.2$ $4.3.1$ $4.3.2$ $4.3.1$ $4.4.2$ $4.4$ Debug $4.4.1$ $4.4.2$ $4.5$ Debug $4.6.1$ $4.6.2$ $4.6.1$ $4.6.2$ $4.6.3$ | 3.4.1.1       Synchronization Problems       8         3.4.1.2       Metrics       86         3.4.2       Design and Implementation       86         3.4.3       Runtime Characteristics       90         3.4.4       Experimental Analysis       91         3.4.4       Experimental Analysis       91         3.4.4       Experimental Analysis       91         3.4.4       Experimental Analysis       91         3.4.4.2       Results       91         3.4.5       Modeling a TM Application       101         3.5       Porting STAMP       102         3.6       Summary       103         3.6       Summary       103         4.1       Motivation       107         4.2       Related Work       100         4.3       Design and Implementation       103         4.3.1       Design Approach       111         4.3.2       Interaction Between TmDbgExt and TmTargetDbg       112         4.3.3       Internal Breakpoints       113         4.3.4       Probe Effect and Overhead       114         4.4       Debugging at the Level of Atomic Blocks       114         4.4.1       Stepping Over Atomic Bloc |

| Pro | filing                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                   | <b>130</b>                        |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 5.1 | Motiva                                                                                                                                              | $\operatorname{ation}$                                                                                                                                                                                                                                                                                                            | 132                               |

| 5.2 | Relate                                                                                                                                              | d Work                                                                                                                                                                                                                                                                                                                            | 132                               |

| 5.3 | Profili                                                                                                                                             | ng Techniques                                                                                                                                                                                                                                                                                                                     | 134                               |

|     | 5.3.1                                                                                                                                               | Basic Conflict Point Discovery                                                                                                                                                                                                                                                                                                    | 135                               |

|     | 5.3.2                                                                                                                                               | Advanced Conflict Point Discovery                                                                                                                                                                                                                                                                                                 | 139                               |

|     | 5.3.3                                                                                                                                               | Quantifying the Importance of Aborts                                                                                                                                                                                                                                                                                              | 142                               |

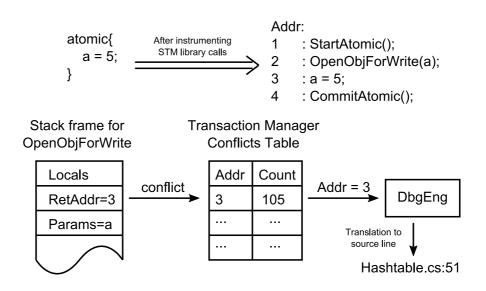

|     | 5.3.4                                                                                                                                               | Identifying Conflicting Data Structures                                                                                                                                                                                                                                                                                           | 143                               |

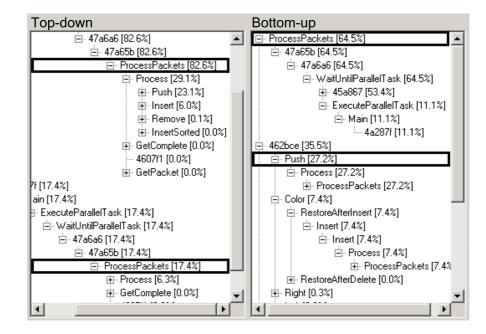

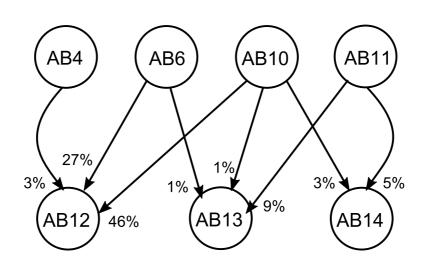

|     | 5.3.5                                                                                                                                               | Visualizing Transaction Execution                                                                                                                                                                                                                                                                                                 | 147                               |

| 5.4 | Profili                                                                                                                                             | ng Framework                                                                                                                                                                                                                                                                                                                      | 149                               |

| 5.5 | Summ                                                                                                                                                | ary                                                                                                                                                                                                                                                                                                                               | 151                               |

| Opt | imizat                                                                                                                                              | ions                                                                                                                                                                                                                                                                                                                              | 152                               |

| 6.1 | Motiva                                                                                                                                              | ation                                                                                                                                                                                                                                                                                                                             | 154                               |

| 6.2 | Relate                                                                                                                                              | d Work                                                                                                                                                                                                                                                                                                                            | 155                               |

| 6.3 | Optim                                                                                                                                               | ization Techniques                                                                                                                                                                                                                                                                                                                | 157                               |

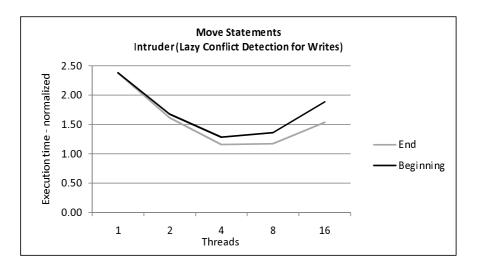

|     | 6.3.1                                                                                                                                               | Moving Statements                                                                                                                                                                                                                                                                                                                 | 157                               |

|     | 6.3.2                                                                                                                                               | Atomic Block Scheduling                                                                                                                                                                                                                                                                                                           | 159                               |

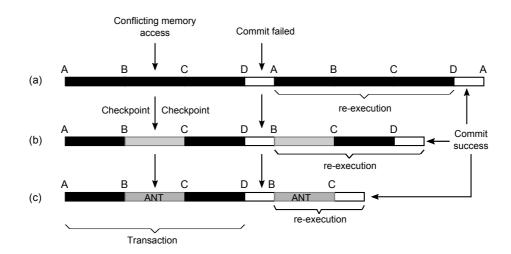

|     | 6.3.3                                                                                                                                               | Checkpoints                                                                                                                                                                                                                                                                                                                       | 159                               |

|     | 6.3.4                                                                                                                                               | Pessimistic Reads                                                                                                                                                                                                                                                                                                                 | 160                               |

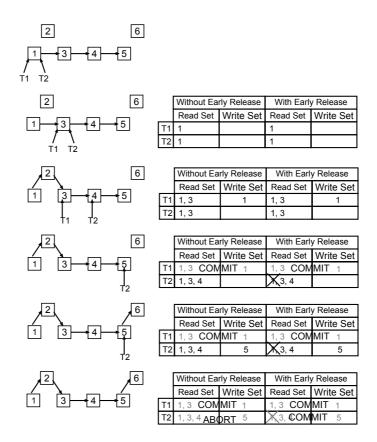

|     | 6.3.5                                                                                                                                               | Early Release                                                                                                                                                                                                                                                                                                                     | 162                               |

| 6.4 | Feedba                                                                                                                                              | ack Directed Compilation                                                                                                                                                                                                                                                                                                          | 164                               |

|     | 6.4.1                                                                                                                                               | Moving Statements                                                                                                                                                                                                                                                                                                                 | 164                               |

|     | 6.4.2                                                                                                                                               | Atomic Block Scheduling                                                                                                                                                                                                                                                                                                           | 165                               |

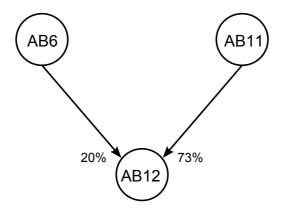

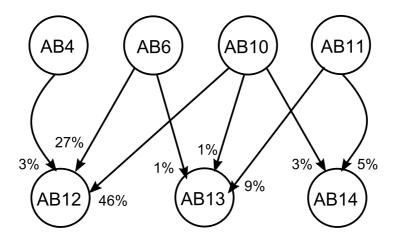

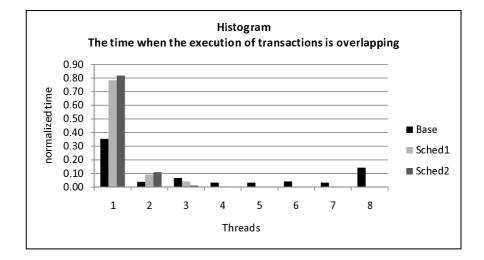

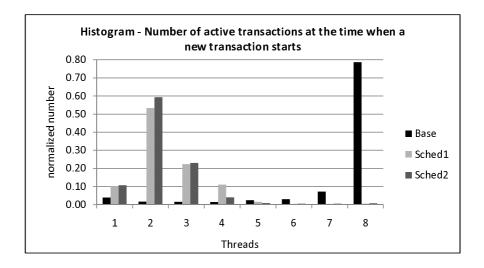

|     | 6.4.3                                                                                                                                               | Checkpoints                                                                                                                                                                                                                                                                                                                       | 165                               |