# On the design of power- and energy-efficient functional units for vector processors

# Ivan Ratković

**ADVERTIMENT** La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del repositori institucional UPCommons (<a href="http://upcommons.upc.edu/tesis">http://upcommons.upc.edu/tesis</a>) i el repositori cooperatiu TDX (<a href="http://www.tdx.cat/">http://www.tdx.cat/</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual **únicament per a usos privats** emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei UPCommons o TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a UPCommons (*framing*). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

ADVERTENCIA La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del repositorio institucional UPCommons (<a href="http://upcommons.upc.edu/tesis">http://upcommons.upc.edu/tesis</a>) y el repositorio cooperativo TDR (<a href="http://www.tdx.cat/?locale-attribute=es">http://www.tdx.cat/?locale-attribute=es</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio UPCommons No se autoriza la presentación de su contenido en una ventana o marco ajeno a UPCommons (<a href="https://rraming/framing/">framing/</a>). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING** On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the institutional repository UPCommons (<a href="http://upcommons.upc.edu/tesis">http://upcommons.upc.edu/tesis</a>) and the cooperative repository TDX (<a href="http://www.tdx.cat/?locale-attribute=en">http://www.tdx.cat/?locale-attribute=en</a>) has been authorized by the titular of the intellectual property rights **only for private uses** placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading nor availability from a site foreign to the UPCommons service. Introducing its content in a window or frame foreign to the UPCommons service is not authorized (framing). These rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author.

# On the Design of Power- and Energy-Efficient Functional Units for Vector Processors

# Ivan Ratković

Department of Computer Architecture

Universitat Politècnica de Catalunya - BarcelonaTech

A thesis submitted for the degree of

Doctor of Philosophy in Computer Architecture

October, 2016

Advisor: Dr. Adrián Cristal

**Co-Advisor:** Dr. Oscar Palomar

Co-Advisor: Dr. Osman S. Unsal

Co-Advisor: Prof. Mateo Valero

# **Abstract**

Vector processors are a very promising solution for mobile devices and servers due to their inherently energy-efficient way of exploiting datalevel parallelism. While vector processors succeeded in the high performance market in the past, they need a re-tailoring for the mobile market that they are entering now. Functional units are a key components of computation intensive designs like vector architectures, and have significant impact on overall performance and power. Therefore, there is a need for novel, vector-specific, design space exploration and low power techniques for vector functional units.

We present a design space exploration of vector adder (VA) and multiplier unit (VMU). We examine advantages and side effects of using multiple vector lanes and show how it performs across a broad frequency spectrum to achieve an energy-efficient speed-up. As the final results of our exploration, we derive Pareto optimal design points and present guidelines on the selection of the most appropriate VMU and VA for different types of vector processors according to different sets of metrics of interest.

To reduce the power of vector floating-point fused multiply-add units (VFU), we comprehensively identify, propose, and evaluate the most suitable clock-gating techniques for it. These techniques ensure power savings without jeopardizing the performance. We focus on unexplored opportunities for clock-gating application to vector processors, especially in active operating mode. Using vector masking and vector multilane-aware clock-gating, we report power reductions of up to 52%, assuming active VFU operating at the peak performance. Among other

findings, we observe that vector instruction-based clock-gating techniques achieve power savings for all vector floating-point instructions. Finally, when evaluating all techniques together, the power reductions are up to 80%.

We propose a methodology that enables performing this research in a fully parameterizable and automated fashion using two kinds of benchmarks, synthetic and "real world" application based. For this interrelated circuit-architecture research, we present novel frameworks with both architectural- and circuit-level tools, simulators and generators (including ones that we developed). Our frameworks include both design-(e.g. adder's family type) and vector architecture-related parameters (e.g. vector length).

Additionally, to find the optimal estimation flow, we perform a comparative analysis, using a design space exploration as a case study, of the currently most used estimation flows: Physical layout Aware Synthesis (PAS) and Place and Route (PnR). We study and compare post-PAS and post-PnR estimations of the metrics of interest and the impact of various design parameters and input switching activity factor ( $\alpha_I$ ).

# Acknowledgements

Pursuing a Ph.D. is a multi-year endeavour that can turn into a tedious and never ending journey. That was not my case, and I am thankful to many people without whom I would not have been able to complete my Ph.D. studies. While it is not possible to make an exhaustive list of names, I would like to mention a few. Apologies if I forget to mention any name below.

Firstly, I would like to express my sincere gratitude to my advisors Oscar Palomar, Osman Unsal, Adrian Cristal, and Mateo Valero for all the help and guidance they provided during my Ph.D. studies. Their support, confidence, and sound technical advice have played a major role shaping my research ideas into the contributions expressed in this thesis.

I am thankful to Professor Borivoje Nikolić, who accepted me kindly and provided me an opportunity to join Berkeley Wireless Research Center, UC Berkeley as a visiting scholar. I had a great and productive time in Berkeley thanks to Borivoje's positive attitude and enthusiasm.

My sincere thanks go to my former supervisor during my studies at the University of Belgrade, Veljko Milutinović, for his guidance and support.

I would also like to thank Professor Carlos Alvarez his useful advice and fruitful discussions.

I would also like to acknowledge all my colleagues from the office in Barcelona Supercomputing Center that helped me throughout my Ph.D. studies; for their insights and expertise in technical matters, and for their unconditional support that has been crucial to keep me sane. My special thanks go to my colleagues from the "Vector Group", Milan Stanić, Milovan Đurić, Timothy Hayes, Nikola Bežanić, and Tassadaq Hussain for the stimulating discussions, for the sleepless nights we were working together before deadlines, and for all the fun we have had in the last six years. I acknowledge to my colleagues Srđan Stipić and Javier Arias for great technical help and tips. Besides, I am thankful to Brian Richards, Vladimir Milovanović, Yunsup Lee and all my other colleagues from Berkeley Wireless Research Center.

Finally, I would like to thank to my friends and family for supporting me during this endeavour. I especially thank my parents Lidija and Živorad and my sister Svetlana for their unconditional love and care.

This thesis has been supported by the cooperation agreement between the Barcelona Supercomputing Center and Microsoft Research, by the Ministry of Science and Technology of Spain under the FPU National Plan (FPU12/06157), by the European Union (FEDER funds) under contracts TIN2007-60625, TIN2008-02055-E, TIN2012-34557, and TIN2015-65316-P, and by the European Union's Seventh Framework Programme (FP7/2007-2013) under the ParaDIME project (GA no. 318693).

# Contents

| 1 | Intr                          | oduction                           | 1  |  |  |  |

|---|-------------------------------|------------------------------------|----|--|--|--|

|   | 1.1                           | Motivation                         | 1  |  |  |  |

|   | 1.2                           | Vector Processors Background       | 8  |  |  |  |

|   |                               | 1.2.1 Power- and Energy-Efficiency | 10 |  |  |  |

|   | 1.3                           | Clock-Gating Background            | 12 |  |  |  |

|   | 1.4                           | Thesis contributions and overview  | 14 |  |  |  |

| 2 | Reference Vector Architecture |                                    |    |  |  |  |

|   | 2.1                           | VectorSim                          | 17 |  |  |  |

|   | 2.2                           | Execution                          | 18 |  |  |  |

|   | 2.3                           | Instruction Set Architecture       | 18 |  |  |  |

|   | 2.4                           | Vector Register File               | 19 |  |  |  |

|   | 2.5                           | Memory System                      | 20 |  |  |  |

|   | 2.6                           | High-Level VFU Configuration       | 20 |  |  |  |

| 3 | Estimation Flows              |                                    |    |  |  |  |

|   | 3.1                           | Introduction                       | 23 |  |  |  |

|   | 3.2                           | Metrics                            | 24 |  |  |  |

|   |                               | 3.2.1 Basic Metrics                | 24 |  |  |  |

|   |                               | 3.2.2 Derived Metrics              | 26 |  |  |  |

|   | 3.3                           | Methodology                        | 27 |  |  |  |

|   |       | 3.3.1     | Framework                                       | 27       |

|---|-------|-----------|-------------------------------------------------|----------|

|   |       | 3.3.2     | Design Parameters                               | 30       |

|   |       | 3.3.3     | Adder Families                                  | 31       |

|   |       | 3.3.4     | Power Estimation                                | 36       |

|   | 3.4   | Result    | ·s                                              | 37       |

|   |       | 3.4.1     | Area                                            | 37       |

|   |       | 3.4.2     | Timing                                          | 38       |

|   |       | 3.4.3     | Power                                           | 42       |

|   |       | 3.4.4     | Related Work                                    | 44       |

|   | 3.5   | Summ      | nary                                            | 45       |

| 4 | Evn   | loration  | n of Energy-Efficient Vector Adders             | 49       |

| 4 | 4.1   |           | uction                                          | 49       |

|   | 4.2   |           | odology                                         | 50       |

|   | 7.2   | 4.2.1     | Framework                                       | 50       |

|   |       | 4.2.2     | Framework Parameters                            | 51       |

|   |       | 4.2.3     | Test Benchmarks Generator - tBenchGen           | 52       |

|   |       | 4.2.4     | Test Benchmarks                                 | 53       |

|   | 4.3   |           | n Space Exploration                             | 54       |

|   |       | 4.3.1     | Adders Characteristics Discussion               | 54       |

|   |       | 4.3.2     | Multi-lane Effectiveness                        | 57       |

|   |       | 4.3.3     | Application-based vs. Random Data Benchmarking  | 59       |

|   | 4.4   |           | lection Guidelines                              | 60       |

|   | 4.5   |           | d Work                                          | 62       |

|   | 4.6   |           | nary                                            | 63       |

| = | Escal | امسمئامسا | of Enguery Efficient Vector Multiplians         | 67       |

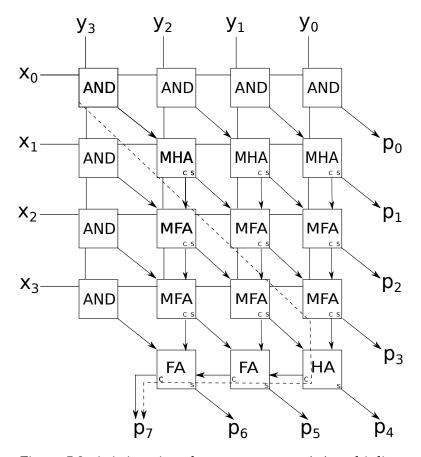

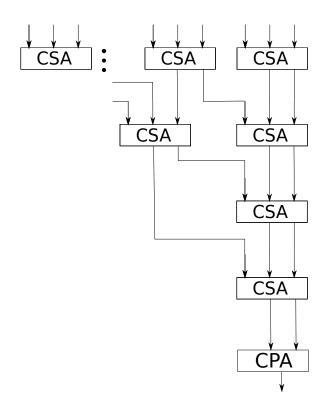

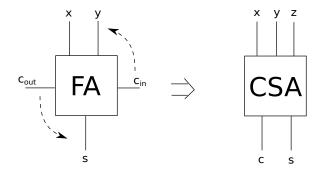

| 5 | 5.1   |           | n of Energy-Efficient Vector Multipliers uction | 67       |

|   | 5.2   |           |                                                 | 68       |

|   | 3.2   | 5.2.1     | Conformation Francescould                       | 68       |

|   |       |           | Exploration Framework                           |          |

|   |       | 5.2.2     | Framework Parameters                            | 70<br>72 |

|   | F 2   | 5.2.3     | Multiplier Families                             | 72<br>75 |

|   | 5.3   | -         | oliers' Characteristics                         | 75<br>75 |

|   |       | 5.3.1     | Area                                            | 75       |

|   |                      | 5.3.2        | Timing                                                  | <b>7</b> 5 |  |  |

|---|----------------------|--------------|---------------------------------------------------------|------------|--|--|

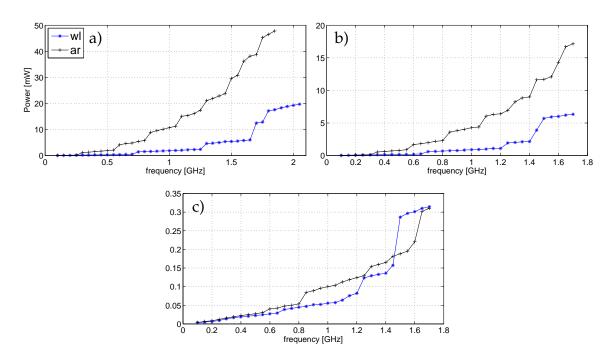

|   |                      | 5.3.3        | Power                                                   | 76         |  |  |

|   | 5.4                  | Multi-       | -Lane Effectiveness                                     | 78         |  |  |

|   | 5.5                  | VMU          | Design Guidelines                                       | 80         |  |  |

|   | 5.6                  | Relate       | ed Work                                                 | 83         |  |  |

|   | 5.7                  | Sumn         | nary                                                    | 83         |  |  |

| 6 | Low Power Vector FMA |              |                                                         |            |  |  |

|   | 6.1                  | Introd       | luction                                                 | 87         |  |  |

|   | 6.2                  | Related Work |                                                         |            |  |  |

|   | 6.3                  | Floati       | ng-Point Arithmetic Background                          | 88         |  |  |

|   |                      | 6.3.1        | Floating-Point Representation                           | 89         |  |  |

|   |                      | 6.3.2        | Fused Multiply-Add (FMA)                                | 90         |  |  |

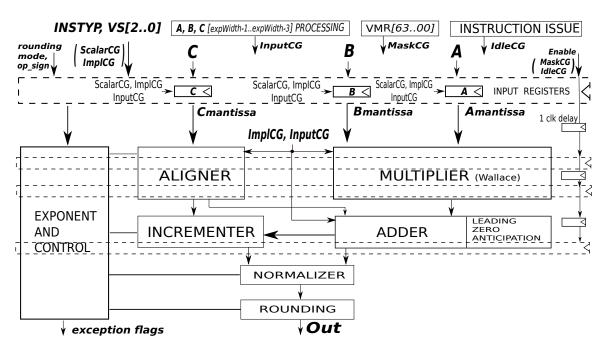

|   | 6.4                  | Propo        | sed Techniques                                          | 92         |  |  |

|   |                      | 6.4.1        | Scalar Operand Clock-Gating (ScalarCG)                  | 92         |  |  |

|   |                      | 6.4.2        | Implicit Scalar Operand Clock-Gating (ImplCG)           | 93         |  |  |

|   |                      | 6.4.3        | Vector Masking and Vector Multi-Lane-Aware Clock-Gating |            |  |  |

|   |                      |              | (MaskCG)                                                | 94         |  |  |

|   |                      | 6.4.4        | Input Data Aware Clock-Gating (InputCG)                 | 95         |  |  |

|   |                      | 6.4.5        | Idle Unit Clock-Gating (IdleCG)                         | 96         |  |  |

|   | 6.5                  | Metho        | odology                                                 | 97         |  |  |

|   |                      | 6.5.1        | Exploration Framework                                   | 97         |  |  |

|   |                      | 6.5.2        | Benchmarking                                            | 98         |  |  |

|   |                      | 6.5.3        | A Fully Parameterizable FMA Generator                   | 100        |  |  |

|   | 6.6                  | Evaluation   |                                                         |            |  |  |

|   |                      | 6.6.1        | Area Efficiency                                         | 102        |  |  |

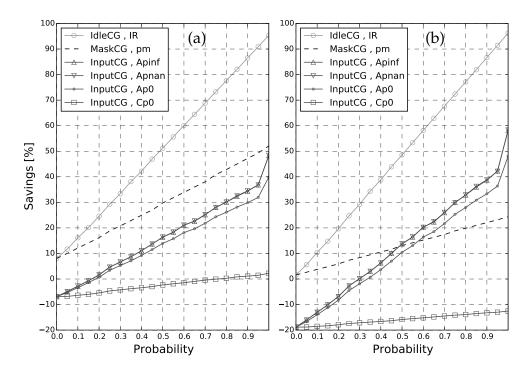

|   |                      | 6.6.2        | Per Technique Power Analysis                            | 103        |  |  |

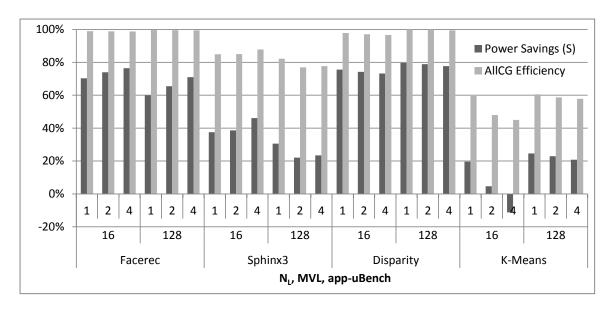

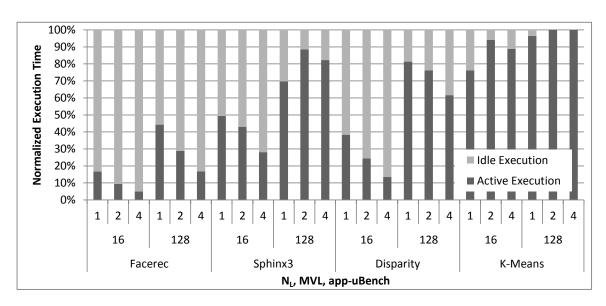

|   | 6.7                  | Real A       | Application-Based Combined Power Evaluation             | 106        |  |  |

|   | 6.8                  | Sumn         | nary                                                    | 110        |  |  |

| 7 | Con                  | clusio       | าร                                                      | 113        |  |  |

| 8  | Publications on the topic |                                                  |     |  |

|----|---------------------------|--------------------------------------------------|-----|--|

|    | 8.1                       | Publications from the thesis:                    | 117 |  |

|    | 8.2                       | Related publications not included in the thesis: | 118 |  |

| Re | eferei                    | nces                                             | 133 |  |

1

# Introduction

This thesis concerns the following two problems: selecting optimal vector functional unit (VFU) structure according to a variety of metrics and lowering VFU power; it also contributes methodologies that allow designers to explore two problems in a fully parameterizable, automated and comprehensive way. In this introductory chapter first we present the motivation of the thesis (Section 1.1) followed by an overview on vector processors (Section 1.2), clock-gating background (Section 1.3), and finally the thesis overview and contributions (Section 1.4).

# 1.1 Motivation

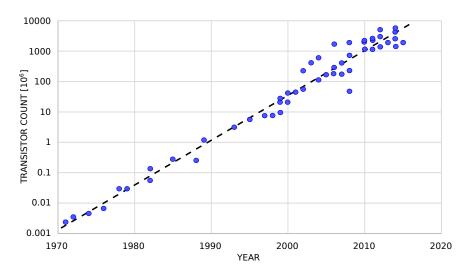

After the technology switch from bipolar to CMOS, in the 1980s and early 1990s, that enabled low power processing, processor designers had high performance as the primary design goal, leaving power and area as secondary goals. However, when it became apparent that further technology feature size scaling according to Moore's law (Figure 1.1) will lead to extreme power density (which could become extremely difficult or too costly to cool), power- and energy-efficiency turned into the primary design constraint for almost all computer systems.

Nevertheless, different computer systems have different demands. Let us consider two fast-growing markets such as mobile devices and data centers. The main design goal of mobile, battery constrained, devices is to achieve energy efficiency. However, computer systems like data centers suffer from both power density and

### 1. INTRODUCTION

Figure 1.1: Moore's law [76, 77] illustrated on Intel's microprocessors transistor count. The number of transistor doubles every two years. Adapted from [78].

energy consumption issues. The power density issue is related to cooling problems and it has recently become even more important with the appearance of the concept of "dark silicon" [35].

Nonetheless, it is still expected that each new generation of microprocessors has higher performance than the previous one. Since frequency does not scale with technology in an energy-efficient way anymore, we need changes at the architectural level that allow faster execution without a power increase [16]. In other words, we want higher performance without an excessive increase of power

Vector processors are an inherently energy-efficient architecture [7, 67, 66, 65, 118] for applications that exhibit data-level parallelism (DLP), i.e. that operate on vectors of independent elements (described in Section 1.2). It has been observed that the best vector-based machines are generally faster and/or more energy-efficient than scalar multicore processors [66]. In some cases, scalar multicores perform better though at a greater energy cost. There are server and mobile workloads with a lot of DLP. For example, Facebook's face recognition feature, running on data centers; or Google's offline voice typing system introduced in Android 4.1 (Jelly Bean). Taking all this into account, we consider that low power vector proces-

<sup>&</sup>lt;sup>1</sup>Dark silicon (the term was coined by ARM [6]) is defined as the fraction of die area that goes unused due to power, parallelism, or other constraints.

sors are quite interesting designs for mobile devices and servers. These computer systems have fairly different design goals than early vector processors that were used almost exclusively for supercomputing. Although considered as a power and energy-efficient solution for workloads that exhibit data-level parallelism, vector processors were not explored sufficiently from a low power perspective in the past. Their designers prioritized performance without caring much about power, and this is not desirable in today's energy-conscious climate. Therefore, modern vector processors require a rethink and new design-space explorations of their functional units in an energy- and power-efficient manner.

There are architecture-related characteristics, specific only to vector processors, that affect functional unit (FU) usage. For example, the activity factor (described in Section 3.2.1) of a VFU is affected by architectural parameters, such as the maximum vector length or number of vector lanes. We have observed that the data of a vector are correlated, so the activity factor of a VFU is less than that of a functional unit operating with scalar data. An additional characteristic of VFUs is that they are typically fully pipelined. The reason for that is that in vector processing the critical metric is the throughput, so we typically we operate on long vectors (a long sequence of the same consecutive operations). For that reason, non-pipelined arithmetic units are not efficient in vector processing. Here we have the opposite situation than in scalar processing where we most care about the latency. Obviously, vector and scalar arithmetic units have different design goals. Therefore, an arithmetic unit's structure that is optimal for scalar architecture may not be optimal for the vector one.

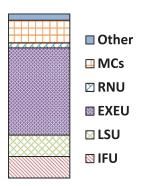

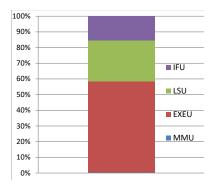

FUs take a significant part in modern processor budget (Figure 1.2), especially in the case of vectors (Figure 1.3). Moreover, it has been observed that FUs are processor's thermal hotspots [99]. VFUs are likely to have even higher temperature since, due to its faster execution, a vector core dissipates more power than the equivalent scalar one [67]. This makes the concern about the hotspots more significant.

To narrow down the discussion, we focus on the most common arithmetic operations in vector processing, present in practically all vector workloads: integer and floating point addition and multiplication.

### 1. INTRODUCTION

Figure 1.2: Power breakdown of an Alpha-based FinFET core. Core components: integrated memory controller (MC), renaming unit (RNU), execution unit (EXEU), load-store unit (LSU), and instruction fetch unit (IFU). Adapted from [107].

Figure 1.3: Power breakdown of ARM-based vector core [103] averaged for a number of benchmarks. Core components: IFU, LSU, EXEU, and memory management unit (MMU).

Addition is one of the most used operations in both general-purpose and application-specific processors and this also applies to vector processors. This operation is included in practically all arithmetic algorithms. Moreover, it is often in the processor's critical path [117]. Therefore, selecting an appropriate adder unit is of crucial importance for an energy-efficient vector processor design.

Multiplication is a fundamental operation in many algorithms that exhibits a lot of DLP, such as image processing. Its importance has increased in the last decade due to ubiquitous media processing. Additionally, multiplication is a common operation in most signal processing algorithms. Multipliers have large area, long latency and consume considerable power. They are a major source of power dissipation in processors specialized for digital signal processing workloads. High

power dissipation in these structures is mainly due to the switching of a large number of gates during multiplication. In addition, much power is also dissipated due to a large number of spurious transitions on internal nodes. Consequently, low power multiplier design has been an important part of low power very-large-scale integration (VLSI) system design.

Floating point fused multiply-add, being a power consuming FU, deserves special attention. Abundant floating-point fused multiply-add (FMA) is typically found in vector workloads such as multimedia, computer graphics or deep learning workloads [102]. Although in the past FMAs have been used for high-performance, they recently have been included in mobile processors as well [91, 65, 118]. Moreover, energy- and power-efficient mobile processors are entering the server market as well [108]. In contrast to high-performance vector processors (e.g. NEC SXseries [74] and Tarantula [36]) that have separated units for each floating-point operation, (e.g. separate floating-point (FP) adder and multiplier) mobile vector processors' resources are limited. Thus, we typically have a single unit per vector lane capable of performing multiple FP operations rather than separate FP units [65, 118]. Additionally, having the FP computations localized inside the same unit reduces the number of interconnections, which is both power- and performance-efficient. Apart from that, FMA units offer better accuracy (single, instead of two round/normalize steps) and improved performance (shorter latency) compared to a multiplication followed by an independent addition.

A well-known method to reduce switching power in FUs (and other synchronous designs) is clock-gating (described in Section 1.3). In addition to its straightforward application to idle units, there are unexplored opportunities for this method, especially when considering active operating mode. Furthermore, there are characteristics of vector processors that provide additional clock-gating opportunities. Moreover, in addition to reducing dynamic power, clock-gating can also reduce static (leakage) power since leakage associated with CMOS devices is exponentially dependent on temperature [51, 61]<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>Although leakage power has increased its importance (or weight) in recent years, when we assume low leakage libraries, it is still an order of magnitude less than dynamic power. The introduction of FinFET, high k devices, and FD-SOI has played an important role in maintaining the leakage low.

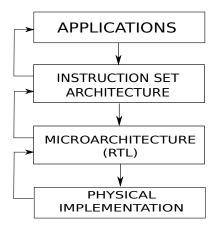

Figure 1.4: A holistic, multi-layered approach in processor design optimizations.

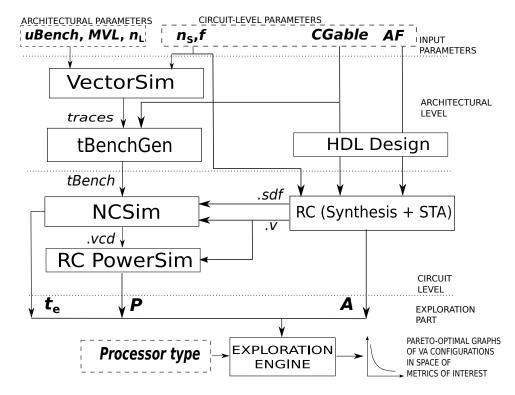

From the aforementioned facts we can conclude that improving energy- and power-efficiency by exploring and selecting optimal VFUs structure depending on the architectural parameters and workloads, and by applying low power techniques such as advanced clock-gating is of crucial importance. To achieve optimal results, a holistic optimization approach should be employed, i.e. bridging the gap between circuits and system should be accomplished (Figure 1.4).

We need a novel methodology that enables a joint circuit circuit-system design space explorations and optimizations using low power techniques such as clockgating. For such a methodology we need a novel integrated framework with both architectural- and circuit-level tools. The framework should include both design-(e.g. arithmetic family type) and vector architecture-related parameters (e.g. vector length). This is necessary for aforementioned exploration as we need to observe how architectural-level parameters (e.g. vector length) affect the circuit-level metrics (e.g. adder's power dissipation) and how circuit-level parameters (e.g. adder's clock cycle) impact the execution time of a microbenchmark.

The final goal of a design-space exploration is to obtain metrics of interest (power, timing, area). Although it is not possible to measure precisely the metrics of interest of a design until it is fabricated, there are various estimation methods aimed for different design phases, which differ in levels of accuracy and estimation speed. The most accurate way to simulate a design is to use transistor-level post-place and route (PnR) data and SPICE. However, such detailed simulation is not possible in early phases of the design process. Moreover, it is impractical for a

large number of test vectors and numerous design points as its computational complexity leads to an unaffordable long time frame to get the results. On the other hand, estimation processes done in early phases (e.g. post-synthesis results) are less detailed which makes them faster. Yet, decreased accuracy of these processes may lead a designer to wrong conclusions.

The most widespread estimation flows work at the gate-level. Assuming this modeling granularity, PnR models are more accurate than synthesized ones as they are closer to fabricated chips. Conversely, synthesis estimation flow deals with simpler models and requires fewer steps, which makes it faster but less accurate than PnR flow. Traditional synthesis tools use wire-load models based on fanouts which do not provide accurate wire delay information. Wiring delay cannot be ignored, and it even increases its importance with further technology scaling [57]. Physical layout Aware Synthesis (PAS) tends to overcome the drawbacks of traditional synthesis tools and to provide post-PAS results which are closer to post-PnR ones. The main advantage of PAS tools over the traditional synthesis flows is their floorplan awareness that provides more realistic interconnect modeling.

Selecting an appropriate estimation method for a given technology and design is of crucial interest as the estimations guide future project and design decisions. The accuracy of the estimations of area, timing, and power (metrics of interest) depends on the phase of the design flow and the fidelity of the models.

Considering design methodologies to tackle the aforementioned problems, we consider reusability and parameterization not just as an on-going trend but as a requirement. The design process has to evolve to provide a way to achieve power-and performance-efficient designs that are cost-effective. The traditional solution to face this problem, building application specific hardware instances, becomes exceedingly expensive. Therefore, there is a need for digital design rethink. An emerging solution is to design fully parameterizable design flows with hardware generators included, instead of the specific hardware instances [95, 78].

# 1.2 Vector Processors Background

Vector processors operate on vectors of data within the same instruction<sup>1</sup>. The key idea behind vector processors is to collect a set of data elements in memory, place them into a large register, operate on them, and then store them back. Vector instructions are a compact way of capturing DLP, and are a simple, scalable way to organize large amounts of computation. Vector processing receives its name because it is designed to work on long one-dimensional arrays, or vectors, of data.

Vector instruction set architecture (ISA)s provide an efficient organization for controlling a large amount of computation resources. Vector instructions offer a good aggregation of control by localizing the expression of parallelism. Furthermore, vector ISAs emphasize local communication and provide excellent computation/area ratios. Vector instructions express DLP in a very compact form, thus removing much redundant work (e.g. instruction fetch, decode, and issue). For example, a vector floating-point FMA instruction (FPFMAV) indicates the operation (FMA), three source vector registers and one destination vector register. Thus, tuples of three elements, one from each source register, are the inputs for the vector fused multiply-add unit (VFMA), and the result is written to the destination. All tuples can be processed independently, and multiple elements could be accommodated in a vector register.

The register file is designed so that a single named register holds a number of elements. The entire architecture is designed to take advantage of the vector style in organizing data. Additionally, the memory system of vector processors allows efficient strided and indexed memory access. The number of elements of a vector register is denoted by the maximum vector length ( $MV_L$ ), and in this thesis it ranges from 16 to 128, thus including in the study both long vector and relatively short vector designs. Occasionally fewer elements than the  $MV_L$  are used, which reduces the effective vector length ( $EV_L$ ). The vector register file typically consists of eight or more vector registers [49]. The number and the length of vector registers to provide is a key decision in the design of a vector unit. The configuration of a

<sup>&</sup>lt;sup>1</sup> On the contrary, a "traditional", non-vector, processor can be defined as a processor that operates on scalar values, hence known as scalar processors.

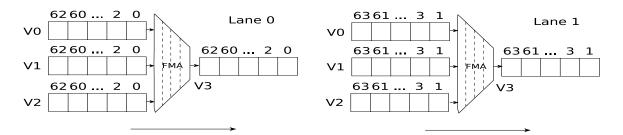

Figure 1.5: A 2-lane, 4-stage VFMA ( $MV_L = EV_L = 64$ ) executing FPFMAV V3<-V0, V1, V2.

vector register file is the programmer-visible partitioning of the vector element storage into vector registers of a given  $MV_L$ .

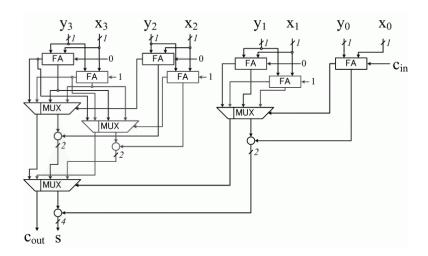

The vector execution model streamlines one vector register element per cycle to a fully pipelined VFU. As a result, the execution time of a vector instruction is the start-up latency (number of stages) of the VFU plus the  $EV_L$ . A common technique to reduce this time is to implement multiple vector lanes through replicated lock-stepped VFUs. Each lane accesses its own "slice" of the vector register file, which reduces the need for increasing the number of ports, typically associated with a larger number of VFUs. Lock-stepping the lanes simplifies control logic and is power-efficient. These concepts are illustrated in Figure 1.5. Using multiple lanes can increase the energy-efficiency of a vector architecture (sections 4.3.2 and 5.4).

Two techniques that significantly increase the performance are vector chaining and dead-time elimination. Chaining is vector equivalent of data forwarding; it allows a vector operation to start as soon as the individual elements of its vector source operand become available. Therefore, the results from the first functional unit in the chain are forwarded to the second functional unit. Dead-time elimination allows the processor to use ALU immediately after the current instruction.

Additionally, an interesting feature that vector processors typically offer is a vector mask control. It uses an  $MV_L$ -bit vector mask register (VMR) for indicating which operations of the vector instruction are actually performed. In other words, vector instructions operate only on the vector elements whose corresponding entries in the VMR are '1'.

Conventional vector processors should not be confused with single instruction multiple data (SIMD) multimedia extensions such as AVX-512 [9] that are an alternative way to exploit DLP and indicate operations to perform on multiple ele-

### 1. INTRODUCTION

ments<sup>1</sup>. The main difference of these extensions with a conventional vector processor is that they exploit subword-SIMD parallelism and are typically implemented with multiple VFUs that operate on all independent elements in parallel. Having a VFU per element to operate on all them in parallel would be inefficient for vector processors because they operate on much longer vectors. Instead, VFU is fully pipelined, and the elements of the vector register are streamlined to the unit, one per cycle, possibly using a small number of vector lanes.

The reference vector architecture that we use in this thesis is described in Chapter 2.

# 1.2.1 Power- and Energy-Efficiency

Vector processors provide power- and energy-efficiency in several ways [7]:

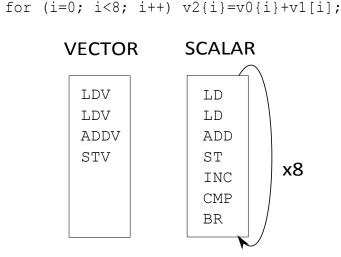

- **Instruction fetch.** The most obvious reduction is in instruction fetch, decode, and dispatch, as mentioned above. For vectorizable code, a vector unit significantly reduces the number of instruction fetches. Vector instructions also remove much of the interlock and dispatch logic overhead. These concepts are illustrated on Figure 1.6 by showing an example of the reduced instruction count compared to an equivalent execution on a scalar processor.

- Register file access. Operations within a vector instruction access the vector register file in a regular pattern, so a high-bandwidth vector register file can be built from smaller, fewer-ported banks. In contrast, a superscalar architecture with its flexibility to access any combination of registers for any operation requires full multiported access to the entire register file storage.

- **Datapath data.** Vector instructions group similar operations, therefore, it is likely that there is much greater bit-level correlation between successive elements in a vector than between successive instructions executed in a scalar processor. This reduces power dissipation (see Section 4.3.1).

<sup>&</sup>lt;sup>1</sup> Vector processors are SIMD architectures in Flynn's taxonomy [40], although by SIMD we refer to such type of multimedia extensions.

Figure 1.6: Vector vs. scalar processor instruction count using array addition as an example. In the scalar case we need to execute 8 times the listed 7 instructions, while in the vector case we need just 4 vector instructions.

- Datapath control lines. A VFU executes the same operation on a set of elements, so datapath control signals are only switched once per vector. This should reduce switching activity compared to a scalar architecture where different types of operation are time multiplexed over the same FUs, and hence datapath control lines are toggled more frequently.

- Memory accesses. Vector memory operations present regular data access

patterns to the memory system, which enables further energy savings. For

example, unit-stride vector memory accesses may only require one, or at most

two, TLB accesses per vector of operands.

The main sources of potential increases in switching activity per operation are in structures that provide inter-lane communication, including control broadcast and the memory system crossbar. This inter-lane cost can be reduced by using highly vectorizable algorithms that avoid inter-lane communication, and by adding caches adapted for vector processors that reduce lane interactions with memory.

# 1.3 Clock-Gating Background

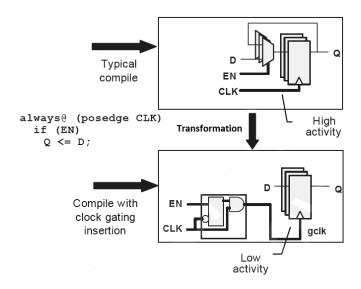

Clock-gating is a well known method to reduce switching power in synchronous pipelines [85]. It is a widely used power saving optimization method and practically a standard in low-power design. It is the most efficient power reduction technique for active operating mode, especially because dynamic power remains dominant over the static power for logic. The early unpopularity of clock gating was due to the inability of the tools of that time to deal with the timing implications of the gated clock signals and by the reduced fault coverage achieved by logic testers [81]. Clock gating was originally conceived as a system level power optimization technique aiming to reduce the power dissipated on the clock network by deactivating parts of the system that are idle. Its applicability has been extended to the register level as a power efficient implementation of registers on a hold condition.

The goal is to "gate" the clock of any component whenever it does not perform useful work. The underlying circuit mechanism is presented on Figure 1.7. A register candidate for clock-gating is shown on the upper part of Figure 1.7. During a hold condition, the register preserves its previous value at a high power cost. Unnecessary power is dissipated on: (1) the clock tree with its buffers and clock lines, (2) the register itself, (3) logic between the registers, and (4) the multiplexors on the feedback paths. By controlling the clock driving the clock input of the register (lower part of Figure 1.7), reloading is only conditionally performed resulting in both reduced power consumption and area overhead. Due to the high potential savings at low cost, clock-gating is fully automated in most commercial synthesis tools [32, 106].

Since it can reduce power significantly, the conditions under which clock-gating can be applied should be extensively studied and identified. A widely used approach is to clock-gate a whole FU when it is idle. An advanced approach is to use a finer granularity (than the whole FU) and to clock-gate FUs on the internal pipeline stage level i.e. only stages where instructions are present are clocked. We call this approach idle clock-gating technique - *IdleCG* (see Section 6.4.5). A complementary, more advanced and challenging approach is to clock-gate the FU or its sub-blocks when it is active, i.e. operating at peak performance. We call these

Figure 1.7: Clock-gating transformation. Adapted from [39].

techniques active clock-gating techniques - *ActiveCG* (see sections 6.4.1, 6.4.2, 6.4.3, and 6.4.4).

While on the circuit level clock-gating is standardized and in most cases automated with library, the real challenges are at the architectural level as an extensive investigation has to be done in order to explore the conditions under which clockgating can be applied (i.e. *Enable* signal generation). In order to prevent timing overheads, enable signal generation has to be done on-time, i.e. it must not be on the critical path.

Regarding alternative gating low power techniques, an important technique is power gating [56, 3, 94]. It is especially important in lowering the leakage power. Reasons why we studied clock-gating rather than power-gating are:

- The main goal of clock-gating is dynamic power suppression, while the main goal of power gating is leakage power suppression. In our experiments, the leakage is practically negligible, and the reasons are explained in sections 3.2.1 and 6.6.

- Clock-gating has much finer granularity than power-gating, thus allowing us to gate not only the whole VFU but its components as well.

### 1. INTRODUCTION

- Clock-gating has low or no timing overhead which is not a case with power gating [56, 62]. Turning power gating mechanism on and off incurs timing overhead, thus, it is more suitable for lowering power in idle mode (long idleness) than in active operating mode (short idleness). During active operating mode (the one that this research targets) gate/ungate frequently happens (often per cycle), thus the overhead of the mechanism can be unacceptable.

- Power-gating physical implementation is more complex and require dealing with power and signal integrity issues [1, 96, 115].

## 1.4 Thesis contributions and overview

In this thesis we try to solve the problems listed in the Motivation (Section 1.1) with the following main thesis' contributions:

- A deep multi-level investigation on achieving high power and energy efficiency of VFUs, in particular of: vector adders (Chapter 4), multipliers (Chapter 5) and IEEE 754-2008 compliant floating point FMA (Chapter 6). We have decoupled 32-bit vector machine with support for 64-bit floating point and TSMC40LP as target architecture and technology, respectively. We achieve these goals mainly in two complementary manners.

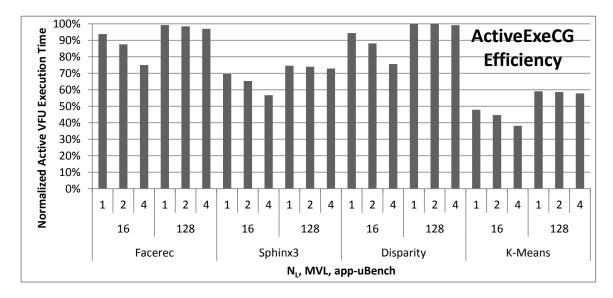

- We identify, propose, and evaluate in-depth the most suitable clock-gating techniques for VFU running at peak performance periods without jeopardizing performance (Chapter 6). We look beyond classical clock-gating: we examine additional opportunities to avoid unnecessary activity in vector workload executions. We present the first proposal of active clock-gating techniques for VFU. Using only one of these techniques can achieve up to 52% of power reductions. Savings of up to 80% are available when the techniques are applied together on a VFU running a variety of benchmarks. This is a consequence of the fact that clock-gating efficiency (percentage of time that clock-gating technique(s) is used) is quite high, often close to 100%.

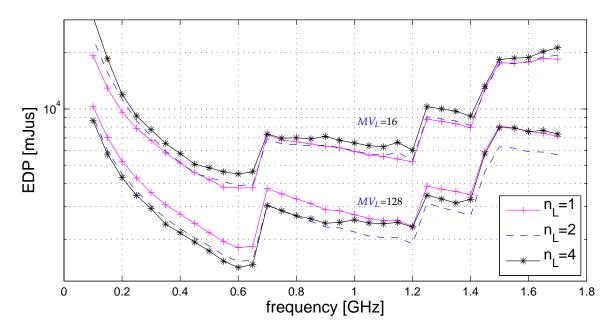

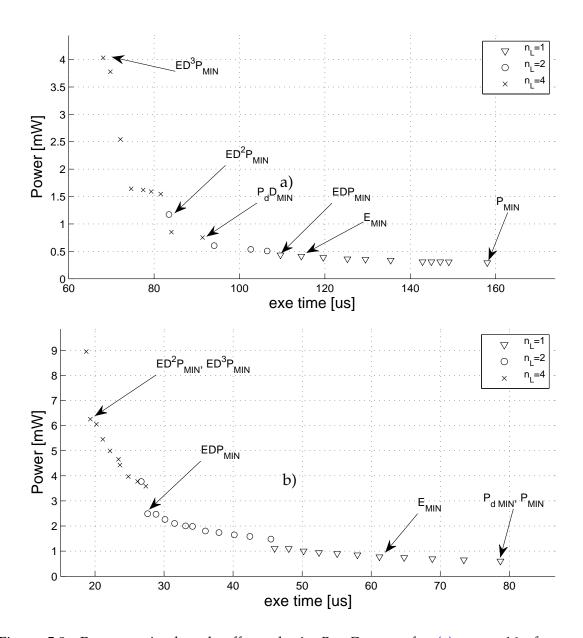

- A comprehensive (power, delay, energy, area, power density) joint circuit-system design space exploration of vector adders (Chapter 4) and multipliers (Chapter 5) for vector processors. The exploration includes circuit-level parameters like the number of pipeline stages, clock-gating support, and arithmetic family, as well as architectural parameters such as MVL and benchmarking. We discover that vector multi-lane is useful for achieving low Energy-Delay products, and beats increasing frequency as a measure to achieve energy- and thermal-efficient speed-up, especially for long vectors lengths. Finally, we provide guidelines on optimal vector adder unit (VA) and vector multiplier unit (VMU) configuration selection for different low power vector architectures.

- A novel methodology that includes exploration frameworks. In order to join architectural-level information (e.g. microbenchmarks) with circuit-level outputs (e.g. power measurements), and accomplish in that way all aforementioned explorations, we developed automated and integrated architecture-circuit exploration frameworks (different variants of frameworks are present in all the chapters) that consist of several generators and simulators at different levels. The frameworks assume both synthetic and real application-based benchmarking (SPEC [101], SDVB [112], and STAMP [72]) and include a variety of parameters at all the abstraction levels from Figure 1.4. Additionally, it includes both hardware (Chisel-based) and software generators. The use of generators facilitates design space explorations through sweeping the parameters of the design. The basis of the frameworks is explained in Chapter 3.

- Development of physical layout aware synthesis (PAS) and PnR estimation flows and their comparative analysis in terms of power, timing, area, and the flow completion time using adders as a case study (Chapter 3). We analyze side-effects of clock-gating, pipelining, and extensive timing optimizations. We perform this analysis using various design parameters, including switching activity factor input switching activity factor ( $\alpha_I$ ). The estimation flows serve as a basis for the above mentioned frameworks.

### 1. INTRODUCTION

The aforementioned chapters that present these contributions are complemented by Chapter 2 that describes reference vector architecture used in the rest of the chapters, as well as vector simulator that we use. Additionally, chapters 8 and 7 list the publication of the thesis and conclude the thesis, respectively.

# Reference Vector Architecture

In this chapter, we present vector microarchitecture that we use as an assumed reference in the rest of the thesis<sup>1</sup>. For vector architecture modeling we use vector simulator *VectorSim*. The main configuration parameters are listed in Table 2.1 and explained in subsequent chapters.

### 2.1 VectorSim

We built VectorSim based on the vector architecture library (VALib) and the SimpleVector simulator (both developed in our research group [102]). VALib is a library that implements vector instructions and allows rapid manual vectorization and characterization of applications. SimpleVector is a simple and very fast trace-based simulator which helps to estimate the performance of a vector processor. We took advantage of the fact that both tools have been designed to be easily extended with new instructions or implementation alternatives. Therefore, we modify them to satisfy our research goals and to enable its integration in our exploration frameworks. High-level VectorSim configuration is presented in Table 2.1.

<sup>&</sup>lt;sup>1</sup>Vector processing background is provided in Section 1.2.

<sup>&</sup>lt;sup>1</sup>VFU and ALU latencies are variable as they are design parameters in our research (see sections 3.3.2, 4.2.2, 5.2.2, and 6.5.3)

### 2. REFERENCE VECTOR ARCHITECTURE

Table 2.1: High-level *VectorSim* configuration.

| Execution            | 32-bit in-order vector core; decoupled vector and scalar core; vector chaining.        |  |  |

|----------------------|----------------------------------------------------------------------------------------|--|--|

| Vector Register File | $MV_L$ : 16, 64, or 128 elements; Number of registers: 8.                              |  |  |

| VFU                  | $n_L$ : 1, 2, or 4; 1 32-bit arithmetic logic unit (ALU), 1 64-bit VFMA <sup>1</sup> . |  |  |

| Memory System        | L2 (direct access to L2, shared with scalar core): 1MB, 4-way, 128b cache line,        |  |  |

|                      | hit latency: 7ns, miss latency: 70ns; 1 load unit, 1 store unit.                       |  |  |

### 2.2 Execution

We setup *VectorSim* to model a decoupled 32-bit vector machine with support for 64-bit floating point. The decoupled execution model assumes separated in-order vector and scalar execution units [36, 2, 65, 118]. They share instruction fetch and decode, and they separate issue logic and functional units, allowing in that way independent scalar execution. In-order execution is common in low power processors and performs more efficient in vector than in scalar processing as in vector architectures the drawbacks of in-order execution are diminished, especially if the vectors are long. As a result, the FUs are kept busy. Also, many modern low power processors are in-order due to its simplicity (e.g. Intel Bonnell (Atom) [59] and some of ARM Cortex-A architectures [27, 28, 24, 25, 26]). Additionally, we model chaining and dead time elimination. For  $MV_L$ , in our experiments, we choose the following values: 16, 64, and 128.

# 2.3 Instruction Set Architecture

We extend the ISA of *VaLib*, which is inspired by traditional register-based vector machines, e.g. CRAY and CONVEX. Among other upgrades, we added a set of vector FMA instructions. The instructions can be grouped into the following classes:

Arithmetic and logical. These instructions are common operations such as addition, multiplication, logical bitwise operations, etc. They can operate in vector-vector or vector-scalar mode. The exception is the FMA instruction that has 3 operands and more combinations of vector and scalar operands (see Table 6.4). Most instructions support masking.

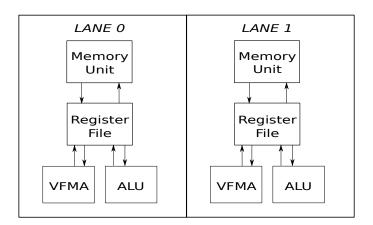

Figure 2.1: A 2-lane vector datapath.

- Memory. There are instructions for unit-stride, strided and indexed access.

Some variants support masking, which is useful to access elements conditionally.

- Reduction. This class includes sum, max, and min.

- Bit/element manipulation. Examples of this class include instructions to read or write individual elements of a vector register, or to compress a register according to a vector mask.

# 2.4 Vector Register File

Our configuration assumes 8 vector registers. We find this number is sufficient for all the workloads we examined. Each lane has its own slice of register file. We rely on the regular access pattern (a characteristic of vector architectures) in order to keep number of R/W ports small. For a low power vector processor it is important to keep the usage of vector register file low. In order to achieve that, the compiler plays a big role. The vector part of the code that we use is compiled by hand, so we avoid unnecessary usage of vector registers.

A 2-lane vector data path is depicted on Figure 2.1, where we can see a 2-lane partitioning of the vector register file.

# 2.5 Memory System

Vector load-store unit. The vector memory unit handles the memory instructions and loads or stores a vector to or from cache memory. The vector loads and stores are fully pipelined, so that words can be moved between the vector registers and cache memory with a bandwidth of 1 word per clock cycle (if accesses hit the cache), after an initial latency. We have 1 load and 1 store unit. More than that would exceed a low power processor budget.

### Cache memory.

Cache configuration (and memory system in general) has significant impact on the execution time for vector processors. In our model, the vector unit directly accesses the L2 cache (shared with the scalar unit). This technique has been proposed to facilitate the inclusion of vector units in microprocessor designs [84, 36, 2, 65, 118]. Accessing the L2 instead of the L1 allows not modifying the design of the L1 interface in the scalar core, which is a critical component of the design, typically in the critical path. By leaving this interface unmodified, we can safely focus on the vector component of the design. Vector code benefits from the large cache lines that L2 can provide. By interfacing the cache hierarchy we can provide enough bandwidth and exploit data locality. As it is larger than L1, L2 is more suitable for multi-banking implementation. Vector processors benefit from using cache banks rather than interleaving mainly due to efficient access to words that are not sequential.

# 2.6 High-Level VFU Configuration

The vector execution engine is organized as  $n_L$  identical vector lanes (Figure 2.1). Possible values of the number of lanes ( $n_L$ ) are 1, 2, and 4. In our experiments, we do not examine more lanes as it would not satisfy well a low power core budget<sup>1</sup>. Moreover, values that we choose are typical in vector processor design [49]. Each lane has a slice of the vector register file, a slice of the vector mask file, 1 vector integer ALU, 1 VFMA, and a private TLB. There is no communication across lanes,

<sup>&</sup>lt;sup>1</sup>The total number of functional unit per core is in accordance with many other low power processors [27, 28, 24, 25, 26, 59, 60, 83]

except for gather/scatter, reduction, and compress instructions. In addition to the vector ALU, each lane also includes 1 logic unit that handles logic operations, shifting and rotating. We assume the division is done in software, since it is rare in vectorizable applications and the hardware support is costly. Additionally, a control unit is needed to detect hazards, both from conflicts for the functional units (structural hazards) and from conflicts for register accesses (data hazards).

# **Estimation Flows**

# 3.1 Introduction

In this chapter, we perform a comparative analysis of PAS and PnR flows using design space exploration of low power 32-bit adders as a case study. Additionally, this chapter serves as a foundation for the rest of chapters. These estimation flows are very important parts of the methodology that we propose and use across the thesis.

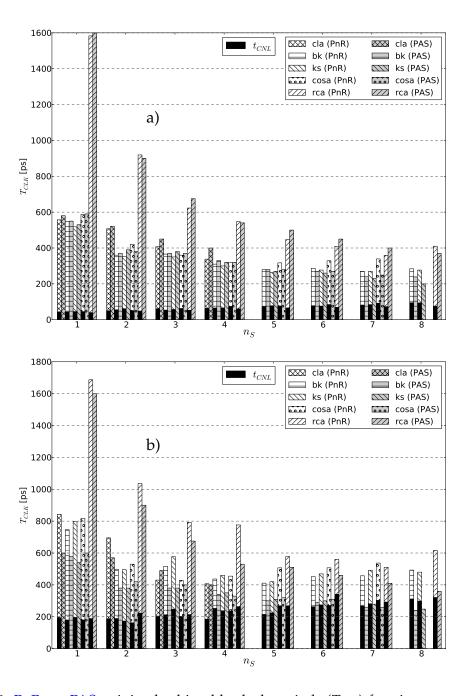

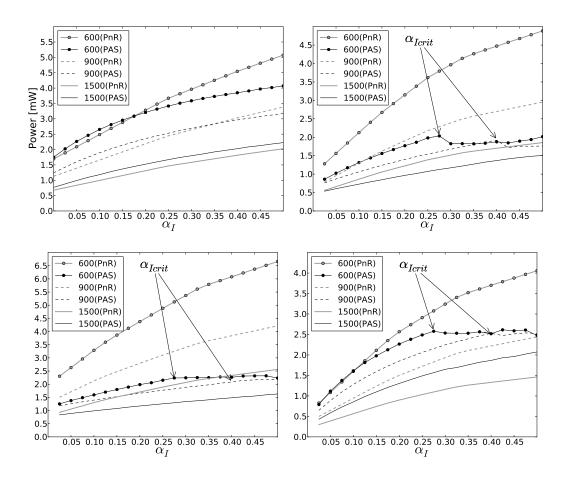

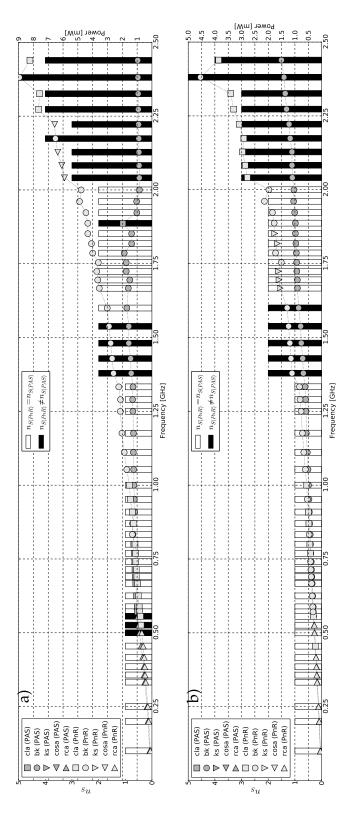

We study and compare post-PAS and post-PnR estimations of the metrics of interest and the impact of various design parameters and input switching activity factor ( $\alpha_I$ ). Specifically, we compare estimations in terms of area, timing, and power for several design parameters: clock cycle, adder family, number of pipeline stages, and clock-gating. We study how adder area, timing and power differ with respect to the applied estimation flow. Adders are particularly interesting for this study because they are fundamental microprocessor units, and their design involves many parameters that create a vast design space. A design space exploration with a large number of design points allows observing advantages and drawbacks of estimation flows in a comprehensive way. We show cases in which the post-PAS and post-PnR estimations could lead to different design decisions, especially from a low-power designer point of view. We examine and explain in which cases post-PAS results are (or are not) reliable, compared to post-PnR (since PnR ones are more accurate and close to post-fabrication results).

Since power has become the primary design constraint for the majority of computer systems, we pay special attention to power dissipation. In contrast to area and timing estimation of a VLSI design that does not require knowledge of the inputs, we cannot have a solid total power estimation without information about the inputs. Therefore, we evaluate how the power numbers obtained in post-PAS and post-PnR estimations vary with input switching activity factor ( $\alpha_I$ ).

### 3.2 Metrics

This section defines the metrics of interest that are used in the rest of the chapter and the thesis. We can define two types of metrics which are used in digital design - basic and derived metrics.

### 3.2.1 Basic Metrics

Switching activity factor ( $\alpha$ ) of a circuit node is the probability the given node will change its state from 1 to 0 or opposite at a given clock tick. Activity factor is a function of the circuit topology and the activity of the input signals. The activity factor is necessary in order to analytically compute (estimate) dynamic power of a circuit.

*Capacitance (C)* is the ability of a body to hold an electrical charge, and its SI unit is the *farad (F)*. Capacitance can also be defined as a measure of the amount of electrical energy stored (or separated) for a given electric potential.

*Energy (E)* is defined as the ability that a physical system has to do work on other physical systems and its SI unit is the *joule (J)*. The total energy consumption of a digital circuit can be expressed as the sum of dynamic and static energy:

$$E_{tot} = E_{dyn} + E_{stat}. (3.1)$$

Dynamic energy has three components that are the result of the next three sources: charging/discharging capacitances (switching), short-circuit currents, and glitches. For processor designers the most relevant energy is the switching one, as the others components are parasitic, thus are not directly affected with architectural level low power techniques. According to the general energy definition,

dynamic energy in digital circuits can be interpreted as: When a transition in a digital circuit occurs (a node change its state  $0\rightarrow 1$  or  $1\rightarrow 0$ ) some amount of electrical work is done; thus, some amount of electrical energy is spent. In order to obtain an analytical expression of dynamic energy, a network node can be modeled as a capacitor  $C_L$  which is charged by voltage source  $V_{DD}$  through a circuit with resistance R. In this case the total energy consumed to charge the capacitor  $C_L$  is  $E = C_L V_{DD}^2$ , where the half of the energy is dissipated on R, and half is saved in  $C_L$ ,  $E_C = E_R = \frac{C_L V_{DD}^2}{2}$ .

The total static energy consumption of a digital circuit is the result of leakage and static currents. Leakage current  $I_{leak}$  consists of drain leakage, junction leakage, and gate leakage current, while static current  $I_{DC}$  is bias which is needed by some circuits for their correct work. Static energy at a time moment t (t > 0) is given as follows:

$$E(t) = \int_0^t V_{DD}(I_{leak} + I_{DC})d\tau = V_{DD}(I_{DC} + I_{leak})t.$$

(3.2)

*Delay (D)*. In processor design, delay has two definitions, depending on the abstraction level (layers from Figure 1.4) that we consider. At the circuit level, it is propagation delay, and is defined as the difference between the time when the input to a logic gate becomes stable and valid and the time when the output of that logic gate is stable and valid. It usually refers to the time required for the output to reach 50% of its final output level when the input changes. However, at the architectural level, by delay we assume the execution time of an application kernel ( $t_e$ ). In this thesis, we assume the latter definition.

*Power (P)* is the rate at which work is performed or energy is converted, and its SI unit is the *watt* (*W*). Average power is given with  $P = \frac{\Delta E}{\Delta t}$ , in which  $\Delta E$  is amount of energy consumed in time period  $\Delta t$ . From architectural perspective, average is more important than instantaneous power. Like energy, power dissipation sources in digital circuits can be divided into two major classes: dynamic and static.

Dynamic power dissipation, similar to dynamic energy consumption, consists of switching ( $P_{switch}$ ), short-circuit ( $P_{sc}$ ) and glitching ( $P_{glitch}$ ) power:

$$P_{dyn} = P_{switch} + P_{sc} + P_{glitch}. (3.3)$$

From references [111, 38, 86] we have:

$$P_{switch} = \frac{1}{2} \alpha f C_L V_{DD}^2, \quad P_{sc} \propto \alpha f V_{DD}^3 / C_L, \text{ and } P_{glitch} \propto \alpha f V_{DD}^2.$$

(3.4)

Static power in CMOS digital circuits is a result of leakage and static currents (the same sources which cause static energy):

$$P_{stat} = V_{DD}(I_{DC} + I_{leak}). (3.5)$$

Further, P is typically structurally divided into power of adder's clock tree and of the rest of the adder:  $P = P_{ct} + P_{rest}$

Generally, in our research, we observe from the results that  $P_{stat}$  is typically two orders of magnitude less than  $P_{dyn}$ . The leakage is negligible due to the following reasons: (1) arithmetic' topologies produce high switching (high  $P_{dyn}$ ), (2) the technology that we use has low leakage, and (3) we optimize non-critical path logic for leakage using high- $V_{TH}$  cells. Therefore, the power of an arithmetic unit (P) is practically equal to its dynamic component ( $P \approx P_{dyn}$ ).

### 3.2.2 Derived Metrics

Energy-Delay Product (*EDP*) - While low power often used to be viewed as synonymous with lower performance that is no longer the case. In many cases, application runtime is of significant relevance even in energy- or power-constrained environments. With the dual goals of low energy and fast runtime in mind, energy-delay product (*EDP*) was proposed as a useful metric [46]. *EDP* offers equal "weight" to either energy or performance degradation. If either energy or delay increases, the *EDP* increases. Thus, lower *EDP* values are desirable.

Energy<sup>i</sup>-Delay<sup>j</sup> product ( $ED^iP^j$ ) - EDP of a design tells how close the design is to a perfect balance between performance and energy efficiency. Sometimes, in real designs, achieving that balance may not necessarily be of interest. Typically, one metric is assigned greater weight, for example, energy is minimized for a given maximum delay or delay is minimized for a given maximum energy. In the high-performance arena, where performance improvements matter more than energy savings we need a metric which has i < j, while in low-power design we need one

with i > j (i, j > 0). For example, a commonly used performance oriented metric is ED2P [71].

*Surface power density* ( $P_d$ ) - Another related metric which is defined as power per unit area:

$$P_d = \frac{P}{A'},\tag{3.6}$$

and its SI unit is  $\frac{W}{m^2}$ . This metric is the crucial one for thermal studies and cooling system selection and design, as it is related with the temperature of the given surface by *Stefan-Boltzmann law* [104].

# 3.3 Methodology

This section describes the methodology, framework, and flow parameters used to perform this extensive comparison of PnR and PAS estimation flows. By flow parameters, we assume design parameters and  $\alpha_I$  (explained in sections 3.3.2 and 3.3.4 respectively).

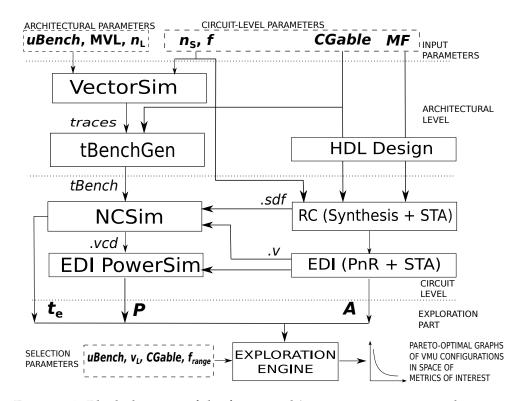

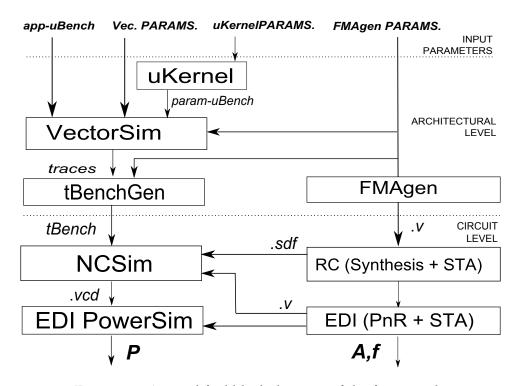

#### 3.3.1 Framework

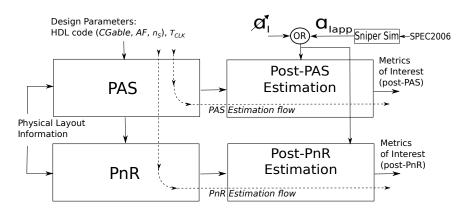

A simplified block diagram of the framework is depicted on Figure 3.1. As a PAS tool and post-PAS results estimator we use Cadence RTL compiler [32] in Physical Layout Estimation mode while for PnR and post-PnR estimations we use Cadence Encounter Digital Implementation System [31]. We developed several scripts for automation and interfacing between tools. PAS is the first common part of both PAS and PnR estimation flows. Each design point is defined by four parameters, adder family (AF),  $n_S$ , CGable and  $T_{CLK}$  (described in Section 3.3.2). We wrote all the hardware description language (HDL) code by hand for the adders of each valid combination of the AF,  $n_S$ , and CGable parameters. For each design point, we supply the HDL code of the adder together with a target clock cycle (the  $T_{CLK}$  parameter) to the PAS tool to produce adder's mapped netlists. We perform PAS for all combinations of our design parameters in an automated way. The PAS tool tries to meet timing constraints ( $T_{CLK}$ ) while prioritizing power over area

Figure 3.1: Block diagram of the framework used to perform the comparative analysis of PnR and PAS estimation flows in terms of area, timing and power (metrics of interest).

optimization. Once we have all the netlists produced using PAS, we perform post-PAS estimation of the metrics of interest (area, timing and power), and complete the PAS estimation flow. Both post-PAS and post-PnR  $\alpha_I$ -based power estimations are explained in Section 3.3.4. In order to complete the PnR estimation flow we further process our designs and perform PnR. The last stage of the PnR estimation flow is post-PnR estimation of the metrics of interest. Additionally, the most critical paths are verified with Cadence Spectre [97]. This step is not shown in Fig. 3.1 for the sake of simplicity.

All designs are implemented using the mentioned TSMC40LP library for *typical* operating conditions. Since practically all existing vector processors (and vector processors exploration is the final goal of the research presented in this chapter) are developed using standard cells [49], we selected this approach in our research. We chose effective current based model (ECSM)[18] as it delivers accuracy to within 2% of SPICE [19]. It is more accurate than conventional models like non-linear delay model (NLDM) which differ as much as 20%.

We perform PAS and PnR under the same conditions. PAS tool requires basic physical layout information in order to perform its physical layout aware synthesis. This is a subset of the complete set of physical layout parameters required by the PnR tool. For example, core density is a fundamental and basic layout parameter required by both tools. An initial core density of 70% is selected as a sensible balance between timing improvement and shrinking area for the wide set

of adder designs parameters that we use. We experimentally found that, in PnR stage in general, density below 70% sometimes provides negligible faster timing for a non-negligible area overhead while densities higher than 70% can spoil timings noticeably as the tool suffers from the lack of free space for optimizations and routing. Additionally, the initial densities below 70% sometimes even cause DRC errors and density violations. Regarding another important parameter used by both flows, number of routing layers, we use 4 since we experimentally found that using more would be a waste of resources as the additional layers do not improve the quality of results (QoR).

The optimization techniques that are applied in the PAS stage are: adding buffers, resizing gates, remapping logic, swapping pins, boundary optimizations (removing undriven or unloaded logic connected, propagating constants, collapsing equal pins, and rewiring of equivalent signals across hierarchy), and deleting buffers. However, we prevent restructuring optimization techniques that could change the adder structure, in order to maintain the original topology of each adder family. The optimization techniques done in the PAS stage are applied again in PnR since there is more optimization space in PnR than in PAS. Additionally, two more techniques are applied in PnR: moving instances and applying useful skew. PAS optimizations are run with high effort, while PnR ones with medium effort rather than high in order to keep PnR runtime affordable for a large number of design points. More details about the optimizations are available in the documentation of the aforementioned Cadence tools.

The necessary times for the complete PAS and PnR estimation flow for a single design are around 70 and 400 seconds in average, respectively. Thus, PAS is around 5.7 times faster than PnR estimation flow. The time needed to perform PnR is fairly reasonable for a small number of designs. However, the difference in execution time of the estimation flows becomes an important issue when we have experiments with a large number of design points. For example, in this design space exploration the number of design points is over 2000, which puts the difference of time needed between the flows completion into days. Moreover, for larger and faster designs this ratio increases as the PnR tool makes more effort on routing and optimizations. Therefore, we can expect the difference between these flows to be higher for large and more complex designs (e.g. accelerator or processor's core).

The framework is built for adders, but it can be easily accommodated for any other kind of arithmetic block. For example, in order to adapt the current framework to perform the same kind of comparative analysis for multipliers, practically the only change would be to supply the HDL code of the multipliers instead of current HDL code. To make it fully compatible with this framework, the new HDL code should, of course, incorporate the same design parameters (AF,  $n_S$ , and CGable).

## 3.3.2 Design Parameters

In this section we present the design parameters used in this comparative analysis of estimation flows:

- *CGable* indicates whether a VFU (in this case an adder) is implemented with or without support for clock-gating (*CG* or *noCG*, respectively). Clock-gating prevents useless switching activity in circuits and makes pipelining more effective. We assume the clock-gating decision is done in the issue stage. It is done at the stage level, i.e. each stage is activated with its *Enable* signals only when the data on its inputs is valid. We implement clock-gating in the HDL code and use latch-based clock-gating cells from TSMC40LP library. This clock-gating technique is called *IdleCG* and it is additionally explained and evaluated in Section 6.4.5. For simple structures like 32-bit integer adders and multipliers, there is no enough room for fruitful application of more advanced techniques like the ones presented in sections 6.4.1, 6.4.2, 6.4.3, and 6.4.4.

- *AF* is the adder family (algorithm). We choose five adder families: Brent-Kung (*bk*), Kogge-Stone (*ks*), carry-lookahead (*cla*), ripple-carry adder (*rca*), and conditional-sum adder (*cosa*), all implemented in HDL code. We choose *rca* as it is a basic algorithm and it is the simplest to implement (as for each bit it practically requires only one full adder cell), *cla* as a basic model of fast adders, and prefix (*bk* and *ks*) and *cosa* adders as they are fast and suitable for pipelining. All the adders that we use in this thesis are explained in Section 3.3.3. We obtain the results for static CMOS. However, as it is observed

in [80], the topology that is the most energy efficient in one logic style, is also the most energy-efficient in the other styles.

- $T_{CLK} = (1/f)$  is the clock period of the adder (and the system), while f is its clock frequency. We define 0.1-5.0 GHz as a frequency range in order to explore a vast design space.

- $n_S$  indicates the number of pipeline stages in the adder (pipeline depth), and it ranges from 1 to 8. We only increase  $n_S$  for a particular AF if it provides shorter  $T_{CLK}$  with PAS. In particular, we implement bk, ks, rca for 1-8, cosa for 1-7, and *cla* for 1-4 stages. The structures of all the observed adders except *cla* are regular, so pipelining these adders is done in a fairly obvious way. *cla* does not have a structure that allows such obvious way to pipeline it, so in this case we need to apply ad-hoc pipelining. Since the adders are pipelined and have a clocked input register (first pipeline stage) they can be easily incorporated into a datapath. The input register of an *n-stage* adder consists of 2x32 DFlipFlops (DFF) for the input operands and one DFF for the carry-in bit, and in case of CG we have n additional DFFs for the Enable signal. Additionally, each *n-stage* adder has *n-1* pipeline clocked registers (consisting of DFFs) which are used to save intermediate results. The size of each register depends on the AF structure and the place inside the adder where the register is inserted (i.e. on the way the adder is pipelined). We include in this study high numbers of pipeline stages because we need high frequencies for vast design space exploration, and because we want to study the impact of deep pipelining.

## 3.3.3 Adder Families

This section presents the adder families used in this chapter and Chapters 4 and 6. Even more detailed explanations of each AF are available in [14, 33].

## Ripple-Carry Adder (rca)

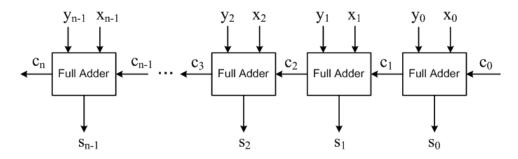

The rca is O(n) for both time and area, where n is the width of the operands. In the worst case, a carry can propagate from the least significant bit position to the most

Figure 3.2: *n*-bit ripple carry adder (*rca*).

Figure 3.3: Full adder (FA) and half adder (HA).

significant bit position. A block diagram of the RCA is shown in Figure 3.2.

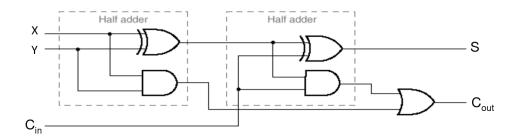

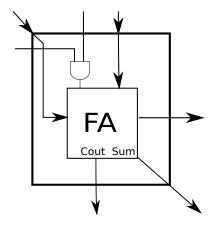

The basic unit is full adder (FA), also referred to as a (3,2) counter, computes a sum bit and a carry bit,  $s_i = x_i \oplus y_i \oplus cin_i$ ,  $c_{i+1} = x_iy_i + x_ic_i + y_ic_i$ . That is, it adds two operand bits with the incoming carry bit to produce a sum bit and an outgoing carry bit. Its block diagram is shown on Figure 3.3

When there is no incoming carry bit, i.e. when it is assumed to be '0', half adder (HA) is used:  $s_i = x_i \oplus y_i$ ,  $c_{i+1} = x_i y_i$ . It is also referred to as (2,2) counter and its block diagram is shown on Figure 3.3

The delay ( $T_{CLK}$  assuming  $n_S = 1$ ) of rca, expressed in logic levels, is  $T_{rca} = 2n$  (O(n)), while area, expressed in number of simple gates, is  $A_{rca} = 7n + 2$  (O(n)).

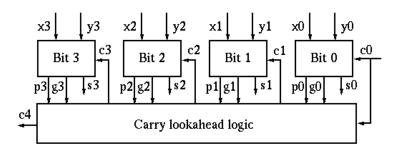

## Carry-Lookahead Adder (cla)

The bottleneck for ripple carry addition is the calculation of  $c_i$ , which takes linear time proportional to n. To improve it, we define Generate ( $g_i = x_i y_i$ ) and Propagate ( $p_i = x_i + y_i$ ) functions. Both  $g_i$  and  $p_i$  can be generated for all n bits in constant

Figure 3.4: 4-bit Carry-Lookahead Adder.

time (1 gate delay).  $g_i$  and  $p_i$  are used for carry generation:

$$c_{i+1} = x_i y_i + x_i c_i + y_i c_i = x_i y_i + (x_i + y_i) c_i = g_i + p_i c_i$$

These equations allow us to calculate all the carries in parallel from the operands. For example, the carries for a 4-bit *cla* adder (Figure 3.4) are given as:

$$c_0 = c_0,$$

$c_1 = g_0 + c_0 p_0,$

$c_2 = g_1 + g_0 p_1 + c_0 p_0 p_1,$

$c_3 = g_2 + g_1 p_2 + g_0 p_1 p_2 + c_0 p_0 p_1 p_2,$

$c_4 = g_3 + g_2 p_3 + g_1 p_2 p_3 + g_0 p_1 p_2 p_3 + c_0 p_0 p_1 p_2 p_3,$

The delay is  $T_{cla} = 4 \log n$  ( $O(\log n)$ ), while area is  $A_{cla} = 14n - 20$  (O(n)).

## Conditional Sum Adder (cosa)

The basic idea in the cosa is to generate two sets of outputs for a group of k operand bits. One set is valid if input carry is one, while another is valid if it is zero. Depending on the value of incoming carry bit, only one of the sets is selected. Both of the sets have k sum bits and an outgoing carry bit. An example of cosa for 4-bit operands is shown on Figure 3.5

The delay is  $T_{cosa} = 2 \log n + 2$  ( $O(\log n)$ ), while area is  $A_{cosa} = 3n \log n + 7n - 2 \log n - 7$  (O(n)).

Figure 3.5: 4-bit Conditional Sum Adder (cosa).

#### **Parallel-Prefix Adders**

Parallel-prefix networks are widely used in high performance adders. They use direct parallel-prefix scheme for fast carry computation. They all have the initial generate and propagate signal generation and the final sum bit generation and differ only in the arrangement of the intermediate carry generation levels.

Parallel-prefix adders are constructed out of fundamental dot operators denoted by • as follows:

$$(g'', p'') \bullet (g', p') = (g'' + g'p'', p'p''),$$

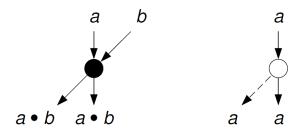

where p'' and p' indicate the propagations while g'' and g' indicate the generations. A parallel-prefix adder can be represented as a parallel-prefix graph consisting of dot operator nodes. In the graphs, the black nodes  $\bullet$  depict nodes performing the binary associative dot operation  $\bullet$  on its two inputs, while the white nodes  $\circ$  represent feed-through nodes with no logic i.e. cells are empty or contain buffers (Figure 3.6).

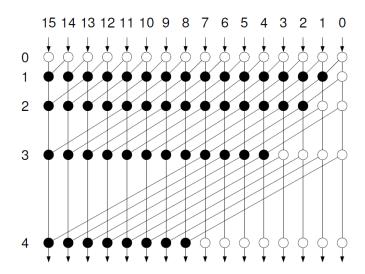

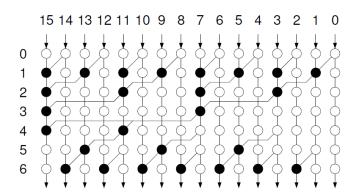

In this research, we focus on bk and ks parallel-prefix algorithms. They all have delay and area at the same order of magnitude: the delay is  $O(\log n)$ , while area is  $O(n \log n)$ .

Figure 3.6: Black and white nodes.

Figure 3.7: 16-bit Kogge-Stone (ks) Adder.

**Kogge-Stone** (*ks*) On Figure 3.7 is shown the parallel-prefix graph of a *ks* adder [64]. This adder structure is characterized by minimum logic depth, and full binary tree with minimum fan-out (maximum fan-out is 2), resulting in a fast adder (due to smaller capacitive loads) but with a large area, i.e. increased number of black nodes and interconnections. The delay is  $T_{ks} = 4 \log n + 4$ , while area is  $A_{ks} = 3n \log n + n + 8$ .

**Brent-Kung** (*bk*) On Figure 3.8 is depicted the parallel-prefix graph of a *bk* adder [17]. The tree has a low number of dot operators, while at the same time there are few cascaded dot operators. This adder is characterized by high logic depth and small area. The delay is  $T_{bk} = 4 \log n$ , while area is  $A_{bk} = 14n - 3 \log n - 1$ .

Figure 3.8: 16-bit Brent-Kung (bk) Adder.

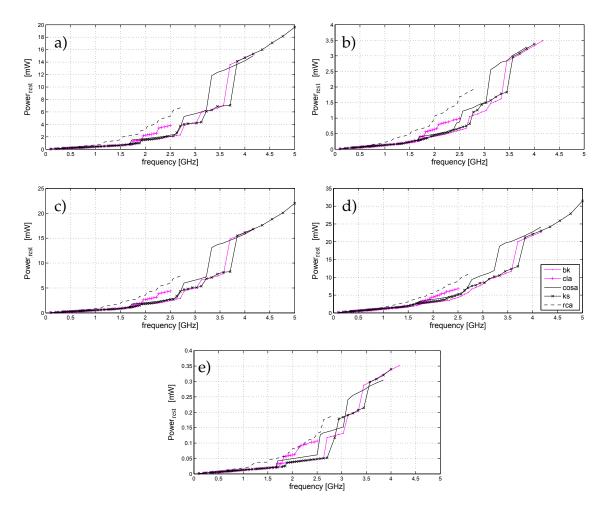

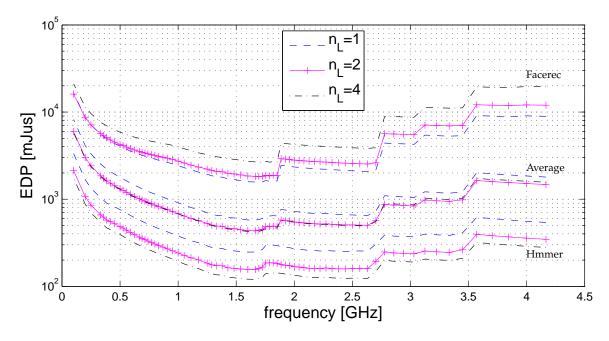

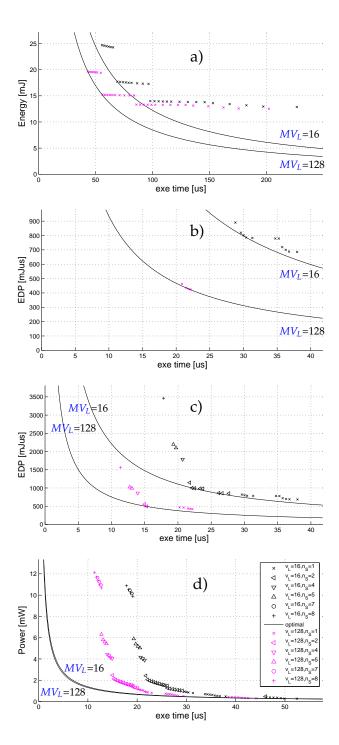

### 3.3.4 Power Estimation