MASTER THESIS

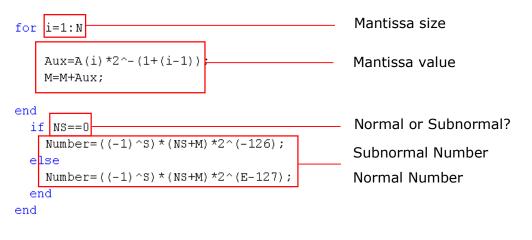

## DESIGN OF SINGLE PRECISION FLOAT ADDER (32-BIT NUMBERS) ACCORDING TO IEEE 754 STANDARD USING VHDL

Arturo Barrabés Castillo

Bratislava, April 25<sup>th</sup> 2012

Supervisors: Dr. Roman Zálusky Prof. Viera Stopjaková Fakulta Elecktrotechniky a Informatiky Slovenská Technická Univerzita v Bratislave

## INDEX

| Index     |                                     | 3    |

|-----------|-------------------------------------|------|

| Resum     |                                     | 5    |

| Zhrnutie  |                                     | 5    |

| Abstract  |                                     | 5    |

| Chapter 1 | Introduction                        | 7    |

| 1.1. Fl   | oating Point Numbers                | 7    |

| 1.2. Th   | e Standard IEEE 754                 | 8    |

| 1.2.1.    | Overview                            | 8    |

| 1.2.2.    | Binary Interchange Format Encodings | 9    |

| 1.2.3.    | Precision and Rounding              | 10   |

| Chapter 2 | Code Development                    | . 13 |

| 2.1. 32   | 2-bits Floating Point Adder Design  | 13   |

| 2.1.1.    | Addition/Subtraction Steps          | 13   |

| 2.1.2.    | Block Diagram                       | 15   |

| 2.2. Bl   | ocks Design                         | 17   |

| 2.2.1.    | Pre-Adder Design                    | 17   |

| 2.2.2.    | Adder Design                        | 17   |

| 2.2.3.    | Standardizing Design                | 19   |

| Chapter 3 | Pre-Adder                           | . 21 |

| 3.1. Sp   | pecial Cases                        | 21   |

| 3.1.1.    | n_case Block                        | 21   |

| 3.2. St   | Ibnormal Numbers                    | 25   |

| 3.2.1.    | n_subn Block                        | 25   |

| 3.3. M    | xed Numbers                         | 27   |

| 3.3.1.    | comp Block                          | 27   |

| 3.3.2.    | zero Block                          | 30   |

| 3.3.3.    | shift_left/shift Block              | 32   |

| 3.3.4.    | norm Block                          | 35   |

| 3.4. No   | ormal Numbers                       | 38   |

| 3.4.1.    | comp_exp Block                      | 38   |

| 3.4.2.    | shift Block                         | 41   |

| 3.4.3.    | n_normal Block                      | 41   |

| 3.5.     | Pre-Adder                         |

|----------|-----------------------------------|

| 3.5.1.   | selector Block44                  |

| 3.5.2.   | MUX/DEMUX Blocks48                |

| 3.5.3.   | preadder Block50                  |

| Chapter  | 4: Adder 55                       |

| 4.1.     | Adder55                           |

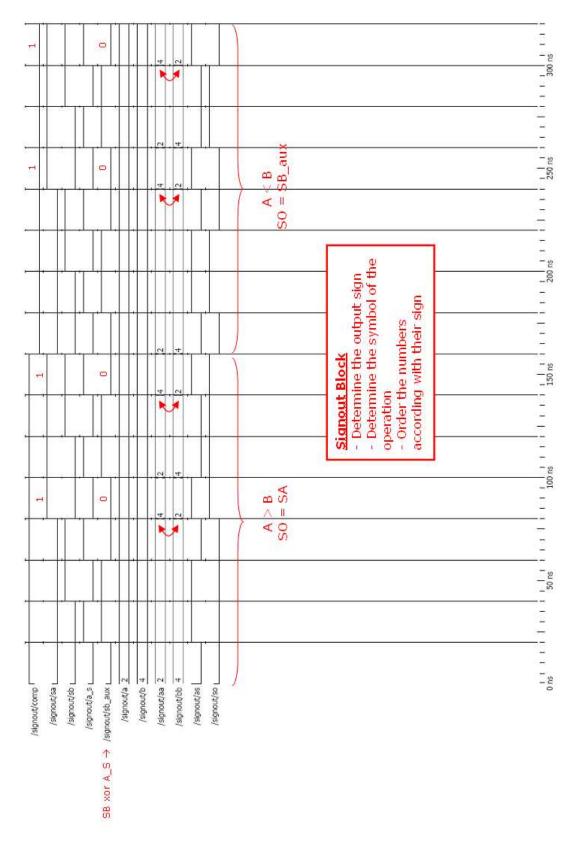

| 4.1.1.   | Signout Block55                   |

| 4.1.2.   | Adder Block                       |

| 4.1.3.   | Block_Adder Block62               |

| 4.2.     | Standardizing Block65             |

| 4.2.1.   | round Block65                     |

| 4.2.2.   | shift_left/zero Block65           |

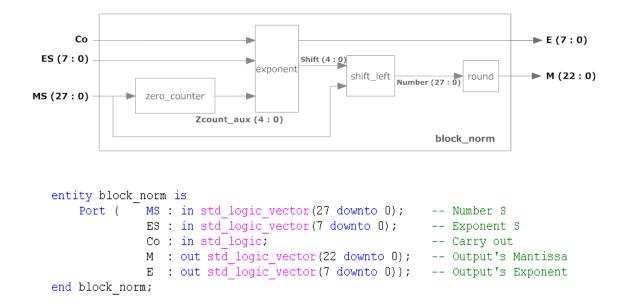

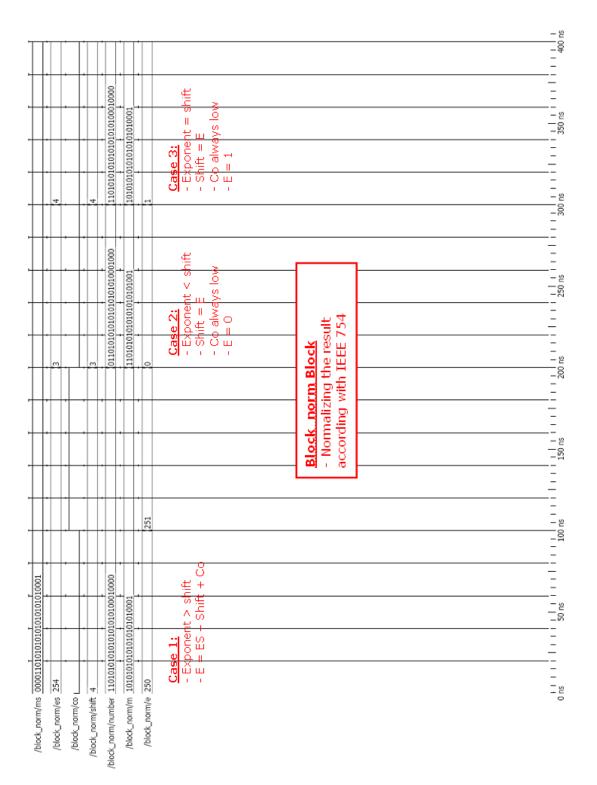

| 4.2.3.   | block_norm Block67                |

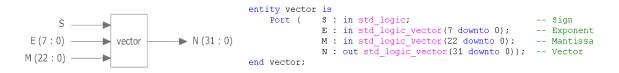

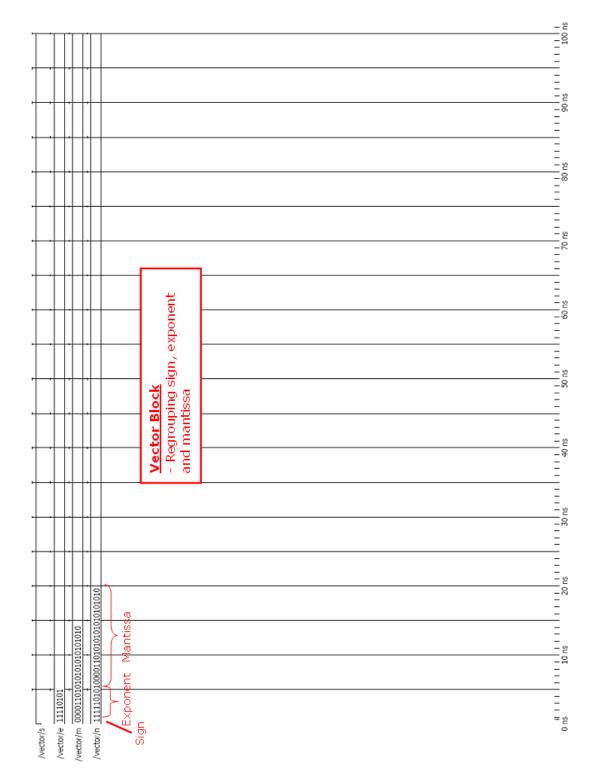

| 4.2.4.   | vector Block70                    |

| Chapter  | 5: 32-Bits Floating Point Adder73 |

| 5.1.     | Floating Point Adder74            |

| 5.1.1.   | Mux_fpadder Block74               |

| 5.1.2.   | fpadder Block74                   |

| 5.2.     | Simulations77                     |

| 5.2.1.   | Special Cases77                   |

| 5.2.2.   | Normal Numbers80                  |

| 5.2.3.   | Subnormal Numbers81               |

| 5.2.4.   | Mixed Numbers82                   |

| Chapter  | 6: Results                        |

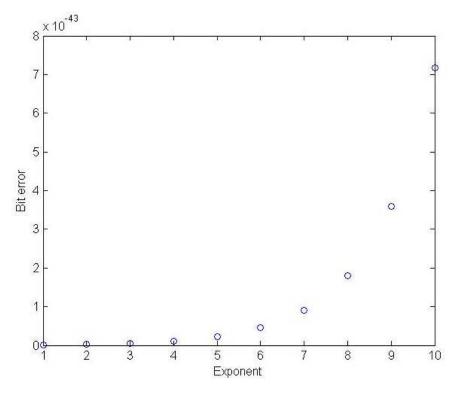

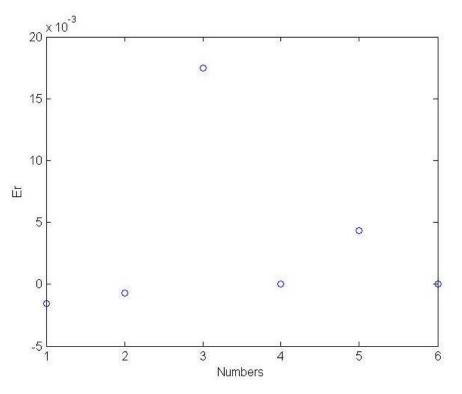

| 6.1.     | Errors83                          |

| 6.1.1.   | Gap between Numbers83             |

| 6.1.2.   | Rounding or Truncation85          |

| 6.1.3.   | Floating Point Addition86         |

| 6.2.     | Results analysis86                |

| 6.2.1.   | Subnormal Numbers86               |

| 6.2.2.   | Mixed Numbers88                   |

| 6.2.3.   | Normal Numbers89                  |

| 6.3.     | Conclusions91                     |

| Chapter  | 7: Bibliography                   |

| Annex: \ | VHDL Code                         |

### RESUM

La aritmètica de punt flotant és, amb diferència, el mètode més utilitzat d'aproximació a la aritmètica amb nombres reals per realitzar càlculs numèrics per ordinador.

Durant molt temps cada màquina presentava una aritmètica diferent: bases, mida dels significants i exponents, formats, etc. Cada fabricant implementava el seu propi model ,fet que dificultava la portabilitat entre diferents equips, fins que va aparèixer la norma IEEE 754 que definia un estàndard únic per a tothom.

L'objectiu d'aquest projecte és, a partir del estàndard IEEE 754, implementar un sumador/restador binari de punt flotant de 32 bits emprant el llenguatge de programació hardware VHDL.

### ZHRNUTIE

Práca s číslami s pohyblivou desatinnou čiarkou je najpoužívanejší spôsob pre vykonávanie aritmetických výpočtov s reálnymi číslami na moderných počítačoch. Donedávna, každý počítač využíval rôzne typy formátov: báza, znamienko, veľkosť exponentu, atď. Každá firma implementovala svoj vlastný formát a zabraňovala jeho prenosu na iné platformy pokiaľ sa nevymedzil jednotný štandard IEEE 754. Cieľom tejto práce je implementovanie 32-bitovej sčítačky/odčítačky pracujúcej s číslami s pohyblivou desatinnou čiarkou podľa štandardu IEEE 754 a to pomocou jazyka na opis hardvéru VHDL.

### ABSTRACT

Floating Point arithmetic is by far the most used way of approximating real number arithmetic for performing numerical calculations on modern computers.

Each computer had a different arithmetic for long time: bases, significant and exponents' sizes, formats, etc. Each company implemented its own model and it hindered the portability between different equipments until IEEE 754 standard appeared defining a single and universal standard.

The aim of this project is implementing a 32 bit binary floating point adder/subtractor according with the IEEE 754 standard and using the hardware programming language VHDL.

# CHAPTER 1: INTRODUCTION

Many fields of science, engineering and finance require manipulating real numbers efficiently. Since the first computers appeared, many different ways of approximating real numbers on it have been introduced.

One of them, the floating point arithmetic, is clearly the most efficient way of representing real numbers in computers. Representing an infinite, continuous set (real numbers) with a finite set (machine numbers) is not an easy task: some compromises must be found between speed, accuracy, ease of use and implementation and memory cost.

Floating Point Arithmetic represent a very good compromise for most numerical applications.

## 1.1. Floating Point Numbers

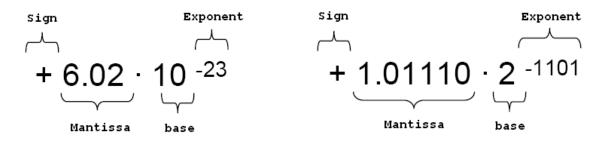

The floating point numbers representation is based on the scientific notation: the decimal point is not set in a fixed position in the bit sequence, but its position is indicated as a base power.

All the floating point numbers are composed by three components:

- *Sign:* it indicates the sign of the number (0 positive and 1 negative)

- *Mantissa*: it sets the value of the number

- *Exponent*: it contains the value of the base power (biased)

- *Base*: the base (or radix) is implied and it is common to all the numbers (2 for binary numbers)

The free using of this format caused either designed their own floating point system. For example, Konrad Zuse did the first modern implementation of a floating point arithmetic in a computer he had built (the Z3) using a radix-2 number system with 14-bit significant, 7-bit exponents and 1-bit sign. On the other hand the PDP-10 or the Burroughs 570 used a radix-8 and the IBM 360 had radix-16 floating point arithmetic.

This led to the need for a standard which would make a clear and concise format to be used by all the developers.

## 1.2. The Standard IEEE 754

The first question that comes to mind is "*What's IEEE?*". The *Institute of Electrical and Electronics Engineers* (IEEE) is a non-profit professional association dedicated to advancing technological innovations and excellence.

It was founded in 1884 as the AIEE (*American Institute of Electrical Engineers*). The IEEE was formed in 1963 when AIEE merged with IRE (*Institute of Radio Engineers*).

One of its many functions is leading standards development organization for the development of industrial standards in a broad range of disciplines as telecommunications, consumer electronics or nanotechnology.

IEEE 754 is one of these standards.

#### 1.2.1. Overview

Standard IEEE 754 specifies formats and methods in order to operate with floating point arithmetic.

These methods for computational with floating point numbers will yield the same result regardless the processing is done in hardware, software or a combination for the two or the implementation.

The standard specifies:

- Formats for binary and decimal floating point data for computation and data interchange

- Different operations as addition, subtraction, multiplication and other operations

- Conversion between integer-floating point formats and the other way around

- Different properties to be satisfied when rounding numbers during arithmetic and conversions

- Floating point exceptions and their handling (NaN,  $\pm \infty$  or zero)

IEEE 754 specifies four different formats to representing the floating point values:

- Simple Precision (32 bits)

- Double precision (64 bits)

- Simple Extended Precision ( $\geq$ 43 bits but not too used)

- Double Extended Precision ( $\geq$ 79 bits, usually represented by 80)

1.2.2. Binary Interchange Format Encodings

Representations of floating point data in the binary interchange formats are encoded in k bits in the following three fields ordered as shown in Figure 1:

|   | 1 bit  | MSB            | w bits | LSB   | MSB | t = p - 1 bits               | LSB |

|---|--------|----------------|--------|-------|-----|------------------------------|-----|

| ſ | S      |                | Е      |       |     | Т                            |     |

|   | (sign) | (biased        | d expo | nent) |     | (trailing significand field) |     |

|   |        | E <sub>0</sub> |        | E1    | d1  |                              | d_1 |

Figure 1. Floating Point format

If a Simple Precision format is used the bits will be divided in that way:

- The first bit (31<sup>st</sup> bit) is set the sign (S) of the number (0 positive and 1 negative)

- Next *w* bits (from  $30^{\text{th}}$  to  $23^{\text{rd}}$  bit) represents the exponent (*E*)

- The rest of the string, t, (from  $22^{nd}$  to 0) is reserved to save the mantissa

The range of the enconding biased exponent is divided in three sections:

- Every integer between 1 and  $2^{w}-2$  (being  $w=8 \rightarrow 254_{(10)}$ ) in order to encode the normal numbers

- The value 0 which encodes subnormal numbers and the zero value

- The reserved value 2<sup>w</sup>-1 (being  $w=8 \rightarrow 255_{(10)}$ ) to encode some special cases as NaN or  $\pm \infty$

The exponent value has a bias of 127. It means the exponent value will be between -126  $(0000000_{(2)})$  and +127  $(1111110_{(2)})$  being zero at the value  $(01111111_{(2)})$ .

Exponent and mantissa values determine the different number r cases that it can be had.

- If  $E = 2^w 1$  and  $T \neq 0$ , then *r* is NaN regardless of *S*

- If  $E = 2^w 1$  and T = 0, then *r* is ±infinity according with the sign bit *S*

- If  $1 \le E \le 2^w 2$ , then *r* is a normal number

- If E = 0 and  $T \neq 0$ , then *r* is a subnormal number

- If E = 0 and T = 0, then *r* is ±zero according with *S*

The mantissa value is 23 bits long but it contains an implicit bit depending on the type of data (1 for normal numbers and 0 for subnormal).

A number can be represented by different ways. As an example, the number  $0.11 \cdot 2^5$  can be described as  $110 \cdot 2^2$  or  $0.011 \cdot 2^6$ .

It is desirable to require unique representations. In order to reach this goal the finite non-zero floating point numbers may be normalized by choosing the representation for which the exponent is minimum.

To cope with this problem the standard provides a solution. The numbers will be standardized in two ways:

- Subnormal numbers will start with a zero an it has a form like  $\pm 0.XX \cdot 2^{\circ}$

- Normal numbers MSB will be high  $(\pm 1.XX \cdot 2^E)$  where 0 < E < 255

Both normal and subnormal numbers MSB will be implied but taken into account in order to get the proper value in decimal.

To calculate the value of the binary bit sequence in decimal this formula will be used:

$$M = \sum_{k=0}^{22} m_{22-k} \cdot 2^{-(1+k)}$$

(1)

Finally the different format parameters for simple and double precision are shown in *table 1*:

| Parameter                                   | binary32   | binary64 |

|---------------------------------------------|------------|----------|

| k, storage width in bits                    | 32         | 64       |

| p, precision in bits                        | 24         | 53       |

| emax, maximum exponent e                    | 127        | 1023     |

| Encoding p                                  | parameters |          |

| bias, E–e                                   | 127        | 1023     |

| sign bit                                    | 1          | 1        |

| w, exponent field width in bits             | 8          | 11       |

| t, trailing significand field width in bits | 23         | 52       |

| k, storage width in bits                    | 32         | 64       |

Table 1. Binary interchange format parameters

#### 1.2.3.

#### Precision and Rounding

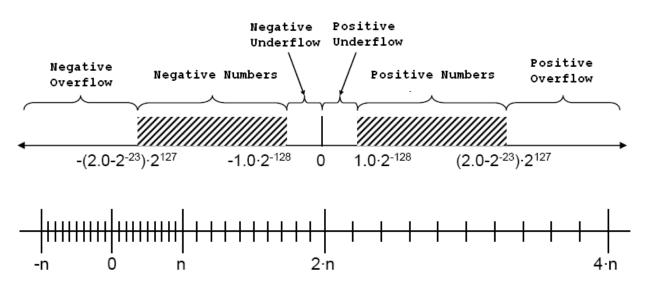

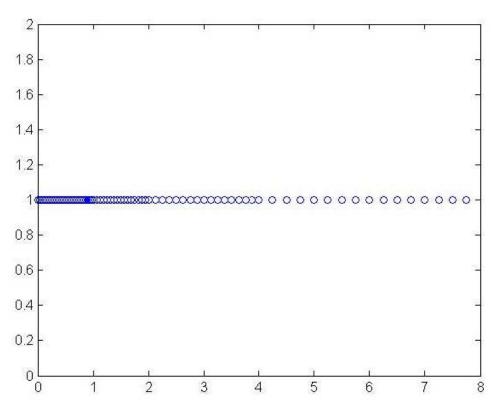

The number of values which can be represented by floating point arithmetic is finite because it has a finite number of bits.

Figure 2. Floating Point values range

As it can be seen in the *figure 2*, the standardized numbers range is described as the values between the higher exponent and mantissa value and the lower ones. The subnormal numbers are between zero and the lowest number (positive or negative) which could be represented by normal numbers. However, these ranges are discontinuous because between two numbers there are also infinite real ones. The quantities of numbers, which can be represented, are the same than in fixed point but at the expense of increasing the distance between numbers a higher range is achieved.

The standard IEEE 754 requires that the operation result must be the same which would obtain if a calculation with absolute precision and rounded had been done.

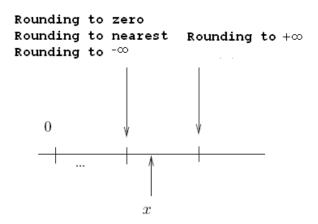

Four types of rounding are described by the standard:

- Rounding to the nearest (to even number in case of tie) is the floating point number that is the closest to *x*.

- Rounding to  $+\infty$  is the smallest floating point number (possibly  $+\infty$ ) greater than or equal to x.

- Rounding to  $-\infty$  is the largest floating point number (possibly  $-\infty$ ) less than or equal to x.

- Rounding to zero is the closest floating point number to x that is no greater in magnitude than x (it is equal to rounding to  $-\infty$  if  $x \ge 0$  and to  $+\infty$  if  $x \le 0$

Figure 3. Rounding Modes

The finite number of representing values and the rounding cause the appearance of errors in the result. This topic should be discussed when the results will be analyzed.

# CHAPTER 2: CODE DEVELOPMENT

Once the standard IEEE 754 has been explained it is time to start with the implementation of the code. First of all thinking about the different steps we should do to perform the operation required is compulsory. It is because of this that this section will talk about the procedure in addition/subtraction operations and a first look at the code design in block diagram way.

A complete description will be done first and the subblocks will be explained immediately afterwards at successive subsections.

## 2.1. 32-bits Floating Point Adder Design

The main goal of this project is the implementation of a 32-bit Floating Point Adder with VHDL code. The format and the main features of the standard have been described before but nothing about the steps to achieve the target has been said.

The first logical step is trying to specify what operations should be done to obtain a proper addition or subtraction. Once the idea will be clear the block diagram of the entire code will be designed.

#### 2.1.1. Addition/Subtraction Steps

Following the established plan, the way to do the operations (addition/subtraction) will be set.

This point will be also used to try to explain why these steps are necessary in order to make clearer and easier the explanation of the code in the next section.

The different steps are as follows:

1. Extracting signs, exponents and mantissas of both A and B numbers. As it has been said, the numbers format is as follows:

| _1 bit | 8 bits   | 23 bits  |

|--------|----------|----------|

| Sign   | Exponent | Mantissa |

Figure 4. Floating Point Number format

Then the first step is finding these values.

- 2. Treating the special cases:

- Operations with A or B equal to zero

- Operations with  $\pm \infty$

- Operations with NaN

- 3. Finding out what type of numbers are given:

- Normal

- Subnormal

- Mixed

- 4. Shifting the lower exponent number mantissa to the right [Exp1-Exp2] bits. Setting the output exponent as the highest exponent.

```

A's Exponent \rightarrow 3B's Exponent \rightarrow -1Difference (A-B) \rightarrow 4

```

Number B:

5. Working with the operation symbol and both signs to calculate the output sign and determine the operation to do.

| A's Sign | Symbol | B′s Sign | Operation |

|----------|--------|----------|-----------|

| +        | +      | +        | +         |

| +        | +      | -        | -         |

| +        | -      | +        | -         |

| +        | -      | -        | +         |

| -        | +      | +        | -         |

| -        | +      | -        | +         |

| -        | -      | +        | +         |

| -        | -      | -        | -         |

| Table 1. | Sign | Operation |

|----------|------|-----------|

|----------|------|-----------|

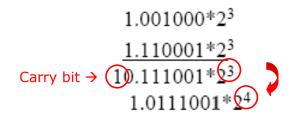

6. Addition/Subtraction of the numbers and detection of mantissa overflow (carry bit)

#### Figure 5. Example

7. Standardizing mantissa shifting it to the left up the first one will be at the first position and updating the value of the exponent according with the carry bit and the shifting over the mantissa.

$0.1010101 \cdot 2^3 \rightarrow 1.010101 \cdot 2^2$

8. Detecting exponent overflow or underflow (result NaN or  $\pm \infty$ )

This is the way forward to proper operation. Obviously there are some parts which have to be discussed because there will be more aspects to be taken into account but this will happen in next sections where the code will be explained.

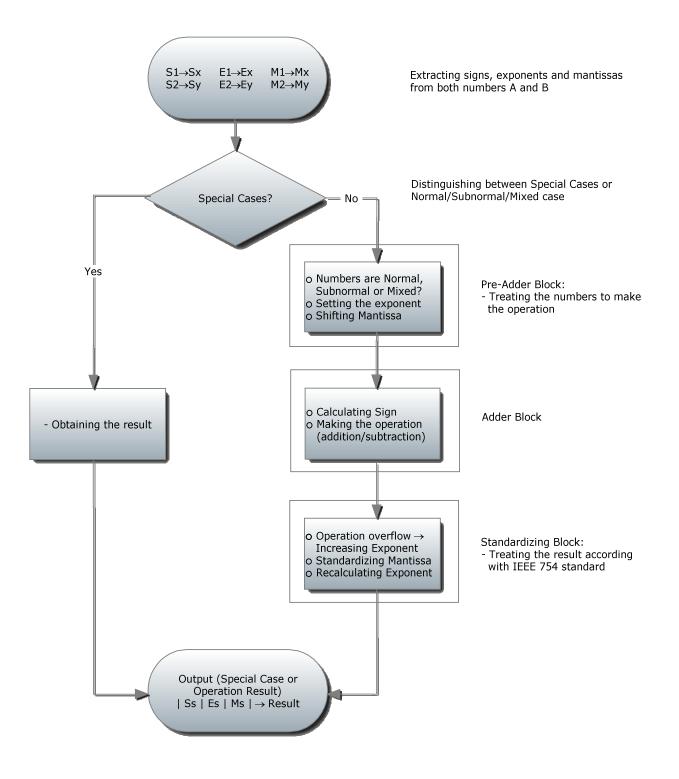

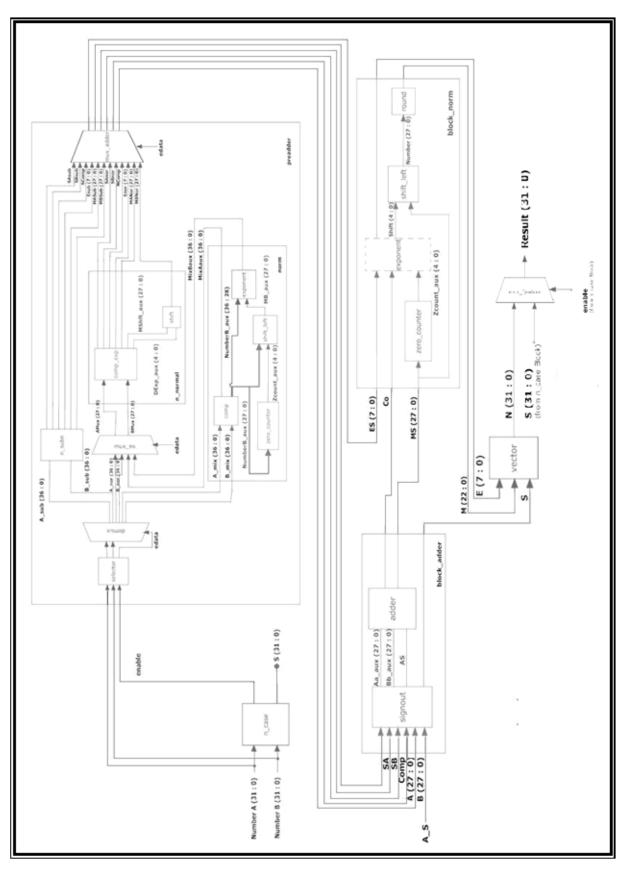

#### 2.1.2. Block Diagram

The main idea has been described before. Once the different steps to follow have been explained it is time to start to think in the code implementation.

In this subsection a first block diagram –as a draft- will be made. It still does not go into the most difficult points because in the next section, once a division of the project in three parts will be done, a complete description of each step will be performed.

These three parts are as follows:

- Pre-Adder Block

- Adder Block

- Standardizing Block

They make reference to the three main processes of the project. First the numbers should be treated (*pre-adder*) in order to perform the operation properly (*adder*) and finally, standardizing the result according with the standard IEEE 754 (*standardizing*).

In *figure 6*, a first approximation of the design has been done:

Figure 6. Block Diagram Code

## 2.2. Blocks Design

In this section the main blocks described in the previous block diagram will be explained.

The diagram has two branches:

- The special cases one is quiet simple because only the combination of the different exceptions are taken into account. This will be explained in the next chapter over the code directly

- The second one is more interesting. It includes the main operation of the adder. The different operations that should be done are divided in three big blocks: pre-adder, adder and normalizing block.

During the next subsections a first description of each block will be done. A block diagram will be designed to support the explanation and facilitate the comprehension. Moreover it will be used to design the different blocks in VHDL which form the 32-bit Floating Point Adder.

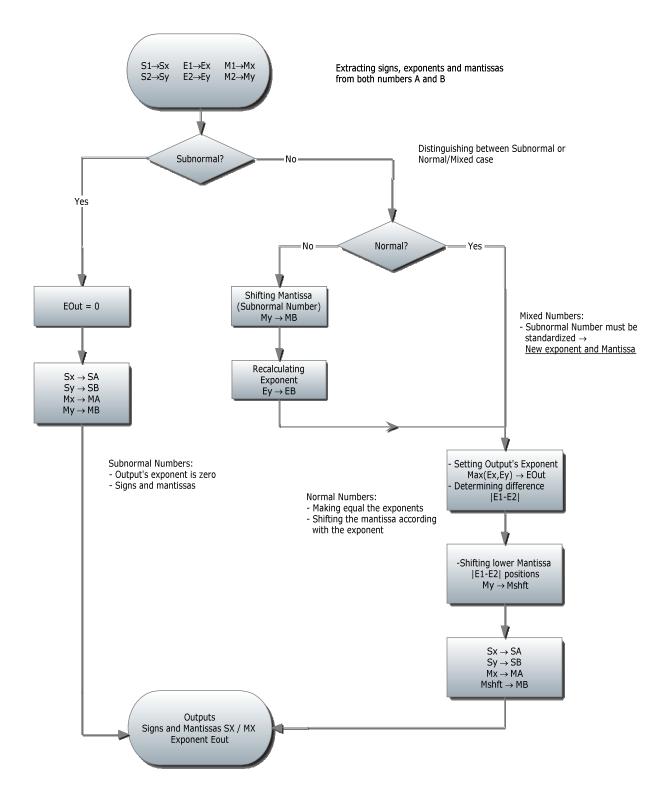

2.2.1. Pre-Adder Design

The first subblock is the Pre-Adder. The goals are:

- 1. Distinguishing between normal, subnormal or mixed (normal-subnormal combination) numbers.

- 2. Treating the numbers in order to be added (or subtracted) in the adder block.

- Setting the Output's exponent

- Shifting the mantissa

- Standardizing the subnormal number in mixed numbers case to be treated as a normal case

The block diagram which display this behaviour is shown (*figure 7*) in the next page.

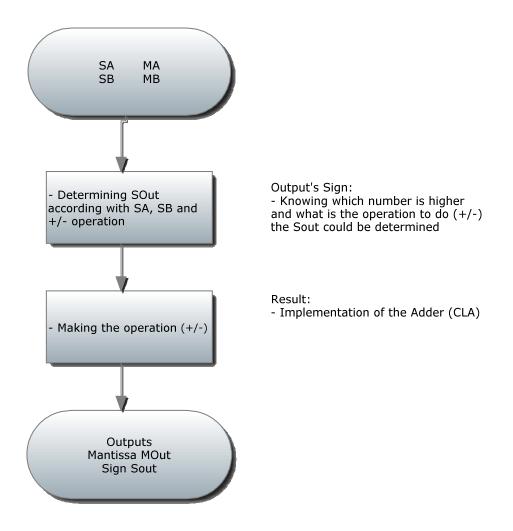

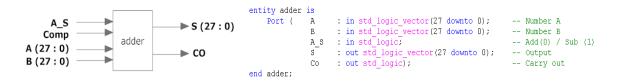

#### 2.2.2. Adder Design

Adder is the easiest part of the blocks. This block only implements the operation (addition or subtraction). It can be said the adder block is the ALU (*Arithmetic Logic Unit*) of the project because it is in charge of the arithmetic operations.

Two functions are implemented in this part of the code:

- 1. Obtaining the output's sign

- 2. Implementing the desired operation

In this block two related problems should be taken into account. Firstly, the calculation symbol (+ or -) depends on itself and the A and B's signs. Secondly, positive or negative numbers addition gives the same result. The problem will appear when the signs are different. In these cases the positive number will be kept in the first operand and the negative one in the second operand. All these problems will be explained in detail in next sections.

As it is normal the easiest block has the easiest block diagram (*figure 8*).

Figure 7. Pre-Adder Block Diagram

Figure 8. Adder Block Diagram

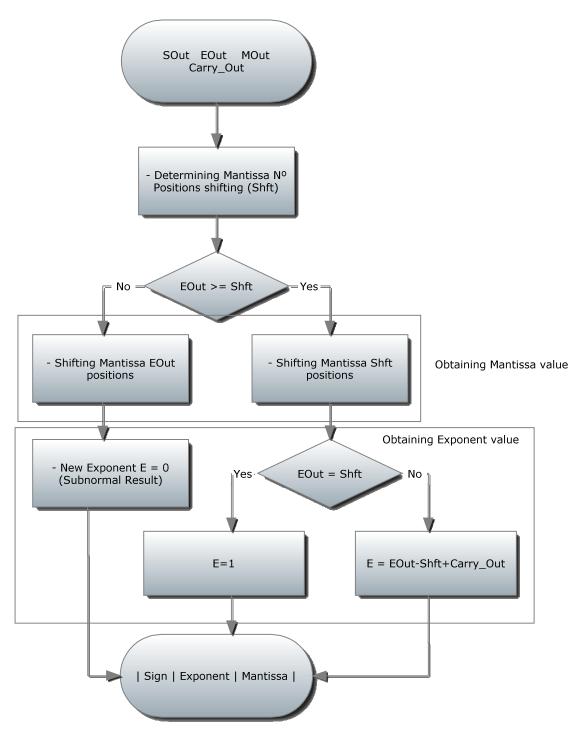

2.2.3.

#### Standardizing Design

Finally the Standardizing Block takes the result of the addition/subtraction and gives it an IEEE 754 format.

The procedure is as follows:

- 1. Shifting the mantissa to standardize the result

- 2. Calculating the new exponent according with the addition/subtraction overflow (carry out bit) and the displacement of the mantissa.

The exponent value must be controlled when these steps are going to be made because it could be the number of positions the mantissa must be shifted are higher than the exponent value. In this case the result becomes subnormal. Another exception is when exponent and number of displacements are equal: mantissa will be shifted and exponent will be one. As the previous subsections a block diagram with this description has been made. It can be seen in the *figure 8* where the different steps to standardize the value are shown.

Figure 9. Standardizing Block Diagram

## CHAPTER 3: PRE-ADDER

The first block is the Pre-adder. It is in the charge of distinguishing the type of numbers which are introduced as an input.

Four different cases are possible:

- 1. One of the different combinations which have been explained and labeled as special cases: NaN-Infinity, Infinity-Normal, Zero-Subnormal, etc.

- 2. A two subnormal numbers introduction.

- 3. A mixed option between normal and subnormal numbers.

- 4. A two normal numbers introduction

All this cases must be treated separately because of the process to achieve a successful operation must be different.

## 3.1. Special Cases

The adder is not always necessary to operate the numbers: there are some special cases which can be solved without it.

As it has been said, in addition to normal and subnormal numbers, infinity, NaN and zero are represented in IEEE 754 standard. Some possible combinations have a direct result, for example, if a zero and a normal number are introduced the output will be the normal number directly. Time and resources are saved implementing this block. The  $n_{case}$  block has been designed to run this behaviour.

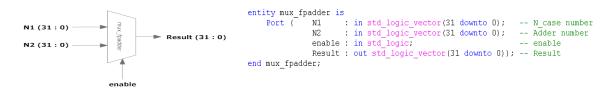

#### 3.1.1. n\_case Block

Both number A and number B are introduced as inputs. Vector S is one of the outputs and it contains the result when there is a special case, otherwise

undefined. Finally, *enable* signal enables or disables the *adder* block if it is needed or not.

|                     |            | entity n case          | is                                                        |

|---------------------|------------|------------------------|-----------------------------------------------------------|

| Number A (31:0)     | ▶ S (31:0) | Port (                 | NumberA : in std_logic_vector(31 downto 0); Number A      |

| . , ,               |            |                        | NumberB : in std_logic_vector(31 downto 0); Number B      |

| n_cas               |            |                        | enable : out std_logic; Enable Adder                      |

| Number B (31:0) — 🕨 | enable     |                        | <pre>S : out std_logic_vector(31 downto 0)); Output</pre> |

|                     |            | <pre>end n_case;</pre> |                                                           |

Firstly the possible number values are coded (zero, infinity, NaN, normal and subnormal numbers) in two signals *outA* and *outB* according to the mantissa and exponent value as it can be seen in table 2.

| outA | "001"<br>"011"<br>"100" | when EA = X"00"<br>when (EA > X"00"<br>when EA = X"FF"<br>when EA = X"FF" | <pre>and MA = 0 else<br/>and MA &gt; 0 else<br/>" and EA &lt; X"FF")<br/>and MA = 0 else<br/>and MA &gt; 0 else</pre> | and MA > 0 else   | Zero<br>Subnormal<br>Normal<br>Infinity<br>NaN |

|------|-------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------|

| outB | "001"<br>"011"<br>"100" | when EB = X"00"<br>when (EB > X"00"<br>when EB = X"FF"<br>when EB = X"FF" | and MB = 0 else<br>and MB > 0 else<br>" and EB < X"FF")<br>and MB = 0 else<br>and MB > 0 else                         | and MB $>$ 0 else | Zero<br>Subnormal<br>Normal<br>Infinity<br>NaN |

Table 2. Data coded

| Exponent                                                            | Mantissa | Output    | Output Coded |

|---------------------------------------------------------------------|----------|-----------|--------------|

| = 0                                                                 | = 0      | Zero      | 000          |

| = 0                                                                 | > 0      | Subnormal | 001          |

| 0 <e<255< td=""><td>&gt; 0</td><td>Normal</td><td>011</td></e<255<> | > 0      | Normal    | 011          |

| = 255                                                               | = 0      | Infinity  | 100          |

| = 255                                                               | > 0      | NaN       | 110          |

Once both A and B numbers have been coded the different signals combinations are taken into account.

Sign, mantissa and exponent are calculated depending on *outA* and *outB* values. For example, if *outA* is a zero and *outB* is a normal number, the result is the normal number coded in *outB*.

All the possible values are shown in table 3 and also in the VHDL code added.

```

process (SA, SB, outA, outB)

begin

----- Zero

if (outA = "000") then

-- Zero +/- Number B

SS <= SB;

ES <= EB;

MS <= MB;

elsif (outB = "000") then

-- Number A +/- Zero

SS <= SA;

ES <= EA;

MS \ll MA;

end if;

----- Infinite

if (outA(0) = '1' and outB = "100") then

-- Normal or Subnormal +/- Infinity

SS <= SB:

ES <= EB;

MS \ll MB:

elsif (outB(0) = '1' and outA = "100") then

-- Infinity +/- Normal or Subnormal

SS <= SA;

ES <= EA;

MS \ll MA;

end if;

if ((outA and outB) = "100" and SA = SB) then

-- +/- Infinity +/- Infinity

SS <= SA;

ES <= EA;

MS <= MA;

----- NaN

elsif ((outA and outB) = "100" and SA /= SB) then -- + Infinity - Infinity

SS <= '1';

ES <= X''FF'';

MS <= "0000000000000000000001";</pre>

if (outA = "110" or outB = "110") then

SS <= '1';

ES <= X'' F F'';

end if:

----- Normal / Subnormal

if((outA(0) and outB(0)) = '1') then

SS <= '-';

ES <= "-----";

MS <= "-----";

end if;

end process;

```

Table 3. Output coded

| Sign  | Out A              | Out B              | Sign Output | Output   |

|-------|--------------------|--------------------|-------------|----------|

| Х     | Zero               | Number B           | SB          | Number B |

| Х     | Number A           | Zero               | SA          | Number A |

| Х     | Normal / Subnormal | Infinity           | SB          | Infinity |

| Х     | Infinity           | Normal / Subnormal | SA          | Infinity |

| SA=SB | Infinity           | Infinity           | SX          | Infinity |

| SA≠SB | Infinity           | Infinity           | 1           | NaN      |

| Х     | NaN                | Number B           | 1           | NaN      |

| Х     | Number A           | NaN                | 1           | NaN      |

X: do not care SA: Number A's sign SB: Number B's sign SX: Sign A or B (it is the same)

Finally an enable signal has been made. If any normal or subnormal combination is had the enable signal is high, otherwise low.

```

-- If A and B are normal or subnormal numbers, enable = 1

-- If not, enable = 0

enable <= '1' when ((outA(0) and outB(0)) = '1') else '0';</pre>

```

| /n_case/numberD 0111111100000000000000000000000000000 | 000000000000000                         | 111111110000000000000000000000000000000 | 00000000000000                          | 010101010000000000000000000000000000000 | 000000000000                            | 100000000000000000000000000000000000000 | 000000000001 | 000000000000000000000000000000000000000 | 00000000 |

|-------------------------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|--------------|-----------------------------------------|----------|

| /n_case/enable                                        |                                         |                                         |                                         |                                         |                                         |                                         |              | •                                       |          |

| /n_case/s 1111111100000000000000000000001             | 000000000000000000000000000000000000000 | 111111111000000000000000000000000000000 | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | XX                                      |              | 100000000000000000000000000000000000000 | 0000000  |

| /n_case/outa 011 NG                                   | Normal Num                              | Der                                     |                                         |                                         |                                         | 5                                       |              | •                                       |          |

| /u_case/sa                                            |                                         |                                         |                                         |                                         |                                         |                                         |              |                                         |          |

| /n_case/ea 170                                        |                                         |                                         |                                         |                                         |                                         |                                         |              |                                         |          |

| /n_case/ma 1                                          |                                         |                                         |                                         |                                         |                                         |                                         |              |                                         |          |

| /n_case/outb 110                                      | NaN                                     | 100                                     | -Infinity                               | 011                                     | Normal                                  | 001                                     | Subnormation |                                         | Zelo     |

| /n_case/sb                                            |                                         |                                         |                                         |                                         |                                         |                                         |              |                                         |          |

| /n_case/eb 255                                        | *<br>*                                  |                                         |                                         | 170                                     |                                         | 0                                       |              |                                         |          |

| /n_case/mb_1                                          |                                         |                                         |                                         | -                                       |                                         |                                         |              |                                         |          |

| /n_case/ss                                            | •                                       |                                         |                                         |                                         |                                         |                                         |              |                                         |          |

| /n_case/es 255                                        |                                         |                                         |                                         | ×                                       |                                         | 716,541                                 |              | 120                                     |          |

| In casalms 1                                          |                                         |                                         |                                         | ×                                       |                                         |                                         |              |                                         |          |

|                                                       |                                         |                                         |                                         |                                         |                                         |                                         |              |                                         |          |

|                                                       | NaN                                     | _                                       | -Infinity                               | Normal                                  | /Subnor                                 | Normal/Subnormal combination            | nation       | ž                                       | Normal   |

|                                                       |                                         |                                         |                                         | - ES and                                | H MS (out                               | ES and MS (output exponent and          | ent and      |                                         |          |

|                                                       |                                         |                                         |                                         | mantissa                                | mantissa) are undefined                 | efined.                                 |              |                                         |          |

|                                                       |                                         |                                         |                                         | - Signal                                | signal <i>enable</i> is high            | ngn                                     |              |                                         |          |

|                                                       |                                         |                                         |                                         |                                         |                                         |                                         |              |                                         |          |

|                                                       |                                         |                                         |                                         |                                         |                                         |                                         |              |                                         |          |

|                                                       |                                         |                                         |                                         |                                         |                                         |                                         |              |                                         |          |

|                                                       |                                         |                                         |                                         |                                         |                                         |                                         |              |                                         |          |

|                                                       |                                         |                                         |                                         |                                         |                                         |                                         |              |                                         |          |

|                                                       |                                         |                                         |                                         |                                         |                                         |                                         |              |                                         |          |

|                                                       |                                         |                                         |                                         |                                         |                                         |                                         |              |                                         |          |

Figure 10. n\_case Simulation

## 3.2. Subnormal Numbers

The operation using subnormal numbers is the easiest one.

It is designed in just one block and the procedure is as follows:

- 1. Obtaining the two sign bits and both mantissas

- 2. Making a comparison between both A and B numbers in order to acquire the largest number

- 3. Fixing the result exponent in zero

#### 3.2.1. n\_subn Block

Obviously Number A and B are the entries. The outputs are six. *SA-MA* and *SB-MB* contain the sign and mantissa of A and B respectively. *Comp* signal is referred to the result comparison and *EO* is the result exponent.

The code is so simply. Sign and mantissa of both numbers are obtained directly from the entries *NumberA* and *NumberB*. The outputs exponent *EO* is always zero because the input exponents are zero as well and *Comp* signal is high when A is bigger than B and low in the opposite case.

The comparison operation does not take into account the sign of the numbers. If the result is negative or positive it will be calculated in the Adder block using *SA*, *SB* and *Comp* signals.

| SA <= NumberA(36);<br>SB <= NumberB(36);                         | Sign A & B        |

|------------------------------------------------------------------|-------------------|

| MAa <= NumberA(27 downto 0);<br>MBb <= NumberB(27 downto 0);     | Mantissa A & B    |

| C <= '1' when MAa >= MBb else<br>'0' when MBb > MAa else<br>'-'; |                   |

| Comp <= C;                                                       |                   |

| EO <= NumberA(35 downto 28);                                     | Output's exponent |

| MB <= MBb when C = '1' else<br>MAa when C = '0' else             | Mantissa          |

| MA <= MAa when C = '1' else<br>MBb when C = '0' else             | <i>";</i>         |

| <i>n</i>                                                         | .";               |

|                                                                                                                                                                                                                                                                                                                                                               | C+15 S0 ns 150 ns 250 n |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bits                                                                                                                                                                                                                                                                                                                                                          | s 111111111111111111111111111111111111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| EO Implicit bit + Mantissa + Guard bits<br>SA<br>/n_subn/numberb<br>/n_subn/numberb<br>/n_subn/sa<br>/n_subn/sa<br>/n_subn/sa<br>/n_subn/sa<br>/n_subn/mb<br>/n_subn/mb<br>/n_subn/mb<br>/n_subn/mb<br>/n_subn/mb<br>/n_subn/mb<br>/n_subn/mb<br>/n_subn/mb<br>/n_subn/mb<br>/n_subn/mb<br>/n_subn/mb<br>/n_subn/mb<br>/n_subn/mb<br>/n_subn/mb<br>/n_subn/mb | Reference (100 ms (100 |

Figure 11. n\_subn Entity

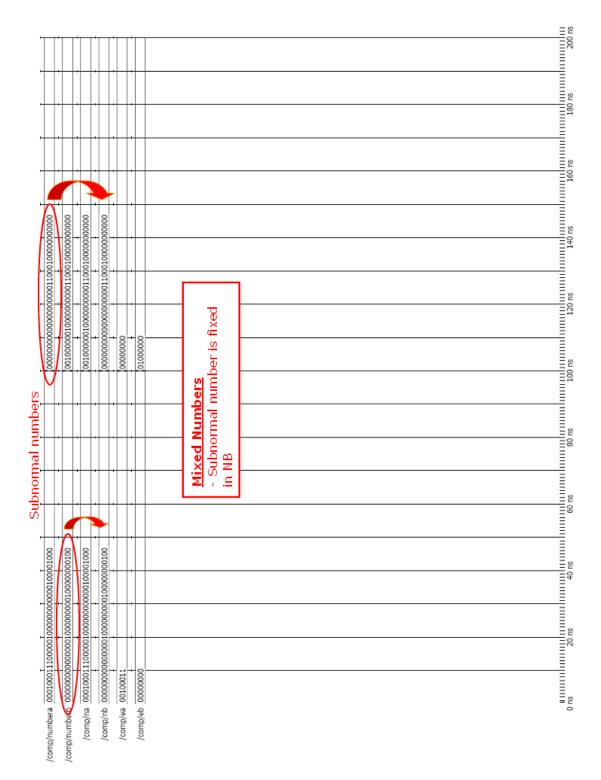

## 3.3. Mixed Numbers

When there is a mixed combination of numbers (one subnormal and other normal) the subnormal one must have a special treatment in order to be added or subtracted to the normal one.

The subnormal number treatment is going to be discuss in this block because once both numbers will be standardized the next block (normal numbers block) will be in charge of the operation between normal ones.

Figure 12. Mixed numbers block diagram

The work operation can be summarized in the following points:

- 1. Finding out what the subnormal number is

- 2. Counting the number of zeros the subnormal number has on the beginning

- 3. Shifting the vector and calculating the new exponent

This block is formed by three entities and each one is responsible for one of the points described.

#### 3.3.1. comp Block

First block is *comp* entity. The block entries are both numbers and the outputs are the same numbers ordered as normal *NA* and subnormal *NB*.

|                         |      |               | entity comp : | is      |                                                        |

|-------------------------|------|---------------|---------------|---------|--------------------------------------------------------|

| Number A (2C + 0)       |      | ▶ NA (36 : 0) | Port (        | NumberA | . : in std logic vector(36 downto 0); Number A         |

| Number A (36 : 0) ———►  |      |               |               | NumberB | ; in std logic vector(36 downto 0); Number B           |

|                         | comp | ► NB (36 : 0) |               | NA      | : out std logic vector(36 downto 0); Normal number     |

| Number B (36 : 0) — 🕨 🕨 |      |               |               | NB      | : out std logic vector(36 downto 0)); Subnormal number |

| L                       |      |               | end comp;     |         |                                                        |

The code is not very extensive. A and B Mantissas are ordered according to the exponent: null exponent indicates what the subnormal number is and then this number is fixed in *NB*, leaving the normal one in *NA*.

```

EA <= NumberA(35 downto 28); -- Exponent & Mantissa

EB <= NumberB(35 downto 28);

process (NumberA, NumberB, EA, EB)

begin

if EA = X"00" then -- If Number A is subnormal...

NB <= NumberA;

NA <= NumberB;

elsif EB = X"00" then -- If Number B is subnormal...

NB <= NumberB;

NA <= NumberA;

else

NA <= "------";

NB <= "-----";

end if;

```

end process;

Figure 13. comp Simulation

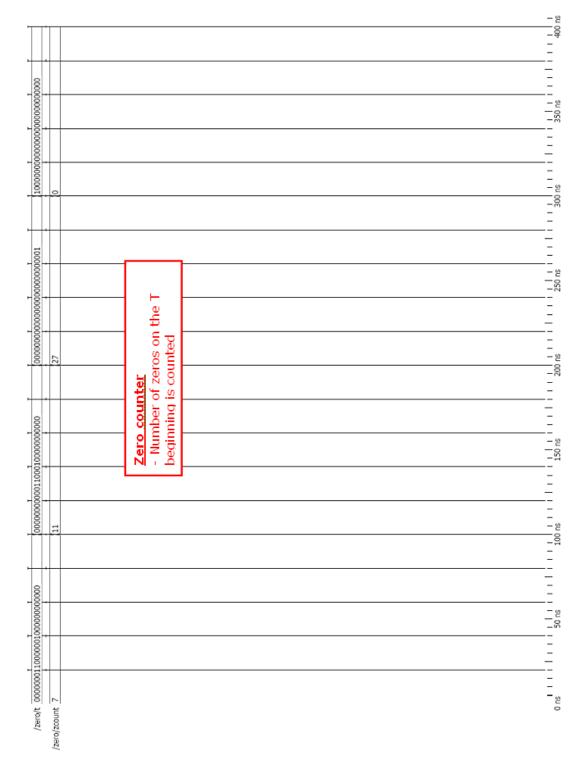

#### 3.3.2. zero Block

Counting zeros is the *zero* block target. The mantissa which is needed to shift is introduced as an entry in *T* vector and the output *Zcount* contains the number of zeros the mantissa has on the beginning which corresponds with the number of positions the vector must be shifted.

|          |   |              |                  | entity zero | is                                                                                                               |

|----------|---|--------------|------------------|-------------|------------------------------------------------------------------------------------------------------------------|

| T (27:0) | - | zero_counter | ► Zcount (4 : 0) | Port (      | T : in std_logic_vector(27 downto 0); Significand<br>Zcount : out std_logic_vector(4 downto 0)); Number of Zeros |

|          |   |              |                  | end zero;   |                                                                                                                  |

A zero vector is created (*Zero\_vector*) and compared with the *T* vector. The *Zcount* value depends on the number of matches.

| aux | <= ""      | when T(27 o | downto 27) = "-" else                  |

|-----|------------|-------------|----------------------------------------|

|     |            |             | o 0) = Zero vector(27 downto 0) else   |

|     |            |             | o 1) = Zero vector(27 downto 1) else   |

|     |            |             | o 2) = Zero vector(27 downto 2) else   |

|     |            |             | o 3) = Zero vector(27 downto 3) else   |

|     |            |             | o 4) = Zero vector(27 downto 4) else   |

|     | X"17" when | T(27 downto | o 5) = Zero vector(27 downto 5) else   |

|     | X"16" when | T(27 downto | o 6) = Zero_vector(27 downto 6) else   |

|     | X"15" when | T(27 downto | o 7) = Zero_vector(27 downto 7) else   |

|     | X"14" when | T(27 downto | o 8) = Zero_vector(27 downto 8) else   |

|     | X"13" when | T(27 downto | o 9) = Zero_vector(27 downto 9) else   |

|     | X"12" when | T(27 downto | o 10) = Zero_vector(27 downto 10) else |

|     | X"11" when | T(27 downto | o 11) = Zero_vector(27 downto 11) else |

|     | X"10" when | T(27 downto | o 12) = Zero_vector(27 downto 12) else |

|     | X"OF" when | T(27 downto | o 13) = Zero_vector(27 downto 13) else |

|     |            |             | o 14) = Zero_vector(27 downto 14) else |

|     | X"OD" when | T(27 downto | o 15) = Zero_vector(27 downto 15) else |

|     | X"OC" when | T(27 downto | o 16) = Zero_vector(27 downto 16) else |

|     | X"OB" when | T(27 downto | o 17) = Zero_vector(27 downto 17) else |

|     | X"OA" when | T(27 downto | o 18) = Zero_vector(27 downto 18) else |

|     |            |             | o 19) = Zero_vector(27 downto 19) else |

|     | X"08" when | T(27 downto | o 20) = Zero_vector(27 downto 20) else |

|     |            |             | o 21) = Zero_vector(27 downto 21) else |

|     |            |             | o 22) = Zero_vector(27 downto 22) else |

|     | X"05" when | T(27 downto | o 23) = Zero_vector(27 downto 23) else |

|     |            |             | o 24) = Zero_vector(27 downto 24) else |

|     |            |             | o 25) = Zero_vector(27 downto 25) else |

|     |            |             | o 26) = Zero_vector(27 downto 26) else |

|     |            | T(27 downto | o 27) = Zero_vector(27 downto 27) else |

|     | X″00″;     |             |                                        |

|     |            |             |                                        |

Zcount <= aux(4 downto 0);</pre>

Figure 14. zero Simulation

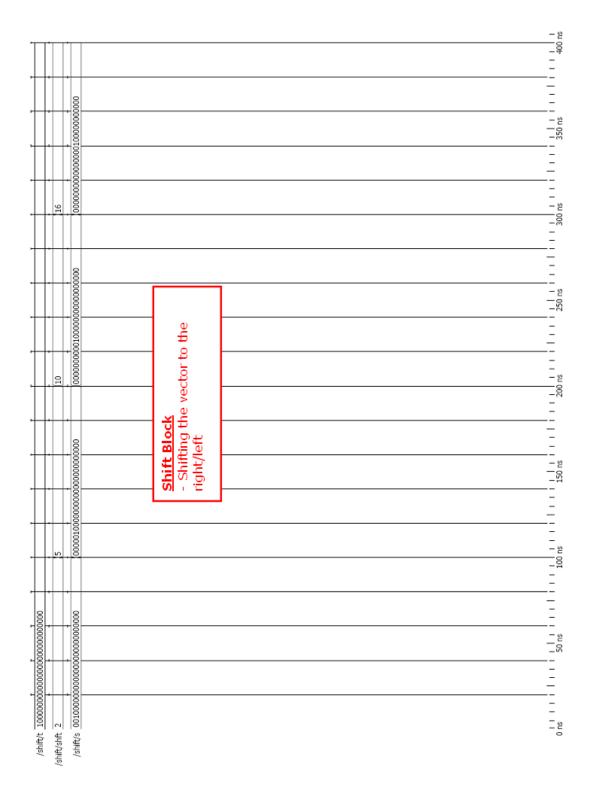

#### 3.3.3.

shift\_left/shift Block

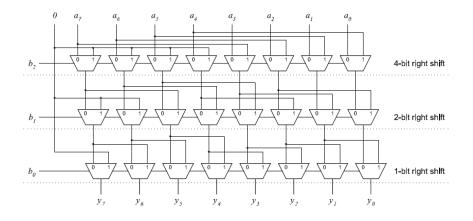

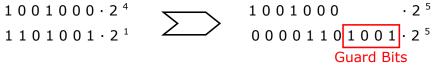

Shifting is required to match the normal and mixed mantissas to perform the addition/subtraction properly.

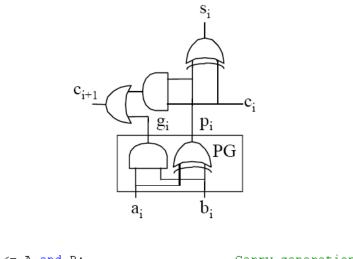

A logarithmic shift schematic as the figure 15 is used but with some differences.

28 bits (1 implicit bit + 23 mantissa's bits + 4 guard bits) is had in the Floating point Adder design then up to 28 positions must be able to shift. Because of the fact that this shifter consists of 5 stages: the first stage shift one position, the second stage 2, the third one 4, the fourth one 8 and the last one 16. Using any combination 32 positions are able to shift which is big enough to the design purpose.

Both shifting left and shifting right are used in the Floating Point Adder implementation. In this chapter, the first one is explained but the code is quite similar to the second one. There is only a difference: the T vector order. If the bits order is changed from 0-27 to 27-0 a shifting right is achieved.

Figure 15. Logarithmic shift

The *T* vector and the number of positions to shift (*Shft*) are the entries of the *shift* entity. The shifted signal is set in *S*.

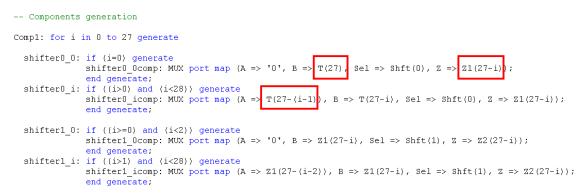

The code is implemented as follows. A multiplexor has been designed and exported to this block. Afterwards a loop *for* has been used to generate the different 5 stages. Following the cascade design which has been shown before a 32 positions logarithmic shifter is implemented.

```

signal Z1, Z2, Z3, Z4, Z5 : std logic vector(27 downto 0);

begin

-- Components generation

Comp1: for i in 0 to 27 generate

shifter0 0: if (i=0) generate

shifter0 0comp: MUX port map (A => '0', B => T(0), Sel => Shft(0), Z => Z1(i));

end generate;

shifterO i: if ((i>O) and (i<28)) generate

shifter0 icomp: MUX port map (A => T((i-1)), B => T(i), Sel => Shft(0), Z => Z1(i));

end generate;

shifter1_0: if ((i>=0) and (i<2)) generate

shifter1 0comp: MUX port map (A => '0', B => Z1(i), Sel => Shft(1), Z => Z2(i));

end generate;

shifter1_i: if ((i>1) and (i<28)) generate</pre>

\label{eq:shifter1_icomp: MUX port map (A => Z1((i-2)), B => Z1(i), Sel => Shft(1), Z => Z2(i));

end generate;

shifter2_0: if ((i>=0) and (i<4)) generate

shifter2 Ocomp: MUX port map (A => '0', B => Z2(i), Sel => Shft(2), Z => Z3(i));

end generate;

shifter2 i: if ((i>3) and (i<28)) generate

shifter2 icomp: MUX port map (A => Z2((i-4)), B => Z2(i), Sel => Shft(2), Z => Z3(i));

end generate;

shifter3_0: if ((i>=0) and (i<8)) generate

shifter3_0comp: MUX port map (A => '0', B => Z3(i), Sel => Shft(3), Z => Z4(i));

end generate;

shifter3 i: if ((i>7) and (i<28)) generate

shifter3_icomp: MUX port map (A => Z3((i-8)), B => Z3(i), Sel => Shft(3), Z => Z4(i));

end generate;

shifter4 0: if ((i \ge 0) \text{ and } (i < 16)) generate

shifter4_Ocomp: MUX port map (A => '0', B => Z4(i), Sel => Shft(4), Z => Z5(i));

end generate:

shifter4_i: if ((i>15) and (i<28)) generate

shifter4_icomp: MUX port map (A => Z4((i-16)), B => Z4(i), Sel => Shft(4), Z => Z5(i));

end generate;

```

end generate;

s <= Z5;

Figure 16. shift\_left/shift Simulation

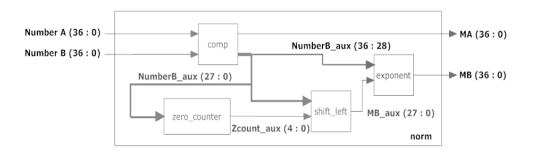

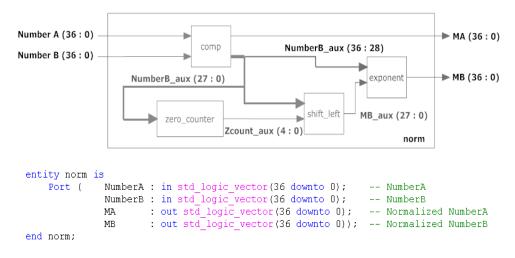

3.3.4. norm Block

Finally, the rest of the entities are all included in the *norm* block. It also performs the output exponent treatment.

The inputs are the numbers A and B. Once the subnormal one has been shifted it is fixed in *MB*. The normal number is set in *MA*.

The code could be divided in two parts. The first one implements the connection between the different blocks which the mixed numbers entity works with. The block diagram is coherent with the VHDL code.

```

comp0 : zero

port map (T => NumberB_aux(27 downto 0), Zcount => Zcount_aux);

comp1 : shift_left

port map (T => NumberB_aux(27 downto 0), shft => Zcount_aux, S => MB_aux);

comp2 : comp

port map (NumberA => NumberA, NumberB => NumberB, NA => MA, NB => NumberB aux);

```

The second one is pretty interesting. As it has been explained before, negative prebiased exponents are not considered by the standard IEEE 754 but there is a possibility a normal and subnormal number may be operated. The number of positions the vector *MB* is shifted could be saved as a positive exponent but introducing a mark in the last guard bit which indicates the positive exponent is actually "negative".

So if a normal number with a quite small exponent is had it is possible that normal and subnormal numbers are able to be operated.

```

----- New Exponent

process(Zcount_aux, NumberB_aux, EB, MB_aux)

begin

if Zcount_aux /= "-----" then

EB <= "000" & Zcount_aux; -- Number shifted

MB(27 downto 0) <= MB_aux(27 downto 1) & '1'; -- Bit 0 --> Mark

else

EB <= "------";

MB(27 downto 0) <= MB_aux;

end if;

MB(35 downto 28) <= EB;

MB(36) <= NumberB_aux(36);

end process;</pre>

```

| 00011100011000110001000000000000000000             | Norm Block - "Negative" exponent is calculated and LSB is marked |  |

|----------------------------------------------------|------------------------------------------------------------------|--|

| /norm/numbera 000000000000000000000000000000000000 |                                                                  |  |

Figure 17. norm Simulation

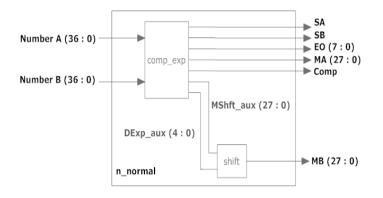

## 3.4. Normal Numbers

Two normal numbers are the most common operation mode because it represents the main operation without any exception.

The procedure is as follows:

- 1. Making a comparison between both A and B numbers and obtaining the largest number

- 2. Obtaining the output exponent (the largest one)

- 3. Shifting the smallest mantissa to equal both exponents

Figure 18. Normal numbers block diagram

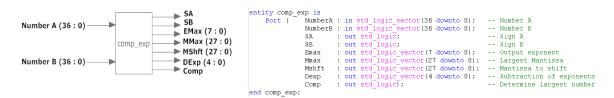

### 3.4.1.

### comp\_exp Block

The *comp\_exp* entries are the two introduced numbers again. There are several outputs: *SA* and *SB* are the sign of A and B respectively, *EMax* is the output exponent, *MMax* the largest mantissa, *Mshft* the mantissa to shift, *Dexp* the number of positions *Mshft* must be shifted and *Comp* indicates what number is the largest one.

Exponents and signs are obtained from the introduced numbers directly. Once the exponents are fixed in *EA* and *EB* signals, these values are used to determine the largest number: if A is larger than B or number B's LSB (negative exponent mark) is high, *Comp* will be `1', otherwise `0'.

Using this signal the output exponent could be determined.

```

SA \ll NumberA(36);

-- Sign A & B

SB <= NumberB(36);</pre>

EA <= NumberA(35 downto 28);

-- Exponent & Mantissa

EB <= NumberB(35 downto 28);

MA <= NumberA(27 downto 0);</pre>

MB <= NumberB(27 downto 0);</pre>

----- Exponent Comparison

C \le '1' when (EA > EB) or (MB(0) = '1') else

-- Exponent A > Exponent B

'0' when EA < EB else

-- Exponent B > Exponent A

'1' when MA \geq MB else

-- EA = EB --> A > B

'0' when MA < MB else

-- EA = EB --> B > A

'-';

Comp <= C;

----- Largest exponent

Emax <= EA when C = '1' else

EB when C = '0' else

"----";

```

Next step is determining the difference between both exponents. Once more time *comp* signal fixes the largest exponent and determines the subtraction order.

If B's LSB is high a negative exponent is had. In this case EA and EB are added.

```

----- Difference between exponents

dif \langle = EA-EB when (C = '1') and (MB(0) = '0') else

EB-EA when C = '0' else

EA+EB when (C = '1') and (MB(0) = '1') else

"----";

process (dif)

begin

if dif <= X"1B" then -- If the difference is less than or equal to 27...

Dexp <= dif(4 downto 0); -- Use directly the subtraction between exponents

elsif dif > X"1B" then -- If the difference is greater...

Devp <= "11100": -- The difference is 28</pre>

Dexp <= "11100";

-- The difference is 28

else

Dexp <= "-----";</pre>

end if:

end process;

----- Mantissa

Mshft <= MB when C = '1' else

MA when C = '0' else

"_____" :

Mmax <= MA when C = '1' else

MB when C = '0' else

_____" .

```

The mantissa to shift corresponds with the smallest number (using *comp* again).

Finally a maximum value is set if the difference between exponents is greater than 28 which is the maximum number of bits that the mantissa has.

|                                       | 00111001110000000000000000000000000000                                                                          | 10001010000000000000000000000000000000     |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------|

|                                       | 00001100000000000000000000000000000000                                                                          | 9<br>1000000000000000000000000000000000000 |

|                                       | 000011000000000000000000000000000000000                                                                         | 9<br>1000000000000000000000000000000000000 |

| · · · · · · · · · · · · · · · · · · · | 000001100000000000000000000000000000000                                                                         | 10000000000000000000000000000000000000     |

|                                       | 000000011110000000000000000000000000000                                                                         | 20 100000000000000000000000000000000000    |

|                                       | 000000000000000000000000000000000000000                                                                         | 20<br>100000000010000000000000000000000000 |

|                                       | 000000011110000000000000000000000000000                                                                         | 100000000010000000000000000000000000000    |

|                                       | 000000000000000000000000000000000000000                                                                         | 20                                         |

| .≪                                    | 000011000000000000000000000000000000000                                                                         |                                            |

|                                       | 0000000000                                                                                                      | 100000000100000000000000000000000000000    |

|                                       | · · ·                                                                                                           | 100000000000000000000000                   |

| EA + EB                               |                                                                                                                 |                                            |

|                                       |                                                                                                                 |                                            |

| Comp                                  | exp Block                                                                                                       |                                            |

| - Comp                                | Compare both numbers<br>Determine Mmax_Mshft and                                                                |                                            |

| Emax                                  | the second se |                                            |

| - Obtair<br>between                   | <ul> <li>Obtain the difference<br/>between exponents</li> </ul>                                                 |                                            |

|                                       |                                                                                                                 |                                            |

|                                       |                                                                                                                 |                                            |

|                                       |                                                                                                                 |                                            |

|                                       |                                                                                                                 |                                            |

|                                       |                                                                                                                 |                                            |

### 3.4.2. shift Block

A shifter is needed to match the exponents. The entity is the same than in the mixed case. The vector T is the input which contains the mantissa to shift, *shft* fix the number of positions to move and S is the output with the result of the operation.

The code is quite similar. Only a part is added because it is enough to see its operation.

Changing the order of the vector, a displacement in the other direction is achieved. The simulation is not required because the result is the same but on the right.

n normal Block

### 3.4.3.

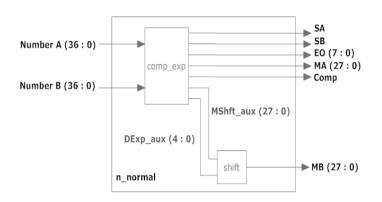

# The *n\_normal* block includes the two blocks which have been explained above. The entries are *NumberA* and *NumberB* and the outputs are both sign A (*SA*) and sign B (*SB*), the result exponent (*EO*), the *Comp* signal and the two mantissas (*MA* and *MB*).

| entity n_norma           | al is   |   |                                                |                       |

|--------------------------|---------|---|------------------------------------------------|-----------------------|

| Port (                   | NumberA | : | <pre>in std logic vector(36 downto 0);</pre>   | <br>Number A          |

|                          | NumberB | : | <pre>in std_logic_vector(36 downto 0);</pre>   | <br>Number B          |

|                          | Comp    | : | out std_logic;                                 | <br>A & B Comparison  |

|                          | SA      | : | out std_logic;                                 | <br>Sign A            |

|                          | SB      | : | <pre>out std_logic;</pre>                      | <br>Sign B            |

|                          | EO      | : | <pre>out std_logic_vector(7 downto 0);</pre>   | <br>Exponent Output   |

|                          | MA      | : | <pre>out std_logic_vector(27 downto 0);</pre>  | <br>Greatest Mantissa |

|                          | MB      | : | <pre>out std_logic_vector(27 downto 0));</pre> | <br>Shifted Mantissa  |

| <pre>end n_normal;</pre> |         |   |                                                |                       |

The VHDL code implements just the interconnection between the different blocks.

*Comp\_exp* fix the mantissa which has to been shifted and the number of positions it must be displaced.

*Shift* block collects these two signals and gives the mantissa in order to be operated in the next block: the *Adder* block.

00011010000011000000100000100001000010 1111000000001100010000000 Comp = '1' → MA := Number≜ 田 1000000110000001111000001000 Ā  $\mathbf{T}$ Dexp\_aux Normal operation 46 operated shifting the smallest - Determine the sign and the - Obtain the mantissas to be Ā £ N normal Block output exponent  $\mathbf{T}$ "Negative" exponent Jexp\_aux 166 8 one 0000010101010101010101010100000 £ 0000001010101010101010101010 /n\_normal/mshft\_aux 10101010101010101010100001 + Ā  $\mathbf{T}$ Dexp\_aux 6 2 /n\_normal/ma /n\_normal/numberb /n\_normal/sa /n\_normal/mb /n\_normal/dexp\_aux /n\_normal/comp /n\_normal/eo /n\_normal/sb

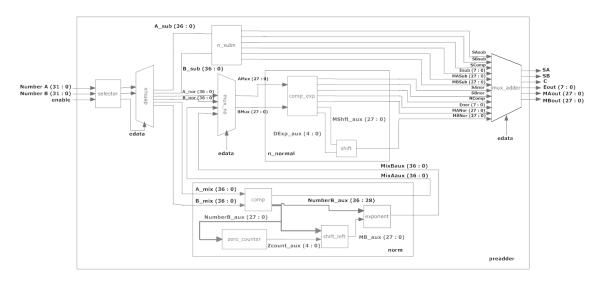

## 3.5. Pre-Adder

Finally a complete Pre-Adder block diagram will be shown and explained. As it could be seen there are some blocks which are not discussed. These blocks are 4:

- 1. The first one is so important: *Selector* block

- 2. A demultiplexor (*demux*) to route the signal in the correspondent block

- 3. A multiplexor (*mux\_ns*) to choose between the mixed numbers or the normal ones

- 4. A multiplexor (mux\_adder) to choose between the normal or subnormal numbers

Figure 21. preadder block diagram

These blocks are going to be grouped in two different chapters. First one includes only the *selector* block which is more important and has more complexity.

The second group contains the different multiplexors and demultiplexors. They are going to be treated all together because of code's simplicity.

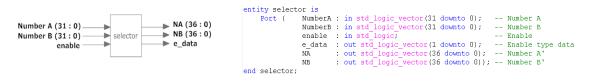

### 3.5.1. selector Block

*Selector* block prepares the numbers: the entries are shorter than outputs because the implicit bit (high if the number is normal and low in subnormal's case) and the guard bits are added in this block. *Enable* signal enables this block (and therefore the entire *preadder* block) when we do not have a special case.

The outputs are the two numbers with the added bits and the *e\_data* signal which distinguish between normal, subnormal and mixed numbers.

If *enable* signal is high it means we do not have a special case. Then the outputs signals *NA* and *NB* are made: first the sign and exponent bits are placed in its positions.

Next step, the implicit bit is fixed according with the exponent value. The mantissa and the guard bits are added too.

```

SA <= NumberA(31);

SB <= NumberB(31);</pre>

EA <= NumberA(30 downto 23):

EB <= NumberB(30 downto 23);</pre>

MA <= NumberA(22 downto 0);</pre>

MB <= NumberB(22 downto 0);</pre>

process (SA, SB, EA, EB, MA, MB, enable)

begin

if enable = '1' then

NA(36) <= SA;

-- Exponent & sign A

NA(35 downto 28) <= EA;

NB(36) <= SB;

-- Exponent & sign B

NB(35 downto 28) <= EB;

If the exponent is bigger

_____ Mantissa A

than 0 \rightarrow Normal Number

if (EA > X"00") then

NA(27) <= '1';</pre>

Implicit bit \rightarrow '1'

-- Implicit bit

NA(26 downto 4) <= MA; -- Mantissa

NA(3 downto 0) <= X"0"; -- Guard bits

_{\blacktriangleright} If the exponent is 0 \rightarrow

elsif EA = X"00" then -----

NA(27) <= '0';</td>

-- Implicit bit

NA(26 downto 4) <= MA;</td>

-- Mantissa

NA(27) <= '0';

Subnormal Number

Implicit bit \rightarrow '0'

NA(3 downto 0) \leq X''0'';

-- Guard bits

else

NA <= "-----";

end if;

----- Mantissa B

if (EB > X''00'') then

NB(27) <= '1';

-- Implicit bit

NB(26 downto 4) <= MB; -- Mantissa

NB(3 downto 0) <= X"0"; -- Guard bits</pre>

elsif EB = X"00" then

NB(27) <= '0';

-- Implicit bit

NB(26 downto 4) <= MB;

-- Mantissa

NB(3 downto 0) <= X"0"; -- Guard bits

else

NB <=

end if;

else

NA <= "--

-----";

NB <= "-----";

end if;

end process;

```

Finally the *e\_data* signal is fixed as follows:

- 1. Subnormal numbers  $\rightarrow$  e\_data := "00"

- 2. Normal numbers  $\rightarrow$  e\_data := "01"

- 3. Mixed numbers  $\rightarrow$  e\_data := "10"

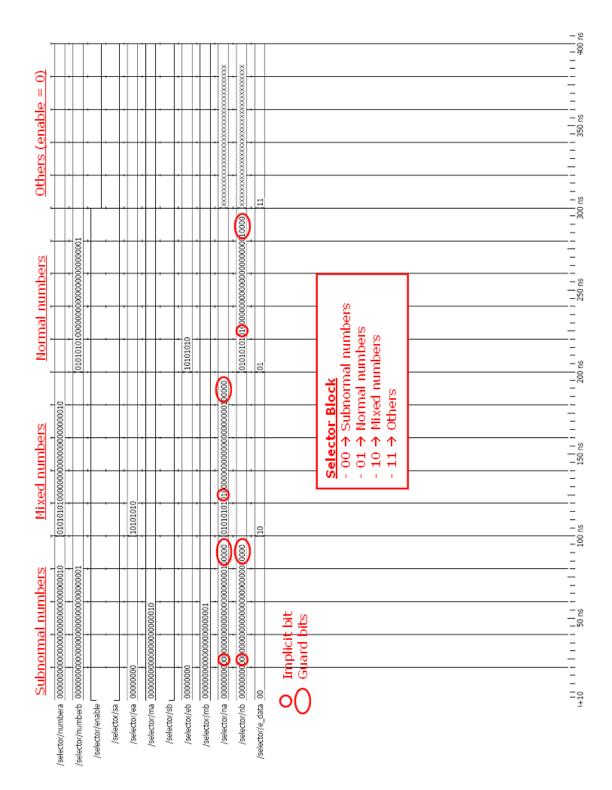

Figure 22. selector Simulation

3.5.2.

MUX/DEMUX Blocks

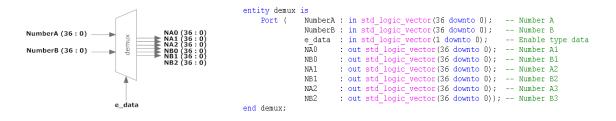

The operation of the *demux* demultiplexor is routing the A and B numbers to the subnormal, normal or mixed block according with the *e\_data* value.

*NumberA*, *NumberB* and the enable signal *e\_data* are the entries and the outputs are 3 pairs of signals but only one pair is activated in each time. The typical demultiplexor's behaviour.

```

process (NumberA, NumberB, e_data)

begin

```

```

case e data is

----- Subnormals

when "00"

=> NA0 <= NumberA;

NBO <= NumberB;

NA1 <= "-----";

"_____";

NB1 <=

NA2 <= "-----";

NB2 <= "-----";

----- Normals

when "01"

=> NA() <= "-----

NBO <= "-----";

NA1 <= NumberA;

NB1 <= NumberB;

NA2 <= "-----

NB2 <= "-----";

----- Mix

=> NAO <= "-----

when "10"

NBO <= "-----";

NA1 <= "-----":

NB1 <= "-----

NA2 <= NumberA;

NB2 <= NumberB;

"_____

when others => NAO <=

"_____

NB0 <=

"_____

NA1 <=

NB1 <= "-----";

"_____";

NA2 <=

NB2 <= "-----";

```

end case;

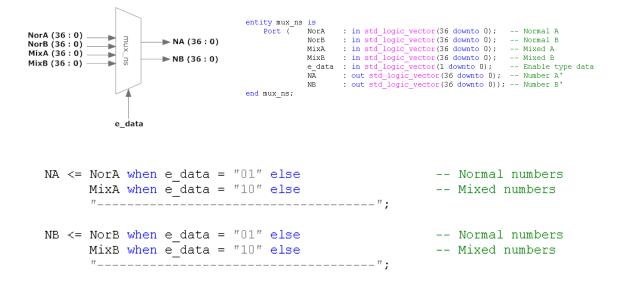

The *mux\_ns* multiplexor's target is selecting which signal must be introduced in the normal numbers block: normal numbers or a standardized numbers from the mixed numbers block.

The entries are the two pairs of numbers and  $e_{data}$  signal and the outputs are the A and B numbers according with  $e_{data}$  value.

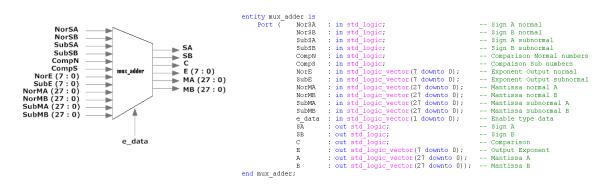

Finally *mux\_adder* multiplexor is in charge of selecting which data are going to be introduced in the adder.

The entries are the *comp* signal, the two mantissas, signs and exponents and all of them multiplied by two: one for the subnormal numbers and another for the normal/mixed numbers. The output is one of the pair's members according with  $e_data$ .

```

A <= NorMA when e data = "01" or e data = "10" else

-- Normal/Mix numbers

SubMA when e_data = "00" else

-- Subnormal numbers

"_____";

B <= NorMB when e data = "01" or e data = "10" else

-- Normal/Mix numbers

SubMB when e data = "00" else

-- Subnormal numbers

<= CompN when e data = "01" or e data = "10" else</pre>

С

-- Normal/Mix numbers

CompS when e data = "00" else

-- Subnormal numbers

1-1;

SA <= NorSA when e data = "01" or e data = "10" else

-- Normal/Mix sign A

SubSA when e_data = "00" else

-- Subnormal sign A

1-1:

SB <= NorSB when e data = "01" or e data = "10" else

-- Normal / Mix sign B

SubSB when e data = "00" else

-- Subnormal sign B

'-';

E <= NorE when e data = "01" or e data = "10" else

-- Normal / Mix exponent

SubE when e data = "00" else

-- Subnormal exponent

"----";

```

### *3.5.3.* preadder Block

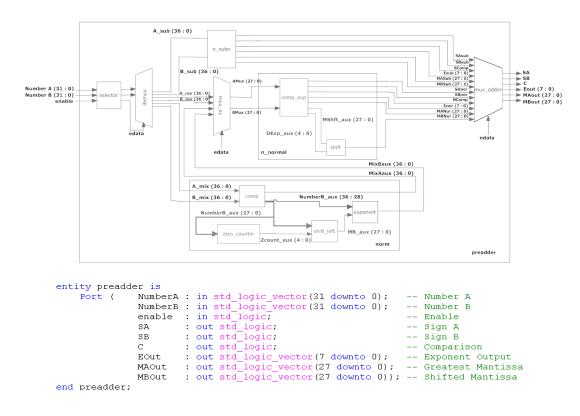

Finally the *preadder* block is going to be explained. The special cases block is not considered in this block diagram because it will be added next to *adder* block in a complete block diagram.

*NumberA, NumberB* and *enable* are the inputs. A and B sign (*SA* and *SB*), the *C* signal, output's exponent *Eout*, and both *MAout* and *MBout* mantissas are the outputs of the design.

The components description is shown in this part of the code. Normal numbers block ( $n\_normal$ ), subnormal numbers block ( $n\_subn$ ), mixed numbers block (*norm*), the multiplexor and demultiplexors ( $mux\_ns$ ,  $mux\_adder$  and demux) and the *selector* entity are added there.

```

----- Normal Numbers

component n normal port (NumberA, NumberB : in std logic vector(36 downto 0);

Comp : out std_logic;

SB : out std_logic;

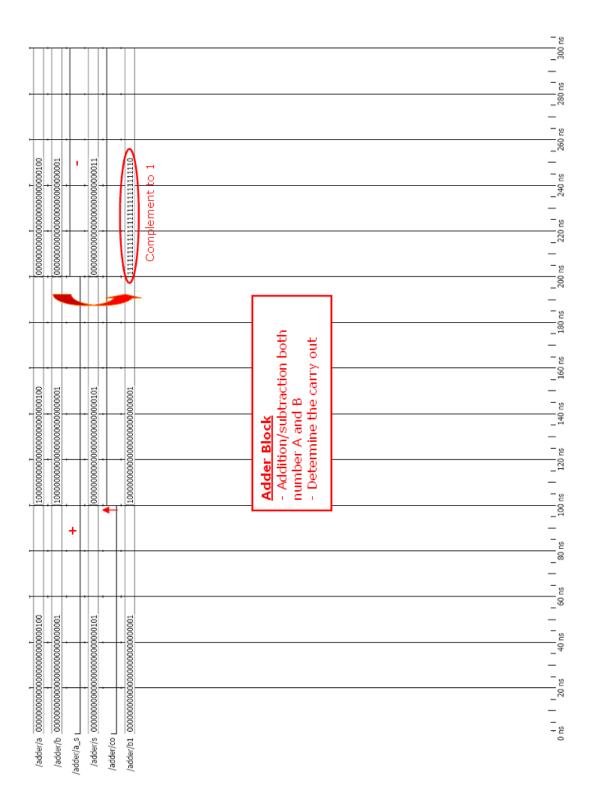

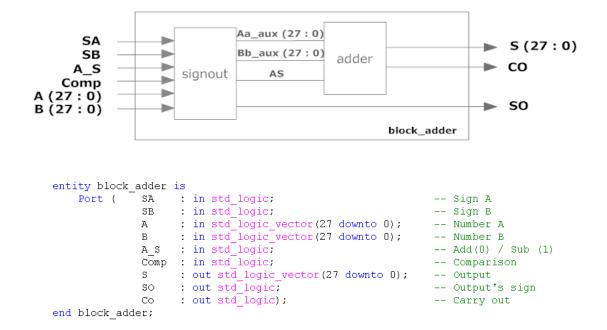

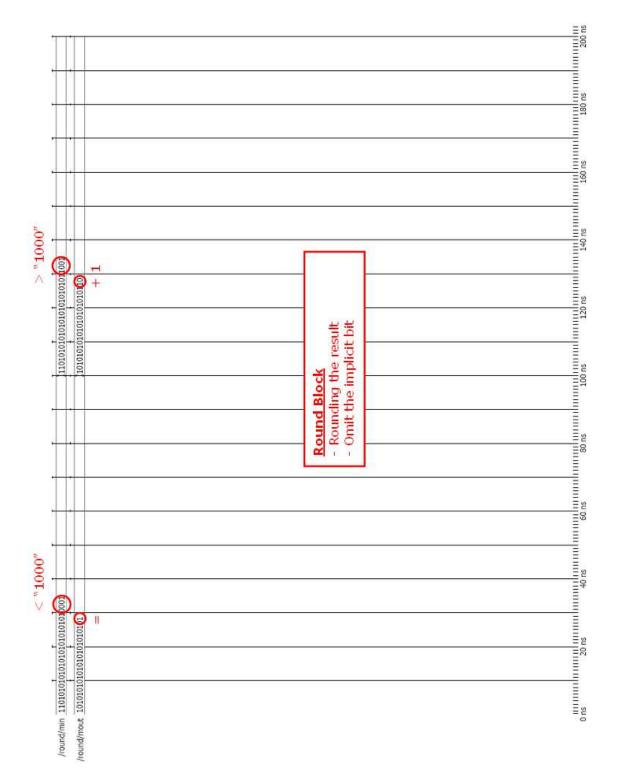

EO : out std_logic;